.P-J LJ

Изобретение относится к вычислительной технике и может быть использовано для сопряжения с вычислительными устройствами, функционирукяцими в системе остаточных классов.

Целью изобретения является сокращение аппаратурных затрат.

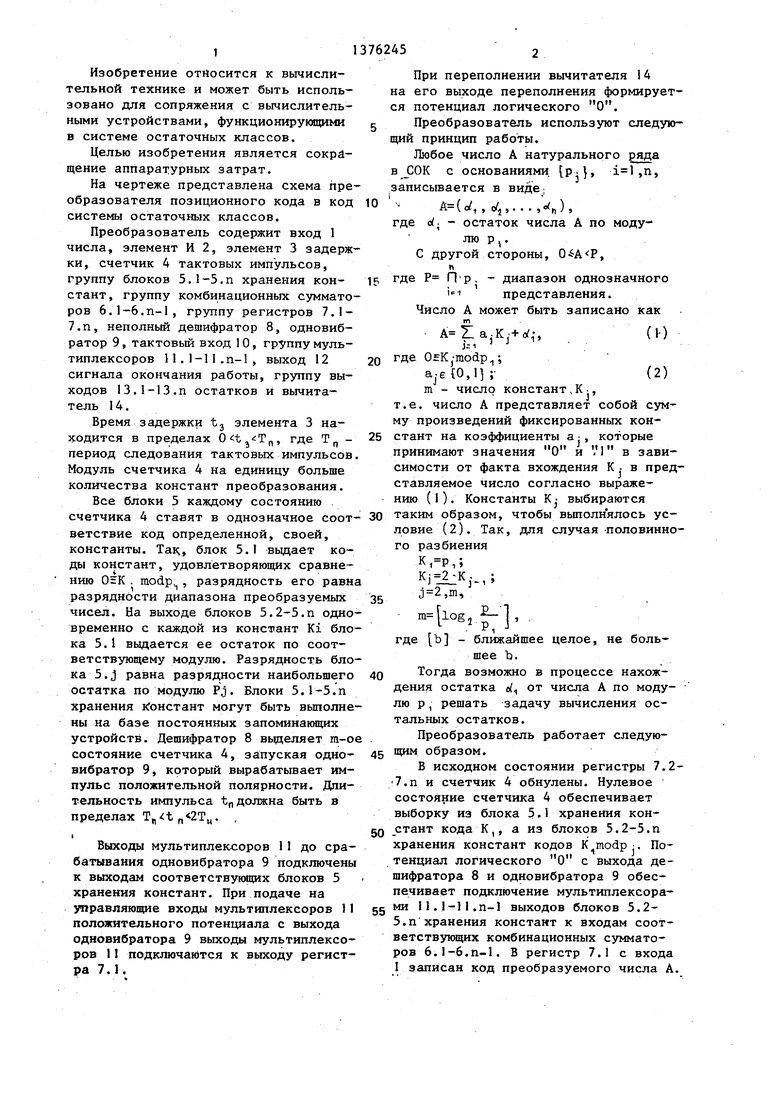

На чертеже представлена схема преобразователя позиционного кода в код CHCTeNbi остаточных классов.

Преобразователь содержит вход 1 чис;ла, элемент И 2, элемент 3 задержки, счетчик 4 тактовых импульсов, группу блоков 5.1-5.П хранения кон- стант, группу комбинационных сумматоров 6.1-6.П-1, группу регистров 7.1- 7.П, неполный дешифратор 8, одновиб- ратор 9, тактовый вход 10, группу мультиплексоров П.1-1I.п-1, выход 12 сигнала окончания работы, группу выходов 13,-13.п остатков и вычита- тель 14.

Время задержки tj элемента 3 находится в пределах , где Т - период следования тактовых импульсов Модуль счетчика 4 на единицу больше количества констант преобразования.

Все блоки 5 каждому состоянию счетчика 4 ставят в однозначное соответствие код определенной, своей, константы. Так, блок 5.1 выдает коды констант, удовлетворяющих сравнению . modp, разрядность его равн разрядности диапазона преобразуемых чисел. На выходе блоков 5.2-5.П одновременно с каждой из констант Ki блока 5. 1 выдается ее остаток по соответствующему модулю. Разрядность блока 5. j равна разрядности наибольшего остатка по мрдулю Рj. Блоки 5.1-5.П хранения кГонстант могут быть вьшолне ны на базе постоянных запоминающих устройств. Дешифратор 8 вьщеляет т-о состояние счетчика 4, запуская одно- вибратор 9, который вырабатывает импульс положительной полярности. Длительность импульса tnдолжна быть в пределах . ,

Выходы мультиплексоров М до срабатывания одновибратора 9 подключены к выходам соответствукйцих блоков 5 хранения констант. Прн подаче на управляющие входы мультиплексоров 11 положительного потенциала с выхода одновибратора 9 выходы мультиплексоров II подключаются к выходу регистра 7.1.

При переполнении вычитателя I4 на его выходе переполнения формируется потенциал логического О.

Преобразователь используют следзто- щий принцип работы.

Любое число А натурального ряда в СОК с основаниями, (р-), ,п, записывается в виде;

А(У, , (/J,. . , ,, где о. - остаток числа А по модулю р,.

С другой стороны, .Р,

h

где Р П р. - диапазон однозначного

представления. Число А может быть записано как

5

0

.К.+ ,

i:i

где ОгКmodp ;

0

5

0

5

(1-) (2)

ajeCO,);m - число констант,К , т.е. число А представляет собой сумму произведений фиксированных констант на коэффициенты а, которые принимают значения О и Vl в зависимости от факта вхождения К - в представляемое число согласно выражению (1). Константы К- выбираются таким образом, чтобы выполнялось условие (2). Так, для случая половинного разбиения

к,Р,;

.

к

,m, b

мPI

где IbJ - ближашшее целое, не большее Ъ.

Тогда возможно в процессе нахождения остатка е, от числа А по модулю р, решать задачу вычисления остальных остатков.

Преобразователь работает следующим образом.

В исходном состоянии регистры 7 7.П и счетчик 4 обнулены. Нулевое состояние счетчика 4 обеспечивает выборку из блока 5.1 хранения кон2

стант кода К,, а из блоков 5.2-5.П хранения констант кодов K modp:. Потенциал логического О с выхода дешифратора 8 и одновибратора 9 обеспечивает подключение мультиплексорами 11.1-11.п-1 выходов блоков 5.2- 5.п хранения констант к входам соответствующих комбинационных сумматоров 6.1-6.п-1. В регистр 7.1 с входа 1 записан код преобразуемого числа А.

С началом работы на вход 10 преобразователя начинают поступать тактовые импульсы. Знак разности А-К, кодов преобразуемого числа и первой константы, поступающих с блока 5,1 хранения констант и регистра 7.1 на вычитатель 14, определяет потенциал на выходе переполнения вычитателя 14. Если разность положительна, то на ВЫходе переполнения вычитателя 14. Если разность положительнй, то на выходе переполнения присутствуют потенциал логической 1, что обеспечивает прохождение тактового.импульса на тактовые входы регистров 7.1-7.П, а следовательно, запись в них результатов суммирования по модулю. В случае, когда разность отрицательна, уровень логического О блокирует прохождение тактового импульса через элемент И 2. Через время задержки tj тактовый импульс поступает на тактовый вход счетчика 4, который изменяет свое состояние и обеспечивает вы

борку констант. Kj, Л из coответствующих блоков 5 хранения констант. Далее процесс преобразования происходит указанным образом, пока по т-му импульсу не будет использована последняя константа К и ее остаточное представление по остальным, кроме первого, модулям. При этом в регистре 7.1 находится код о/,, После га-го импульса на выходе блока 5.1 хранения констант присутствует нулевой код, кроме того, на выходе дешифратора 8 появляется потенциал

й 1, запускается одновиб- единичный потенциал с выхо- дС го посредством мультиплек.l-ll.n-l подключает выход 7.1 к первым входам комбисумматоров 6.1-6.П-1. При ыходе этих сумматоров форми- д соединены тинные значения of,-о и мпульс записывает их в ре.2-7.п. После чего одновибра- еходит в нулевое состояние, 12 преобразователя форми- ,Q сигнал окончания работы, по ронту которого прекращается ние тактовых импульсов на преобразователя.

Форму Преобр в код сис содержащи маторов, блоков хр ход i-ro группы (1 оснований входом (i ход котор го слагае сумматора группы яв татков пр чающи кращения держит гр татель, э счетчик т дешифрато тактовьй нен с пер рез элеме входом сч выход кот входами группы и тора, вых дом однов ляется вы работы пр управляющ группы, в входами в вующих ко группы, в соединен го регист соединен тателя и с входами му ды блоков

вычитаемог информацио ров группы полнения в ственно с вого регис дом элемен динен с вх регистров

Q 5

0

5

0

5

С соединены Q

Формула изобретения Преобразователь позиционного кода в код системы остаточных классов, содержащий группу комбинационных сумматоров, группу регистров и группу блоков хранения констант, причем выход i-ro комбинационного сумматора группы ( ,...,п-1 ; п - количество оснований) соединен с информационным входом (i+l)-ro регистра группы, выход которого соединен с входом первого слагаемого i-ro комбинационного сумматора группы, выходы регистров группы являются группой выходов остатков преобразователя, отличающийся тем, что,с целью сокращения аппаратурных затрат, он содержит группу мультиплексоров, вычитатель, элемент И, элемент задержки, счетчик тактовых импульсов, неполный дешифратор и одновибратор, причем тактовьй вход преобразователя соединен с первым входом элемента И и через элемент задержки - со счетным входом счетчика тактовых импульсов, выход которого соединен с адресными входами блоков хранения констант группы и с входом неполного депшфра- тора, выход которого со.единен с входом одновибратора, выход которого является выходом сигнала окончания работы преобразоват.еля и соединен с управляющими входами мультиплексоров группы, выходы которых соединены с входами вторых слагаемых соответствующих комбинационных сумматоров группы, вход числа преобразователя соединен с установочным входом первого регистра группы, выход которого соединен с входом уменьшаемого вычитателя и с первьми информационными входами мультиплексоров группы, выходы блоков хранения констант группы

соответственно с входом вычитаемого вычитателя и с вторыми информационными входами мультиплексоров группы, выходы разности и переполнения вычитателя соединен соответственно с информационным входом первого регистра группы и с вторым входом элемента И, выход которого соединен с входами разрешения приема регистров группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1735856A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ СТЕПЕНИ ЗАГРУЗКИ КАНАЛОВ В СИСТЕМАХ С ДРЕВОВИДНОЙ ТОПОЛОГИЧЕСКОЙ ОРГАНИЗАЦИЕЙ ПРИ НАПРАВЛЕННОЙ ПЕРЕДАЧЕ ИНФОРМАЦИИ | 2011 |

|

RU2451334C1 |

| Многоканальная микропрограммная управляющая система | 1985 |

|

SU1280628A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Преобразователь модулярного кода в двоичный код | 1984 |

|

SU1238244A1 |

| Преобразователь позиционного кода в модулярный код | 1987 |

|

SU1460772A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения с вычислительными устройствами, функционирующими в системе остаточных классов. Целью изобретения является сокращение аппаратурных затрат. Для этого преобразователь позиционного кода в код системы остаточных классов, содержащий группу блоков 5.1- 5.П хранения констант, группу комбинационных сумматоров 6.1-6.П-1, группу регистров 7. 1-7.П , соде1)жит элемент И 2, элемент 3 задержки, счетчик 4 тактовых импульсов, неполный дешифратор 8, одновибратор 9, группу мультиплексоров 11.1-11.п-1 вычита- тель 14 с соответствующими связями, ил. у i (Л со о ю 4 СП

| Преобразователь позиционных кодов в код (сок) системы остаточных классов | 1976 |

|

SU601688A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1980 |

|

SU959062A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-02-23—Публикация

1986-08-15—Подача