Изобретение относится к вычислительной технике и может быть использовано для сопряжения со спецвычислителями, функционирующими в модулярном коде, в блоках контроля по модулю.

Цель изобретения - повышение быстродействия .

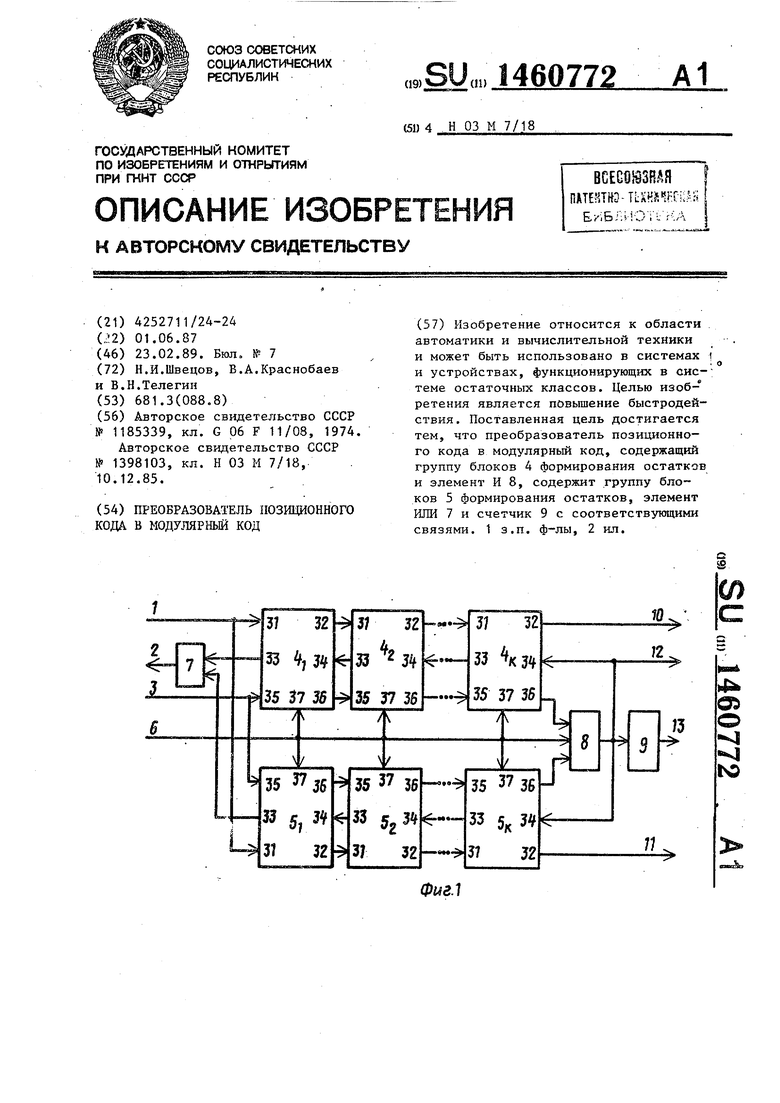

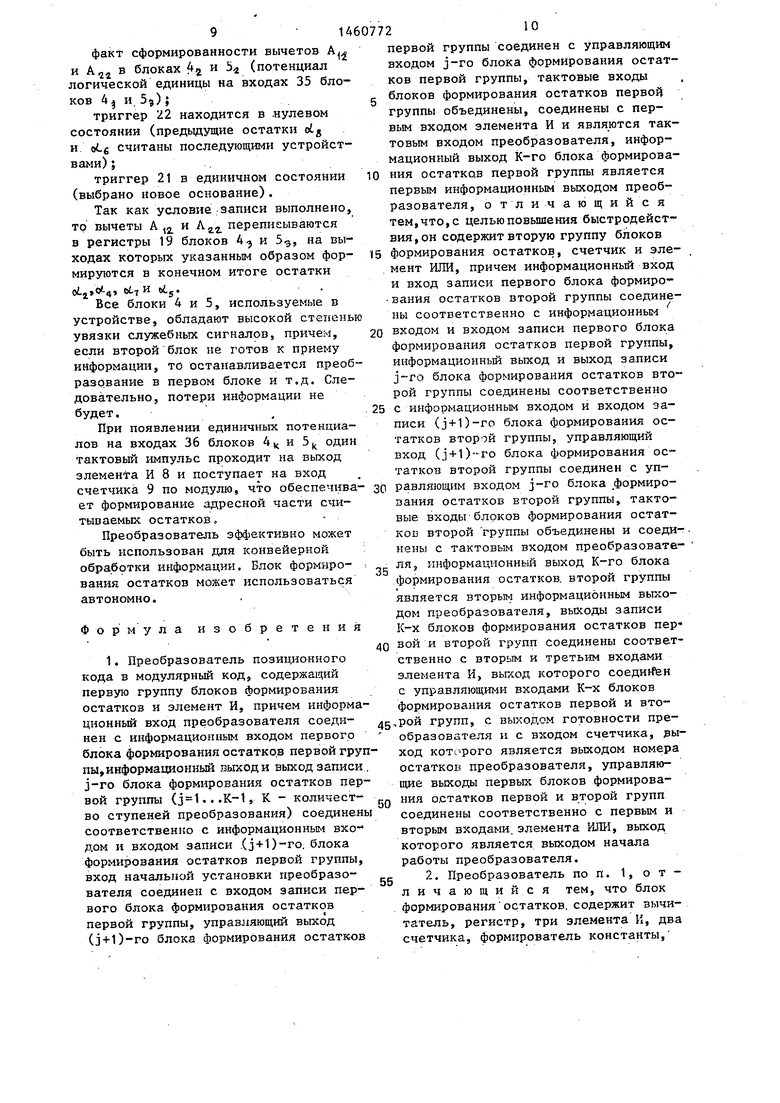

На фиг. 1 приведена схема преобразователя позиционного кода в моду- лярный код; на фиг. 2 - функциональная схема блока формирования остатков

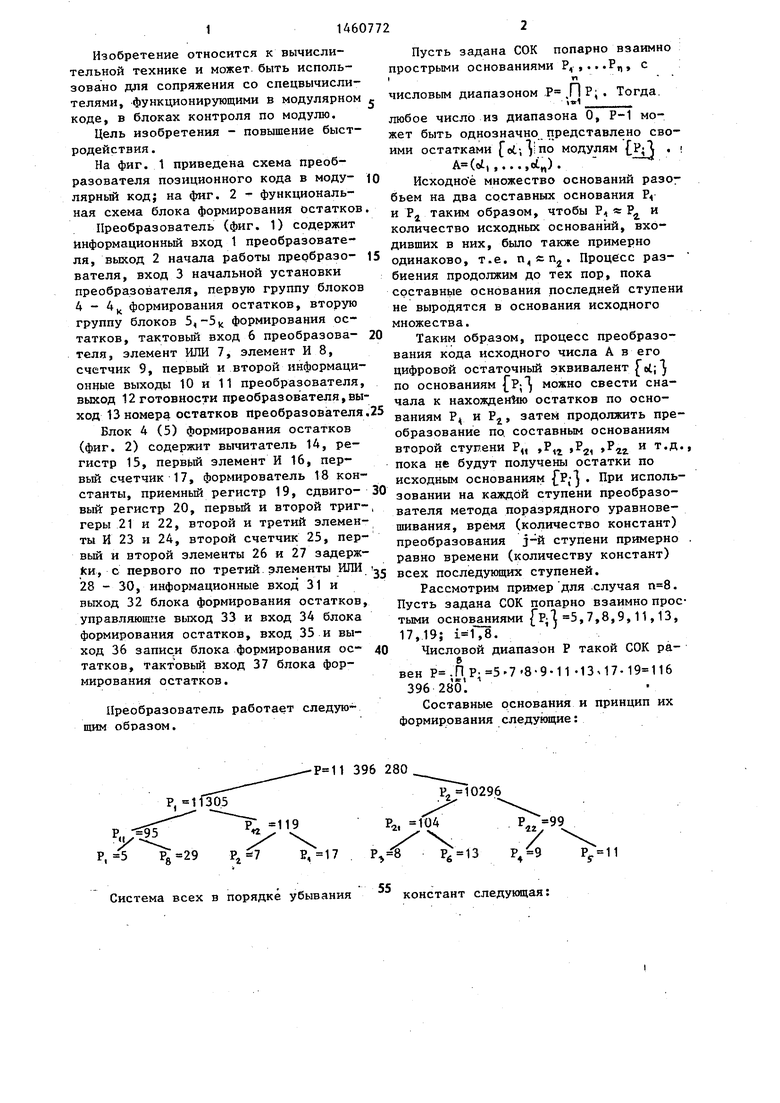

Преобразователь (фиг. 1) содержит информационный вход 1 преобразователя, выход 2 начала работы прербразо- вателя, вход 3 начальной установки преобразователя, первую группу блоков А - 4 формирования остатков, вторую группу блоков 5,-5 к формирования остатков, тактовьй вход 6 преобразова- теля, элемент ИЛИ 7, элемент И 8, счетчик 9, первый и второй информационные выходы 10 и 11 преобразователя, выход 12 готовности преобразователя,выход 13 номера остатков преобразователя

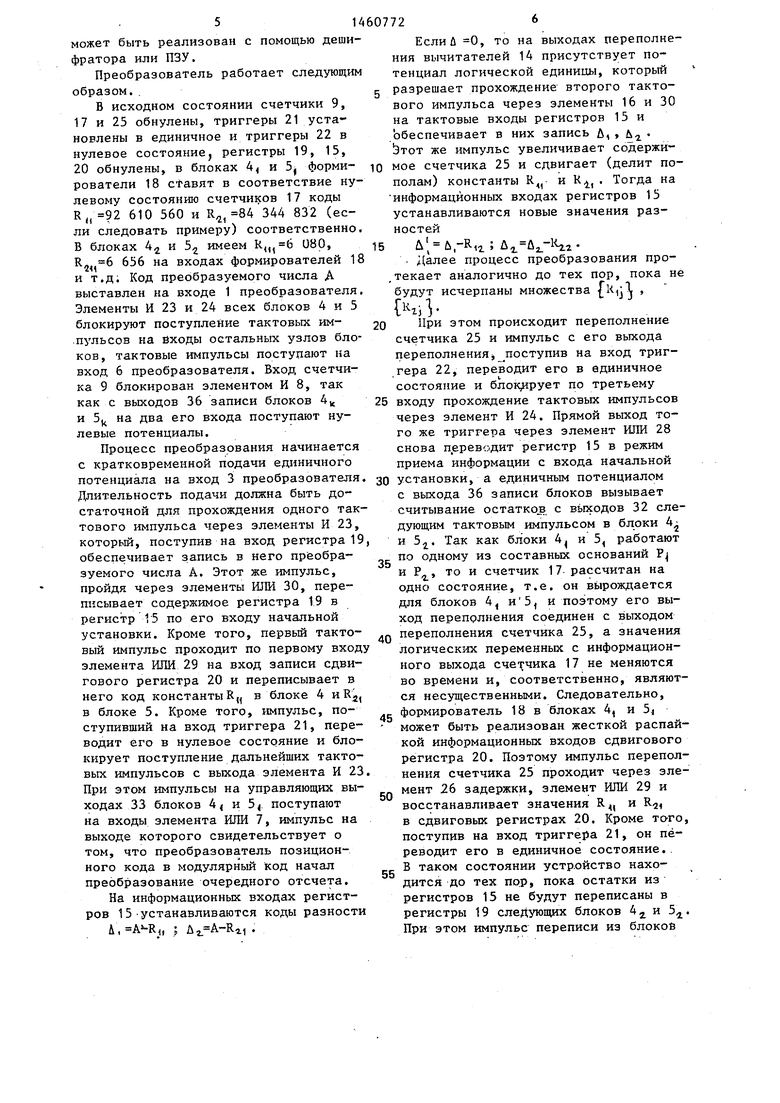

Блок 4 (5) формирования остатков (фиг. 2) содержит вычитатель 14, регистр 15, первый элемент И 16, первый счетчик 17, формирователь 18 константы, приемный регистр 19, сдвиго- вый регистр 20, первый и второй триггеры 21 и 22, второй и третий элементы И 23 и 24, второй счетчик 25, первый и второй элементы 26 и 27 задержки, с первого по третий элементы ИЛИ 28 - 30, информационные вход 31 и выход 32 блока формирования остатков управляющие выход 33 и вход 34 блока формирования остатков, вход 35 и выход 36 записи блока формирования ос- татков, тактовый вход 37 блока формирования остатков.

Преобразователь работает следую- щим образом.

Пусть задана СОК попарно взаимно

прострыми основаниями Р,, Р), с

I

числовым диапазоном ,Р ПР;. Тогда.

(«1

любое число из диапазона О, Р-1 может быть однозначно представлено своими остатками ot-,1 по модулям Р; .

A(oti ,... ,о1„) .

Исходно ё множество оснований разобьем на два составных основания Р и Pj таким образом, чтобы Pj Р количество исходных оснований, входивших в них, было также примерно одинаково, т.е. . Процесс разбиения продолжим до тех пор, пока составные основания последней ступени не выродятся в основания исходного множества.

Таким образом, процесс преобразования кода исходного числа А в его цифровой остаточный эквивалентное; по основаниям можно свести сначала к нахожден1во остатков по основаниям Р и PJ, продолжить преобразование по составным основаниям второй ступени Р„ ,Р, ,Р2, . т.д пока не будут получены остатки по исходным основаниям . При использовании на каждой ступени преобразователя метода поразрядного уравновешивания, время (количество констант) преобразования j-й ступени примерно равно времени (количеству констант) всех последующих ступеней.

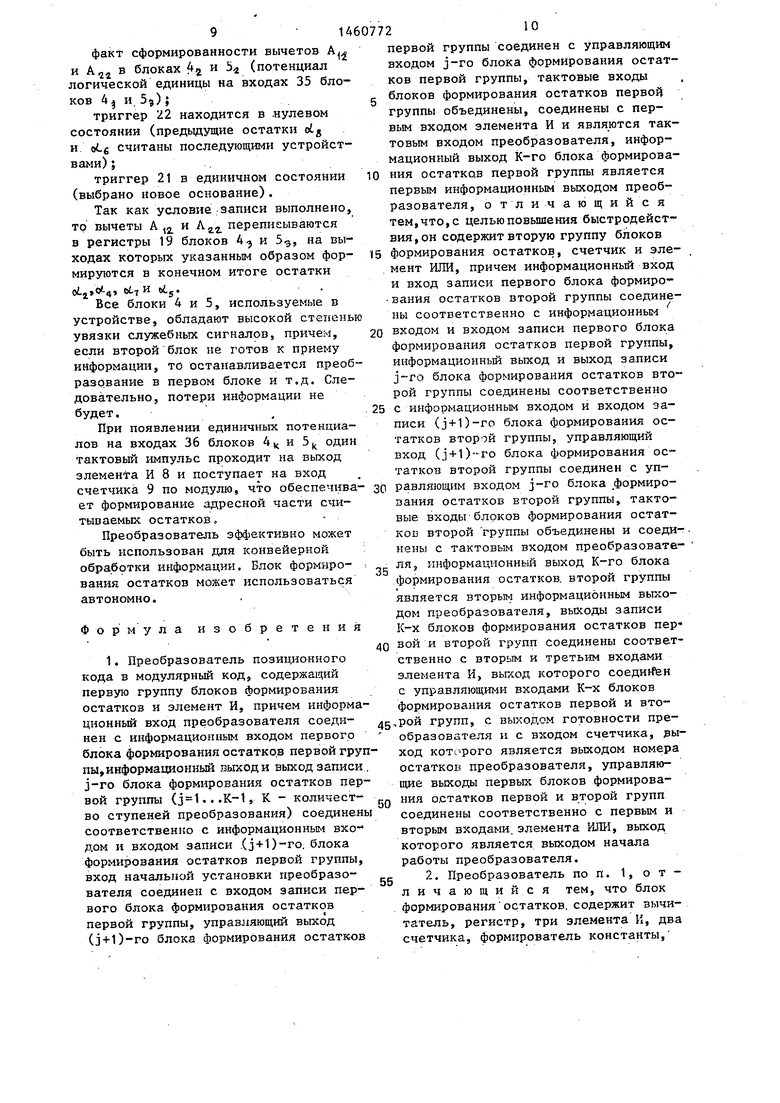

Рассмотрим пример для случая . Пусть задана СОК попарно взаимно простыми основа-ниями {Р; 5,7,8,9,11,13, 17,19; ,8.

Числовой диапазон Р такой СОК равен Р; 5-7 8-9-11 .13 17-19 116 396 280.

Составные основания и принцип их формирования следующие:

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения чисел в модулярном коде | 1985 |

|

SU1256013A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1236617A1 |

| Преобразователь модулярного кода в двоичный код | 1984 |

|

SU1238244A1 |

| Преобразователь кода системы остаточных классов в двоичный код | 1983 |

|

SU1133669A1 |

| Преобразователь позиционного кода в код системы остаточных классов | 1986 |

|

SU1376245A1 |

| Устройство для преобразования непозиционного кода в позиционный код | 1986 |

|

SU1410281A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1987 |

|

SU1587503A1 |

| Преобразователь кода | 1989 |

|

SU1619401A1 |

| Преобразователь непозиционного кода в двоичный код | 1982 |

|

SU1083179A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в системах и устройствах, функционирующих в сие-; теме остаточных классов. Целью изобретения является повышение быстродействия . Поставленная цель достигается тем, что преобразователь позиционного кода в модулярный код, содержащий группу блоков 4 формирования остатков и элемент И 8, содержит группу блоков 5 формирования остатков, элемент ИЛИ 7 и счетчик 9 с соответствующими связями. 1 з.п. ф-лы, 2 ил.

396 280

Р, 4 Р Р,17 Р, 8

Система всех в порядке убывания

Р2 10296

55

констант следующая:

7 616

3 808

1 904

952

476

238

119

fR,,, 76 R,,, 112 fR,,68 R,, 64 ,,,52 к„, 72 |н,,,88

Схематичное представление состав-55 честно последовательно соединенных ных оснований и соответствующих им блоков 4 и 5 равно трем, констант одновременно поясняет прин- Формирователь 18 константы по зна- цип и процесс преобразования позици- рению, поступившему на его вход, онного кода в модулярный код. Коли- . формирует код наибольшей константы и

может быть реализован с помощью дешифратора или ПЗУ.

Преобразователь работает следующим

образом..

В исходном состоянии счетчики 9, 17 и 25 обнулены, триггеры 21 установлены в единичное и триггеры 22 в нулевое состояние, регистры 19, 15, 20 обнулены, в блоках 4 и 5 форми- рователи 18 ставят в соответствие нулевому состоянию счетчиков 17 коды R,,92 610 560 и R, 84 344 832 (если следовать примеру) соответственно. В блоках 4 и 5 имеем К„,6 080, 656 на входах формирователей 18 и т.д. Код преобразуемого числа Д выставлен на входе 1 преобразователя. Элементы И 23 и 24 всех блоков 4 и 5 блокируют поступлейие тактовых им- .пульсов на йходы остальных узлов блоков, тактовые импульсы поступают на вход 6 преобразователя. Вход счетчика 9 блокирован элементом И 8, так как с выходов 36 записи блоков 4 и 5ц на два его входа поступают нулевые потенциалы.

Процесс преобразования начинается с кратковременной подачи единичного потенциала на вход 3 преобразователя Длительность подачи должна быть достаточной для прохождения одного тактового импульса через элементы И 23, который, поступив на вход регистра 19 обеспечивает запись в него преобразуемого числа А. Этот же импульс, пройдя через элементы ШШ 30, переписывает содержимое регистра 19 в регистр 15 по его входу начальной установки. Кроме того, первый тактовый импульс проходит по первому вход элемента ИЛИ 29 на вход записи сдвигового регистра 20 и переписывает в него код константы R,, в блоке 4 иК, в блоке 5. Кроме того, импульс, поступивший на вход триггера 21, переводит его в нулевое состояние и блокирует поступление дальнейших тактовых импульсов с выхода элемента И 23 При этом импульсы на управляющих выходах 33 блоков 4| и 5 поступают на входы элемента ИЛИ 7, импульс на выходе которого свидетельствует о том, что преобразователь позиционного кода в модулярный код начал преобразование очередного отсчета.

На информационных входах регистров 15 Устанавливаются коды разности А, ,, ; Д А-Кг1 .

0

Еслий 0, то на выходах переполнения вычитателей 14 присутствует потенциал логической единицы, который разрешает прохождение второго тактового импульса через элементы 16 и 30 на тактовые входы регистров 15 и обеспечивает в них запись Л, , & . 1Этот же импульс увеличивает содержимое счетчика 25 и сдвигает (делит пополам) константы R, и К, . Тогда на информационных входах регистров 15 устанавливаются новые значения разностей

,-RII; .-1Чг- . Далее процесс преобразования протекает аналогично до тех пор, пока не будут исчерпаны множества

Г 1- J J

(,

При этом происходит переполнение

счетчика 25 и импульс с его выхода переполнения,поступив на вход триггера 22, переводит его в единичное состояние и по третьему

5 входу прохождение тактовых импульсов через элемент И 24. Прямой выход того же триггера через элемент ИЛИ 28 снова п ереводит регистр 15 в режим приема информации с входа начальной

0 установки, а единичньм потенциалом с выхода 36 записи блоков вызывает считывание остатков с вькодов 32 следующим тактовым импульсом в блоки 4 и 52. Так как блоки 4 и 5, работают по одному из составных оснований Р и Р , то и счетчик 17 рассчитан на одно состояние, т.е. он вырождается для блоков 4, и 5, и поэтому его выход переполнения соединен с выходом

.Q переполнения счетчика 25, а значения логических переменных с информационного выхода 17 не меняются во времени и, соответственно, являются несущественными. Следовательно, формирователь 18 в блоках 4, и 5 может быть реализован жесткой распайкой информационных входов сдвигового регистра 20. Поэтому импульс переполнения счетчика 25 проходит через элемент 26 задержки, элемент ИЛИ 29 и

50

55

восстанавливает значения R д, и R, в сдвиговых регистрах 20. Кроме то-го, поступив на вход триггера 21, он переводит его в единичное состояние.. В таком состоянии устройство находится до тех пор, пока остатки из регистров 15 не будут переписаны в регистры 19 следующих блоков 42 и 5. При этом импульс переписи из блоков

5, по управляющему входу 34 по- формирует адрес остатков w;, н 9

ступает в блоки 4 и 5, , переводит триггер 22 в нулевое состояние, единичный потенциал с инверсного выхода которого разблокирует элементы И 24 и 23. Одновременно в регистре 15 восстанавливается значение кода числа А что несущественно для блоков 4 , и 5,, которые готовы к приему очередного числа А для последующего преобразования, которое повторяет описанньш цикл работы.

Таким образом, позиционный код А из числовсй-о диапазона Р сначала параллельно и независимо преобразует

ся в вычеты по основаниям Р, и Р блоками 4| и 5. На это требуется 14 циклов работы. После того, как вычеты Ai

и А по основаниям Р,

и Р, бу-

дут сформированы в регистрах 15 блоков 4 и 5,, на выходах 36 этих блоков, и на входах 35 блоков 4 и 5 появляются потенциалы логической единицы, которые обеспечивают запись вычетов А и А в регистры 19 блоков 4j и 52, причем этот же импульс с выхода 33 блоков 4 и 5,2. поступает на вход 33 блоков 4 и 5,., устанавливает триггеры 22 этих блоков в нулевое состояние и тем самым подготавливает (обеспечивает) прием нового значения А позиционного кода в регистры 19 блоков и 5 . Если на входе 35 уже -присутствует единичный потенциал, то первый же тактовый импульс его входа 37 обеспечивает запись ,в регистре 19, а если нет, то блоки А и 5 будут ожидать разрешение на прием с входа 35 нового значения А по входу 31.

Наибольшая константа из fi,, и блоков и 5 соответственно заносится в сдвиговый регистр 20 одновременно с записью в регистр 19

значений А и А импульсом п первого входа элемента ИЛИ 29. После того, как упомянутые множества констант будут исчерпаны и сформированы вычеты А, и Aj, ло основаниям Р 95; .Р, 104, эти вычеты описанным образом будут переписаны в регистры 19 блоков 4 и 5,, где сразу же начнут преобразовываться в вычеты по основаниям Р, 5 и .

Преобразование по основаниям Р| и Р заканчивается одновременно ( (фиг. 2) и очередной тактовый импульс проходит через элемент И 8,

и импульс на выходе 21 преобразователя, по которому будут считаны остатки и odj с информационных выходов 10 и 11 устройства. Этот же импульс в блоках , и 5 5 устанавливает триггеры 22 в нулевое состояние, что обеспечивает перепись вычетов А, и AJ из регистров 19 в регистры 15 для последующего преобразования по основаниям Р 19 и соответственно. Тактовый импульс с выхода эле0

мента И 24, кроме того, сбрасывает 5 счетчик 23, импульс переполнения с выхода которого переводит счетчик 17 в следующее состояние, код которого выбирает из формирователя 18 коды констант (2| 2121 52 которые спустя время задержки элемента 26 записываются в сдвиговые регистры 20. Процесс формирования остатков осутцествляется описанным образом, при этом процесс формирования множе- 5 ства {К(,2е производится посредством сдвигов в регистрах 20. Различие в числе констант в блоках 4з и 5j, обусловленное неравномерностью распределения простых чисел среди 0 натуральных, может быть учтено либо увеличением числа используемых констант, как показано- выше звездочками (), т.е. вводятся холостые такты, либо усложнением алгоритма функционирования счетчиков 25. Так, для рассматриваемого примера блоки 4, и 5 тратят по четыре цикла своей работы на обработку одного отсчета А. Модуль счета счетчика 25 Q блока 4 должен принимать по циклам значения 5,3,5,3, а в блоке 5, - 4, 3,4,4.

После получения остатков oio и otic

о ь

счетчик тактов переполняется вторично, что вызывает переполнение счетчика 17, импульс с выхода переполнения которого устанавливает триггер 21 в единичное состояние. Так как импульс переполнения появляется на каждое второе состояние счетчика, то реально он подключен к второму его разряду. Модуль счета.счетчика 17 равен , где К - номер ступени

преобразования.

Условием записи в регистры 19

блоков 4, и 5, вычетов А„ и А

ia

22

является одновременное выполнение ;следующего:

факт сформированности вычетов А и А,2 в блоках 2 и Ь-г (потенциал логической единицы на входах 35 блоков 4 и 5});

триггер 22 находится в .нулевом состоянии (предьщутдие остатки oig и. oi-e считаны последующими устройствами) ;

триггер 21 в единичном состоянии (выбрано новое основание).

Так как условие записи выполнено, то вычеты А ,2. и гг переписываются в регистры 19 блоков 4 и 5, на выходах которых указанным образом формируются в конечном итоге остатки oJ.j,o(-4, Ы-тИ tij.

Все блоки 4 и 5, используемые в устройстве, обладают высокой стетшнью увязки служебных сигналов, причем, если второй блок не готов к приему информации, то останавливается преобразование в первом блоке и т.д. Следовательно, потери информации не будет.

При появлении единичных потенциалов на входах 36 блоков 4 и 5, один тактовый импульс проходит на вьпсод элемента И 8 и поступает на вход

первой группы соединен с управляющим входом j-ro блока формирования остатков первой группы, тактовые входы блоков формирования остатков первой группы объединены, соединены с первым входом элемента И и являются тактовым входом преобразователя, информационный выход К-го блока формирова- 10 ния остатков первой группы является первым информационным выходом преобразователя.

тли чающийся

тем, что, с целью повышения быстродействия, он содержит вторую группу блоков

15 формирования остатков, счетчик и элемент ИЛИ, причем информационный вход и вход записи первого блока формиро- вания остатков второй группы соединены соответственно с информационным

20 входом и входом записи первого блока формирования остатков первой группы, информационньй выход и выход записи j-ro блока формирования остатков второй группы соединены соответственно

.25 с информационным входом и входом записи (j+1)-ro блока формирования остатков второй группы, управляющий вход (j+1)ro блока формирования остатков второй группы соединен с упi3лсгасп 1 о. л v «1 HWV-1J i(.- - t-vf , л д.

счетчика 9 по модулю, что обеспечива- ЗО равляющим входом j-ro блока .формиро35

ет формирование адресной части считываемых остатков.

Преобразователь эффективно может быть использован для конвейерной обработки информации. Блок формирования остатков может использоваться автономно.

Формула изобретения

зания остатков второй группы, тактовые входы блоков формирования остатков второй группы объединены и соеди нены с тактовым входом преобразовате ля, информационный выход К-го блока формирования остатков, второй группы является вторым информационным выходом преобразователя, выходы записи К-х блоков формирования остатков пер 40 вой и второй групп соединены соответ ственно с вторым и третьим входами элемента И, выход которого соеди1 ен с управляющими входами К-х блоков формирования остатков первой и вто- 45,рой групп, с выходом готовности преобразователя и с входом счетчика, зы ход котс рого является выходом номера остатков преобразователя, управляющие выходы первых блоков формирования остатков первой и второй групп соединены соответственно с первым и вторым входами,элемента ИЛИ, выход которого является вьрсодом начала работы преобразователя.

первой группы соединен с управляющим входом j-ro блока формирования остатков первой группы, тактовые входы блоков формирования остатков первой группы объединены, соединены с первым входом элемента И и являются тактовым входом преобразователя, информационный выход К-го блока формирова- 0 ния остатков первой группы является первым информационным выходом преобразователя.

тли чающийся

тем, что, с целью повышения быстродействия, он содержит вторую группу блоков

5 формирования остатков, счетчик и эле . мент ИЛИ, причем информационный вход и вход записи первого блока формиро- вания остатков второй группы соединены соответственно с информационным

0 входом и входом записи первого блока формирования остатков первой группы, информационньй выход и выход записи j-ro блока формирования остатков второй группы соединены соответственно

25 с информационным входом и входом записи (j+1)-ro блока формирования остатков второй группы, управляющий вход (j+1)ro блока формирования остатков второй группы соединен с уп л д.

О равляющим входом j-ro блока .формиро5

зания остатков второй группы, тактовые входы блоков формирования остатков второй группы объединены и соеди- нены с тактовым входом преобразователя, информационный выход К-го блока формирования остатков, второй группы является вторым информационным выходом преобразователя, выходы записи К-х блоков формирования остатков пер- 0 вой и второй групп соединены соответственно с вторым и третьим входами элемента И, выход которого соеди1 ен с управляющими входами К-х блоков формирования остатков первой и вто- 45,рой групп, с выходом готовности преобразователя и с входом счетчика, зы- ход котс рого является выходом номера остатков преобразователя, управляющие выходы первых блоков формирования остатков первой и второй групп соединены соответственно с первым и вторым входами,элемента ИЛИ, выход которого является вьрсодом начала работы преобразователя.

55

1 1460772

приемный регистр, сдвиговый регистр, ,рого элемента И два триггера, два элемента задержки и три элемента ИЛИ, причем информационный вход блока формирования остатков соединен с информационным входом приемного регистра, выход которого соединен с установочным входом регистра, выход которого является инс первым входом

тр тьего элемента И, второй вход которого соединен с тактовым входом блока формирования остатков, управляющий выход которого соединен с третьим входом третьего элемента ИЛ и с входом установки в О второго триггера, инверсный выход которого

формационным выходом блока формирова- ю соединен с четвертым входом второго

ния остатков и соединен с входом уменьшаемого вычитателя, выход разности которого соединей с информационным входом регистра, вход разрешения записиокоторого соединен с выходом первого элемента ИЛИ, первый вход которого соединен с первым входом второго элемента И и является входом записи блока формирования остатков, управляющий выход которого соединен с входом разрешения записи приемного регистра, с первыми входами второго и третьего элементов ИЛИ, с входом установки в О первого триггера и с выходом второго элемента И, второй вход которого соединен с тактовым входом блока формирования остатков, выход переполнения вычитателя соединен с первым входом первого элемента И, выход которого соединен с вто- рб1м входом третьего элемента ИЛИ, выход которого соединен с входом синхронизации регистра, прямой и инверсный выходы первого триггера соединены соответственно с третьим входом вто,рого элемента И

с первым входом

тр тьего элемента И, второй вход которого соединен с тактовым входом блока формирования остатков, управляющий выход которого соединен с третьим входом третьего элемента ИЛИ и с входом установки в О второго триггера, инверсный выход которого

соединен с четвертым входом второго

элемента И и с третьим входом третьего элемента И, выход которого соединен с входом второго счетчика,с вторым входом первого элемента И и

через второй элемент задержки - с входом разрешения сдвига сдвигового регистра, выход которого соединен с входом вычитаемого вычитателя, выход второго счетчика соединен с входом

установки в 1 второго триггера, с входом первого счетчика и через первый элемент задержки - с вторьм входом второго элемента ИЛИ, выход которого соединен с входом разрешения записи сдвигового регистра, информационный вход которого соединен с выходом формирователя константы, вход которого, соединен с информационным выходом первого счетчика, выход

переполнения которого соединен с входом установки в 1 первого триггера, прямой, выход второго триггера соединен с вторым входом первого элемента ИЛИ и является г выходом записи блока формирования остатков.

51

Фиг. 2

37

| Устройство для вычисления вычетов числа по двум произвольным модулям | 1984 |

|

SU1185339A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь позиционного кода числа в модулярный код | 1985 |

|

SU1398103A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-02-23—Публикация

1987-06-01—Подача