Изобретение относится к вычислительной технике и может быть применено при создании устройств обработки информации, использующих представление чисел в системе остаточных классов (модулярные коды).

Цель изобретения - расширение . функциональных возможностей путем обеспечения смены системы оснований в процессе работы.

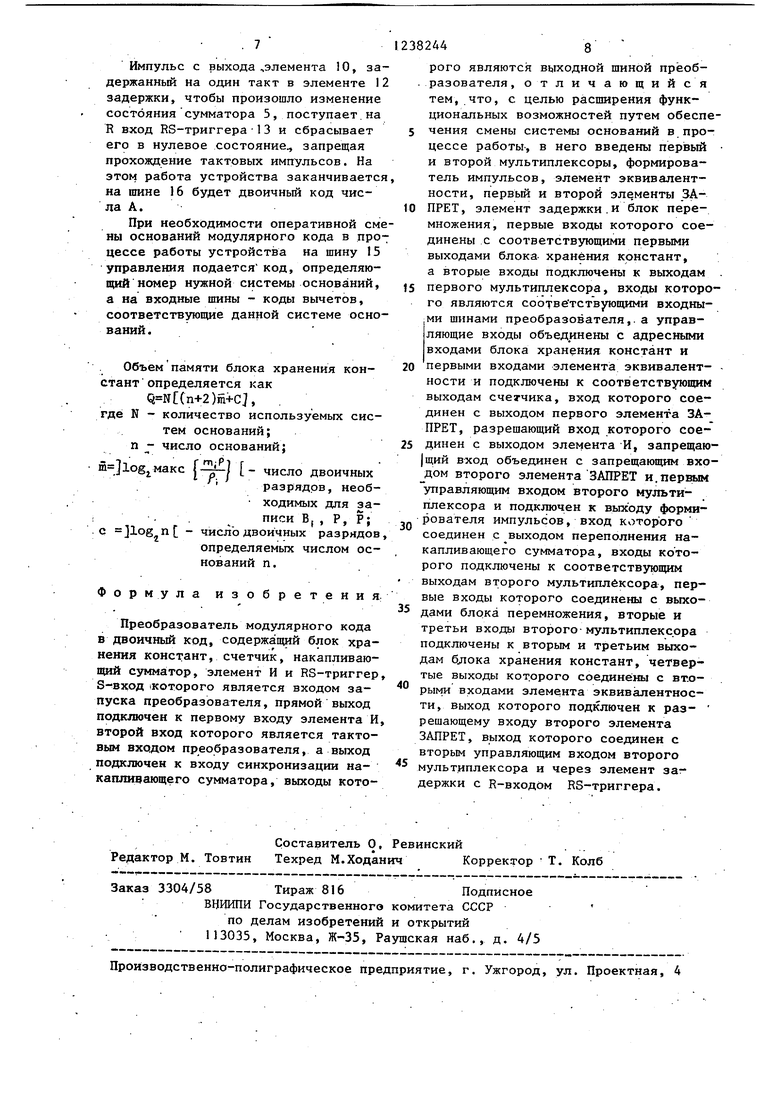

. На чертеже представлена функциональная схема преобразователя.

Преобразователь модулярного кода в двоичный код содержит блок 1 хранения констант, блок 2 перемножения,

)первый, и второй мультиплексоры 3 и 4 накапливающий сумматор 5, формирователь 6 импульсов, элемент 7 эквивалентности, счетчик 8, первый У и второй 10 элементы ЗАПРЕТ, элемент 11 И, элемент 12 задержки и НЗ-триг- гер 13. Входы первого мультиплексора 3 являются соответствующими входными шинами 14 устройства, а входы блока I хранения констант являются шиной 15 управления устройства. Первые выходы блока 1 подключены к первым входам блока 2 перемножения, вторые входы которого соединены с

. соответствующими выходами первого мультиплексора 3, а выходы - с первыми входами второго мультиплексора 4, вторые и третьи входы которого подключены к вторым и третьим выходам блока 1 соотве.тственно. Выходы ёторого мультиплексора 4 соедине-

.ны с входами накапливающего сумматора 5, выходы которого являются выходной шиной 16 устройства, выход переполнения накапливающего сумматора 5 соединен с входом формирователя 6 импульсов, а вход синхронизации объе диненс разрешающим входом первого элемента ЗАПРЕТ 9 и подключен к выходу элемента 1.1-И., один вход которого является тактовым входом 17 устройства , а другой подключен к выходу RS-триггера 13, S-вход которого является входом 18 запуска уст- ройства, а -R-вход соединен с выходом элемента 12 задержки. Выход фО1рмирователя 6 импульсов подключён первому управляющему входу второго мультиплексора 4 и запрещающим входам элементов 9 и 10 ЗАПРЕТ. Выход элемента 9 соединен с входом счетчи- ка 8, выходы которого подключены к первым входам элемента 7 эквивалентности, управляющим входам первого

мультиплексора. 3 и адресным входам блока 1 хранения констант, четвертые выходы которого соединены с вторыми входами элемента 7 эквивалентности, выход которого подключен к разрешающему входу второго элемента 10 ЗАПРЕТ, выход которого соединен с вторым управляющим входом второго мультиплексора 4 и входом элемента 12 задержки.

В основе преобразователя лежат следующие соотношения.Преобразование числа А ведется по формуле

,- В;|р , (1)

1

где - вычет числа А по основа-

fi .Bj -J- 1 (modpj ) - ортонормиро i

ванный вектор, являющийся константой для выбранной системы оснований;

Р и Р; - диапазон представлени

- г

чисел, гте екрываемый системой оснований Я, .... ,/ .

Известно, что если есть модуль , то любое число С можно преобразовать как |С|р |С+Р1„ , если , j

где - дополнение диапазона Р до модуля М. С учетом этого выражение (1) мржно представить как

(c(;B;-br,.P), (2).

. ,1:1

Рде г. - число добавлений Р, которое выполняется до тех пор, пока Не выполнится условие

I. .,11 ot ;В, +Р| +Р|„ +.; .+Р)„чМ,

что означает отсутствие переполнения сумматора по модулю М. . V

Поскольку I (ot,Bj+ri Р)|„

I 1 на величину Р, то для получения в (2) необходимо прибавлять Р по модулю М, что эквивалентно вычитанию дополнения Р..

д . 55

50

Блок 1 хранения констант может быть вьтолнен на постоянном запоминающем устройстве, в котором записаны -коды совокупности констант (орто- нормированных векторов В,- , диапазона Р представления чисел, дополнения Р диапазона и числа п оснований системы) для N систем оснований модулярной арифметики. Выбор системы оснований определяется кодом номера системы

3 12382444

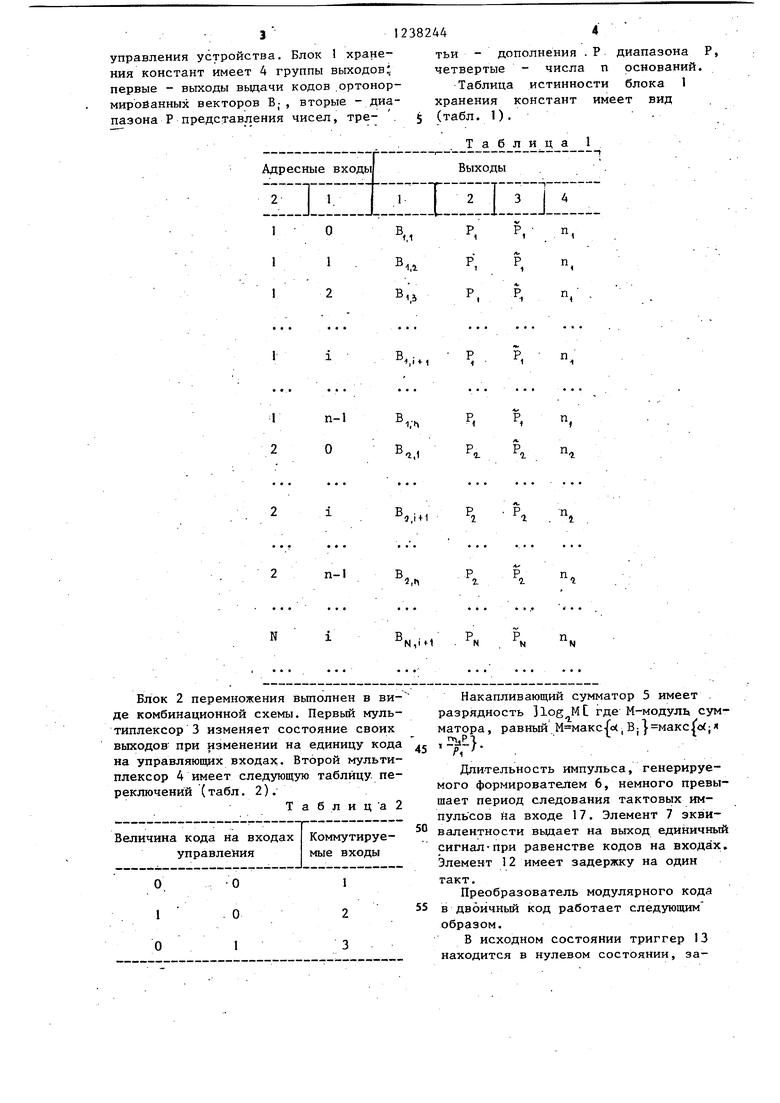

управления устройства. Блок хране- тьи - дополнения .Р диапазона Р, ния констант имеет 4 группы выходов:; четвертые - числа п оснований, первые - выходы вьщачи кодов .ортонор- Таблица истинности блока 1 миробанных векторов В; , вторые - диа- хранения констант имеет вид

пазонаР представления чисел, тре- .j (табл. 1)..

Таблица 1

О 1 2

лп-1В,.

О

2 . . -Ра .

п-1

N

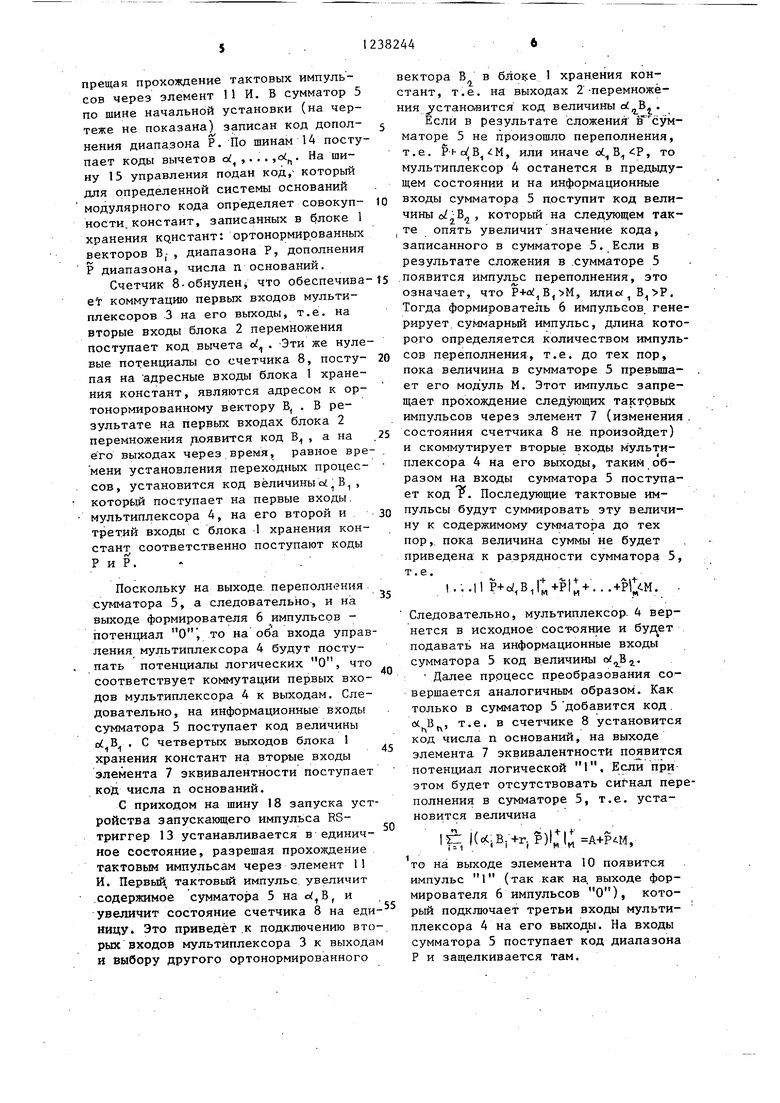

Блок 2 перемножения вьтолнен в ви- де комбинационной схемы. Первый мультиплексор 3 изменяет состояние своих выходов- при изменении на единицу кода на управляющих входах. Второй мультиплексор 4 имеет следующую таблицу, переключений (табл. 2).

Т а б л и ц а 2

Величина кода на входах управления

Коммутируемые входы

О

О

. о

3

В.

м

в

1Д

в

3

и,

Р

1

р. Р,

РГ Па

В

2,М

В

N,iH

П.

- Г/Накапливающий сумматор 5 имеет . разрядность 3log МС где М-модуль сумматора, равный М макс- о(|

/Г

Длительность импульса, генерируемого формирователем 6, немного превышает период следования тактовых импульсов на входе 17. Элемент 7 эквивалентности вьщает на выход единичный сигнал-при равенстве кодов на входах. Элемент 12 имеет задержку на один

такт.

Преобразователь модулярного кода в двоичный код работает следующим образом.

В исходном состоянии триггер 13 находится в нулевом состоянии, за

прещая прохождение тактовых импульсов через элемент 11 И, В сумматор 5 по шине начальной установки (на чертеже не показана) записан код допол-

v .нения диапазона Р. По шинам 14 поступает коды вычетов о ,. . . ,oi. На шину 15 управления подан код,- который для определенной системы оснований модулярного кода определяет совокуп- ности.констант, записанных в блоке 1 хранения KqHCTaHTt ортонормированных векторов В-, диапазона Р, дополнения Р диапазона, числа п оснований.

Счетчик 8-обнуленj что обеспечива et коммутацию первых входов мультиплексоров 3 на его выходы, т.е. на вторые входы блока 2 перемножения поступает код вычета о . Эти же нулевые потенциалы со счетчика 8, посту- пая на адресные входы блока 1 хранения констант, являются адресом к ор- тонормйрованному вектору В, . В результате на первых входах блока 2 перемножения доявится код В , а на его выходах через время, равное вре мени установления переходных процес- сов, установится код вёличиныЫ В , который поступает на первые входы. мультиплексора 4, на его второй и третий входы с блока 1 хранения констант соответственно поступают коды Р и Р. -

Поскольку на выходе, переполнения

сумматора 5, а следовательно, и на выходе формирователя 6 импульсов - потенциал , то на оба входа управления мультиплексора 4 будут поступать потенциалы логических О, что соответствует коммутации первых входов мультиплексора 4 к выходам. Следовательно, на информационные входы сумматора 5 поступает код величины о(В , С четвертых выходов блока 1 хранения констант на вторые входы элемента 7 эквивалентности поступает код числа п оснований.

С приходом на шину 18 запуска устройства запускающего импульса RS- триггер 13 устанавливается в единичное состояние, разрешая прохождение тактовым импульсам через элемент 1 И. Первьй тактовый импульс увеличит .содержимое сумматора 5 на , и увеличит состояние счетчика 8 на еди ницу. Это приведёт .к подключению вторых входов мультиплексора 3 к выхода и выбору другого ортонормированного

0

5 0 5 о

5

40

45

50

вектора В в блоке 1 хранения констант, т.е. на выходах 2 -перемножения устано/вится код величины °l.i

Если в результате сложения маторе 5 не произошло переполнения, т.е. &ho/B M, или иначе ot В Р, то мультиплексор 4 останется в предьщу- щем состоянии и на информационные входы сумматора 5 поступит код величины ot , который на следующем так- , те опять увеличит значение кода, записанного в сумматоре 5. Если в результате сложения в .сумматоре 5 .появится импульс переполнения, это означает, что P+oi,, Ш1ис(. Тогда формирователь 6 импульсов генерирует, суммарный импульс, длина которого определяется количеством импульсов переполнения, т.е. до тех пор, пока величина в сумматоре 5 превьппа- ет его модуль М. Этот импульс запрещает прохождение следующих тактовых импульсов через элемент 7 (изменения . состояния счетчика 8 не произойдет) и скоммутирует вторые входы мультиплексора 4 на его выходы, таким образом на входы сумматора 5 поступает код . Последующие тактовые импульсы будут суммировать эту величину к содержимому сумматора до тех пор,. пока величина суммы не будет приведена к разрядности сумматора 5,

,.-..11 р.о/.в,;.....Pl. .

Следовательно, мультиплексор. 4 вернется в исходное состояние и буллет подавать на информационные входы сумматора 5 код величины ,.

Далее процесс преобразования совершается аналогичным образом. Как только в сумматор 5 добавится код. ОС В, т.е. в счетчике 8 установится

h п .

КОД числа п оснований, на выходе элемента 7 эквивалентности появится потенциал логической 1, Если при этом будет отсутствовать сигнал переполнения в сумматоре 5, т.е. установится величина

(«iB.r,p)i;i;- A-hp.M,

о на выходе элемента 10 появится импульс 1 (так как на. выходе формирователя 6 импульсов О), который подключает третьи входы мультиплексора 4 на его выходы. На входы сумматора 5 поступает код диапазона Р и защелкивается там.

. 7

Импульс с выхода ,элемента 10, задержанный на один такт в элементе 12 задержки, чтобы произошло изменение состояния сумматора 5, поступает.на R вход RS-триггера13 и сбрасывает его в нулевое состояние запрещая прохождение тактовых импульсов. На этом работа устройства заканчивается на шине 16 будет двоичный код числа А .

При необходимости оперативной смены оснований модулярного кода в процессе работы устройства на шину 15 управления подается код, определяющий номер нужной системы оснований, а на входные шины - коды вычетов, соответствующие данной системе оснований.

Объем памяти блока хранения констант определяется как

(n+2)m+Cj,

где N - количество используемых систем оснований; п - число оснований;

,MaKC - число двоичных разрядов, необ- ходимых для за:. .ПИСИ В,, Р, Р;

С log п - число двоичных разрядов определяемых числом оснований п.

Формула изобретения.

Преобразователь модулярного кода в двоичный код, содержащий блок хранения констант, счетчик, накапливающий сумматор, элемент И и RS-триггер S-вход iKOTOporo является входом запуска преобразователя, прямой выход подключен к первому входу элемента И второй вход которого является тактовым входом преобразователя, а выход подключен к входу синхронизации накапливающего сумматора, выходы котоСоставитель О. Ревинский. .

Редактор М. Товтин Техред М.Ходанич Корректор Т. Колб

Заказ 3304/58 Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

0

5

0

0

382А48

рого являются выходной шиной прёоб- . разователя, отличающийся тем, что, с целью расширения функциональных возможностей путем обеспе- 5 чения смены системы оснований в процессе работы, в него введены первый и второй мультиплексоры, формирователь импульсов, элемент эквивалентности, первый и второй элементы ЗАПРЕТ, элемент задержки.и блок перемножения, первые входы которого соединены с соответствующими первыми выходами блока хранения констант, а вторые входы подключены к выходам первого мультиплексора, входы которого являются соотве тствующими входными шинами преобразователя,, а управляющие входы объединены с адресными входами блока хранения констант и первыми входами элемента эквивалентности и подключены к соответствующим выходам счетчика, вход которого соединен с выходом первого элемента ЗАПРЕТ, разрешающий вход которого соединен с выходом элемента И, запрещаю- )щий вход объединен с запрещающим вхо- дом второго элемента ЗАПРЕТ и.первым управляющим входом второго мультиплексора и подключен к выходу формирователя импульсов, вход которого соединен с выходом переполнения накапливающего сумматора, входы которого подключены к соответствующим выходам второго мультиплексора, первые входы которого соединены с выхо- 5 дами блока перемножения, вторые и третьи входы второго-мультиплексора подключены к вторым и третьим выходам блока хранения констант, четвертые выходы которого соединены с вторыми входами элемента эквивалентности, выход которого подключен к раз- решающему входу второго элемента ЗАПРЕТ, выход которого соединен с вторым управляющим входом второго мультиплексора и через элемент задержки с R-входом RS-триггера.

5

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения чисел в модулярном коде | 1985 |

|

SU1256013A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

| Преобразователь позиционного кода в модулярный код | 1987 |

|

SU1460772A1 |

| Устройство обнаружения и коррекции ошибки модулярного кода | 2017 |

|

RU2653257C1 |

| Устройство для определения позиционных характеристик непозиционного кода | 1985 |

|

SU1283948A1 |

| Устройство для преобразования чисел из позиционной системы счисления в модулярный код | 1985 |

|

SU1305870A1 |

| УСТРОЙСТВО ДЛЯ ОСНОВНОГО ДЕЛЕНИЯ МОДУЛЯРНЫХ ЧИСЕЛ | 2013 |

|

RU2559771C2 |

| Устройство для преобразования непозиционного кода в позиционный код | 1986 |

|

SU1410281A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1236617A1 |

Изобретение предназначено для применения в устройствах обработки информации, представленн.ой в виде вьгчетов в системе остаточных классов . Цель изобретения - расширение функциональных возможностей путем обес- смены системы -оснований в процес.се работы. Преобразователь содержит блок 1 хранения констант, блок 2 перемножения, два мультиплек.сора 3, 4, накапливающий сумматор 5, формирователь 6 импульсов, элемент 7 эквивалентности, счетчик 8, два элемента 9, 10 ЗАПРЕТ, элемент 11 И, элемент 12 задержки и RS-триггер 13. Выбор системы оснований производится подачей на входы блока 1 соответствующего кода. Каждый вычет умножается в блоке 2 на соответствующий орто- нормированный базис и суммируется с содержимым сумматора 5-, Если сумматор 5 не переполняется, то содержи-, мое счетчика 8 увеличивается на еди- ницу и на блок 2 поступает нозая пара сомножителей. При переполнении сумматора 5 формирователь 6 закроет элемент 9, останавливая счетчик 8, и переключит на входы сумматора 5 код дополнения диапазона данной системы оснований. Когда счетчик 8 досчитает до чирла оснований данной сие- темы, элёме нт ,/ эквивалентности .остановит работу преобразователя . 1 ил, 2 табл.(Л С ч % Mk Ч S СО 00 to 4 NU

| Устройство для перевода чисел из системы остаточных классов в полиадическую | 1977 |

|

SU605209A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь кода из системы остаточных классов в позиционный код | 1980 |

|

SU924695A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-15—Публикация

1984-11-05—Подача