Изобретение относится к вычислительной технике и может использоваться для отладки- многопроцессорных вычислительных систем.

Цель изобретения - расширение функциональных возможностей устройства за счет возможности контроля хода программы многопроцессорных систем,

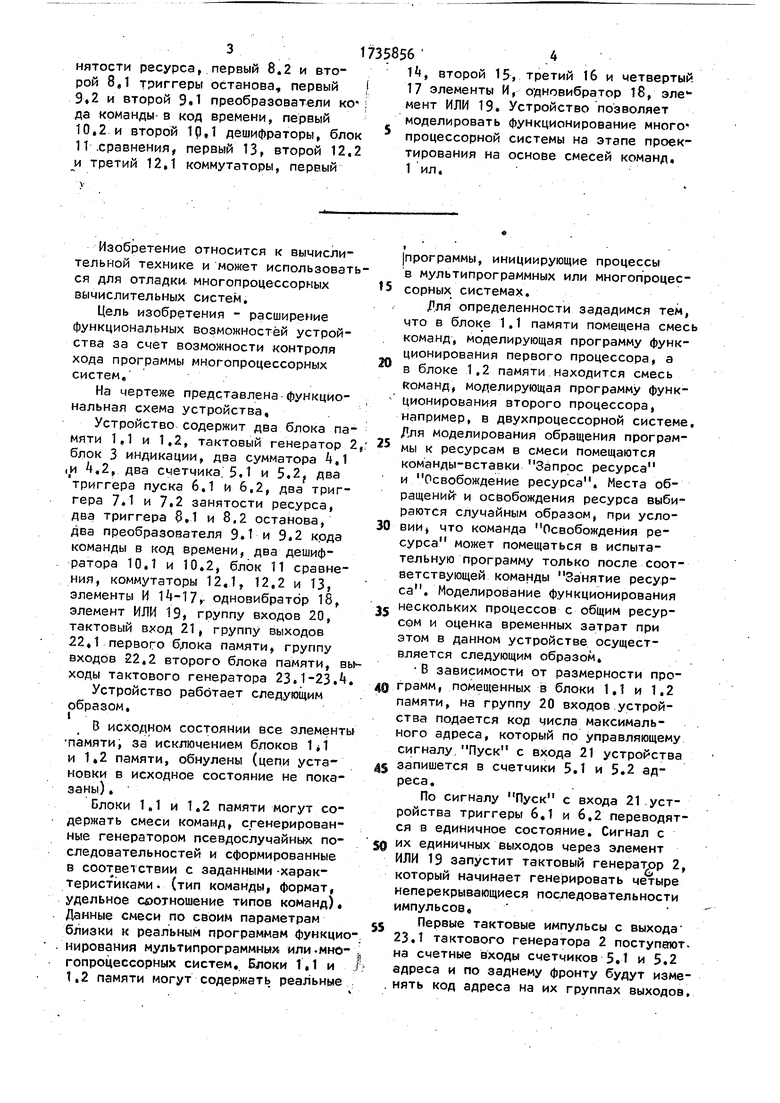

На чертеже представлена-функциональная схема устройства.

Устройство содержит два блока памяти 1,1 и 1,2, тактовый генератор 2 блок 3 индикации, два сумматора 4,1 ,и 4,2, два счетчика. 5.1 и 5.2 два триггера пуска 6,1 и 6,2, два триггера 7.1 и 7.2 занятости ресурса, два триггера 8,1 и 8.2 останова, два преобразователя 9.1 и 9.2 кода команды в код времени, два дешифратора 10.1 и 10.2, блок 11 сравнения, коммутаторы 12,1, 12.2 и 13, элементы И 14-17,- одновибратор 18, элемент ИЛИ 19, группу входов 20, тактовый вход 21, группу выходов 22,1 первого блока памяти, группу входов 22.2 второго блока памяти, входы тактового генератора 23.1-23.4

Устройство работает следующим

образом, t

В исходном состоянии все элемент

памяти, за исключением блоков 1,1 и памяти, обнулены (цепи установки в исходное состояние не показаны) .

Блоки 1.1 и 1.2 памяти могут содержать смеси команд, сгенерированные генератором псевдослучайных последовательностей и сформированные в соответствии с заданными -характеристиками . (тип команды, формат, удельное соотношение типов команд). Данные смеси по своим параметрам близки к реальным программам функци . нирования мультипрограммных или-мно гопроцессорных систем. Блоки 1,1 и 1.2 памяти могут содержать реальные

программы, инициирующие процессы в мультипрограммных или многопроцес- 5 сорных системах.

Для определенности зададимся тем, что в блоке 1.1 памяти помещена смесь команд, моделирующая программу функционирования первого процессора, а

в блоке 1,2 памяти находится смесь

команд, моделирующая программу функ- ционирования второго процессора, например, в двухпроцессорной системе. Для моделирования обращения программы к ресурсам в смеси помещаются команды-вставки Запрос ресурса и Освобождение ресурса. Места обращений1 и освобождения ресурса выбираются случайным образом, при усло0 вии, что команда Освобождения ресурса может помещаться в испытательную программу только после соответствующей команды Занятие ресурса. Моделирование функционирования

5 нескольких процессов с общим ресурсом и оценка временных затрат при этом в данном устройстве осуществляется следующим образом,

В зависимости от размерности про0 грамм, помещенных в блоки 1,1 и 1.2 памяти, на группу 20 входов устройства подается код числа максимального адреса, который по управляющему сигналу Пуск с входа 21 устройства

5 запишется в счетчики 5.1 и 5.2 адреса.

По сигналу Пуск с входа 21 устройства триггеры 6,1 и 6,2 переводятся в единичное состояние. Сигнал с

0 их единичных выходов через элемент ИЛИ 19 запустит тактовый генератор 2, который начинает генерировать четыре неперекрывающиеся последовательности импульсов

5 Первые тактовые импульсы с выхода 23.1 тактового генератора 2 поступают, на счетные входы счетчиков 5.1 и 5.2 адреса и по заднему фронту будут изме- . нять код адреса на их группах выходов.

э17

По данным адресам из блоков 1,1 и 1.2 начинают считываться коды команд, которые поступают на соответствующие преобразователи 9.1 и 9.2 кодов. Преобразователи 9.1 и Я.2 работают в соответствии с функцией F т.е. каждой считанной команде ставится в соответствие код приведенного времени выполнения системой данной команды. Коды приведенного времени поступают соответственно на коммутаторы 12,1 и 12.2.

Так как на единичных выходах триггеров 8,1 и 8.2 присутствуют сигналы логического 0м, то по инверсным входам коды -приведенного времени через коммутаторы 12.1 и 12,2 поступают на соответствующие сумматоры ,1 и k.2, где по четвертому тактовому импульсу с входа 23.3 тактового генератора 2 происходит сложение и запомина-, ние накопленной информации. Коды сумм времен функционирования процессоров | сравниваются в блоке 11 сравнения.

Так как производительность многопроцессорных систем оценивают по времени обработки наиболее большой программы, то блок 11 сравнения выработает управляющий сигнал на своем выходе h В, если время обработки программы первым процессором больше, чем вторым, и, наоборот, управляющий сигнал будет на выходе Л В в слу

больше, чем первого.

В соответствии с этими сигналами на группе выходов коммутатора 13 по первому тактовому сигналу с выхода 23.1 тактового генератора 2 появится информация либо с группы выходов сумматора .1, либо с группы выходов суматора .2. По тактовому импульсу с выхода 23.3 тактового генератора 2 иформация о времени работы многопроцессорной системы поступит в блок 3 индикации, где запишется в регистр 2 и отобразится на группе 28 элементов индикации, В многопроцессорных системах значительное влияние на производительность оказывают конфликтные ситуации, общий ресурс требуется одновременно нескольким процессорам, в этом случае запрашивающий процесс при занятом ресурсе прекращает обработку команд программы до тех пор/ пока данный ресурс не освободится«

Конфликтная ситуация в данном . устройстве контролируется следующим образом.

0

856

5

0

5

Предположим, что в первый момент времени функционирования устройства из блока 1.1 памяти будет считан код команды Запрос ресурса, данный код с группы выходов блока 1,1 памяти поступит на группу входов дешифратора 10,1, у которого на выходе 2.1 при этом коде появится управляющий сигнал, устанавливающий по приходу второго импульса с выхода 23.2 тактового генератора 2, триггер 7.1 занятости ресурса в единичное состояние, на его единичном выходе устанавливается сигнал логической 1, Данный триггер 7.1 будет в единичном состоянии до прихода на группу входов дешифратора 10.1 команды- вставки Освобождение ресурсов, тогда сигнал с выхода 2.2 триггера

7.1будет обнулен по R-входу,- В интервале между двумя командами-вставками Занять и Освободить находятся команды работы с данным ресурсом.

В случае запроса ресурса вторым процессом, когда ресурс занят первым процессом (интервал времени между командами Занят ресурс 1 и Освободить ресурс), команда1 апрос ресурса вторым процессом считывается из блока 1,2 памяти, дешифрируется дешифратором 10.2 и сигналом с выхода 25.1 по приходу второго импульса с выхода 23.2 генератора 2 установит 5 триггер 7.2 в единичное состояние. Сигнал с единичного выхода триггера

7.2поступит на второй вход элемента И 14, на первом входе которого присутствует потенциальный сигнал с еди0 ничного выхода триггера 7.1. По третьему импульсу с выхода 23.3 тактового генератора 2 сигнал с выхода элемента И 14 установит триггер 8,2 остано - ва в единичное состояние,

5 Сигнал логической единицы с единичного выхода триггера 8,2 подается на инверсный запрещающий вход счетчика 5.2, тем самым не разрешает работу счетчика 5,2 по счетному входу,

0 смена кодов адресов на группе выходов этого счетчика прекращается, считывание кодов команд из блока 1,2 памяти приостанавливается. Сигнал с единичного выхода триггера гос5 танова поступает также на управляющие входы коммутатора 12.2. По. инверсному входу закрывается коммутатор 12,2.для поступления кодов приведенного времени своего,второго

0

7

процесса с преобразователя 9; 2, а по прямому входу открывается пропуском на группу-входов сумматора 4.2 кодов приведенного времени команд первого процесса. Тем самым сум матрр 4,2 к сумме времени обработки вторым процессом программы прибавит время простоя данного процесса в связи с занятым ресурсом. Это время простоя будет определяться количеством команд работы ресурса с первым .процессом с момента при-хода , запроса Занять ресурс от второго процесса (т.е. останова-отчитывания команд второй программы) до ко-- манды Освобождение ресурса первым процессом, когда второй процесс начинает обрабатывать вновь свои команды, работая с ресурсом.

При считывании команды Освободить ресурс из блока 1.1 в памяти дешифратор на выходе 24 ..2 сформирует сигнал обнуляющий триггер 7.1 (ресурс освобожден), сигнал логического О поступит на первый вход

элемента И 14 и закроет его. Также сигнал с выхода 24,2 обнулит триггер 8.2 останова, при этом на единичном выходе триггера 8,2 появится сигнал логического О, который разрешит работу счетчика 5.2 по инверсному запрещающему входу, а также разре шит по инверсному входу коммутатора 12,2 пропуск на сумматор 4.2 кодов приведенного времени своего второго процесса,

Предположим, что второй процесс первым займет ресурс, т.е. из блока 1.2 считается команда Запрос ресурса, сигнал с выхода 25.1 дешифратора 10,2 по приходу второго импульса с выхода 23,2 тактового генератора 2 установит триггер 7.2 занятости ресурса в единичное положение.

Сигнал с его единичного выхода поступит на первый вход элемента И 16. На втором входе элемента И 1 б присутствует сигнал логической 1м, так как на инверсный вход элемента И 15 подан сигнал логического нуля с единичного выхода триггера 7И занятости ресурса первым процессом. Сигнал логической 1 с выхода эле мента И 16 поступает на вход одно- вибратора 18, где длительность сигнала увеличивается по заднему фронту,}

При считывании кода Запрос ресурса из блока 1,1 памяти дешиф10

15

20

25

1735856S

ратор 10.1 вырабатывает сигнал по 1 приходу второго импульса с выхода 23.2 тактового генератора 2, устанавливающий триггер 7.1 в единич- ное состояние. Сигнал логической 1 поступает на второй вход элемента И 17, на первом входе также присутствует сигнал логической 1м повы-. шенной длительности

1

Сигнал с «выхода элемента И 17 установит триггер 8,1 останова первого процесса в единичное состояние. При этом сигналом.с его единичного выхода приостановит свою работу счетчик 5.1 адреса, а сумматор 4,1 начнет суммировать время простоя первого процесса в связи с занятым ресурсом, т.е. будет принимать информацию о кодах времен от второго процесса.

Сигнал Освобождение ресурса вторым процессом с выхода 25.2 дешифратора 10,2 по приходу второго импульса с выхода 23.2 обнулит триггер 8.1 останова и триггер 7.2 занятости ресурса. При этом счетчик 5.1.адреса возобновит свою работу (т.е. по тактовым импульсам на счетном входе продолжит формирование кодов адресов), а коммутатор 12.1 по инверсному входу разрешит выдачу кодов со своего преобразователя 9.1 на группу входов сумматора 4.1

В случае одновременного считыва35 ния по первому такту из блоков- 1,1 и 1.2 памяти команд Запрос ресурса первым и вторым процессами триггеры 7.1 и 7.2 занятости ресурса по второму синхроимпульсу установятся в

40 единичное состояние. Сигналы с их единичных выходовпоступают на соответствующие входы элемента И 14 и по третьему тактовому импульсу с выхода 23.3 тактового генератора 2,Им45 пульсом с выхода элемента И 14.триггер 8,2 останова установится в единичное состояние и запретит работу счетчика 5.2 и сменит управление на коммутаторе 12,2., .Далее работа50 устройства будет происходить- аналог гично описанному выше. Так как единичный сигнал с единичного выхода триггера 7.1. подается на инверсный вход элемента У 15., то триггер 8.1 в единичное состояние переведен не будет. Таким образом,, в этом случае . приоритет отдается первому процессу, ресурс занимается первым процессом, а второй процесс приостанавливается

30

55

91

до освобождения ресурса первым процессом,

Устройство заканчивает свою работу следующим образом. Сметчик 5.1, настроенный на n-е количество кодов адресов, переполнившись, выдаст на свой выход сигнал переполнения, который обнулит соответствующий триггер 6.1 пуска, сигнал с нулевого выхода триггера 6,1 обнулит счетчик 5. и будет удерживать счетчик в нулевом состоянии до следующего запуска устройства.,

При пропадании сигнала логической 1 на прямом выходе триггера 6.1, либо 6,2 на выходе элемента ИЛИ 19 пропадет единичный сигнал, генератор 2 перестанет вырабатывать импульсы. Работа устройства завершена, .

Формула изобретения

Устройство для отладки -микропроцессорных систем, содержащее тактовый генератор, два счетчика, два дешифратора, четыре элемента И, элемен ИЛИ, причем первый выход тактового генератора подключен к счетному входу первого счетчика, первый выход первого дешифратора подключей к первому входу первого элемента И, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет возможности контроля хода программы многопроцессорных систем, введены два блока памяти, блок индикации, два сумматора, два триггера пуска, два триггера останова, два триггера занятости ресурса, два преобразователя кодов команды в код времени, блок сравнения, три коммутатора, од- новибратор, причем группа выходов первого блока памяти подключена к группам входов первого дешифратора и первого преобразователя кода команды в код времени, группа выходов второго блока памяти подключена к группам входов второго дешифратора и второго преобразователя кодов команды в код времени, первый выход тактового генератора подключен«к счетному входу второго счетчика, группа выходов которого подключена к группе адресных входов первого блока памяти, выход переполнения второго . счетчика подключен к нулевому входу первого триггера пуска, первый вы15

58561°

ход тактового генератора подключен

к первому и второму управляющим входам первого коммутатора, группа вы- / ходов которого подключена к группе

входов блока индикации, второй выход тактового генератора подключен к входу разрешения блока индикации, к второму входу первого элемента И,

. первому входу -второго элемента И, выход которого соединен с первым входом третьего элемента И, третий выход тактового генератора соединен с входами разрешения первого и второго сумматоров, группа выходов первого сумматора соединена с первыми группами входов блока сравнения и первого коммутатора, группа выходов второго сумматора соединена с 2Q вторыми группами входов блока срав- . нения и первого коммутатора, группа выходов первого счетчика соединена с группой адресных входов второго блока памяти, выход переполнения 2 первого счетчика соединен с нулевым входом второго триггера пуска, прямой и инверсный выходы которого соединены соответственно с первым входом элемента 1.ЛИ и входом сброса первого счетчика, прямой и инверсный выходы первого триггера пуска соединены- соответственно с вторым входом элемента ИЛИ и входом сброса второго счетчика, выход элемента ИЛИ соединен с входом тактового генератора, прямой 35 выход первого триггера занятости ресурса подключен к инверсному входу второго элемента И, третьему входу первого элемента И, первому входу чет.- вертого элемента И, выход первого 0 элемента И соединен с единичным входом первого триггера останова, выход четвертого элемента И соединен с единичным входом второго триггера останова, прямой выход второго триггера 5 занятости ресурса подключен к входу одновибратора, прямой выход первого триггера останова соединен с входом разрешения первого счетчика и первым и вторым управляющими входами второ- 0 го коммутатора, группа выходов которого соединена с группой входов второго сумматора, прямой выход второго триггера останова соединен с входом разрешения второго счетчика и 5 первым и вторым управляющим входом третьего коммутатора, группа.выходов которого подключена к группе входов первого сумматора, группа выходов ,

первого преобразователя кодов- команды

в код времени соединена с первыми группами информационных входов второ-i го и третьего коммутаторов, группа выходов второго преобразователя кода i команды в код времени соединена с вторыми группами информационных входов второго и третьего коммутаторов, первый выход первого дешифратора соединен с единичным входом второго триггера занятости ресурса, второй выход первого дешифратора соединен с нулевыми входами второго гера занятости ресурса и второго триггера останова, первый выход второго дешифратора соединен с единичным входом первого триггера занятости ресурса, второй выход второго дешифратора соединен с нулевыми вхо

5

дами первого триггера занятости ресурса и первого триггера останова, выходы блока сравнения соединены с третьим и четвертым управляющими вхо дами третьего коммутатора,выход од- новибратора соединен с вторым входом четвертого элемента И, группа входов задания максимального адреса устройства соединена с группами информационных входов первого и второго счетчиков, тактовый вход устройства соединен с синхровходами первого и второго счетчиков и I- и Обходами триггеров пуска, четвертый выход тактового генератора соединен с синхровходами триггеров занятости ресурса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки мультипрограммных систем | 1989 |

|

SU1735855A1 |

| Многотактное микропрограммное устройство управления | 1986 |

|

SU1332318A1 |

| Многоканальная микропрограммная управляющая система | 1985 |

|

SU1280628A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1543402A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Устройство для моделирования дискретных систем | 1985 |

|

SU1295411A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256026A1 |

Изобретение относится к вычислительной технике, может найти применение для контроля и отладки многопроцессорных вычислительных систем. Цель изобретения - расширение функциональных возможностей. Устройство содержит первый 1,1 и второй 1.2 блоки памяти, тактовый генератор 2, блок 3 индикации, первый .1 и второй А,2 сумматоры, первый и второй 5.1 счетчики адресов, первый 6.1 и второй 6,2 триггеры пуска, пео- вый 7.1 и второй 7.2 триггеры за

| Клямко З.И | |||

| Схемный и тестовый контроль автоматических цифровых вычислительных машин | |||

| - М.: Советское радио, 1963, с | |||

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Насос | 1917 |

|

SU13A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| ( УСТРОЙСТВО ДЛЯ ОТЛАДКИ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | |||

Авторы

Даты

1992-05-23—Публикация

1989-04-18—Подача