СО

« о

чика 16 дополнительного интервала, триггеров 18 и 19, элементов И 21, 22 и 29, элементов ИЛИ 24 и 25 и соответствующий выбор старших и младших разрядов счетчика 15 периодов позволяет обеспечивать отнесение значений делителя и делимого в делителе 30 частоты к одному периоду измеряемой частоты. Поступление на вход блока 27 вычитания одного импульса обеспечивает практически всегда равенство результата деления нулю. Это, в свою очередь, приводит к правильному результату измерения частоты. Таким образом обеспечивается меньшая динамическая погрешность измерения и измерение частот, в большой степени изменяющихся в процессе измерения. В описании приведен пример реализации блока 1 управления. 1 з.п. ф-лы, 5 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ измерения частоты импульсного сигнала и устройство для его осуществления | 1980 |

|

SU911359A1 |

| Цифровой частотомер | 1980 |

|

SU941906A1 |

| Программируемый делитель частоты | 1985 |

|

SU1290515A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| Умножитель частоты | 1978 |

|

SU798831A1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Цифровой частотомер | 2019 |

|

RU2730047C1 |

| ЦИФРОВОЙ ЧАСТОТОМЕР | 1973 |

|

SU406169A1 |

| Устройство для измерения частоты сигналов | 1979 |

|

SU789863A1 |

Изобретение может быть использовано в системах обработки информа днии управления для измерения низких и инфранизких частот. Цифровой частотомер содержит блок 1 управления, счетчики 13-16 измерительного интервала, целой части результата измерения, периода и дробной части результата измерения соответственно, элемент И 20, элемент ИЛИ 23, группу 26 элементов И, блок 27 вычитания и делитель 30 частоты. Введение счет-

1

Изобретение относится к вычислительной и электроизмерительной технике и может быть использовано в системах обработки информации и управления для измерения низких и инфра- низких частот.

Цель изобретения - уменьшение динамической погрешности измерения и расширение функциональных возможностей устройства.

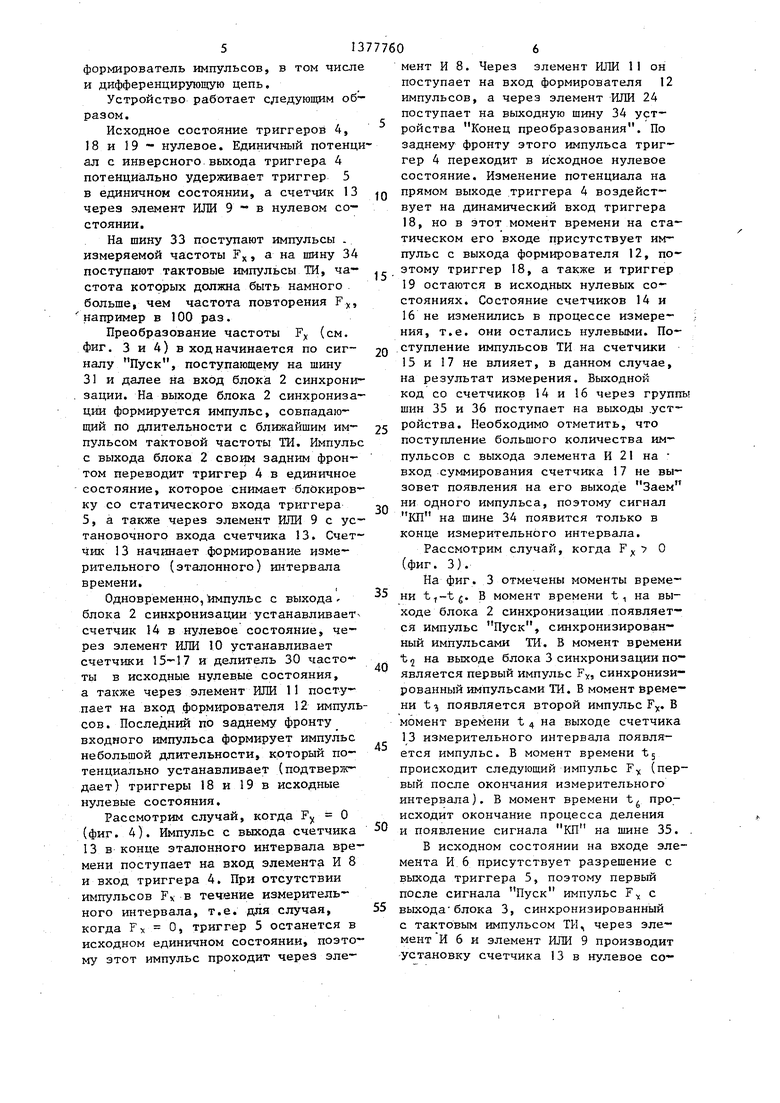

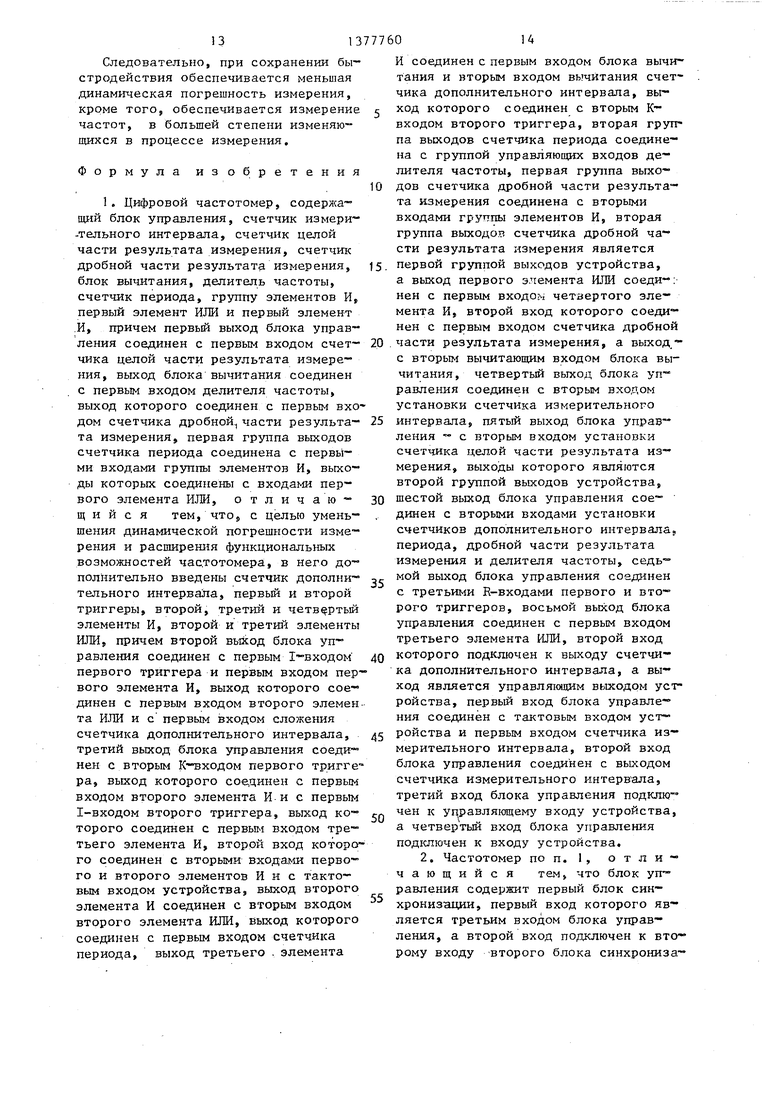

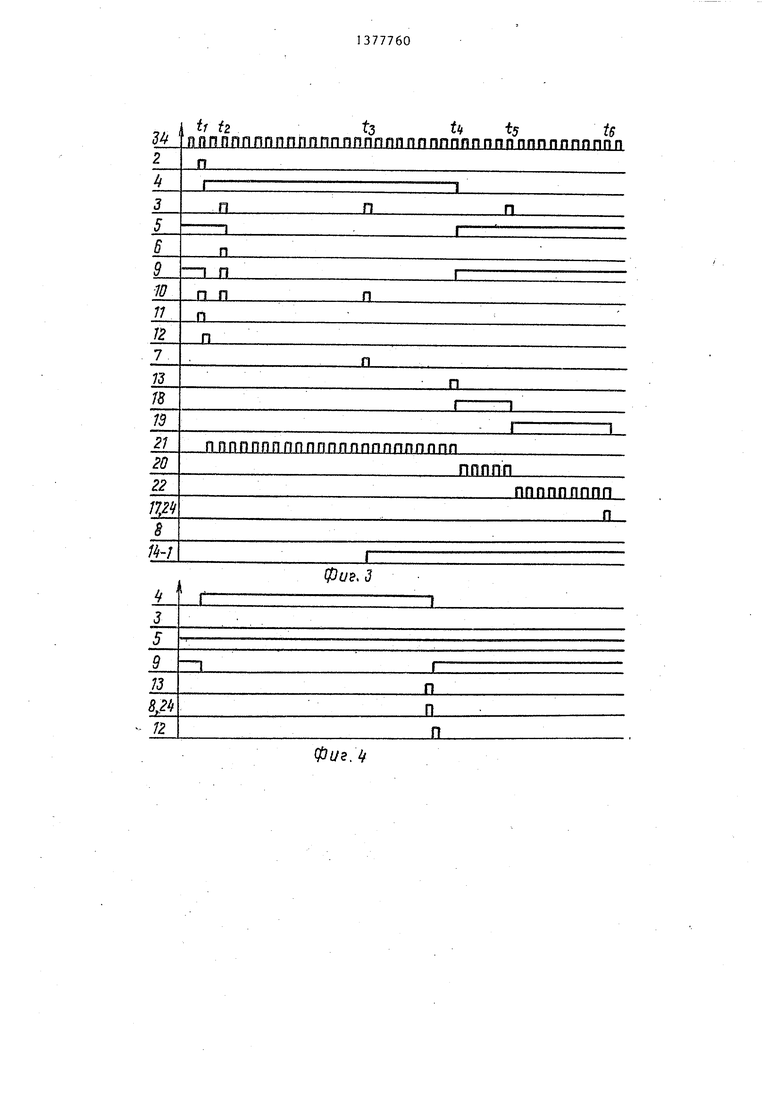

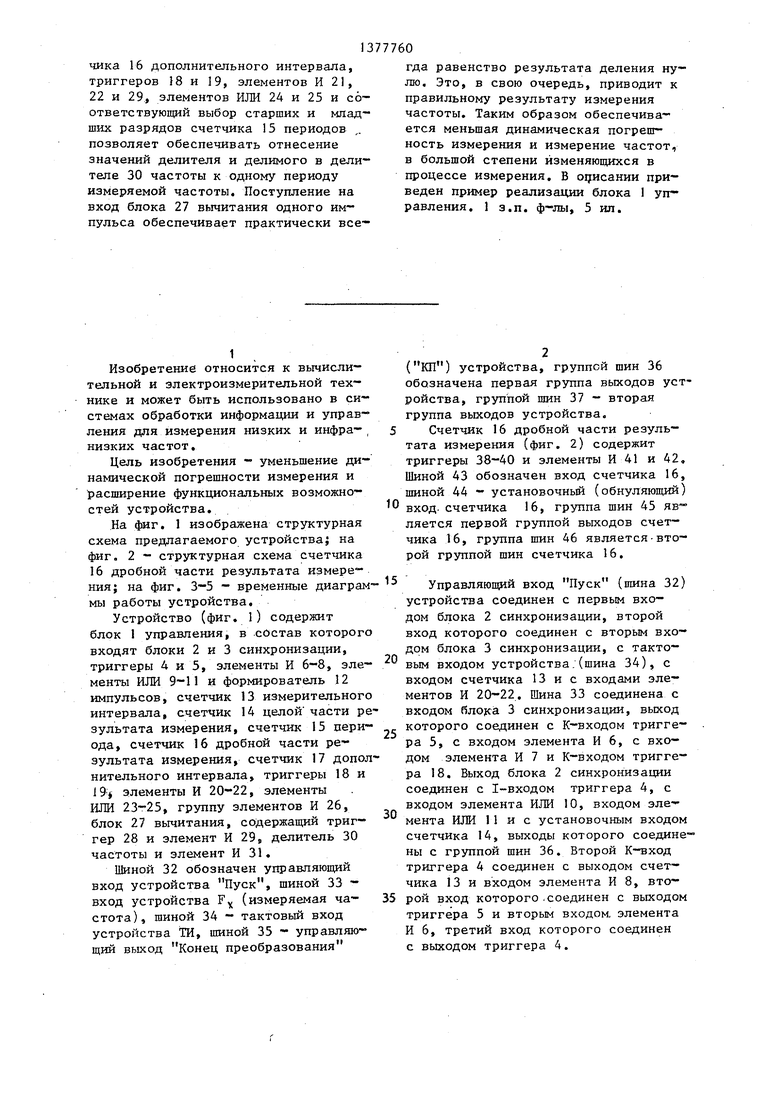

На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - структурная схема счетчика 16 дробной части результата измерения; на фиг. 3-5 - временные диаграммы работы устройства.

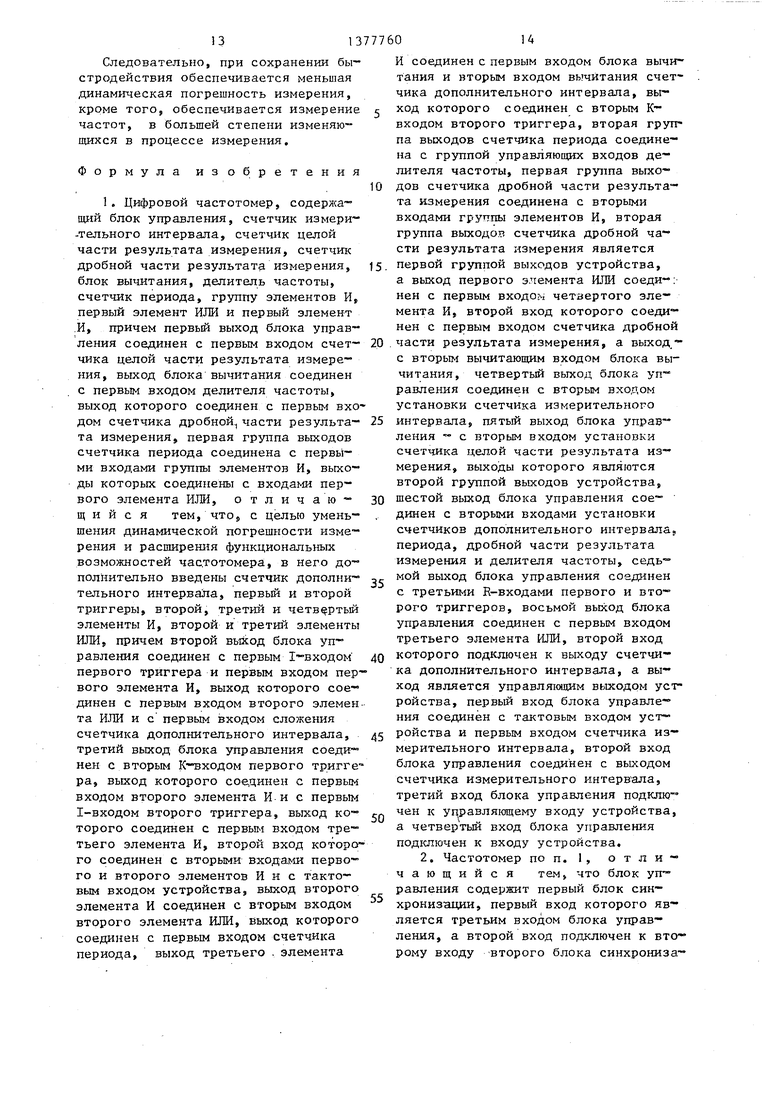

Устройство (фиг. 1) содержит блок 1 управления, в состав которого входят блоки 2 и 3 синхронизации, триггеры 4 и 5, элементы И 6-8, элементы ИЛИ 9-11 И формирователь 12 импульсов, счетчик 13 измерительного интервала, счетчик 14 целой части результата измерения, счетчик 15 цери ода, счетчик 16 дробной части результата измерения, счетчик 17 дополнительного интервала, триггеры 18 и i9j элементы И 20-22, элементы ИЛИ 23-25, группу элементов И 26, блок 27 вычитания, содержащий триггер 28 и элемент И 29, делитель 30 частоты и элемент И 31,

Шиной 32 обозначен управляющий вход устройства Пуск, шиной 33 - вход устройства F (измеряемая частота), шиной 34 - тактовый вход устройства ТИ, шиной 35 управляющий выход Конец преобразования

(КП) устройства, группой шин 36 обозначена первая группа выходов устройства, группой шин 37 - вторая группа выходов устройства.

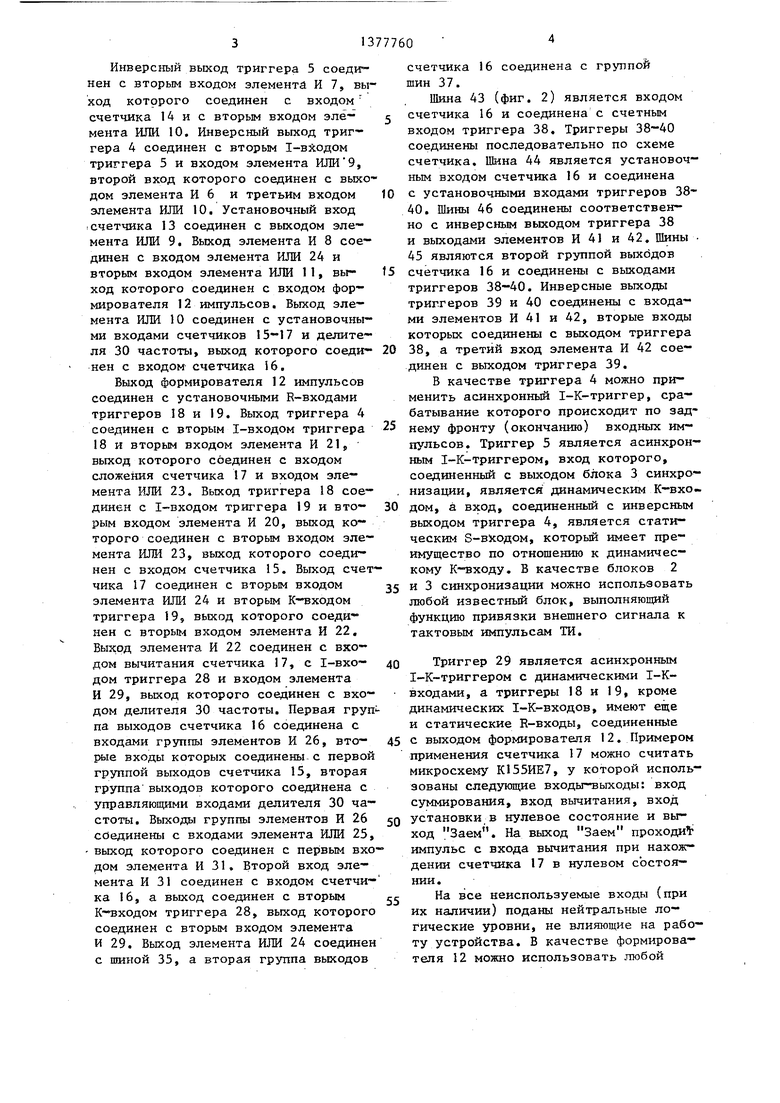

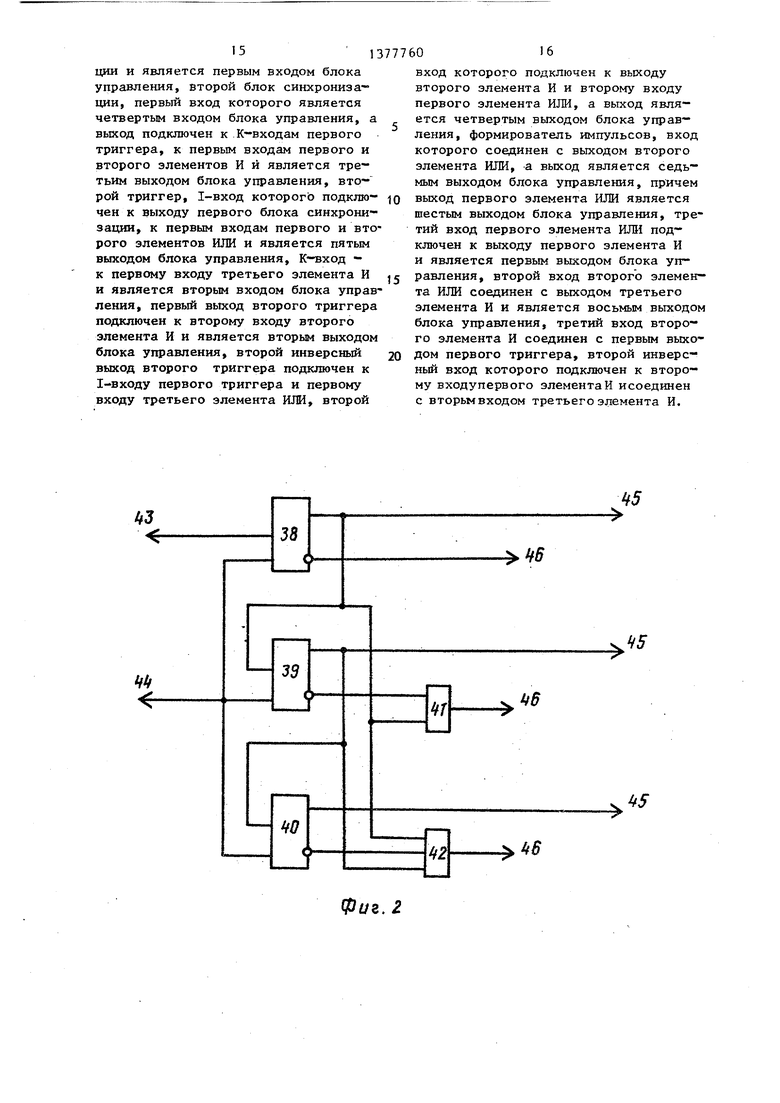

5 Счетчик 16 дробной части результата измерения (фиг. 2) содержит триггеры 38-40 и элементы И 41 и 42, Шиной 43 обозначен вход счетчика 16, шиной 44 - установочный (обнуляющий)

вход- счетчика 16, группа шин 45 является первой группой выходов счетчика 16, группа шин 46 является-второй группой шин счетчика 16.

Управляюдай вход Пуск (шина 32) устройства соединен с первым входом блока 2 синхронизации, второй вход которого соединен с вторым входом блока 3 синхронизации, с такто- вым входом устройства.(шина 34), с входом счетчика 13 и с входами элементов И 20-22. Шина 33 соединена с входом блока 3 синхронизации, выход которого соединен с К-входом триггера 5, с входом элемента И 6, с входом элемента И 7 и К-входом триггера 18. Выход блока 2 синхронизации соединен с 1-входом триггера 4, с входом элемента ИЛИ 10, входом элемента ИЛИ 11 и с установочным входом счетчика 14, выходы которого соединены с группой шин 36. Второй К-вход триггера 4 соединен с выходом счетчика 13 и входом элемента И 8, вто-

5 рой вход которого .соединен с выходом триггера 5 и вторым входом, элемента И 6, третий вход которого соединен с выходом триггера 4.

5

0

Инверсный выход триггера 5 соединен с вторым входом элементй И 7, выход которого соединен с входом счетчика 14 и с вторым входом элемента ИЛИ 10. Инверсный выход триггера 4 соединен с вторым 1-входом триггера 5 и входом элемента ИЛИ 9, второй вход которого соединен с выходом элемента И 6 и третьим входом элемента ИЛИ 10. Установочный вход 1 счетчика 13 соединен с выходом элемента ИЛИ 9. Выход элемента И 8 соединен с входом элемента ИЛИ 24 и вторым входом элемента ИЛИ 11, выход которого соединен с входом формирователя 12 импульсов. Выход элемента ИЛИ 10 соединен с установочными входами счетчиков 15-17 и делителя 30 частоты, выход которого соединен с входом счетчика 16.

Выход формирователя 12 импульсов соединен с установочными R-входами триггеров 18 и 19. Выход триггера 4 соединен с вторым 1-входом триггера 18 и вторым входом элемента И 21, выход которого соединен с входом сложения счетчика 17 и входом элемента ИЛИ 23. Выход триггера 18 соединен с 1-входом триггера 19 и вторым входом элемента И 20, выход ко торого соединен с вторым входом элемента ИЛИ 23, выход которого соединен с входом счетчика 15. Выход счетчика 17 соединен с вторым входом элемента ИЛИ 24 и вторым К-входом триггера 19, выход которого соединен с вторым входом элемента И 22, Выход элемента И 22 соединен с входом вычитания счетчика 17, с 1-вхо- дом триггера 28 и входом элемента И 29, выход которого соединен с входом делителя 30 частоты. Первая груп па выходов счетчика 16 соединена с входами группы элементов И 26, вторые входы которых соединены с первой группой выходов счетчика 15, вторая группа выходов которого соединена с управляющими входами делителя 30 частоты. Выходы группы элементов И 26 соединены с входами элемента ИЛИ 25, выход которого соединен с пер1вым входом элемента И 31, Второй вход элемента И 31 соединен с входом счетчи- ка 16, а выход соединен с вторым К-входом триггера 28, выход которого соединен с вторым входом элемента И 29. Выход элемента ИЛИ 24 соединен с шиной 35, а вторая группа выходов

счетчика 16 соединена с группой шин 37.

Шина 43 (фиг. 2) является входом

счетчика 16 и соединена с счетным входом триггера 38. Триггеры 38-40 соединены последовательно по схеме счетчика. Шина 44 является установочным входом счетчика 16 и соединена

с установочными входами триггеров 38- 40. Шины 46 соединены соответственно с инверсным выходом триггера 38 и выходами элементов И 41 и 42. Шины 45 являются второй группой выходов

счетчика 16 и соединены с выходами триггеров 38-40. Инверсные выходы триггеров 39 и 40 соединены с входами элементов И 41 и 42, вторые входы которых соединены с выходом триггера

38, а третий вход элемента И 42 соединен с выходом триггера 39.

В качестве триггера 4 можно применить асинхронный 1-К-триггер, срабатывание которого происходит по заднему фронту (окончанию) входных импульсов. Триггер 5 является асинхронным 1-К-триггером, вход которого, соединенный с выходом блока 3 синхро- низации, является динамическим К-входом, а вход, соединенный с инверсным выходом триггера 4, является статическим 8-вКодом, который имеет преимущество по отношению к динамическому К-входу, В качестве блоков 2

и 3 синхронизации можно использовать любой известный блок, выполняющий функцию привязки внешнего сигнала к тактовым импульсам ТИ.

Триггер 29 является асинхронным 1-К-триггером с динамическими I-K- входами, а триггеры 18 и 19, кроме динамических 1-К-входов, имеют еще и статические R-входы, соединенные

с выходом формирователя 12. Примером применения счетчика 17 можно считать микросхему К155ИЕ7, у которой использованы следующие входы-выходы: вход суммирования, вход вычитания, вход

установки в нулевое состояние и выход Заем. На выход Заем проходиТ:- импульс с входа вычитания при нахождении счетчика 17 в нулевом состоянии.

На все неиспользуемые входы (при их наличии) поданы нейтральные логические уровни, не влияющие на работу устройства. В качестве формирователя 12 можно использовать любой

формирователь импульсов, в том числе и дифференцирующую цепь.

Устройство работает следующим образом.

Исходное состояние триггеров 4, 18 и 19 - нулевое. Единичный потенциал с инверсного.выхода триггера 4 потенциально удерживает триггер 5 в единичном состоянии, а счетчик 13 через элемент ИЛИ 9 - в нулевом состоянии.

На шину 33 поступают импульсы . измеряемой частоты F, а на шину 34 поступают тактовые импульсы ТИ, частота которых должна быть намного . больше, чем частота повторения Р,,, например в 100 раз.

Преобразование частоты F (см. фиг. 3 и 4) в ход начинается по сигналу Пуск, поступающему на шину 31 и далее на вход блока 2 синхронизации. На выходе блока 2 синхронизации формируется импульс, совпадающий по длительности с ближайшим импульсом тактовой частоты ТИ. Импульс с выхода блока 2 своим задним фронтом переводит триггер 4 в единичное состояние, которое снимает блокировку со статического входа триггера 5, а также через элемент ИЛИ 9 с установочного входа счетчика 13. Счетчик 13 начинает формирование измерительного (эталонного) интервала времени.

Одновременно, импульс с выхода блока 2 синхронизации устaHaBnHBaeTN счетчик 14 в нулевое состояние, через элемент ИЛИ 10 устанавливает счетчики 15-17 и делитель 30 частоты в исходные нулевые состояния, а также через элемент ИЛИ 1 поступает на вход формирователя 12 импульсов. Послеу ний по заднему фронту входного импульса формирует импульс небольшой длительности, который потенциально устанавливает (подтверждает) триггеры 18 и 19 в исходные нулевые состояния.

Рассмотрим случай, когда Fy О (фиг. 4). Импульс с выхода счетчика 13 в конце эталонного интервала времени поступает на вход элемента И 8 и вход триггера 4. При отсутствии импульсов FX в течение измерительного интервала, т.е. для случая, когда FX О, триггер 5 останется в исходном единичном состоянии, поэтому этот импульс проходит через эле5

0

5

мент И 8. Через элемент ИЛИ II он поступает на вход формирователя 12 импульсов, а через элемент ИЛИ 24 поступает на вьисодную шину 34 устройства Конец преобразования. По заднему фронту этого импульса триггер 4 переходит в исходное нулевое состояние. Изменение потенциала на

Q прямом выходе триггера 4 воздействует на динамический вход триггера 18, но в этот момент времени на статическом его входе присутствует импульс с выхода формирователя 12, поэтому триггер 18, а также и триггер 19 остаются в исходных нулевых состояниях. Состояние счетчиков 14 и 16 не изменились в процессе измерения, т.е. они остались нулевыми. Поступление импульсов ТИ на счетчики 15 и 17 не влияет, в данном случае, на результат измерения. Выходной код со счетчиков 14 и 16 через группь шин 35 и 36 поступает на выходы .устройства. Необходимо отметить, что поступление большого количества импульсов с выхода элемента И 21 на вход суммирования счетчика 17 не вызовет появления на его выходе Заем ни одного импульса, поэтому сигнал КП на шине 34 появится только в конце измерительного интервала.

Рассмотрим случай, когда F О (фиг. 3).

На фиг. 3 отмечены моменты времени . В момент времени t, на выходе блока 2 синхронизации появляется импульс Пуск, синхронизированный импульсами ТИ. В момент времени ti; на выходе блока 3 синхронизации по является первый импульс F, синхронизированный импульсами ТИ. В момент времени t появляется второй импульс F.В момент времени t 4 на выходе счетчика 13 измерительного интервала появляется импульс. В момент времени t происходит следующий импульс F (первый после окончания измерительного интервала). В момент времени t происходит окончание процесса деления

0 и появление сигнала КП на шине 35. . В исходном состоянии на входе элемента И 6 присутствует разрешение с выхода триггера 5, поэтому первый после сигнала Пуск импульс F с

5 выхода блока 3, синхронизированный с тактовым импульсом ТИ, через элемент И 6 и элемент ИЛИ 9 производит установку счетчика 13 в нулевое со0

5

0

5

стояние, синхронизируя тем самым начало измерения входным импуль сом Fy . Счетчик 13 начинает новое формирование эталонного измерительного интервала времени. Одновременно импульс с выхода элемента И 6 проходит через элемент ИЛИ Ш и устанавливает счетчики 15-17 и делитель 30 частоты в исходные нулевые состояния. Одновременно первый импульс F, с выхода блока 3 своим задним фронтом переводит триггер 5 в нулевое состояние, которое блокирует элемент И 6 и снимает блокировку с элемента И 7. Дальнейшие импульсы F (при их наливши) с выхода блока 3 подтверзкдают нулевые состояния триггеров 5 и 18, через элемент И 7 изменяют состояние счетчика 14 целой части результата измерения и через элемент ИЛИ 10 периодически устанавливают счетчики 15-17 и делитель 20 частоты в нулевые исходные состояния. Если в течение нового эталонного интервала времени не было импульсов Fy, то целая часть результата изме-- рения (содержимое счетчика 14) будет нулевой.

Счетчик 17 измеряет величину интервала между последним импульсом измеряемой частоты F и концом эталонного измерительного интервала времени. Для этого при переходе тригге ра 4 в единичное состояние на вход элемента И 21 подается разрешакщий потенциал и тактовые импульсы ТИ поступают на вход счетчика 17. При поступлении очередного импульса F происходит очередная установка счетчика 17 в исходное нулевое состояние и начинается новое измерение и т.д. При переходе 4 в исходное нулевое состояние триггер 18 переходит в единичное состоя ние, а на вход элемента И 21 поступает запрет, в результате чего в счетчике 17 будет записана величина интервала междупоследним импульсом F и концом эта лонного измерительного интервала.

Одновременно импульсы с выхода элемента И 21 через элемент ИЛИ 23 поступают на вход счетчика 3 периода, поэтому к моменту перехода триггера 18 в единичное состояние в нем будет записано такое же значение кода, как и в счетч1п е 17, Далее разрешающий потенциал с выхода триггера 18 поступает на вход элемента И 20 и

ТИ через элемент И 20 и элемент ИЛИ 23 продолжают поступать на вход счетчика 15 периода, увеличивая его содержимое. Следующий импульс Fy вызовет переход триггера 18 в нулевое состояние, который, в свою очередь, переведет триггер 19 в едшпгчное (разрешающее) состояние. К этому

0 моменту времени в счетчике 15 будет записана величина периода измеряемой частоты, npi-niex именно для этого периода измерялась величина отрезка между последн Ш 1гнпульсом FX внутри

5 эталонного измеритель юго интервала и концом этого инт.рвала.

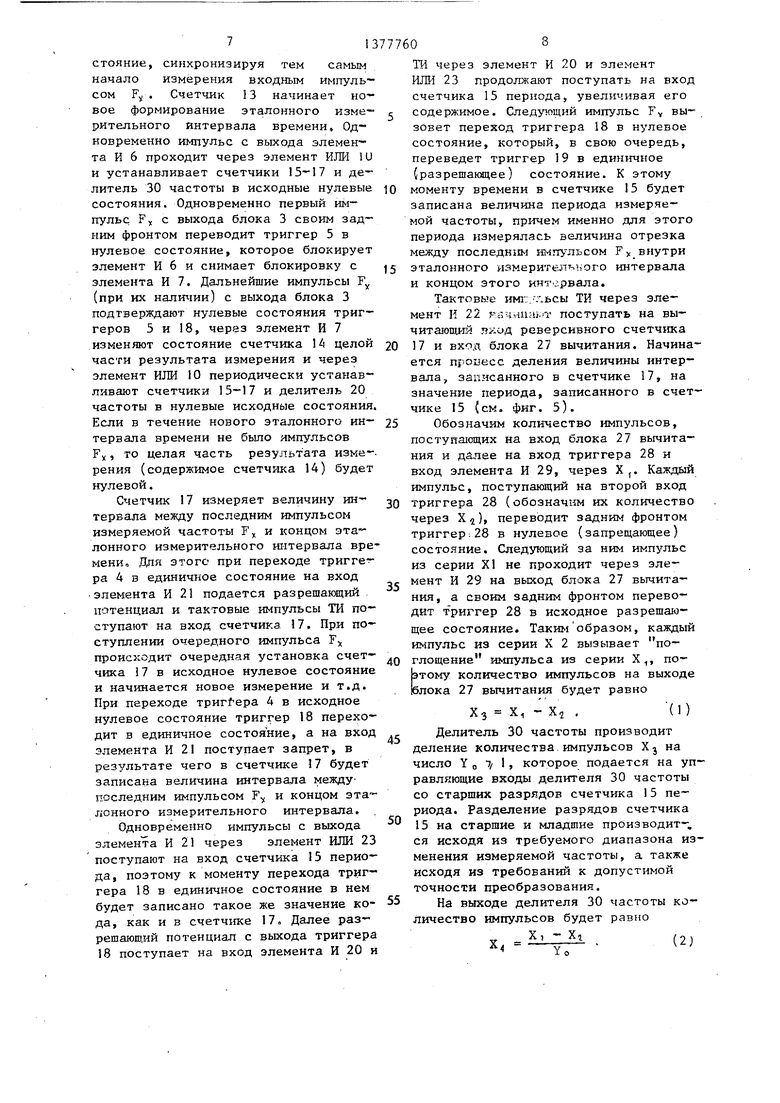

Тактовые ишт/т.ьсы ТИ через элемент И 22 кзчипак поступать на вы- читающиз лкод реверсивного счетчика

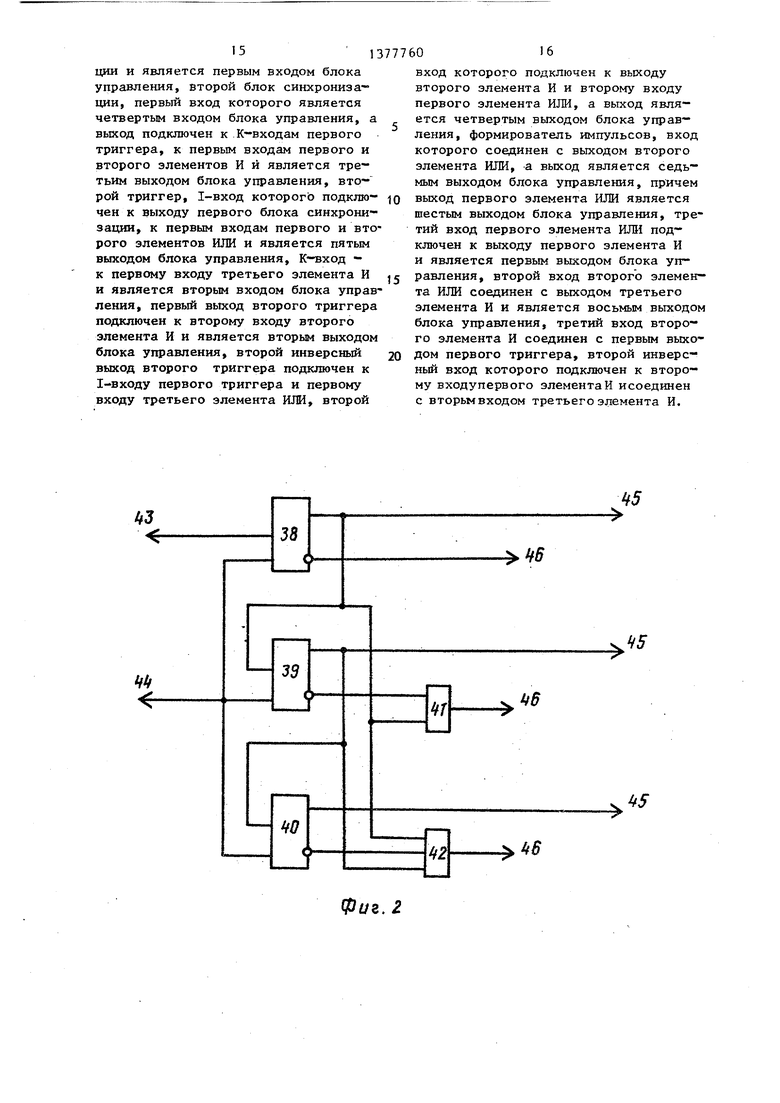

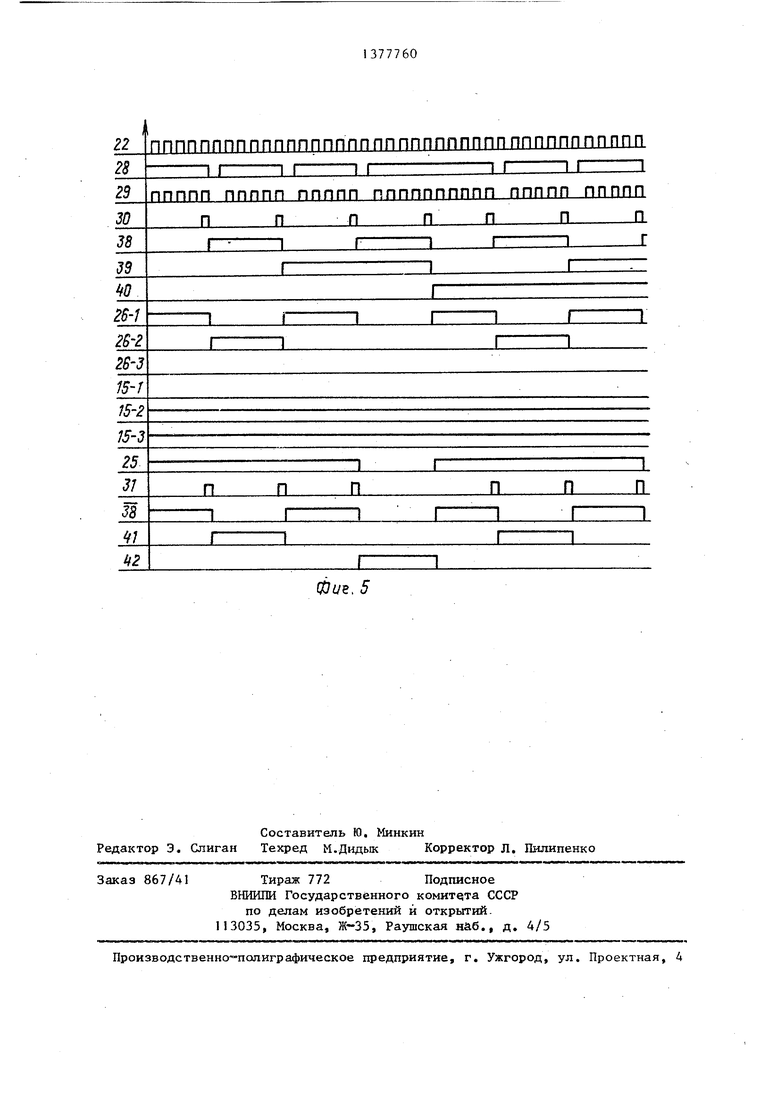

0 17 и вход блока 27 вычитания. Начинается процесс деления величины интервала, записанного в счетчике 17, на значение периода, записанного в счетчике 15 (см, фиг. 5).

5 Обозначим количество импульсов, поступающих на вход блока 27 вычитания и далее на вход триггера 28 и вход элемента И 29, через X,. Каждый импульс, поступающий на второй вход

0 триггера 28 (обозначг м их количество через Х/), переводит задним фронтом триггер.28 в нулевое (запрещающее) состояние. Следующий за ним импульс из серии XI не проходит через элемент И 29 на выход блока 27 вычитания, а своим задним фронтом переводит т риггер 28 в исходное разрешающее состояние. Таким образом, каждый импульс из серии X 2 вызывает поглощение ш-тульса из серии X,, по- Ьтому количество импульсов на выходе Ьлока 27 вычитания будет равно

Хз Х, - Х-г . (1)

Делитель 30 частоты производит деление количества.импульсов Xj на число Y о / 1 , которое подается на управляющие входы делителя 30 частоты со старших разрядов счетчика 15 периода. Разделение разрядов счетчика 15 на старшие и младшие производит-, ся исходя из требуемого диапазона изменения измеряемой частоты, а также исходя из требований к допустимой точности преобразования. 5 На выходе делителя 30 частоты количество импульсов будет равно у - X - Хг

5

0

5

0

(2)

Данные импульсы поступят на вход счетчика 16,. Счетчик 16 будет изме-. нять свое состояние и на шинах 46 будут появляться импульсы. Элементы И 41 и 42 необходимы для того, чтобы импульсы на шинах 46 взаимно не перекрывались. Количество импульсов на шинах 46 будет уменьшаться с ростом номера разряда счетчика 16 и будет соответственно равно

Х4

; -;

b.v 8

Х4

7б

и т.д.

На выходе элементов И 26 группы пройдут не- все импульсы с шин 46, а только те, для которых существует разрешение с выходов младших разрядов счетчика 15 периода.

Количество импульсов на выходах элементов И 26 группы, или на входах элемента ИЛИ 25 будет равно

Х4

Х4 Уз Х4

Y4

16

и т.д..

где YJ принимают два значения: нуль или единица. На выходе элемента ИЛИ 25 происходит суммирование входных импульсов и общее их количество будет равно

(3)

Данные импульсы через элемент И 31 поступают на вычитающий вход блока 27 вычитания.

Наличие элемента И 31 необходимо для дальнейшего уменьшения длительности импульсов, чтобы они не слива - лись на входе блока 27 вычитания (см. фиг. 5).

Решая совместно уравнение (2) и (3), получим

X, Х « -S-

(4)

YO +

Y.-2

Количество импульсов XL, равно значению интервала, записанного в

счетчике 17. При достижении кода счетчика 17 нулевого значения на его выходе появляется импульс, который задним фронтом переводит триггер 19 в исходное нулевое состоян1ие, заканчивая тем самым процесс деления и преобразования частоты в код. Одновременно этот импульс через элемент ИЛИ 24 поступает на входную шину 35 КП.

Результат деления величины интервала между последним импульсом измеряемой частоты внутри эталонного из- .мерительного интервала на значение периода измеряемой частоты будет записан в счетчике 16 дробной части результата измерения и по шинам 37 поступит на выход устройства. В счетчи- .ке 14 будет записана целая часть результата измерения.

Процесс деления изображения на фиг. 5 для случая, когда коэффициент

деления равен Y О,

Y 5; Y, Y 1

т.е.

Y - 5

5,75.

0

0

5

0

5

На. фиг. 3 изображены диаграммы для случая, когда момент времени t4 лежит между t и t, но возможен

случай, когда импульс с выхода счетчика 13 совпадает, с импульсом F (момент времени t совпадает с моментом времени , Данный (последний) импульс F обнуляет счетчик 17 и, начиная с этого момента, на вход суммирования счетчика 17 не поступит бо лее ни одного импульса, т.е. его состояние останется нулевьм (на входе элемента И 21 будет запрет с выхода триггера 4). На вход счетчика 15 будут поступать импульсы с вькода эле мента И 20 через элемент ИЛИ 23 до следующего импульса Fj,, который переводит триггер 18 в нулевое состояние. При переходе триггера 19 в единичное состояние подается разрешение на вход элемента И 22. Первый импульс с выхода элемента И 22, поступая на вход вычитания счетчика 17, вызьтает появление импульса на его выходе Заем который переводит триггер 19 в исход- нее нулевое состояние, заканчивая процесс деления. На вход блока 27 вычитания поступит один импульс, поэтому результат деления практически всегда будет равен нулю, т.е. результат измерения частоты будет правиль-

,

Рассмотрим принцип разделения разрядов счетчика 15 на старшие и младшие на конкретном примере. Пусть например, счетчик 15 периода содержи пятнадцать двоичных разрядов, из которых пять старших разрядов занимает целая часть коэффициента деле- ния, а десять разрядов - дробная, F 10 МГц, где F у - частота повторения тактовых импульсов.

Для правильной работы схемы деления необходимо, чтобы целая часть коэффициента, деления была больше нуля, т.е. Y о т/ 1, поэтому минимальное значение периода входной частоты будет составлять 102,4 мкс или 1024 импульсов тактовой частоты. Отсюда находим

BY. мачс.

0ТС. MU Н

980 Гц.

Максимальное значение периода входной частоты будет при полном заполнении счетчика 15 периода, т,з.

ev. МЫМГ

3276,7 МКС или 32767 тактов

откуда Fg „у„ 30,6 Гц.

Диапазон входных частот будет раF

вен

tx. макс

32, Т.е. равен

Вх. мим

максимальному значению YO.

Здесь Fg „„„ и F.g - максимальное и минимальное значения измеряемой частоты, Tg и Т,

максимальное и минимальное значения измеряемого периода.

Погрешность измерения будет зависеть от величины измерительного интервала (времени измерения). Допустим, что время измерения равно 0,1 с, F 30 Гц. Целая часть результата измерения, записанная в счетчике 14, будет равна три и занимать два двоичных разряда, а дробная часть результата измерения, записанная в счетчике 16, будет занимать десять разрядов, т.еф суммарный результат измерения будет занимать двенадцать двоичных разрядов. Погрешность измерения не превысит 0,025%.

Дпя F X 500 Гц целая часть результата измерения будет занимать

5

0

5

0

5

0

5

0

5

не менее шести двоичных разрядов, а суммарный результат измерения будет занимать шестнадцать двоичных разрядов, т.е. погрешность измерения будет существенно меньше. Если уменьшить количество старших разрядов счетчика 15 периода и соответственно увеличить количество младших разрядов, то уменьшится допустимый диапазон измеряемых частот, но возрастет точность измерения.

При 1 МГц можно измерить с такой же точностью частоты 3,1 - 98 Гц, но время измерения должно составлять 1 с. Делитель 30 частоты производит деление количества импульсов, поступающих на его вход с выхода элемента И 29, на коэффициент, равный Yg. На временной диаграмме, изображенной на фиг. 5, рассмотрен процесс деления при YO 5. Делитель 30 частоты подсчитьшает количество входных импульсов и в момент поступления каждого пятого импульса пропускает его на выход, одновременно приходя в исходное нулевое состояние. Срабатывание делителя 30 частоты должно происходить .до переднему фронту, а количество поступивших импульсов может определяться схемой сравнения. Примером построения такого, делителя может служить делитель частоты с переменным коэффициентом деления, содержащий счетчик импульсов, элементы сравнения, задающее устройство, элементы И и триггер. Делитель 30 частоты также можно по- . строить на базе счетчика с регулируемым коэффициентом пересчета.

Соединение старших разрядов счетчика 15 периода с управляющим входом делителя 30 частоты на фиг. 1 условно показано одной линией.

Введение счетчика дополнительного интервала, двух триггеров, трех дополнительных элементов И и дополнительного элемента ИЛИ и соответству ющий выбор старших и младших разрядов счетчика I5 позволяет обеспечивать отнесение значений делителя и делимого в делителе 30 частоты к одному периоду измеряемой частоты. Поступление на вход блока 27 вычитания одного импульса обеспечивает вследствие этого практически всегда равенство результата деления нулю, что, в свою очередь, приводит к правильному результату измерения частоты.

13

Следовательно, при сохранении быстродействия обеспечивается меньшая динам1-гческая погрешность измерения, кроме того, обеспечивается измерение частот, в большей степени изменяю щихся в процессе измерения,

Формула изобретения

13

-

та измерения, первая группа выходов счетчика периода соединена с первыми входами группы элементов И, выхо ды которых соединены с входами первого элемента ИЖ, отличаю щ и и с я тем, чтол с целью уменьшения динамической погрешности измерения и расширения функциональных возможностей час.тотомера, в него дополнительно введены счетчик дополнительного интервала, первый и второй триггеры, второй, третий и четвертьй элементы И, второй и третш элементы ИЛИ, причем второй выход блока управления соединен с первым 1 входом первого триггера и первым входом первого элемента И, выход которого сое динен с первым входом второго элемента ИЛИ и с первым входом сложения счетчика дополнительного интервала, третий выход блока управления соеди иен с вторым К- ходом первого тригге ра, выход которого сое,чинен с первым входом второго элемента И и с первь1м 1-входом второго триггера, выход которого соединен с первьп- входом третьего элемента И, второй вход которого соединен с вторыми входами первого и второго элементов И и с тактовым входом устройства, выход второго элемента И соединен с вторым входом второго элемента ИЛИ, выход которого соединен с первым входом счетчика периода, выход третьего . элемента

7776014

И соединен с первым входом блока вычи тания и вторым входом вычитания счетчика дополнительного интервала, вы- г ход которого соединен с вторым К- входом второго триггера, вторая грутг- па выходов счетчика периода соединена с группой управляющих входов делителя частоты, первая группа выхо10 дов счетчика дробной части результата измерения соединена с вторыми входами группы элементов И, вторая группа выходов счетчика дробной части результата измерения является

0

5

0

5

0

5

ления ™ с вторым входом установки счетчика целой части результата из мерения, выходы которого являются второй группой выходов устройства, шестой выход блока управления сое- динен с вторыми входами установки счетчиков дополнительного интервала периода, дробной части результата измерения и делителя частоты, седьмой выход блока управления соединен с третьш- и R-входами первого и второго триггеров, восьмой выход блока управления соединен с первым входом третьего элемента ИЛИ, второй вход которого подключен к выходу счетчика дополнительного интервала, а вы ход является управлякидим выходом устройства, первый вход блока управления соединен с тактовым входом устройства и первым входом счетчика измерительного интервала, второй вход блока управления соединен с выходом счетчика измерительного интерв ала, третий вход блока управления подключен к управлягадему входу устройства, а четвертый вход блока управления подключен к входу устройства,

2, Частотомер по п, 1, о т л и чающийся тем, что блок уп™ равления содержит первый блок синхронизации, первый вход которого является третьим входом блока управления, а второй вход подключен к второму входу второго блока синхрониза

15 1

ции и является первым входом блока управления, второй блок синхрониза ции, первый вход которого является четвертым входом блока управления, а выход подключен к .К входам первого триггера, к первым входам первого и второго элементов И и является третьим выходом блока управления, второй триггер, 1-вход которого подключен к выходу первого блока синхронизации, к первым входам первого и второго элементов ИЖ и является пятым выходом блока управления. К-вход - к первому входу третьего элемента И и является вторым входом блока управления, первый выход второго триггера подключен к второму входу второго элемента И и является вторым выходом блока управления, второй инверсный выход второго триггера подключен к 1-входу первого триггера и первому входу третьего элемента ИЛИ, второй

ff3

38

LJ fff/ 39

LJT

0

LJT

Фи.2

0

7760

5

0

16

вход которого подключен к выходу второго элемента И и второму входу первого элемента ИЛИ, а выход является четвертым выходом блока управления, формирователь импульсов, вход которого соединен с выходом второго элемента ИЛИ, а выход является седьмым выходом блока управления, причем выход первого элемента ИЛИ является шестым выходом блока управления, третий вход первого элемента ИЛИ подключен к выходу первого элемента И и является первым выходом блока управления, второй вход второго элемента ИЛИ соединен с выходом третьего элемента И и является восьмым выходом блока управления, третий вход второго элемента И соединен с первым выходом первого триггера, второй инверсный вход которого подключен к второму входупервого элемента И исоединен с вторьмвходом третьего элемента И.

6

5

s

l4

i iztsи isis

nnnnnnnnnnnnnnnnnnnnnnnnnnnnnnnnnnnnnnnn

nПTL

70

П ПП

77

-П

J2

n

73

21

rLCLDJCin П ППППППППППППППППП

20

22

/m

Фи.З

Фиг.

П

ппппп

ппппппппп

JL

, 5

| Цифровой частотомер | 1980 |

|

SU941906A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой частотомер | 1982 |

|

SU1018036A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-02-28—Публикация

1986-10-27—Подача