Изобретение oTHocHfcH к импульсной технике и может быть использовано в системах автоматики в качестве делителя частоты на любой вещественный коэффициент деления, в устройствах синхронизации, а также в Цифровых синтезаторах частоты.

Цель изобретения - повышение на- дежности устройства при сохранении быстродействия и диапазона коэффициентов деления.

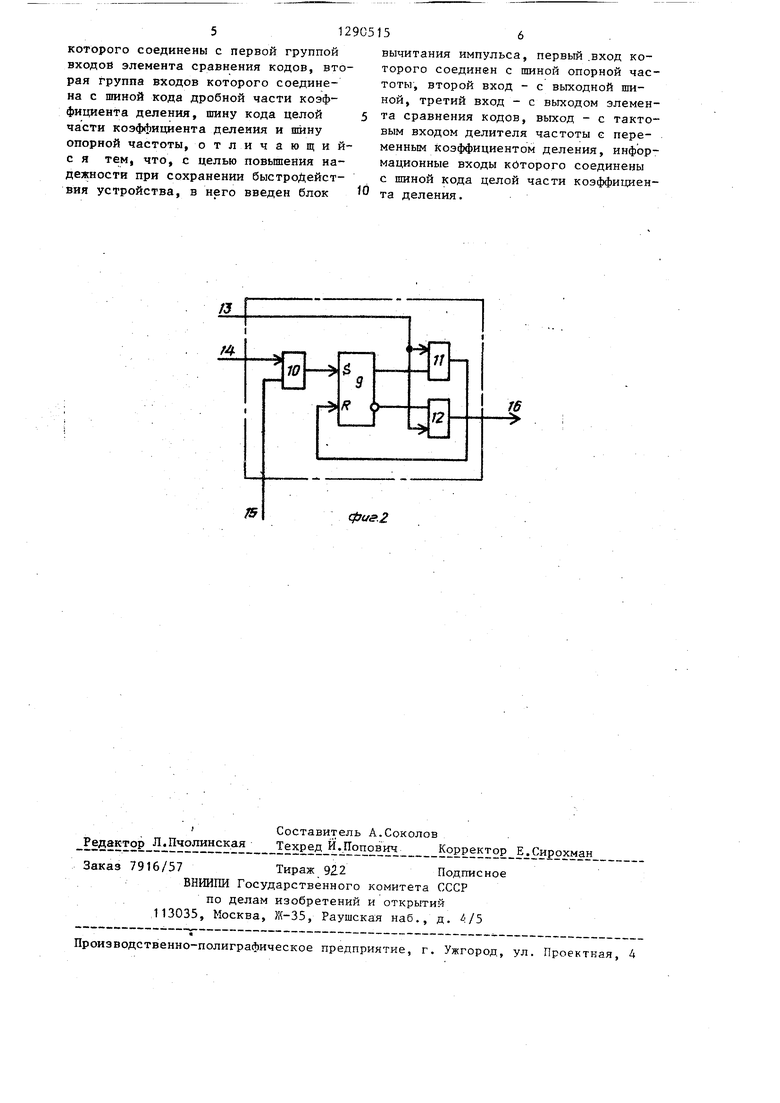

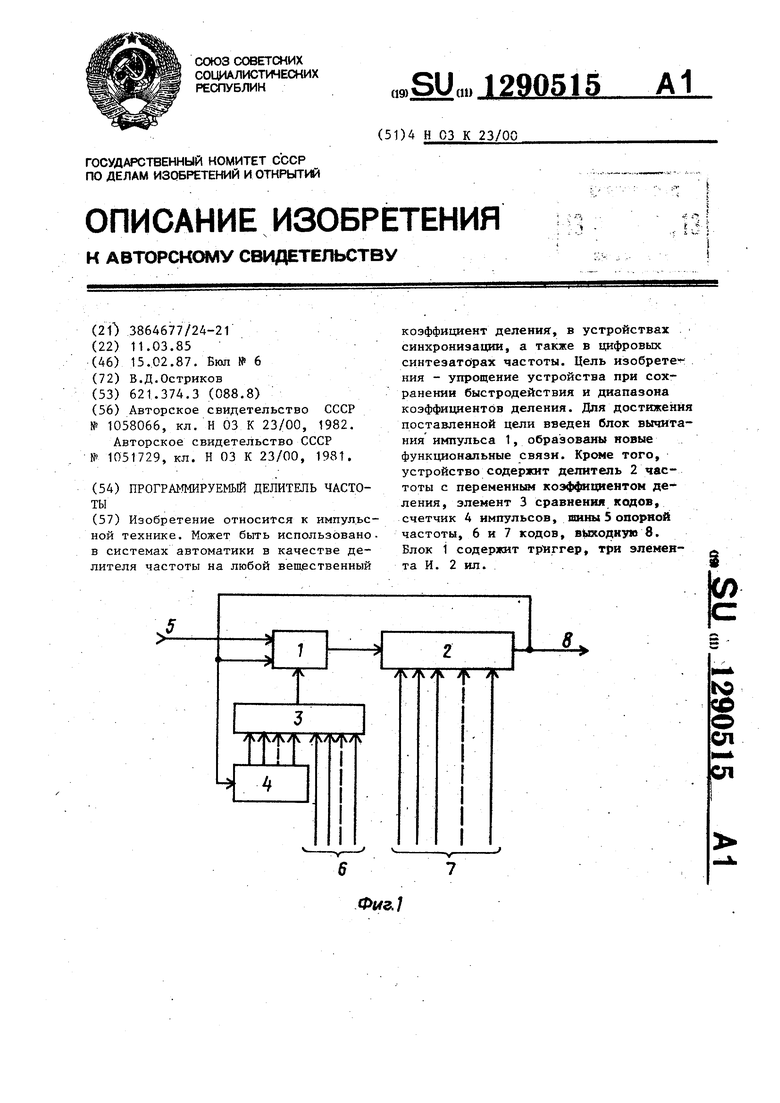

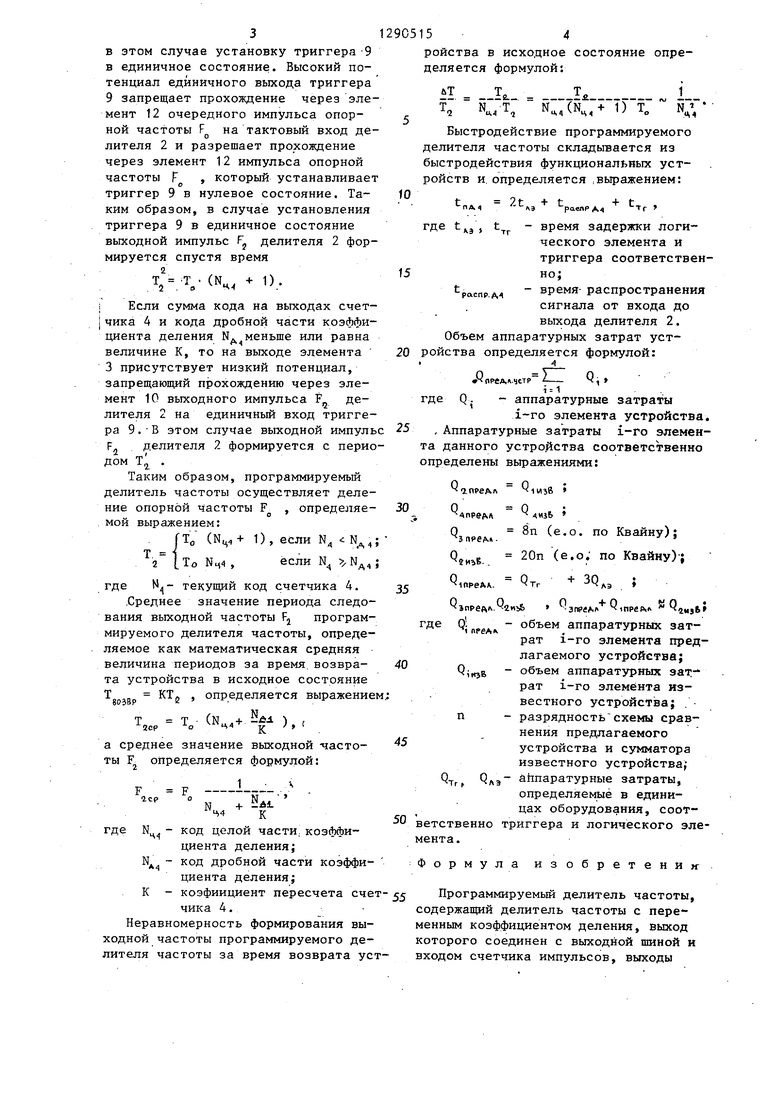

На фиг. 1 приведена электрическая структурная схема программирую- мого делителя частоты на фиг. 2 - электрическая функциональная схема блока вычитания импульса..

Программируемый делитель частоты содержит блок 1 вычитания импульса, делитель 2 частоты с переменным коэффициентом деления, элемент 3 сравнения кодов, счетчик 4 импульсов, шину 5 опорной частоты, шины б и 7 кодов соответственно дробной и целой частей коэффициентов деления и выходную шину 8, при этом шина 5 опорной частоты соединена с первым входом блока 1 вычитания импульса. Выход блока 1 вычитания импульса соединен с тактовым входом делителя 2 частоты с переменным коэффициентом деления. Шина 7 кода целой части коэффициента деления соединена с ийформадаонными входами делителя 2 частота с переменным коэффициентом деления. Выход делителя 2 частоты с переменным коэффициентом деления соединен с выходной шиной 8, вторым входом блока 1 вычитания импульса и входом счетчика 4 импульсов. Выходы счетчика 4 импульсов соединены с первой группой входов элемента 3 сравнения кодов. Шина 6 кода дробной части коэффициента деления соединена с второй группой входов элемен- та 3 сравнения кодов, выход которого соединен с третьим входом блока 1 вычитания импульса.

Блок 1 вычитания импульса .начен для выработки выходной rj , значение которой прибли к величине опорной частоты-F число импульсов определяется шением: /., N. . если Т.

N.

Тл

N

Рл

если

Тд

где N,

- число импульсов опорной частоты: Р„ г

N - число импульсов выходной

° час-тоты F ; Tj - состояние триггера 9 блока 1 вычитания импульса (см. фиг, 2).

Блок 1 вычитания импульса 1 содержит триггер 9, первый 10, второй 11 и третий 12 элементы И, первый 13, второй 14 и третий 15 входы и выход 16, Первый вход 13 опорной частоты соединен с первыми входами элементов И 11 и 12;управляющий и разрешам- щий входы 14 и 15 соединены соответственно с первым и вторым входами элемента И 10, Выход элемента И 10 соединен с установочным входом единицы триггера 9. Единичный и нулевой выходы триггера 9 соединены с вторыми входами элементов И 11 и 12 соответственно. Выход второго элемента И t1 соединен с установочным входом нуля триггера 9, Выход эле мента И 12 является выходом 16 блока 1.

Программируемый делитель частоты работает следующим образом.

За исходное состояние программи- руемог о делителя частоты принимают состояние, при котором триггер 9 блока 1 находится в нулевом состоянии, в делителе 2 находится (двоичный) код целой части коэффициента деления N, ,

Импульсы входной частоты Р„, поступающие с шины 5, через элемент 12 5 блока 1 поступают на тактовый вход ;р;елителя 2. Формирование выходного импульса F,

0

5

0

делителя 2 осуществляется в соответствии с выражением:

Т , где

41

5

L - период следования входной частоты Б (на шине 5) ;

Nц - код целой части коэффициента деления (на шине 7).

Импульсы с частотой г с выхода делителя 2 поступают на йход счетчика 4 и на второй вход блока 1,

Если сумма кода на выходах счетчика 4 и к ода дробной части коэффициента деления N,

1д присутствующего на шине 6, больше величины К, то на выходе элемента 3 присутствует вы- 5 сокий потенциал, разрещающий прохождение через элемент 10 выходного импульса F делителя 2 на единичный вход триггера 9 блока 1. Выходной импульс К делителя 2 осуществляет

3

в этом случае установку триггера -9 в единичное состояние. Высокий потенциал единичного выхода триггера 9 запрещает прохождение через элемент 12 очередного импульса опор- ной частоты F на тактовый вход делителя 2 и разрешает прохождение через элемент 12 импульса опорной частоты F , который устанавливает триггер 9 в нулевое состояние. Та- КИМ образом, в случае установления триггера 9 в единичное состояние выходной импульс FJ делителя 2 формируется спустя время

2 . .

. (N

ц-

1).

: Если сумма кода на выходах счет- 1чика 4 и кода дробной части коэффициента деления N меньше или равна величине К, то на выходе элемента 3 присутствует низкий потенциал, запрещающий прохождению через элемент 10 выходного импульса F делителя 2 на единичный вход триггера 9. В этом случае выходной импульс F. делителя 2 формируется с периодом Т .

Таким образом, программируемьш делитель частоты осуществляет деление опорной частоты F , определяе- мой выражением:

. ГТо (N, + 1), если N N,,,;

То , если N хНд,;

где текущий код счетчика 4.

.Среднее значение периода следования выходной частоты Fj программируемого делителя частоты, определяемое как математическая средняя величина периодов за время, возвра- та устройства в исходное состояние Т КТ„ , определяется выражением

803ВР It

2CP

Т„- (N. + J ),

а среднее значение выходной -часто- ты FJ определяется формулой:

F

о

1

N N + к

где N - код целой части, коэффициента деленияJ N код дробной части коэффи циента деления; К - коэфиициент пересчета счетчика 4.

Неравномерность формирования выходной частоты программируемого делителя частоты за время возврата уст15 4

ройства в исходное состояние определяется формулой:

ьТ Т„ Т„1

, N,,(N,.-b 1) Т„

N,,

Ч и,4 ,1 Ц

Быстродействие программируемого делителя частоты складьгаается из быстродействия функциональных устройств и. определяется .выражением:

ПАЧ раепРА fr

где tnj , t - время задержки логического элемента и триггера соответствено;

-раепрА время-распространени сигнала от входа до выхода делителя 2. Объем аппаратурных затрат устройства определяется формулой:

.Q

лрелл.чстр

Ы

Q,

где Q. - аппаратурные затраты

i-ro элемента устройства. , Аппаратурные затраты i-ro элемента данного устройства соответственно определены вьфажениями;

апрсАл

Q

1Изв

0

5

0

Q Q

АПРвЛЛ

0

5

4«jb

О 8п (е.о. по KBайну):

ЗПРвА.

гиъв (е.о; по Квайну)-{ QinpeAv QT. + 3Q, ; .

1пРеАЛ- 2иъ& anPiA-A ШРйАл Qa«j6

где Q - объем аппаратурных затрат i-ro элемента предлагаемого устройства; QinjB объем аппаратурных затрат i-ro элемента известного устройства; . п - разрядность схемы сравнения предлагаемого устройства и сумматора известного устройства; тг, Члэ ййпаратурные затраты, определяемые в единицах оборудования, соответственно триггера и логического элемента.

Формула изобретенииПрограммируемый делитель частоты, содержащий делитель частоты с переменным коэффициентом деления, выход которого соединен с выходной шиной и входом счетчика импульсов, выходы

которого соединены с первой группой входов элемента сравнения кодов, вторая группа входов которого соединена с шиной кода дробной части коэффициента деления, шину кода целой части коэффициента деления и шину опорной частоты, отличающий- с я тем, что, с целью повьшения надежности при сохранении быстродействия устройства, в него введен блок

12905156

вычитания импульса, первый .вход которого соединен с шиной опорной частоты, второй вход - с выходной шиной, третий вход - с выходом элемента сравнения кодов, выход - с тактовым входом делителя частоты с переменным коэффициентом деления, информационные входы которого соединены с шиной кода целой части коэффициента деления.

10

т

фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый делитель частоты следования импульсов | 1983 |

|

SU1088136A1 |

| Дробный делитель частоты следования импульсов | 1983 |

|

SU1120490A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Формирователь импульсов с регулируемой частотой следования | 1990 |

|

SU1780186A1 |

| Делитель частоты с регулируемым коэффициентом деления | 1982 |

|

SU1051732A1 |

| Цифровой частотомер | 1986 |

|

SU1377760A1 |

| Устройство для коррекции числа импульсов по входному параметру | 1984 |

|

SU1187146A2 |

| Преобразователь фазового сдвига в цифровой код | 1983 |

|

SU1104438A1 |

| Делитель частоты следования импульсов | 1982 |

|

SU1150755A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

Изобретение относится к импульсной технике. Может быть использовано, в системах автоматики в качестве делителя частоты на любой вещественный /v/yyv/v / V/ °F коэффициент деления, в устройствах синхронизации, а также в цифровых синтезаторах частоты. Цель изобретв : НИН - упрощение устройства при сохранении быстродействия и диапазона коэффициентов деления. Для достижения поставленной цели введен блок вычитания импульса 1, образованы новые функциональные связи. того, устройство содержит делитель 2 частоты с переменным коэффициентом деления, элемент 3 сравнения кодов, счетчик 4 импульсов, шины 5 опорной частоты, 6 и 7 кодов, вЪкодну 8. Блок i содержит триггер, три элемента И. 2 ил. . /V / ffk. CD о сл

| Делитель частоты | 1982 |

|

SU1058066A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Делитель частоты с дробным коэффициентом деления | 1981 |

|

SU1051729A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-02-15—Публикация

1985-03-11—Подача