со

00

Изобретение относится к вычислительной технике, в частности к устройствам для моделирования деятельности человека-оператора системы Человек-машина.

Цель изобретения - расширение функциональных возможностей зе счет моделирования деятельности оператора при наличии логических условий в алгоритме работы.

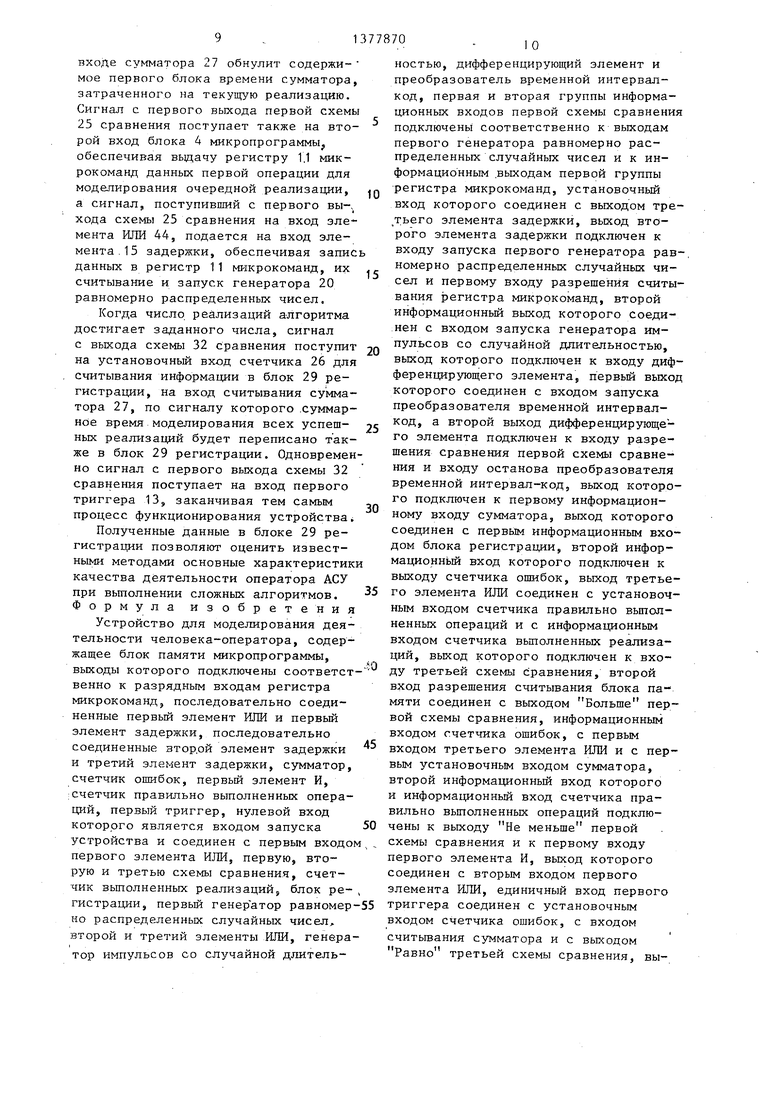

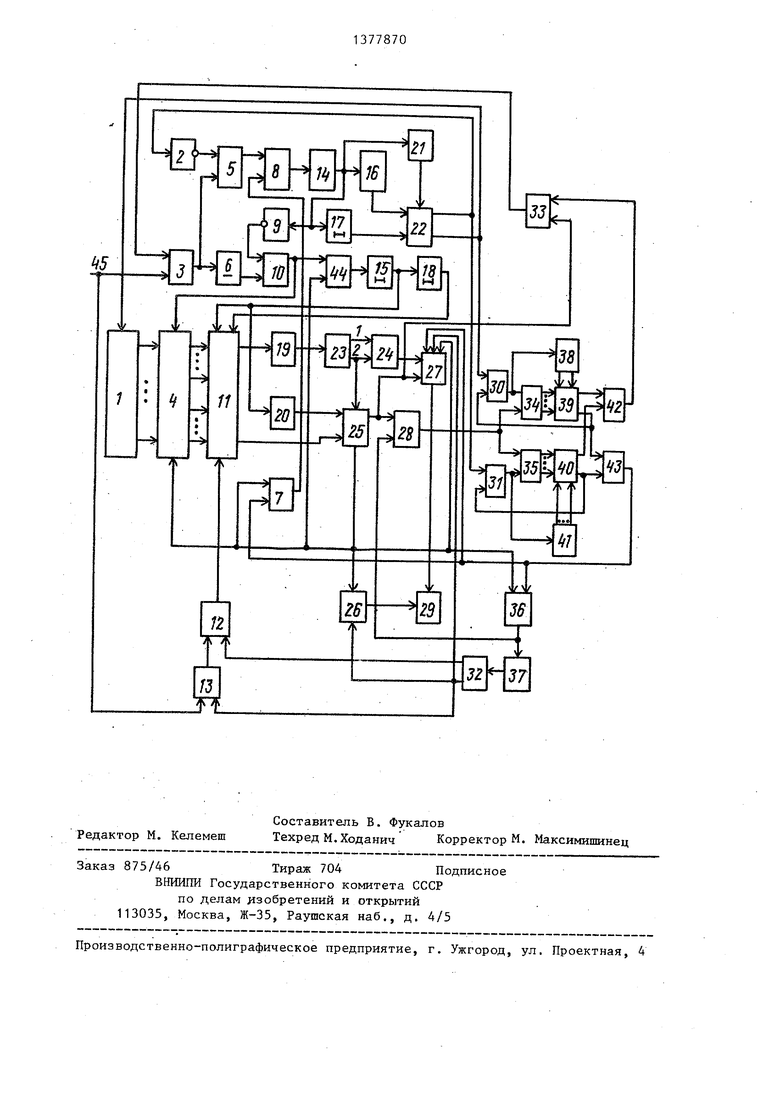

На чертеже представлена структурная схема предложенного устройства.

Устройство для моделирования деятельности человека-оператора содер- жит регистр 1 адреса микрокоманд, первьй элемент НЕ 2, первый элемент ИЛИ 3, блок 4 памяти микропрограммы, второй элемент И 5, первый элемент 6 задержки, пятый элемент ИЛИ 7, счетчик 8 контроля позиции логическо операции, второй элемент НЕ 9, трети элемент И 10, регистр 11 микрокоманд второй элемент 12 ШШ, первый триггер 13, формирователь 14 импульсов, второй элемент 15 задержки, второй генератор 16 равномерно распределенных случайных чисел, четвертый элемент .17 задержки, третий элемент 18 задержки, генератор 19 тотульсов со случайной длительностью, перв1 1й генератор 20 равномерно распределенных случайных чисел, первый регистр 21, четвертую схему 22 сравнения, дифференцирующий элемент 23, преобразова- тель 24 временной интервал - код, первую схему 25 сравнения, счетчик 26 ошибок, сумматор 27, счетчик 28 правильно вьшолненных операций, блок 29 регистрации, второй триггер 30, третий триггер 31, третью схему 32 сравнения, первый элемент И 33, первый блок 34 элементов И, второй блок 35 элементов И, третий элемент ИЛИ ШШ 365 счетчик 37 вьшолненных pea- лизацией, второй регистр 38, пятую схему 39 сравнения, вторую схему 40 сравнения, третий регистр 41, четвертый элемент И 42, четвертый 43 и 44 шестой элементы ИЛИ и вход 45 запус- ка устройства,моделирования.

Регистр 1 адреса микрокоманд предназначен для хранения управляющей составляющей алгоритма деятельности и осуществления выбора дальнейшей требуемой реализации моделируемого алгоритма в зависимости от исхода срабатывания логического условия данного алгоритма.

Блок 4 памяти микропрограммы предназначен для хранения и выдачи в регистр 11 цараметров операций моделируемого алгоритма управления. В нем хранятся данные об операционной составляющей алгоритма деятельности, вьшолнение которого моделируется. Считывание этих данных осуществляетс путем подачи сигналов на его входы, при этом при появлении сигнала от элемента И 10 производится вьщача параметров первой и всех последующих операций алгоритма, а при появлении сигнала от блока 25 в регистр вьщают ся данные только о первой операции алгоритма, что соответствует началу новой реализации алгоритма при условии, что предьщущая реализация была завершена безуспешно. Другими словами, оператор не выполнил в этот раз задачи управления. Блок 4 памяти разделен на две зоны, причем в перво его зоне хранятся значения математического ожидания и среднеквадратичес кого отклонения времени вьтолнения каждого типа элементарных операций алгоритма. Данные значения размещены в порядке следования операций при выполнении алгоритма управления. Во второй зоне располагаются значения вероятностей безошибочного выпол нени соответствующего типа элементарных операций алгоритма Р ,.

Эти параметры характеризуют операционную составляющую, а порядок их следования в соответствии с очеред- ностью выполнения элементарных операций - управляющую составляющую моделируемого алгоритма деятельности.

Элементы 6,15 и 18 задержки предназначены для организации надежной записи и считывания данных из блока 4 памяти микропрограммы в регистр 11 микрокоманд.

Счетчик 8 контроля позиции логической операции в схеме моделируемого алгоритма представляет собой вычитающий счетчик. В исходном состоянии в нем записано число, соответствующее номеру логической операции алгоритма (в рассматриваемом случае число 5). Он предназначен для запуск формирователя 14 импульсов.

Регистр 11 микрокоманд осуществляет хранение и выдачу трех микроопераций, поступающих от блока 4 памяти.

10

}5

Триггер 13 управляет включением и выключением устройства.

Формирователь 14 импульсов предназначен для выработки сигнала, длительность которого равняется требуемой длительности запирания элемента И 10.

Генератор 19 импульсов со случайной длительностью служит для выдачи импульсов случайной длительности, распределенных по необходимому закону с .параметрами, вьщаваемыми блоком 4 памяти микропрограммы.

Питание на генераторы 16,19 и 20 подается по сигналу, определяющему начало функционирования устройства (цепи подачи питания на схеме устройства не показаны).

В схеме 22 сравнения при поступлении от элемента 17 задержки импульса производится сравнение случайного числа Хц, выработанного ранее по команде с формирователя 14 импульсов генератора 16 со значением вероятнос-25 ти срабатывания логического условия Рд, , которое пер.ед началом работы записывается в регистр 21.

Элемент 23 вьщеляет импульс на- ала и импульс окончания импульсов до формированных генератором 19 для альнейшего преобразования отрезка ремени в код в преобразователе 24.

В схеме 25 сравнения при поступлеии от элемента 23 импульса Конец

20

35

производится сравнение случайного числа х, вьфаботанного ранее по команде с выхода второго элемента 15 задержки, генератором 20 со значением вероятности безошибочного вьтол нения операции данного типа Р, , переписанного в схему 25 сравнения с регистра 11 микрокоманд. В результате сравнения этих чисел определяется безошибочность выполнения текущей операции алгоритма. В случае, если . , то операция считается вьшол- ненной правильно, в противном случае засчитывается ошибка, на этом моделирование данной реализации прекращается, подачей сигнала на второй вход блока 4 памяти микропрограммы и вход элемента ИЛИ 44 обеспечиваетс моделирование очередной реализации с первой операции алгоритма.

Счетчик 26 подсчитьгоает число опш- бок, допущенных при выполнении алгоритма,, что соответствует числу без10

}5

-25

до

20

- я

- 377870

успешных реализаций, т.е. попыток вьтолнения алгоритма.

Сумматор 27 осуществляет суммирование всех значений временных интервалов вьтолнения операций как за одну, так и за все операции алгоритма, и за все успешные его реализации. При этом в случае, если при вьтолне- нии алгоритма оператором -допущена ошибка, т.е. алгоритм не вып.олнен, значения всех предыдуш х до данной операции временных затрат стираются и с безошибочными реализациями не суммируются.

Счетчик 28 числа правильно выполненных операций подсчитывает число правильно вьшолненных операций для дальнейшего сравнения с числом операций, содержащихся в алгоритме управления, что позволяет определить момент завершения -выполнения задачи управления оператором и перех од к новой реализации.

Число операций моделируемого алгоритма в зависимости от результата срабатьгоания логического условия устанавливается в регистрах 38,41 перед началом моделирования.

Блок 29 регистрирует по окончании моделирования число безуспешных попыток выполнения алгоритма, т.е. содержимое счетчика 26, а также значение общего времени моделирования

всех успешных реализаций алгоритма

I

т.е. содержимое сумматора 27.

Триггеры 30,31 предназначены для выдачи разрешающих сигналов на перезапись информации из счетчика 28 в схемы 39,40 сравнения.

Счетчик 37 подсчитывает число проведенных реализаций, причем как успешных, так и ошибочных для сравнения в схеме 32 сравнения с требуемым числом реализаций. Это число записывается в схему 32 сравнения также перед началом моделирования и определяется исходя из требуемой точности результатов моделирования.

Элементы 1,4 и 11 в совокупности представляют собой блок микропрограммного управления, который является аппаратной реализацией математической- модели автоматного представления алгоритма деятельности оператора.

Рассмотрим процесс моделирования заданного алгоритма, например следующей логической схемой алгоритма (ЛСА):

35

40

45

50

55

А1А2АЗА4 рЧЗАб ; А7А8А9А10А11 .

В случае, если при сравнении значений в схеме 22 сравнения , моделирование алгоритма должно перейти после четвертой операции к седьмой операции, т.е. к выбору следующей реализации.

А1А2АЗА4А7А8А9А10А11 , (1) в противном случае моделироваться будет другая реализация алгоритма, а именно

А1А2АЗА4А5А6А7А8А9А10А1Г. (2)

Устройство функционирует следующим образом.

После подачи на вход 45 устройства сигнала Пуск включаются генераторы 16,19 и 20, первый и третий из которых подготавливаются к генерации случайных равномерно распределенных чисел, а второй - к формированию последовательности импульсов случайной длительности. Кроме того, импульс запуска через элемент ИЛИ 3 поступает на вход элемента И5 и на вход элемен- та 6 задержки, время задержки которого устанавливается в- зависимости от выхода на заданньш режим работы генераторов 16,19 и 20, в то же время

она больше задержки переходных про

цессов в цепи: блоки 5-8-14-16-22-1-4 Сигнал с выхода элемента 6.задержки поступает на вход элемента И10, ко- торьм срабатывает, так как на другом его входе имеется сигнал с вькода элемента НЕ 9, а выходньм сигналом, поступающим на первый вход считьша- ния блока 4 памяти микропрограммы, элемент И10 производит считывание данных из обеих зон в регистр 11 микрокоманд для моделирования вьшол- нения первой операции. Кроме того, сигнал с выхода элемента И 10 поступает на вход элемента ИЛИ 44, с выхода которого он поступает на элемент 15 задержки. Время его задержки выбирается исходя из продолжительности перезаписи информации из блока 4 микропрограммы в регистр 11 микрокоманд. Сигнал с выхода элемента 15 задержки поступает на вход третьего элемента 18 задержки, на вход генератора 20 равномерно распределенных случайных чисел и на вход разрешения считывания регистра 11 микрокоманд. По этому сигналу осуществляется перезапись значений параметров моделируемой операции в генератор 19 и схему 25 сравнения соответственно. Генера

Q

г

0 5

0

0

5

5

тор 19 начинает формирование импульсов случайной длительности, которые поступают на вход дифференцирующего элемента 23. Величина задержки времени элементом 18 задержки обеспечивает надежное считывание информации из регистра 11. При поступлении сигнала с выхода элемента 18 задержки на установочньй вход регистра 11 микрокоманд производится обнуление регистра.

Сигнал Начало с первого выхода дифференцирующего элемента 23 поступает на первый вход преобразователя

24временной интервал-код, а сигнал Конец - с второго выхода дифференцирующего элемента 23 на второй вход преобразователя 24, формируя код продолжительности временного интервала. Одновременно сигнал Конец дает команду на сравнение первой схеме

25сравнения. В ней сравнивается случайное равномерно; распределенное число со значением вероятности без- ошибочного вьшолнения операции данного типа. В том случае, если ., операция считается вьшолненной безошибочно и импульс с второго выхода схемы 25 сравнения поступает на вход элемента И 33. При наличии сигнала на втором входе элемента 33 И, т.е. если не все операции алгоритма выполнены, происходит подача этого сигнала на. вход элемента ИЛИ 3 и весь цикл работы, но уже для моделирования второй операции алгоритма, повторяется. Кроме того, .импульс с второго выхода схемы 25 сравнения поступает на первьй информационный вход сумматора 27 и на информационный вход счетчика 28 числа правильно выполненных операций. Сумматор 27 состоит из двух блоков, в первом

подсчитывается время моделирования текущей реализации, а во втором - время предыдущих, успешно выполненных реализаций. Если реализация будет завершена успешно, то время ее моделирования будет суммироваться с содержимым второго блока сумматора 27 за. счет появления сигнала на его втором установочном входе, в противном случае, т.е. при неуспешной реализации сигнал на первом установочном входе сумматора 27 обнулит содержимое первого блока. С выхода счетчика 28 число успешных операций поступает на входы блоков 34,35 элементов И, которые не срабатывают из-за отсутствия .разрешающего сигнала на управляющих входах. С вторых выходов схем 39,40 сравнения снимается постоянньй еди- ничньм сигнал до тех пор, пока не будут вьтолнены все операции алгоритма управления (1) или (2). Когда все операции соответствующего алгоритма будут выполнены успешно, единичньш импульс с первого выхода схемы 39 или 40 сравнения поступит через элементы ИЛИ 43, 36 на счетчик 37 для подсчета общего числа реализаций. Одновременно сигнал с выхода элемента ИЛИ 36 поступит на установочный вход счётчика 28 и обнулит его содержимое, подготовив его тем самым к подсчету числа успешных операций в очередной реализации. С второго выхода схемы 32 сравнения через элемент ИДИ 12 на второй вход регистра 11 будет поступать сигнал до тех пор пока не будет произведено заданное

число реализаций. При каждой успешно перезапись информации со счетчика 28

вьшолненной операции срабатывает элемент И 5 и счетчик 8 каждьш раз вычитает из своего содержимого единицу. Как только устройство начинает моделировать логическую операцию (в данном случае пятую операцию) алгоритма счетчик 8 вьграбатьшает сигнал, который поступает на формирователь 14 импульсов, выходным импульсом который запускает генератор 16 равномерно распределенных случайных чисел. Одновременно выходной импульс с формирователя 14, длительность которого равняется требуемой длительности запирания элемента И 10, поступает на вход элемента 17 задержки, на вход регистра 21 и на вход элемента НЕ 9, который запрещает (до выбора требуе. мой реализации алгоритма) моделирование очередной операции. Сигнал, задержанный элементом 17 задержки на время перезаписи информации из гене- рат.ора 16 и регистра 21 в схему 22 «гравнения, дает команду на сравнение информации в четвертой схеме 22 сравнения. В ней сравнивается случайное равномерно распределенное число со значением вероятности срабатывания логического условия, записанного в первом регистре 21. В том случае, если , сигнал появляется на втором выходе схемы 22 сравнения, на входе элемента НЕ2 и на единичном входе-триггера 31, вькодным сигналом

30

35

40

45

50

55

и регистра 38 в схему 39 сравнения. Если вьшолнены не все операции алгоритма, то сигналы с выходов схем 39 и 40 продолжают поступать на входы элемента И 42. Выходными сигналами регистр 1 адреса микрокоманд обеспечивает обращение к зонам памяти блока 4 микропрограммы, где хранятся значения предшествующей операции очередного моделирования, т.е. А6, а при поступлении задержанного сигнала на первьм вход блока 4 произойдет считьшание данных из обеих зон уже для операции А7. Дальнейшая работа устройства в этом случае уже описа- . на.

Если при сравнении значений в первой схеме 25 сравнения окажется XjiPj , то операция считается невыполненной. В этом случае с первого выхода первой схемы 25 сравнения поступит на счетчик 26 подсчета числа безуспешных реализаций, на вход элемента ИЛИ 36 для подсчета общего числа реализаций в счетчике 37 и обнуления счетчика 28 для подготовки его к новой реализации. Одновременно сигнал с первого выхода схемы 25 сравнения поступает через элемент ИЛИ 7 на установочный вход счетчика 8 контроля позиции логической операции в схеме моделируемого алгоритма приводя его в исходное состояние. Кроме того, сигнал на установочном

0

5

0

который разрешает перезапись информации со счетчика 28 и регистра 41 в схему 40 сравнения. Если операции алгоритма вьшолнены не все, то сигнал с второго выхода продолжает поступать как со схемы 39 сравнения, так и со схемы 40 сравнения на элемент И 42, выходной сигнал которого поступит на вход элемента И 33. Элемент И 33 сра- батьтает так как предьщущая операция выполнена верно и на его входе имеется сигнал с второго выхода схемы 25 сравнения. Выходной сигнал элемента И 33 поступает на вход элемента РИГИ 3. Далее произойдет моделирование реализации (2) алгоритма по описанному принципу.

В том случае, если при сравнении значений в схеме 22 , , сигнал появится на первом ее выходе, на входе регистра 1 адреса микрокоманд и на единичном входе триггера 30, сигнал с выхода которого разрешает

0

5

0

5

0

5

и регистра 38 в схему 39 сравнения. Если вьшолнены не все операции алгоритма, то сигналы с выходов схем 39 и 40 продолжают поступать на входы элемента И 42. Выходными сигналами регистр 1 адреса микрокоманд обеспечивает обращение к зонам памяти блока 4 микропрограммы, где хранятся значения предшествующей операции очередного моделирования, т.е. А6, а при поступлении задержанного сигнала на первьм вход блока 4 произойдет считьшание данных из обеих зон уже для операции А7. Дальнейшая работа устройства в этом случае уже описа- . на.

Если при сравнении значений в первой схеме 25 сравнения окажется XjiPj , то операция считается невыполненной. В этом случае с первого выхода первой схемы 25 сравнения поступит на счетчик 26 подсчета числа безуспешных реализаций, на вход элемента ИЛИ 36 для подсчета общего числа реализаций в счетчике 37 и обнуления счетчика 28 для подготовки его к новой реализации. Одновременно сигнал с первого выхода схемы 25 сравнения поступает через элемент ИЛИ 7 на установочный вход счетчика 8 контроля позиции логической операции в схеме моделируемого алгоритма приводя его в исходное состояние. Кроме того, сигнал на установочном

входе суьматора 27 обнулит содержи- мое первого блока времени сумматора, затраченного на текущую реализацию. Сигнал с первого выхода первой схемы 25 сравнения поступает также на второй вход блока 4 микропрограммы обеспечивая вьщачу регистру 1,1 микрокоманд данных первой операции для моделирования очередной реализации, а сигнал, поступивший с первого вы-, хода схемы 25 сравнения на вход элемента ИЛИ 44, подается на вход элемента. 15 задержки, обеспечивая запис данных в регистр 11 микрокоманд, их считывание и запуск генератора 20 равномерно распределенных чисел.

Когда число реализаций алгоритма достигает заданного числа, сигнал с выхода схемы 32 с:равнения поступит на установочньй вход счетчика 26 для считывания информации в блок 29 регистрации, на вход считывания сумматора 27, по сигналу которого .суммарное время моделирования всех успешных реализаций будет переписано также в блок 29 регистрации. Одновременно сигнал с первого выхода схемы 32 сравнения поступает на вход первого триггера 13, заканчивая тем самым процесс функционирования устройства

Полученные данные в блоке 29 регистрации позволяют оценить известными методами основные характеристик качества деятельности оператора АСУ при вьшолнении сложных алгоритмов. Формула изобретения

Устройство для моделирования деятельности человека-оператора, содержащее блок памяти микропрограммы, выходы которого подключены соответственно к разрядньгм входам регистра микрокоманд, последовательно соединенные первый элемент ИЛИ и первьй элемент задержки, последовательно соединенные второй элемент задержки и третий элемент задержки, сумматор, счетчик ошибок, первый элемент И, : счетчик правильно выполненных операций, первый триггер, нулевой вход которого является входом запуска устройства и соединен с первым входо первого элемента ИЛИ, первую, вторую и третью схемы сравнения, счетчик выполненных реализаций, блок ре- гистрации, первьш генер атор равномер но распределенных случайных чисел, второй и третий элементы ЯЛИ, генератор импульсов со случайной длитель

0

5

0

5

. .. 5

0

5

5

0

ностью, дифференцирующий элемент и преобразователь временной интервал- код, первая и вторая группы информационных входов первой схемы сравнения подключены соответственно к выходам первого генератора равномерно распределенных случайных чисел и к информационным .выходам первой группы регистра микрокоманд, установочный вход которого соединен с ВЕ КОДОМ тре- тьего элемента задержки, выход второго элемента задержки подключен к входу запуска первого генератора рав-, номерно распределенных случайных чисел и первому входу разрешения считывания регистра микрокоманд, второй информационньш выход которого соединен с входом запуска генератора импульсов со случайной длительностью, выход которого подключен к входу дифференцирующего элемента, первьм выход которого соединен с входом запуска преобразователя временной интервал- код, а второй выход дифференцирующего элемента подключен к входу разре- щения сравнения первой схемы сравнения и входу останова преобразователя временной интервал-код, выход которого подключен к первому информационному входу сумматора, выход которого соединен с первым информационным входом блока регистрации, второй инфор- мационньй вход которого подключен к выходу счетчика ошибок, выход третьего элемента ИЛИ соединен с установочным входом счетчика правильно выполненных операций и с информационным входом счетчика вьшолненных реализаций, выход которого подключен к входу третьей схемы сравнения, второй вход разрешения считывания блока па мяти соединен с выходом Больще первой схемы сравнения, информационным входом счетчика ошибок, с первым входом третьего элемента ИЛИ и с первым установочным входом сумматора, второй информационный вход которого и информационньй вход счетчика правильно выполненных операций подключены к выходу Не меньше первой схемы сравнения и к первому входу первого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, единичный вход первого триггера соединен с установочным входом счетчика ошибок, с входом считьшания сумматора и с выходом Равно третьей схемы сравнения, вы1377870

одключен к : элемента ИЛИ, оединен с вы, а выход втолючен к второму ания регистра чающеег расширения остей устройст-jo ия деятельносии логических боты, оно доегистр адреса второй элемен- и четвертью нтроля позиции етвертый элегенератор -равслучайных 20

с ин ве вы ны да ря ко ад пр ад ни вы не вх ве ре ны к ме а то до вх ми эл с вт хо вы с мя ше ко пе то вт ты пу ра кл пу вы по нб вы вх Б а по с и со ме та ни вы ср

чисел, первьй, второй и третий ре гистры, четвертую и пятую схемы сравнения, второй и третий триггеры, первый и второй блоки элементов И, четвертый, пятый и шестой элементы ИЛИ и формирователь импульсов, причем выход четвертого элемента ИЛИ соединен с вторыми входами третьего и пятого элементов mHi и вторым установочным входом сумматора, первый вход четвертого элемента ИЛИ соединен с нулевым входом третьего триггера и выходом Больше второй схемы сравнения, первая группа информационных входов которой подключена к выходам второго блока элементов И, управляюрщй вход которого соединен с единичным выходом третьего триггера и входом считывания третьего регистра, разрядные выходы которого подключены к информационным входам второй группы второй схемы сравнения выходом Меньше которой соединен с первым входом четвертого элемента И, выход которого подключен к второму входу первого элемента И, а второй вход четвертого элемента И соединен с выходом Меньше пятой схемы сравнения, выход Равно которой подключен к второму входу четвертого элемента ИЛИ и к нулевому входу второго триггера, единичньш выход которого соединен с управляющим входом первого блока элементов И и с входом считывания второго регистра, разрядные выходы которого подключены к инфор- мационным входам второй группы пятой схемы сравнения, первая группа информационных входов которой соединена

12

o 0

0

5 5

5

0

5

0

с выходами первого блока элементов И, информационные входы которого соответственно подключены к разрядным выходам счетчика правильно вьшолн ен- ных операций и к информационным входам второго блока элементов Pi, разрядные выходы регистра адреса микрокоманд соединены соответственно с адресными входами блока памяти микропрограммы, а вход считывания регистра адреса микрокоманд подключен к единичному входу второго триггера и к выходу Больше четвертой схемы сравнения, первая группа информационных входов которой соединена соответственно с paзpяднь мзi выходами первого регистра, вторая группа информационных входов подключена соответственно к выходам второго генератора равномерно распределенных случайных чисел а вход разрешения сравнения четвертой схемы сравнения соединен с выходом четвертого элемента задержки, вход которого подключен к выходу формирователя импульсов и входу второго элемента НЕ, выход которого соединен с первым входом третьего элемента И, второй вход которого подключен к вы ходу первого элемента задержки, а выход третьего элемента И соединен с первым входом считывания блока памяти микропрограммы и первым входом шестого элемента ИЛИ, второй вход которого соединен с выходом Больше первой схемы сравнения, а выход шестого элемента ИЛИ подключен к входу второго элемента задержки, вход считывания первого регистра и вход запуска второго генератора равномерно распределенных случайных чисел под ключены к выходу формирователя импульсов, вход которого подключен к выходу обнуления счетчика контроля позиции логической операции, уста- нбвочньш вход которого соединен с выходом пятого элемента ИЛИ, первый вход которого подключен к выходу Больше первой схемы сравнения, а вычитающий вход счетчика контроля позиции логической операции соединен с выходом второго элемента И, первый и второй входы которого подключены соответственно к выходу первого элемента ИЛИ и к выходу первого элемента НЕ, вход которого соединен с единичным входом третьего триггера и с выходом Не больше четвертой схемы сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования алгоритма деятельности человека-оператора | 1989 |

|

SU1621042A1 |

| Устройство управления тренажером операторов | 1989 |

|

SU1714645A1 |

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОПЕРАТОРОВ | 1991 |

|

RU2011226C1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Устройство для обучения операторов | 1989 |

|

SU1661820A2 |

| Устройство для обучения операторов | 1989 |

|

SU1730651A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

| Устройство для обучения операторов | 1987 |

|

SU1492366A1 |

| Устройство для обучения операторов | 1991 |

|

SU1786500A1 |

| МОДУЛЬ МИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1997 |

|

RU2112272C1 |

Изобретение относится к вычислительной технике, в частности к устройствам для моделирования деятельности человека-оператора системы- Человек-машина. Цель изобретения- расширение функциональных возможностей устройства за счет моделирования деятельности оператора при наличии логических условий в алгоритме работы. Устройство содержит блок памяти микропрограммы, регистр микрокоманд, первьй, второй и третий элеме нты задержки, первьш, второй и третий элементы ИЛИ, сумматор, счетчик ошибок, первый элемент И, счетчик правильно выполненных операций, первый триггер, первую, вторую и третью схемы сравнения, счетчик вьтолненных реализаций, блок регистрации, первый генератор равномерно распределенных слу- чайных чисел, генератор импульсов со случайной длительностью, дифференцирующий элемент и преобразователь временной интервал-код. Полученные данные в блоке регистрации позволяют оценить известными методами основные характеристики качества деятельности оператора АСУ при вьшолнении сложных алгоритмов. 1 ил. i (Л

| Устройство для моделирования деятельности человека-оператора систем "человек-машина | 1982 |

|

SU1053109A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования деятельности человека-оператора | 1984 |

|

SU1164726A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-28—Публикация

1986-09-08—Подача