Физ,Г

Изобретение относится к импульс- ной технике и может использоваться в радиотехнике и в вычислительной технике.

. Целью изобретения является расширение функциональных возможностей генератора псевдослучайных последовательностей за счет обеспечения возможности регулирования длительности серий одноименных символов.

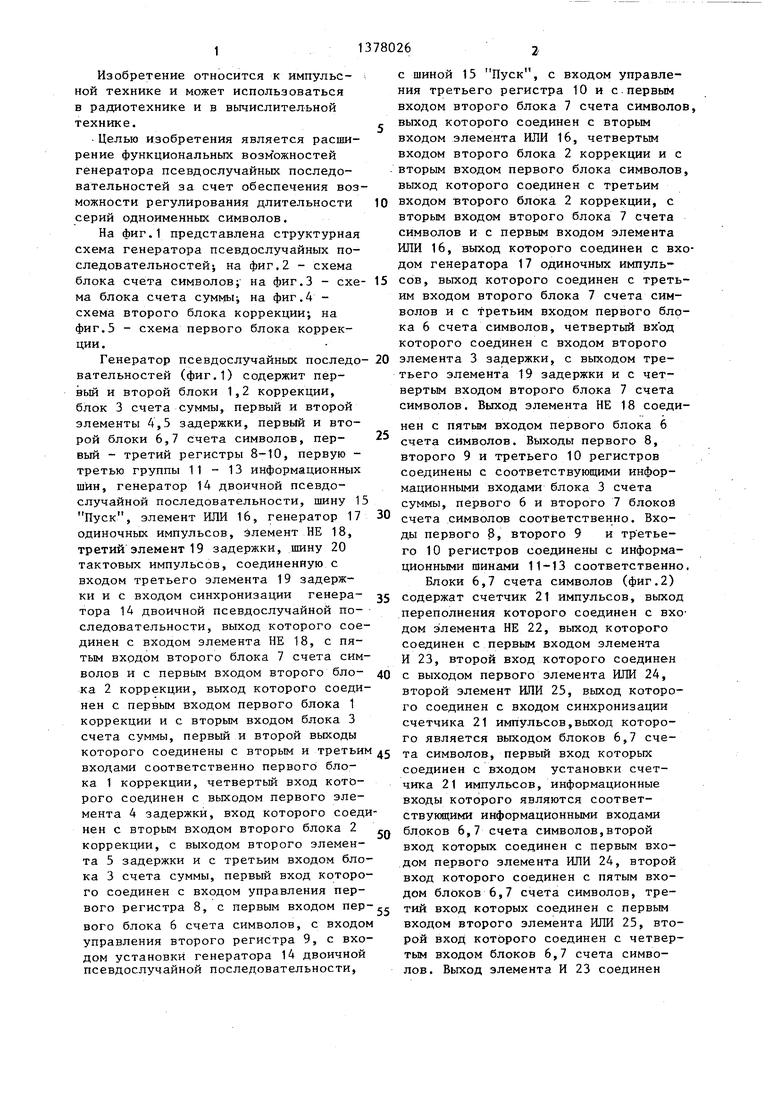

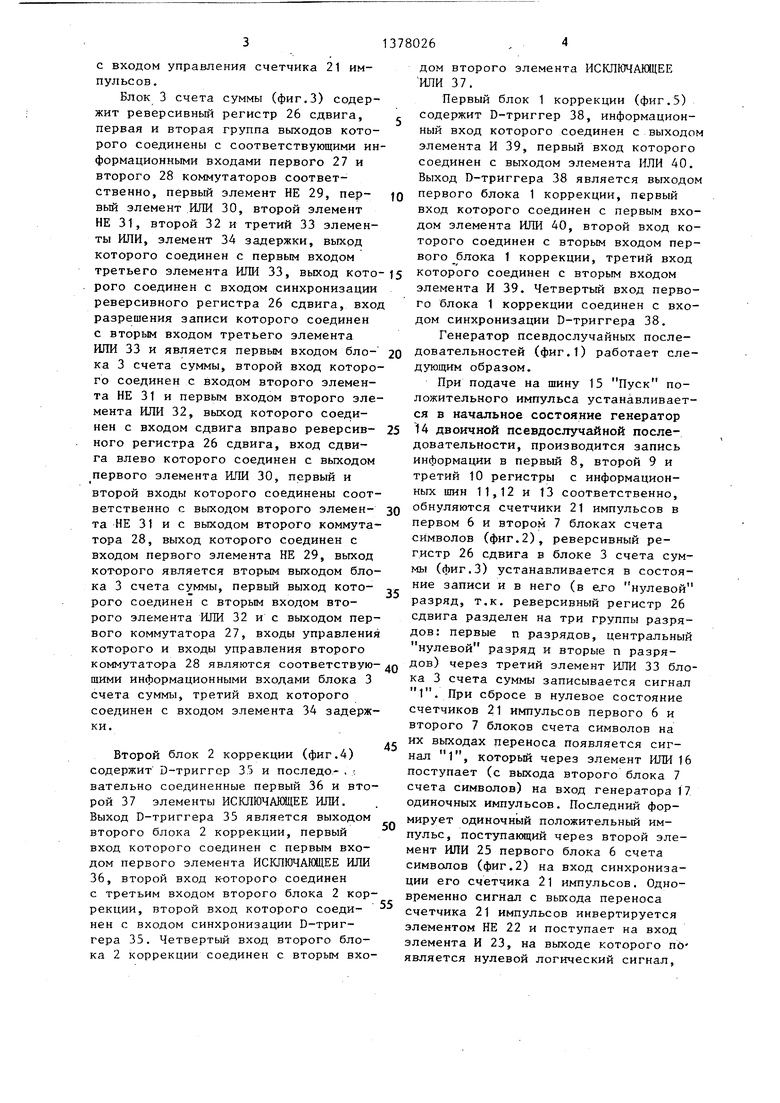

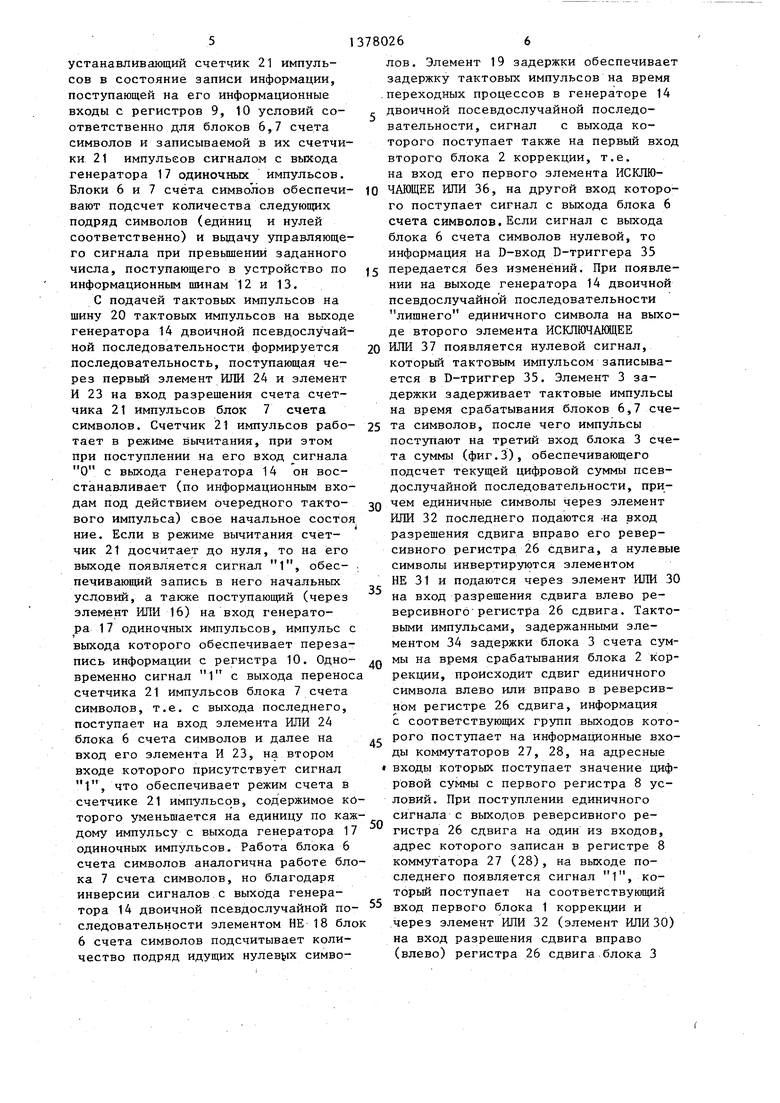

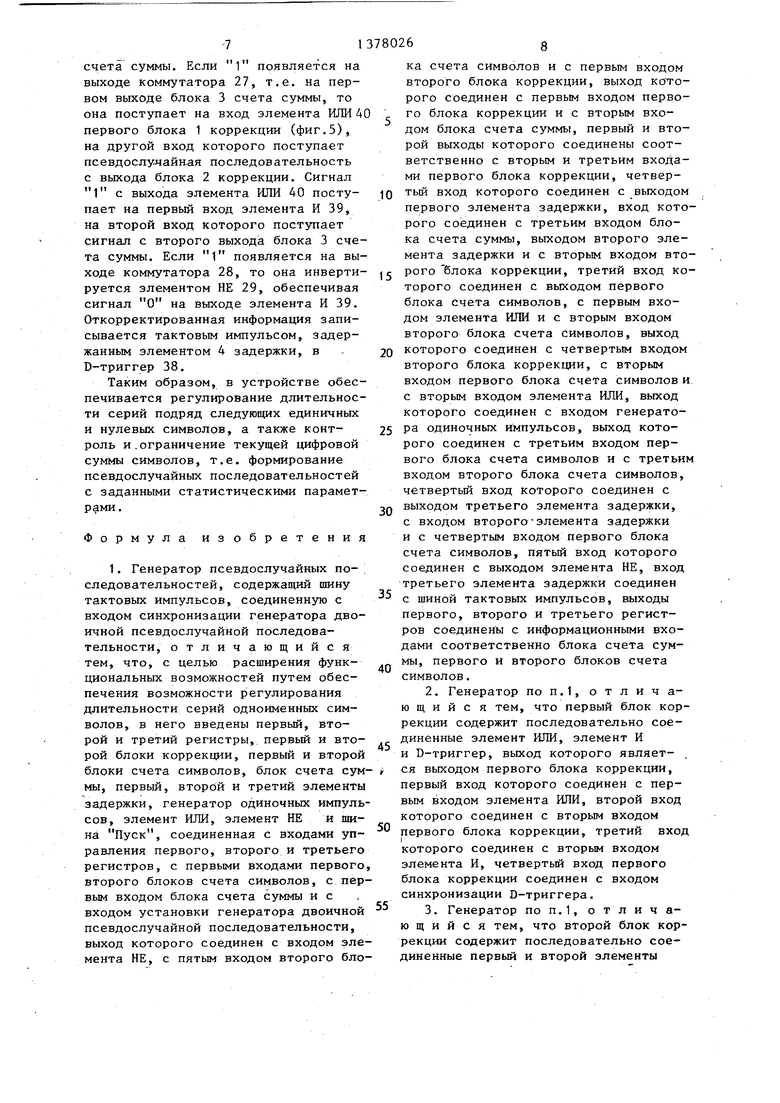

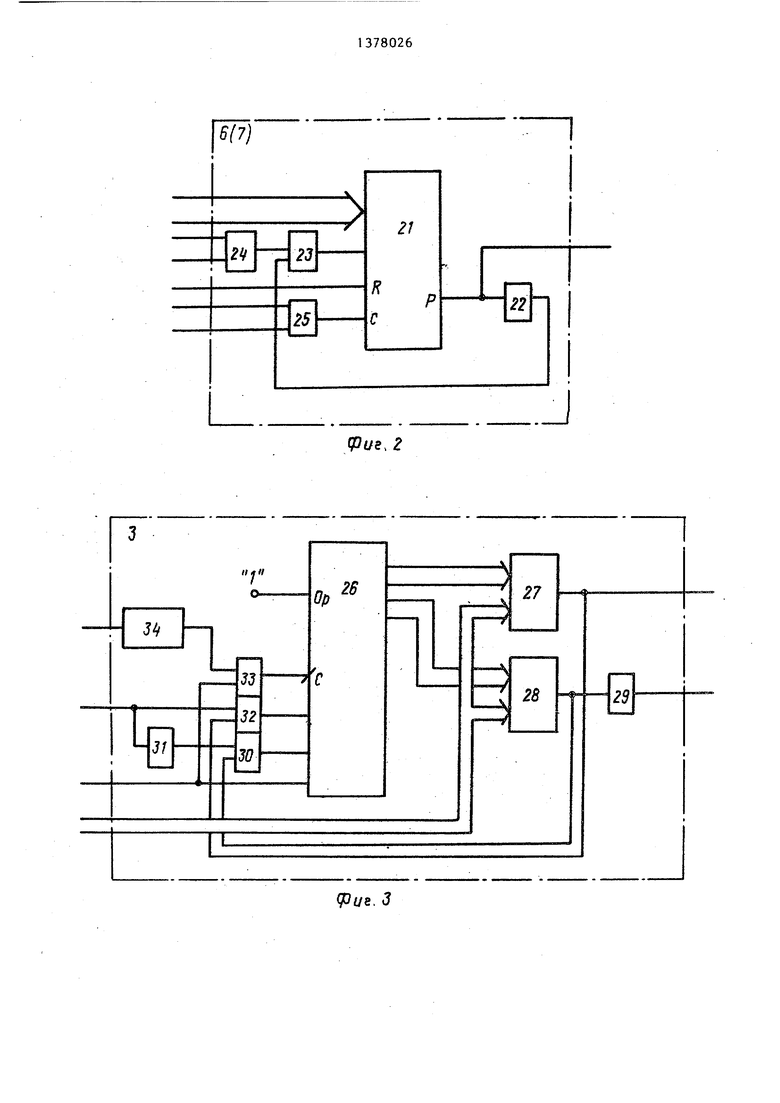

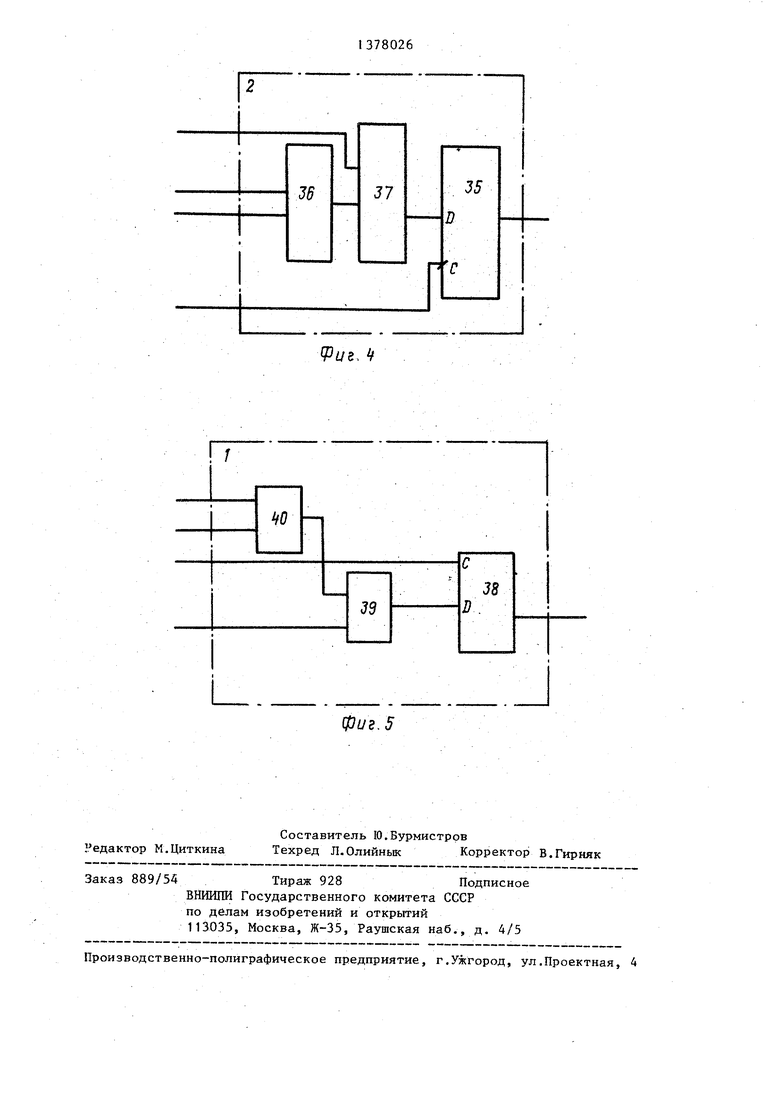

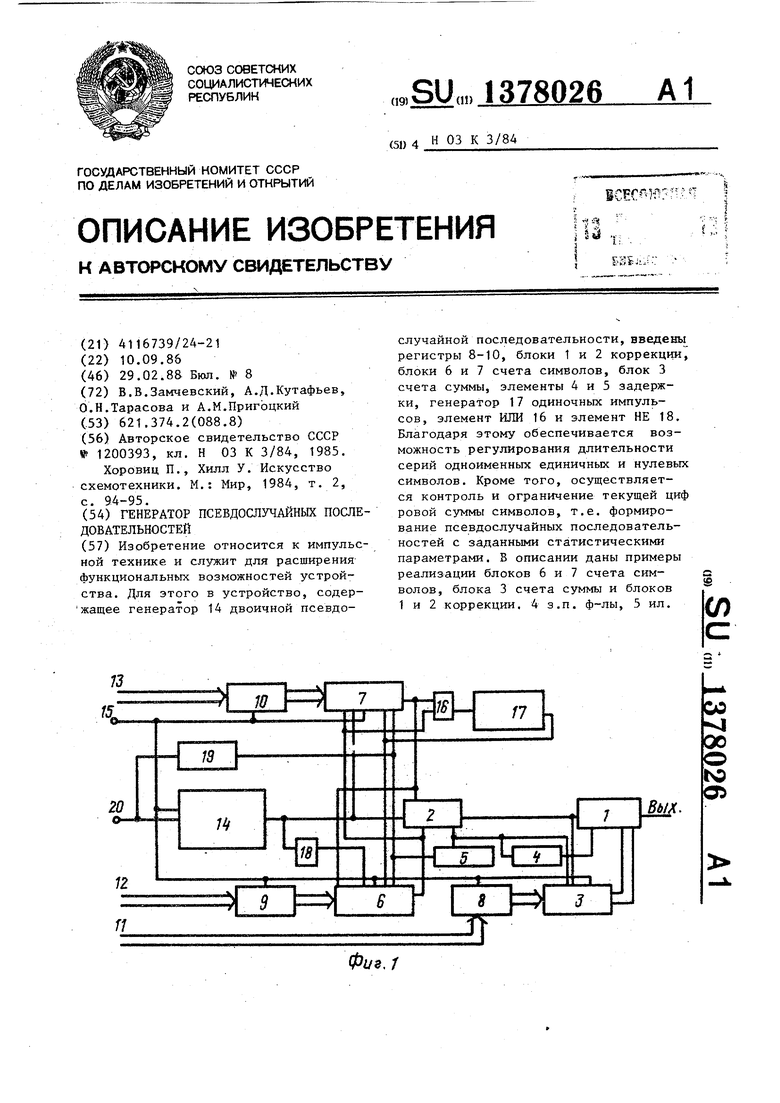

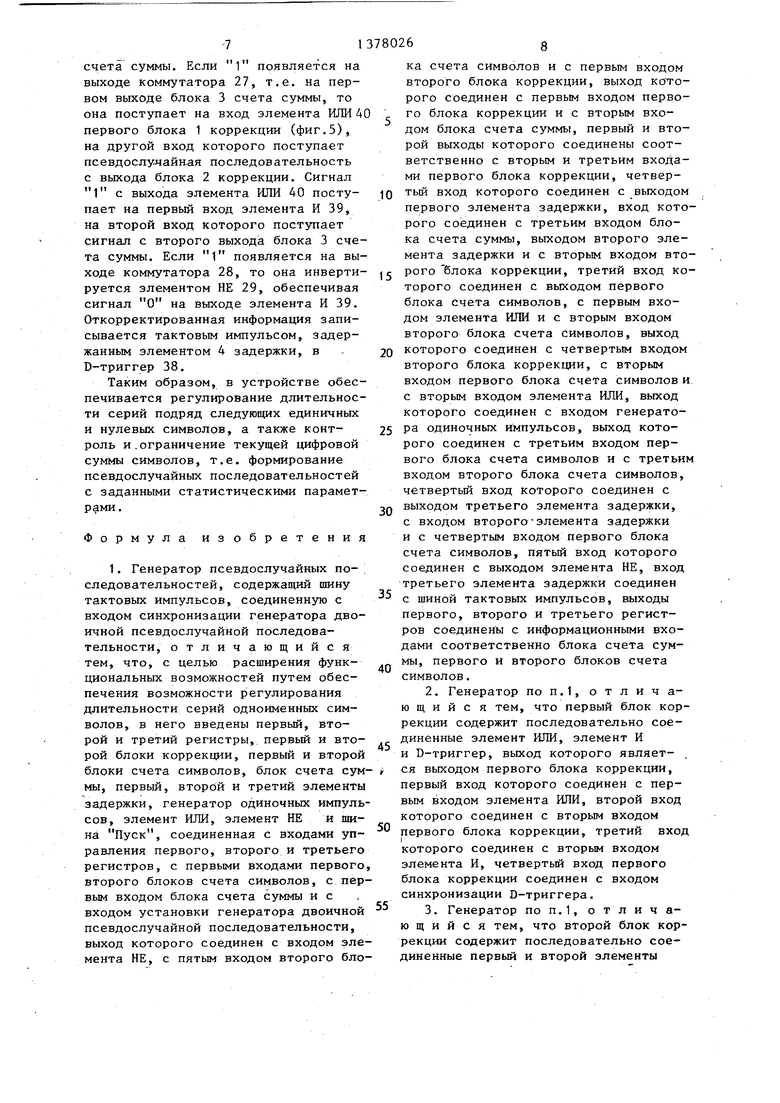

На фиг.1 представлена структурная схема генератора псевдослучайных последовательностей; на фиг.2 - схема блока счета символов; на фиг.З - схе ма блока счета суммьц на фиг.4 - схема второго блока коррекции; на фиг.З - схема первого блока коррекции.

Генератор псевдослучайных последо вательностей (фиг.1) содержит первый и второй блоки 1,2 коррекции, блок 3 счета суммы, первый и второй элементы 4,5 задержки, первый и второй блоки 6,7 счета символов, пер- вый - третий регистры 8-10, первую - третью группы 11-13 информационных шин, генератор 14 двоичной псевдослучайной последовательности, шину 1 Пуск, элемент ИЛИ 16, генератор 17 одиночных импульсов, элемент НЕ 18, третий элемент 19 задержки, шину 20 тактовых импульсов, соединенную с входом третьего элемента 19 задержки и с входом синхронизации генера- тора 14 двоичной псевдослучайной последовательности, выход которого соединен с входом элемента НЕ 18, с пятым входом второго блока 7 счета символов и с первьм входом второго бло- ка 2 коррекции, выход которого соединен с первым входом первого блока 1 коррекции и с вторым входом блока 3 счета суммы, первый и второй выходы которого соединены с вторым и третьи входами соответственно первого блока 1 коррекции, четвертый вход которого соединен с выходом первого элемента 4 задержки, вход которого соеднен с вторым входом второго блока 2

коррекции, с выходом второго элемента 5 задержки и с третьим входом блока 3 счета суммы, первый вход которого соединен с входом управления первого регистра 8, с первым входом пер-„ вого блока 6 счета символов, с входом управления второго регистра 9, с входом установки генератора 14 двоичной псевдослучайной последовательности,

с

0

5

0 5 0 5 0 0

с шиной 15 Пуск, с входом управления третьего регистра 10 и с.первым входом второго блока 7 счета символов, выход которого соединен с вторым входом элемента ИЛИ 16, четвертью входом второго блока 2 коррекции и с вторым входом первого блока символов, выход которого соединен с третьим входом второго блока 2 коррекции, с вторым входом второго блока 7 счета символов и с первым входом элемента ИЛИ 16, выход которого соединен с входом генератора 17 одиночных импульсов, выход которого соединен с третьим входом второго блока 7 счета символов и с третьим входом первого блока 6 счета символов, четвертый вход которого соединен с входом второго элемента 3 задержки, с выходом третьего элемента 19 задержки и с четвертым входом второго блока 7 счета символов. Выход элемента НЕ 18 соединен с пятым входом первого блока 6 счета символов. Выходы первого 8, второго 9 и третьего 10 регистров соединены с соответствующими информационными входами блока 3 счета суммы, первого 6 и второго 7 блокой счета символов соответственно. Входы первого 8, второго 9 и третьего 10 регистров соединены с информационными шинами 11-13 соответственно.

Блоки 6,7 счета символов (фиг.2) содержат счетчик iZI импульсов, выход переполнения которого соединен с входом элемента НЕ 22, выход которого соединен с первым входом элемента И 23, второй вход которого соединен с выходом первого элемента ИЛИ 24, второй элемент ИЛИ 25, выход которого соединен с входом синхронизации счетчика 21 импульсов,выход которого является выходом блоков 6,7 счета символов, первый вход которых соединен с входом установки счетчика 21 импульсов, информационные входы которого являются соответствующими информационными входами блоков 6,7 счета символов,второй вход которых соединен с первым входом первого элемента ИЛИ 24, второй вход которого соединен с пятым входом блоков 6,7 счета символов, третий вход которых соединен с первым входом второго элемента ИЛИ 25, второй вход которого соединен с четвертым входом блоков 6,7 счета символов. Выход элемента И 23 соединен

с входом управления счетчика 21 импульсов.

Блок 3 счета суммы (фиг.З) содержит реверсивньй регистр 26 сдвига, первая и вторая группа выходов которого соединены с соответствующими информационными входами первого 27 и второго 28 коммутаторов соответственно, первый элемент НЕ 29, пер- вый элемент ИЛИ 30, второй элемент НЕ 31, второй 32 и третий 33 элементы ИЛИ, элемент 34 задержки, выход которого соединен с первым входом третьего элемента ИЛИ 33, выход кото рого соединен с входом синхронизации реверсивного регистра 26 сдвига, вход разрешения записи которого соединен с вторым входом третьего элемента ИЛИ 33 и является первым входом бло- ка 3 счета суммы, второй вход которого соединен с входом второго элемента НЕ 31 и первым входом второго элемента ИЛИ 32, выход которого соединен с входом сдвига вправо реверсив- ного регистра 26 сдвига, вход сдвига влево которого соединен с выходом первого элемента ИЛИ 30, первый и второй входы которого соединены соответственно с выходом второго элемен- та НЕ 31 и с выходом второго коммутатора 28, выход которого соединен с входом первого элемента НЕ 29, выход которого является вторым выходом блока 3 счета суммы, первый выход кото- рого соединен с вторым входом второго элемента ИЛИ 32 и с выходом первого коммутатора 27, входы управления которого и входы управления второго коммутатора 28 являются соответствую- шими информационными входами блока 3 счета суммы, третий вход которого соединен с входом элемента 34 задержки.

Второй блок 2 коррекции (фиг.4)

содержит D-триггер 35 и последо- , с вательно соединенные первый 36 и второй 37 элементы ИСКЛЮЧАЩЕЕ ИЛИ. Выход D-триггера 35 является выходом второго блока 2 коррекции, первый вход которого соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 36, второй вход которого соединен с третьим входом второго блока 2 коррекции, второй вход которого соеди нен с входом синхронизации D-триггера 35. Четвертый вход второго блока 2 коррекции соединен с вторым вхо

сfg1520 25ЗО ,Q 45

50

55

дом второго элемента ИСКЛЮЧАКХЦЕЕ ИЛИ 37.

Первый блок 1 коррекции (фиг.5) содержит D-триггер 38, информационный вход которого соединен с выходом элемента И 39, первый вход которого соединен с выходом элемента ИЛИ 40. Выход D-триггера 38 является выходом первого блока 1 коррекции, первый вход которого соединен с первым входом элемента ИЛИ 40, второй вход которого соединен с вторым входом первого блока 1 коррекции, третий вход

f

которого соединен с вторым входом элемента И 39. Четвертый вход первого блока 1 коррекции соединен с входом синхронизации D-триггера 38.

Генератор псевдослучайных последовательностей (фиг.1) работает следующим образом.

При подаче на шину 15 Пуск положительного импульса устанавливается в начальное состояние генератор 14 двоичной псевдослучайной последовательности, производится запись информации в первый 8, второй 9 и третий 10 регистры с информационных шин 11,12 и 13 соответственно, обнуляются счетчики 21 импульсов в первом 6 и втором 7 блоках счета символов (фиг.2), реверсивный регистр 26 сдвига в блоке 3 счета суммы (фиг.З) устанавливается в состояние записи и в него (в его нулевой разряд, т.к. реверсивный регистр 26 сдвига разделен на три группы разрядов: первые п разрядов, центральный нулевой разряд и вторые п разрядов) через третий элемент ИЛИ 33 блока 3 счета суммы записывается сигнал 1. При сбросе в нулевое состояние счетчиков 21 импульсов первого 6 и второго 7 блоков счета символов на их выходах переноса появляется сигнал 1, который через элемент ИЛИ 16 поступает (с выхода второго блока 7 счета символов) на вход генератора 17 одиночных импульсов. Последний формирует одиночный положительньй импульс, поступающий через второй элемент ИЛИ 25 первого блока 6 счета символов (фиг.2) на вход синхронизации его счетчика 21 импульсов. Одновременно сигнал с выхода переноса счетчика 21 импульсов инвертируется элементом НЕ 22 и поступает на вход элемента И 23, на выходе которого пЪ является нулевой логический сигнал.

устанавливакиций счетчик 21 импульсов в состояние записи информации, поступающей на его информационные входы с регистров 9, 10 условий соответственно для блоков 6,7 счета символов и записываемой в их счетчики 21 импульсов сигналом с выхода генератора 17 одиночных импульсов.

13780266

лов. Элемент 19 задержки обеспечивает задержку тактовых импульсов на время .переходных процессов в генераторе 14 г двоичной посевдослучайной последовательности, сигнал с выхода которого поступает также на первый вход второго блока 2 коррекции, т.е. на вход его первого элемента ИСКЛЮ

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных последовательностей | 1988 |

|

SU1626345A2 |

| Генератор псевдослучайной последовательности | 1987 |

|

SU1528770A1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU962931A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Устройство для тренировки операторов | 1989 |

|

SU1721620A1 |

| Генератор псевдослучайной последовательности импульсов | 1989 |

|

SU1735846A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

| Устройство для моделирования дискретного радиоканала | 1983 |

|

SU1103256A2 |

| Генератор квазирегулярных последовательностей импульсов | 1979 |

|

SU866717A1 |

| Дискретный согласованный фильтр | 1978 |

|

SU771891A2 |

Изобретение относится к импульсной технике и служит для расширения функциональных возможностей устройства. Для этого в устройство, содержащее генератор 14 двоичной псевдослучайной последовательности, введеньг регистры 8-10, блоки 1 и 2 коррекции, блоки 6 и 7 счета символов, блок 3 счета суммы, элементы 4 и 5 задержки, генератор 17 одиночных импульсов, элемент ИЛИ 16 и элемент НЕ 18. Благодаря этому обеспечивается возможность регулирования длительности серий одноименных единичных и нулевых символов. Кроме того, осуществляется контроль и ограничение текущей циф ровой суммы символов, т.е. формирование псевдослучайных последовательностей с заданными статистическими параметрами. В описании даны примеры реализации блоков 6 и 7 счета символов, блока 3 счета суммы и блоков 1 и 2 коррекции. 4 з.п, ф-лы, 5 ил. с: (Л

Блоки 6 и 7 счёта символов обеспечи- ю ЧАЮЩЕЕ ИЛИ 36, на другой вход которовают подсчет количества следующих подряд символов (единиц и нулей соответственно) и вьщачу управляющего сигнала при превышении заданного числа, поступающего в устройство по информационным шинам 12 и 13.

С подачей тактовых импульсов на щину 20 тактовых импульсов на выходе генератора 14 двоичной псевдослучайной последовательности формируется последовательность, поступающая через первый элемент ИЛИ 24 и элемент И 23 на вход разрешения счета счетчика 21 импульсов блок 7 счета символов. Счетчик 21 импульсов рабо- тает в режиме вычитания, при этом при поступлении на его вход сигнала О с выхода генератора 14

с выхода генератора 1 он восстанавливает (по информационным входам под действием очередного тактового импульса) свое начальное состоя ние. Если в режиме вычитания счетчик 21 досчитает до нуля, то на его выходе появляется сигнал 1, обес- печивающий запись в него начальных условий, а также поступающий (через элемент ИЛИ 16) на вход генерато- ра 17 одиночных импульсов, импульс с выхода которого обеспечивает перезапись информации с регистра 10. Одновременно сигнал 1 с выхода перенос счетчика 21 импульсов блока 7 счета символов, т.е. с выхода последнего, поступает на вход элемента ИЛИ 24 блока 6 счета символов и далее на вход его элемента И 23, на втором входе которого присутствует сигнал 1, что обеспечивает режим счета в счетчике 21 импульсов, содержимое которого уменьшается на единицу по каждому импульсу с выхода генератора 17 одиночных импульсов. Работа блока 6 счета символов аналогична работе блока 7 счета символов, но благодаря инверсии сигналов с выхода генератора 14 двоичной псевдослучайной по- следовательности элементом НЕ 18 бло 6 счета символов подсчитывает количество подряд идущих нулев 1Х симво

5

0

5

0

5

го поступает сигнал с выхода блока 6 счета символов. Если сигнал с выхода блока 6 счета символов нулевой, то информация на D-вход D-триггера 35

5 передается без изменений. При появлении на выходе генератора 14 двоичной псевдослучайной последовательности лишнего единичного символа на выходе второго элемента ИСКЛЮЧАЩЕЕ

0 ИЛИ 37 появляется нулевой сигнал, который тактовым импульсом записывается в D-триггер 35. Элемент 3 задержки задерживает тактовые импульсы на время срабатывания блоков 6,7 счета символов, после чего импульсы поступают на третий вход блока 3 счета суммы (фиг.З), обеспечивающего подсчет текущей цифровой суммы псевдослучайной последовательности, причем единичные символы через элемент ИЛИ 32 последнего подаются -на вход разрешения сдвига вправо его реверсивного регистра 26 сдвига, а нулевые символы инвертируются элементом НЕ 31 и подаются через элемент ИЛИ 30 на вход разрешения сдвига влево реверсивного регистра 26 сдвига. Тактовыми импульсами, задержанными элементом 34 задержки блока 3 счета суммы на время срабатывания блока 2 коррекции, происходит сдвиг единичного символа влево или вправо в реверсивном регистре 26 сдвига, информация с соответствующих групп выходов которого поступает на информационные входы коммутаторов 27, 28, на адресные входы которых поступает значение цифровой суммы с первого регистра 8 условий. При поступлении единичного сигнала с выходов реверсивного регистра 26 сдвига на один из входов, адрес которого записан в регистре 8 коммутатора 27 (28), на выходе последнего появляется сигнал 1, который поступает на соответствующий вход первого блока 1 коррекции и через элемент ИЛИ 32 (элемент ИЛИ 30) на вход разрешения сдвига вправо (влево) регистра 26 сдвига блока 3

5

0

7

II ч II

1

счета суммы. Если 1 появляется на выходе коммутатора 27, т.е. на первом выходе блока 3 счета суммы, то она поступает на вход элемента ИЛИ 4 первого блока 1 коррекции (фиг.5), на другой вход которого поступает псевдослулайаая последовательность с выхода блока 2 коррекции. Сигнал 1 с выхода элемента ИЛИ 40 посту- пает на первый вход элемента И 39, на второй вход которого поступает сигнал с второго выхода блока 3 счета суммы. Если 1 появляется на выходе коммутатора 28, то она инверти- руется элементом НЕ 29, обеспечивая сигнал О на выходе элемента И 39. Откорректированная информация записывается тактовым импульсом, задержанным элементом 4 задержки, в - D-триггер 38.

Таким образом, в устройстве обеспечивается регулирование длительности серий подряд следующих единичных и нулевых символов, а также конт- роль и .ограничение текущей цифровой суммы символов, т.е. формирование псевдослучайных последовательностей с заданными статистическими параметрами .

Формула изобретения

мента НЕ, с пятым входом второго бло- диненные первый и второй элементы

8

ю 0

5 0

5

0

5

0

5

ка счета символов и с первым входом второго блока коррекции, выход которого соединен с первым входом первого блока коррекции и с вторым входом блока счета суммы, первый и второй выходы которого соединены соответственно с вторым и третьим вхоДа- ми первого блока коррекции, четвертый вход которого соединен с выходом первого элемента задержки, вход которого соединен с третьим входом блока счета суммы, выходом второго элемента задержки и с вторым входом второго блока коррекции, третий вход которого соединен с выходом первого блока счета символов, с первым входом элемента ИЛИ и с вторым входом второго блока счета символов, выход которого соединен с четвертым входом второго блока коррекоди, с вторым входом первого блока счета символов и с вторым входом элемента ИЛИ, выход которого соединен с входом генератора одиночных импульсов, выход которого соединен с третьим входом первого блока счета символов и с третьим входом второго блока счета символов, четвертый вход которого соединен с выходом третьего элемента задержки, с входом второго Элемента задержки и с четвертым входом первого блока счета символов, пятый вход которого соединен с выходом элемента НЕ, вход третьего элемента задержки соединен с шиной тактовых импульсов, выходы первого, второго и третьего регистров соединены с информационными входами соответственно блока счета суммы, первого и второго блоков счета символов.

и D-триггер, выход которого является выходом первого блока коррекции, первый вход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с вторым входом первого блока коррекции, третий вход которого соединен с вторым входом элемента И, четвертьй вход первого блока коррекции соединен с входом синхронизации D-триггера.

с выходом второго элемента НЕ и с вы5 Q

5

0

ходом второго коммутатора, выход которого соединен с входом первого элемента НЕ, выход которого является вторым выходом блока счета суммы,первый выход которого соединен с вторым входом второго элемента ИЛИ и с выходом первого коммутатора, входы управления которого и входы управления второго коммутатора являются соответствующими информационными входами блока счета суммы, третий вход которого соединен с входом элемента задержки.

fpue. 2

(pus. 3

,.J

J

9Ji/5, t

фиг. 5

J7

35

38

D

| Авторское свидетельство СССР « 1200393, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Хоровиц П., Хилл У | |||

| Искусство схемотехники | |||

| М.: Мир, 1984, т | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Экономайзер | 0 |

|

SU94A1 |

Авторы

Даты

1988-02-28—Публикация

1986-09-10—Подача