(Л

00 05 05

со со оо

qnie-l

113

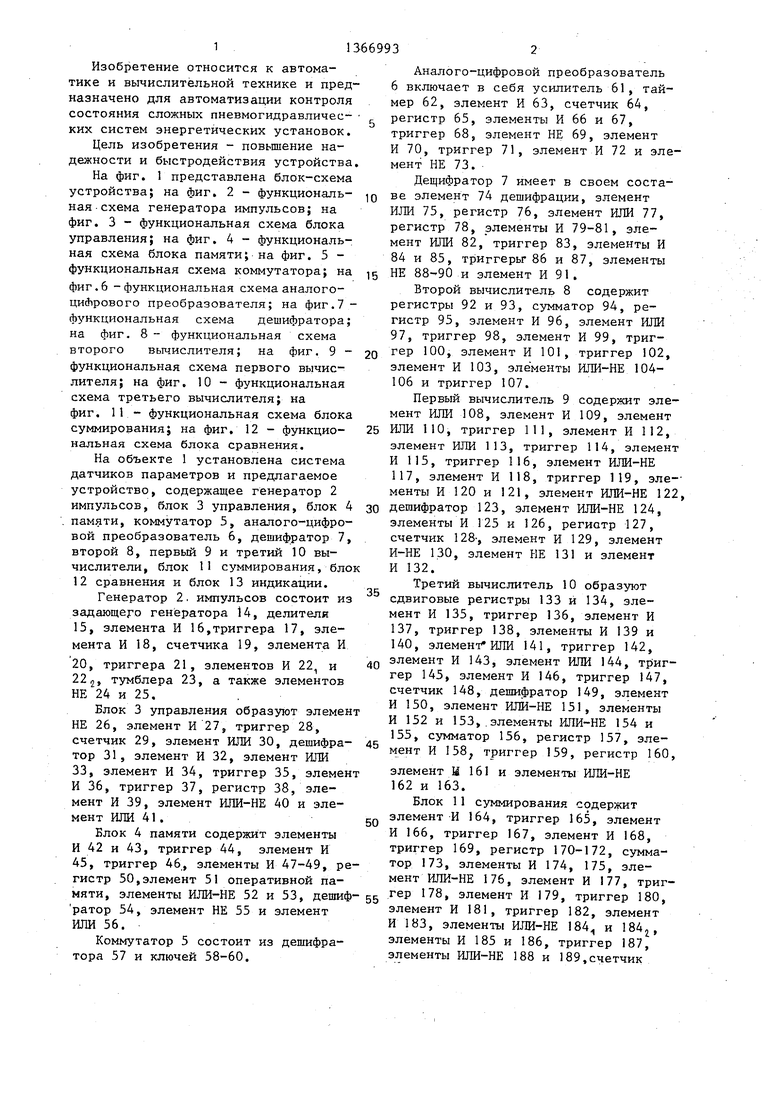

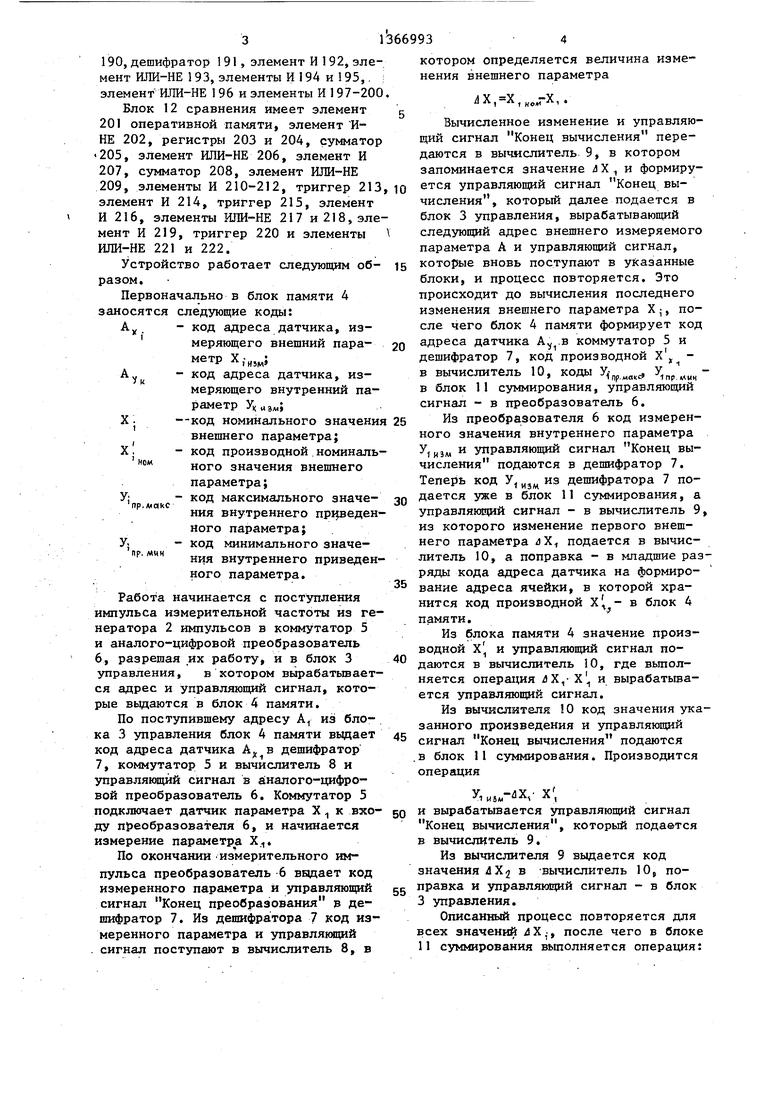

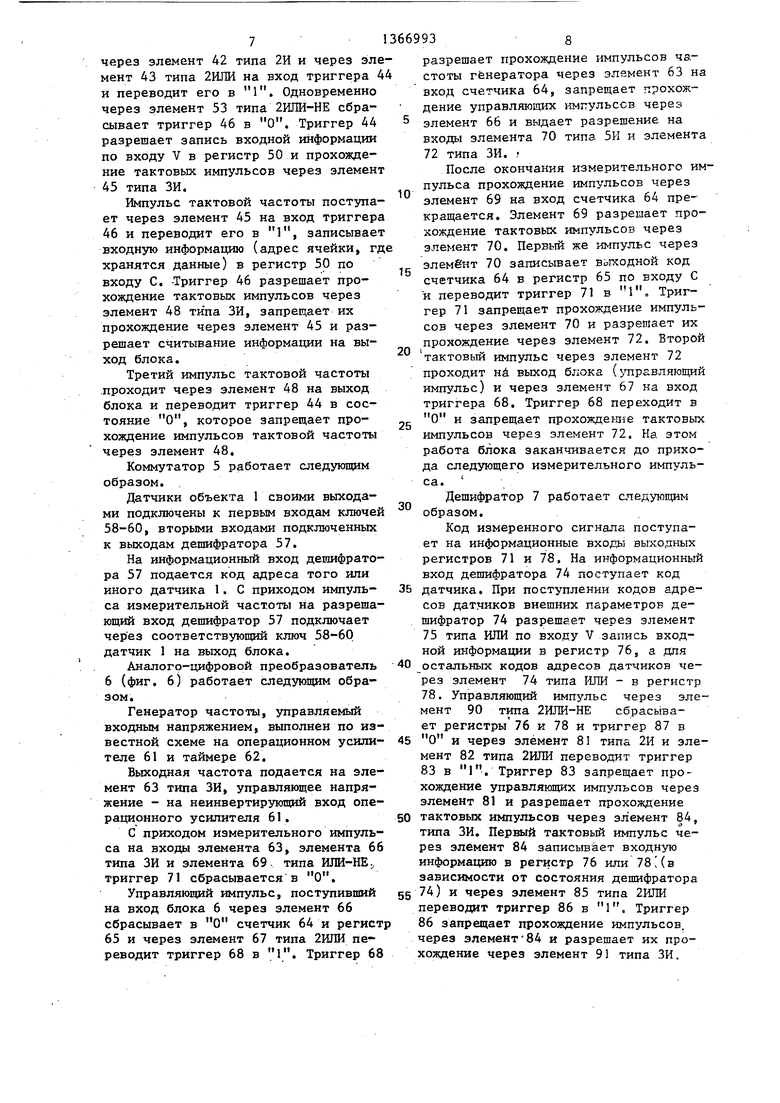

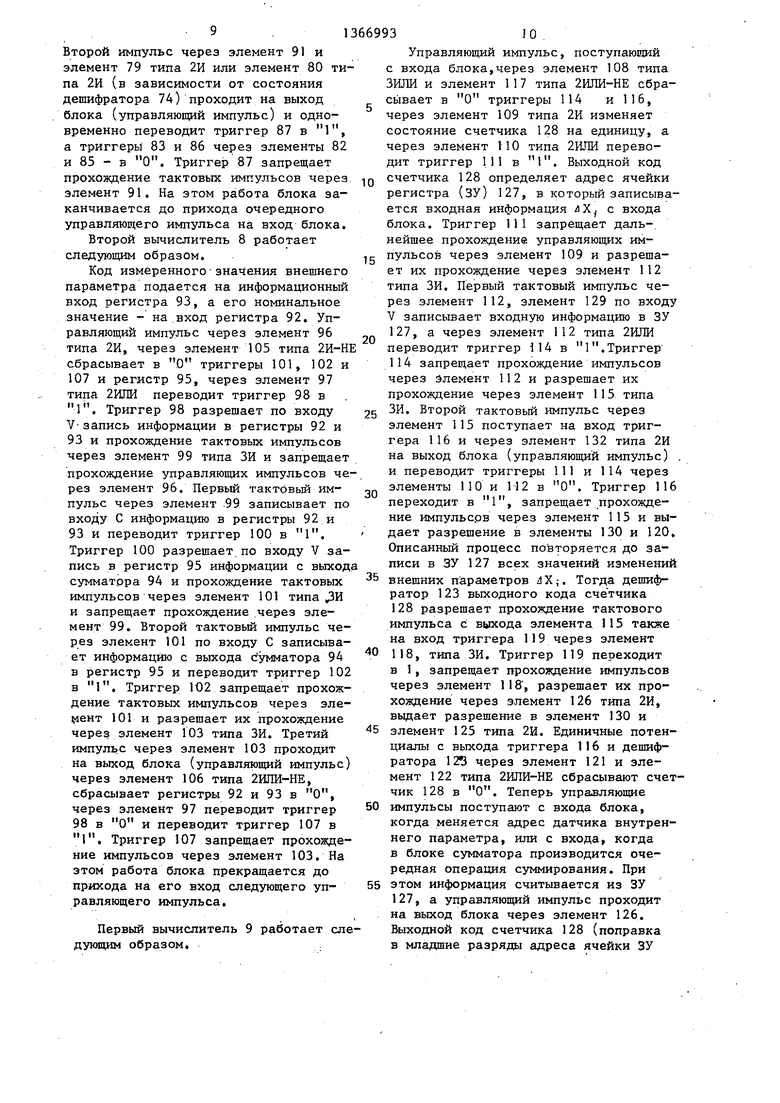

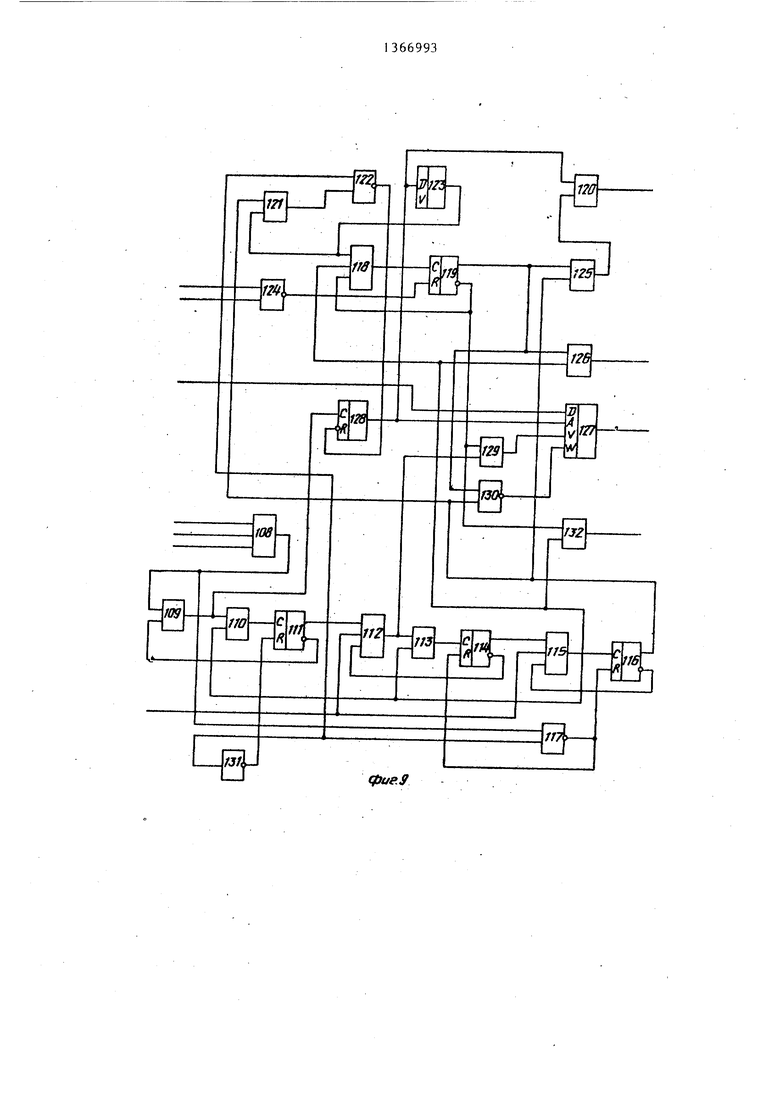

Изобретение относится к автоматике и вычислительной технике и предназначено для автоматизации контроля состояния сложных пневмогидравличес- ких систем энергетических установок. Цель изобретения - повьшение надежности и быстродействия устройства На фиг. 1 представлена блок-схема устройства; на фиг. 2 - функциональ- ная-схема генератора импульсов; на фиг. 3 - функциональная схема блока управления; на фиг. 4 - функциональная схема блока памяти; на фиг. 5 - функциональная схема коммутатора; на фиг.6 -функциональная схемааналого- цисНрового преобразователя; на фиг.7- функциональная схема дешифратора; на фиг. 8 - функциональная схема второго вычислителя; на фиг. 9функциональная схема первого вычислителя; на фиг. 10 - функциональная схема третьего вычислителя; на фиг. 11 - функциональная схема блока суммирования; на фиг. 12 - функцио- нальная схема блока сравнения.

На объекте 1 установлена система датчиков параметров и предлагаемое устройство, содержащее генератор 2

импульсов, блок 3 управления, блок 4 памяти, коммутатор 5, аналого-цифровой преобразователь 6, дешифратор 7, второй 8, первый 9 и третий 10 вычислители, блок 11 суммирования, бло 12 сравнения и блок 13 индикации.

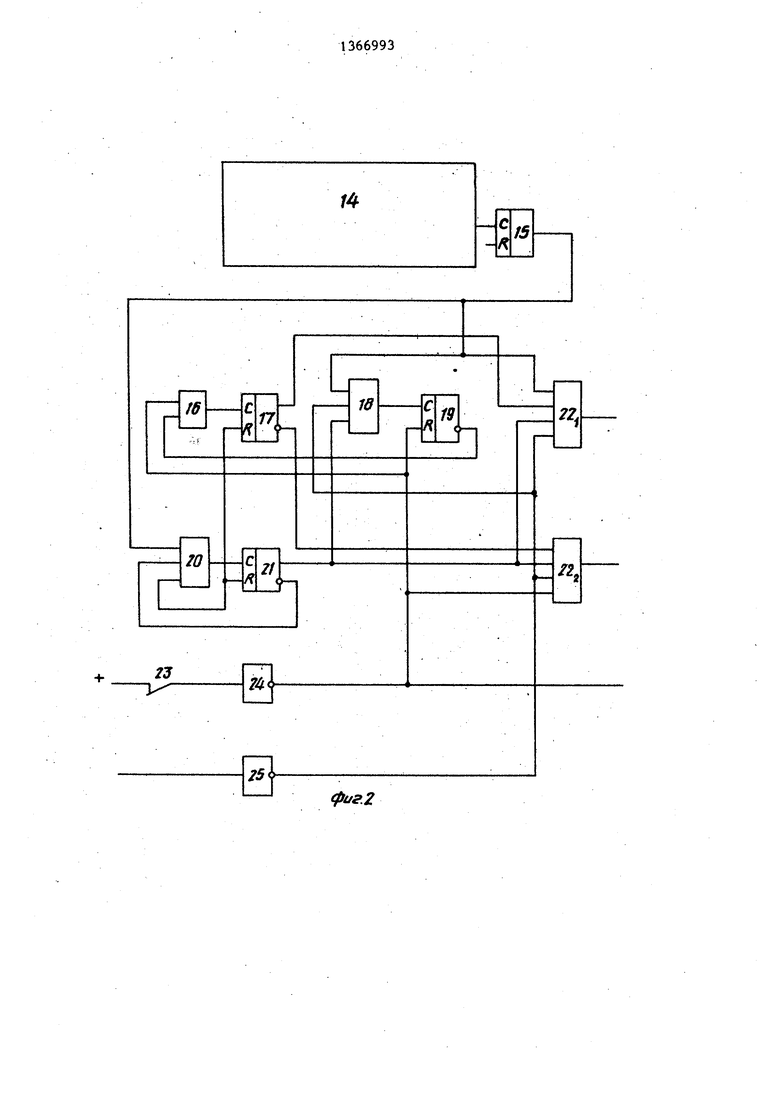

Генератор 2. импульсов состоит из задаю1це о генератора 14, делителя 15, элемента И 16,триггера 17, элемента И 18, счетчика 19, элемента И

20, триггера 21, элементов И 22 и 222, тумблера 23, а также элементов НЕ 24 и 25. .

Блок 3 управления образуют элемен НЕ 26, элемент И 27, триггер 28, счетчик 29, элемент ИЛИ 30, дешифратор 31, элемент И 32, элемент ИЛИ 33, элемент И 34, триггер 35, элемен И 36, триггер 37, регистр 38, элемент И 39, элемент ИЛИ-НЕ 40 и элемент ИЛИ 41.,

Блок 4 памяти содержит элементы И 42 и 43, триггер 44, элемент И 45, триггер 46, элементы И 47-49, ре

Блок 11 суммирования содержит элемент И 164, триггер 165, элемент И 166, триггер 167, элемент И 168, триггер 169, регистр 170-172, сумматор 173, элементы И 174, 175, элемент ИЛИ-НЕ 176, элемент И 177, триг

гистр 50,элемент 51 оперативной памяти, элементы ИЛИ-НЕ 52 и 53, дешиф- 55 Р элемент И 179, триггер 180, ратор 54, элемент НЕ 55 и элемент элемент И 181, триггер 182, элемент ИЛИ 56.И 183, элементы ИЛИ-НЕ 184 и 184,

Коммутатор 5 состоит из дешифра- элементы И 185 и 186, триггер 187, тора 57 и ключей 58-60.элементы ИЛИ-НЕ 188 и 189,счетчик

5

5

0

О

5

0

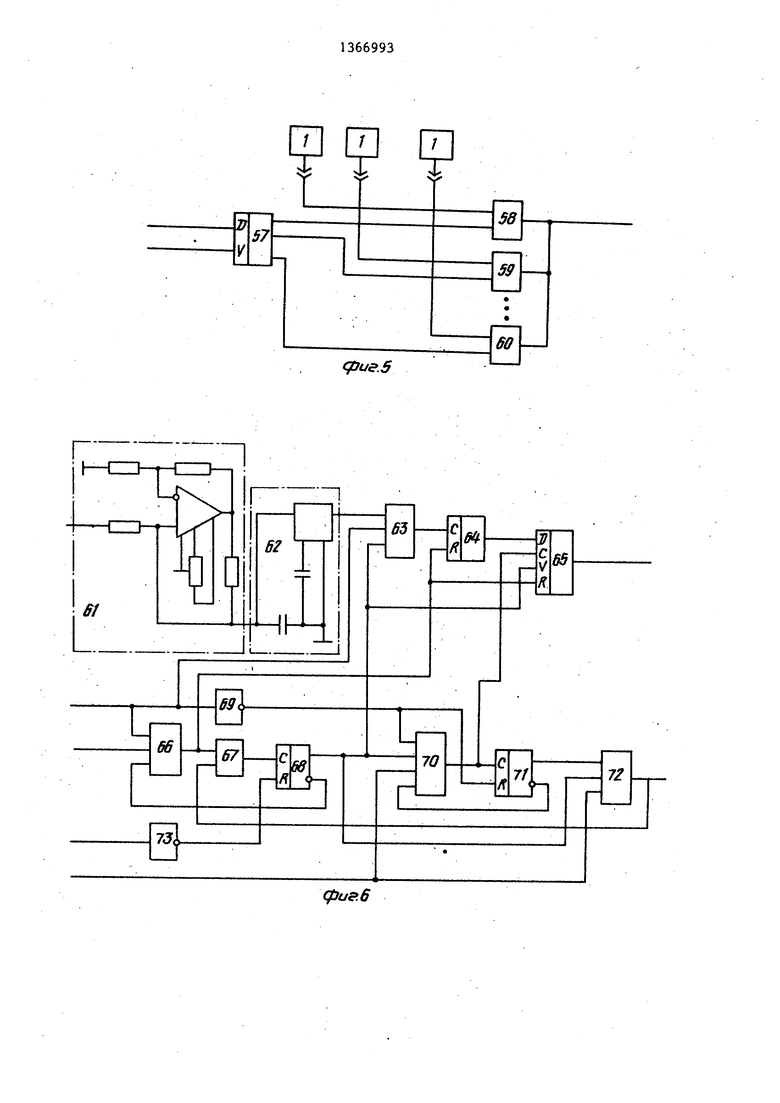

Аналого-цифровой преобразователь 6 включает в себя усилитель 61, таймер 62, элемент И 63, счетчик 64, регистр 65, элементы И 66 и 67, триггер 68, элемент НЕ 69, элемент И 70, триггер 71, элемент И 72 и элемент НЕ 73.

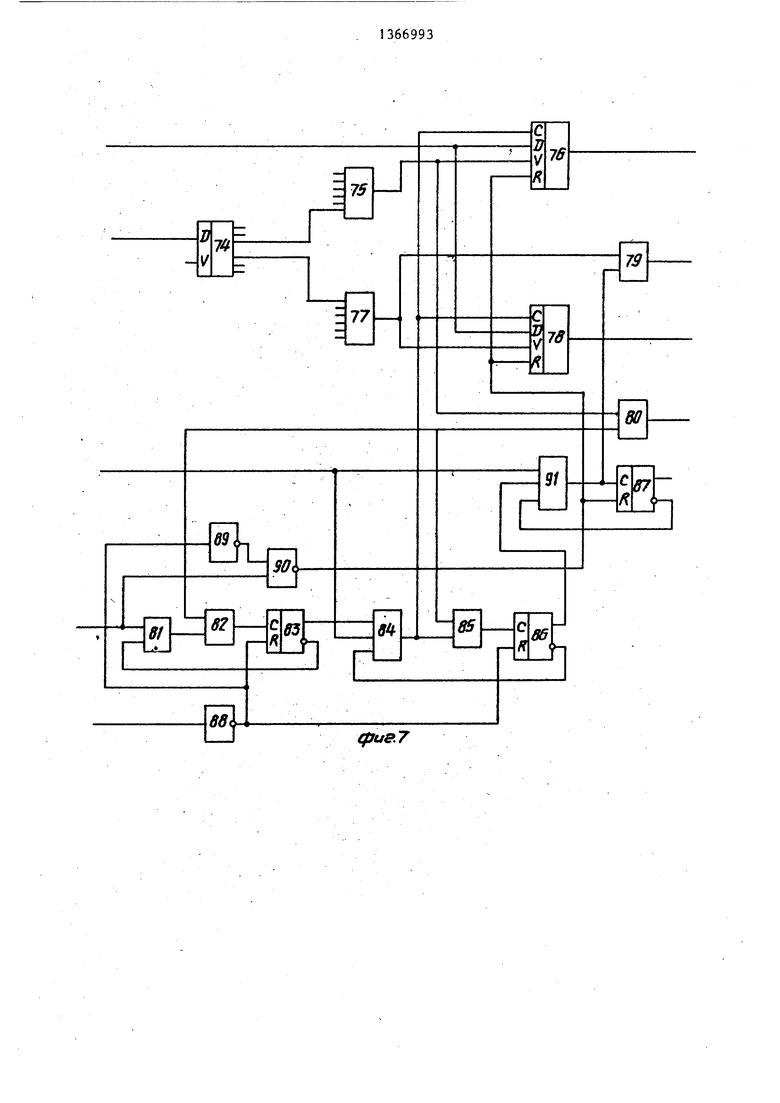

Дещифратор 7 имеет в своем составе элемент 74 дешифрации, элемент ИЛИ 75, регистр 76, элемент ИЛИ 77, регистр 78, элементы И 79-81, элемент РШИ 82, триггер 83, элементы И 84 и 85, триггеры 86 и 87, элементы НЕ 88-90 и элемент И 91.

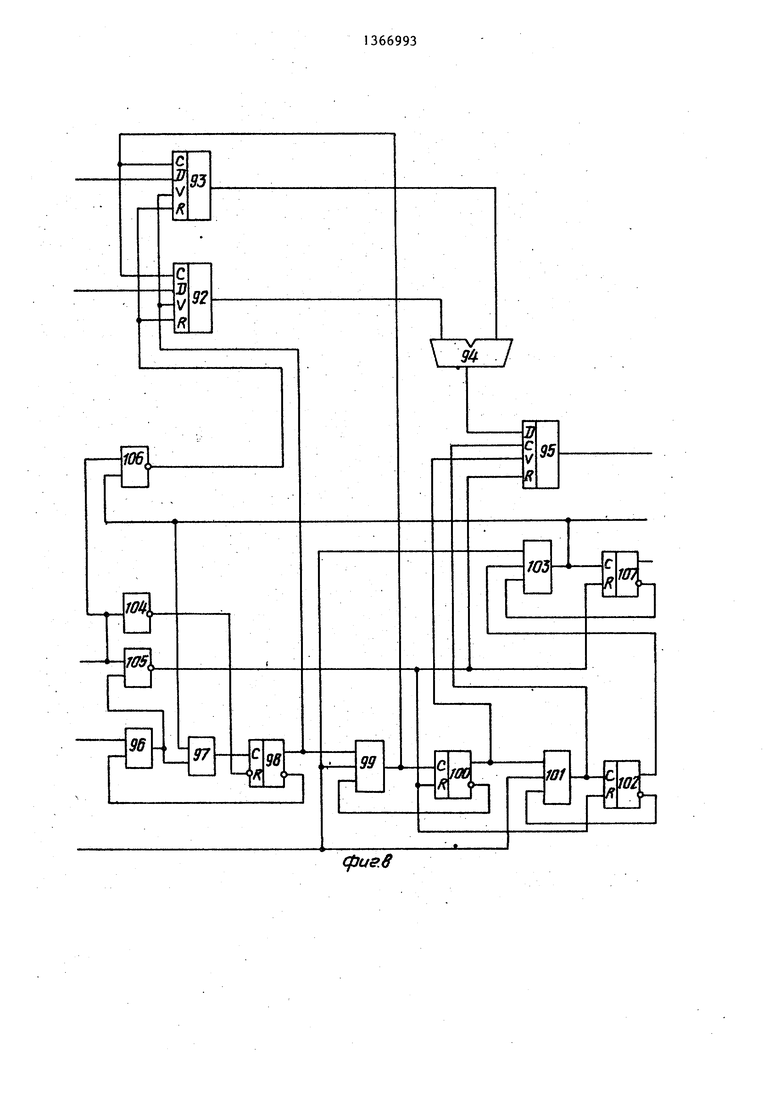

Второй вычислитель 8 содержит регистры 92 и 93, сумматор 94, регистр 95, элемент И 96, элемент ИЛИ 97, триггер 98, элемент И 99, триггер 100, элемент И 101, триггер 102, элемент И 103, элементы ИЛИ-НЕ 104- 106 и триггер 107.

Первый вычислитель 9 содержит элемент ИЛИ 108, элемент И 109, элемент ИЛИ 110, триггер 111, элемент И 112, элемент ИЛИ 113, триггер 114, элемент И 115, триггер 116, элемент ИЛИ-НЕ 117, элемент И 118, триггер 119, эле-- менты И 120 и 121, элемент ИЛИ-НЕ 122, дешифратор 123, элемент ИЛИ-НЕ 124, элементы И 125 и 126, регистр 127, счетчик 128-, элемент И 1 29, элемент И-НЕ 130, элемент НЕ 131 и элемент И 132.

Третий вычислитель 10 образуют сдвиговые регистры 133 и 134, элемент И 135, триггер 136, элемент И 137, триггер 138, элементы И 139 и 140, элемент ИЛИ 141, триггер 142, элемент И 143, элемент ИЛИ 144, гер 145, элемент И 146, триггер 147, счетчик 148, дешифратор 149, элемент И 150, элемент ИЛИ-НЕ 151, элементы И 152 и 153,.элементы ИЛИ-НЕ 154 и 155, сумматор 156, регистр 157, элемент И 158 триггер 159, регистр 160,

элемент И 161 и элементы ИЛИ-НЕ 162 и 163.

Блок 11 суммирования содержит элемент И 164, триггер 165, элемент И 166, триггер 167, элемент И 168, триггер 169, регистр 170-172, сумматор 173, элементы И 174, 175, элемент ИЛИ-НЕ 176, элемент И 177, триг5 Р элемент И 179, триггер 180, элемент И 181, триггер 182, элемент И 183, элементы ИЛИ-НЕ 184 и 184,

190,дешифратор 191 , элемент И 192, элемент ИЛИ-НЕ 1 93, элементы И 194 и 195,. : элемент ИЛИ-НЕ 1 96 н элементы И 197-200.

Блок 12 сравнения имеет элемент g 201 оперативной памяти, элемент И- НЕ 202, регистры 203 и 204, сумматор 205, элемент ИЛИ-НЕ 206, элемент И 207, сумматор 208, элемент ИЛИ-НЕ 209, элементы И 210-212, триггер 213, ю элемент И 214, триггер 215, элемент И 216, элементы ИЛИ-НЕ 217 и 218, элемент И 219, триггер 220 и элементы ШШ-НЕ 221 и 222.

Устройство работает следующим об- 15 разом.

Первоначально в блок памяти 4 заносятся следующие коды:

А. - код адреса датчика, измеряющего внешний пара- 20 метр Х,-„,;

- код адреса датчика, измеряющего внутренний параметр Уцизл.; -код номинального значения 25

внешнего параметра; X, - код производной номиналь- ного значения внешнего параметра;

У; - код максимального значе- on np.vakcJ

ния внутреннего пр: еденного параметра;

У; - код минимального значепр.

Vk

х:

ния внутреннего приведенного параметра.

35

Работа начинается с поступления импульса измерительной частоты из генератора 2 импульсов в коммутатор 5 и аналого-цифровой преобразователь

6,разрешая их работу, и в блок 3 управления, в котором вырабатьшает

ся адрес и управляющий сигнал, которые вьщаются в блок 4 памяти.

По поступившему адресу А, из блока 3 управления блок 4 памяти ведает код адреса датчика А, в дешифратор

7,коммутатор 5 и вычислитель 8 и управляющий сигнал в аналого-цифровой преобразователь 6. Коммутатор 5 подключает датчик параметра X к вхо- ду п1 еобразователя 6, и начинается измерение параметра Х.

По окончании измерительного импульса преобразователь 6 ввдает код измеренного параметра и управляющий сигнал Конец преобразования р дешифратор 7. Из дешифратора 7 код измеренного параметра и управляннций . сигнал поступают в вычислитель 8, в

g

5

0

5

n

5

0

5

0

5

котором определяется величина изменения внешнего параметра

, .

Вычисленное изменение и управляющий сигнал Конец вычисления передаются в вычислитель 9, в котором запоминается значение 5 X и формируется управляющий сигнал Конец вычисления, который далее подается в блок 3 управления, вырабатывающий следующий адрес внешнего измеряемого параметра А и управляющий сигнал, которые вновь поступают в указанные блоки, и процесс повторяется. Это происходит до вычисления последнего изменения внешнего параметра X , после чего блок 4 памяти формирует код адреса датчика А .в коммутатор 5 и дешифратор 7, код производной х , - в вычислитель 10, коды У|„р.„„, У1пр ,««- в блок 11 суммирования, управляющий сигнал - в преобразователь 6.

Из преобразователя 6 код измеренного значения внутреннего параметра 1изм управляющий сигнал Конец вычисления подаются в дешифратор 7. Теперь код ,., из дешифратора 7 поI пЭМ

дается уже в блок 11 суммирования, а управляющий сигнал - в вычислитель 9, из которого изменение первого внешнего параметра dX, подается в вычислитель 10, а поправка - в младшие разряды кода адреса датчика на формирование адреса ячейки, в которой хранится код производной Х - в блок 4 памяти.

Из блока памяти 4 значение производной и управляющий сигнал подаются в вычислитель 10, где выполняется операция ЛХ,- Х и вырабатьша- ется управляющий сигнал.

Из вычислителя 10 код значения указанного произведения и управляющий сигнал Конец вычисления подаются .в блок 11 суммирования. Производится операция

1

и вырабатывается управляющий сигнал Конец вычисления, который подается в вычислитель 9.

Из вычислителя 9 выдается код значения ЛXj в -вычислитель 10, поправка и управляющий сигнал - в блок 3 управления.

Описанный процесс повторяется для всех значений ЛХ,-, после чего в блоке 11 суммирования выполняется операция:

l np У1ц5м 2-.Л X j- X j

Приведенное значение У.

13669936

Триггер 17 изменяет выходной потенци р

ал на. выходе элемента 222 нуле управляющий сигнал Конец вычисления подаются в блок 12 сравнения, в котором производится операция сравнения:

вой (так формируется измерительный импульс) и разрешает прохождение тактовых импульсов через элемент 22 на блока. Эти импульсы используются для управления блоками устройства. После прохождения серии тактовых импульсов через счетчик 19 опять появляется импульс переполнения, который переводит триггер 17 в О. Снова начнется процесс генерации измерительного импульса и т.д.

У, У

V

ПР 1 пр. ЛАСТ КС

У-,

I пр 1 nf. мин

Если условия выполняются, то в блоке 12 сравнения вырабатывается управляющий сигнал Конец сравнения который подается в блок формирования адреса, и описанный процесс приведения У,зм повторяется для У и т.д. для всех Уц5Ал

Если же указанные условия не выполняются дпя какого-то внутреннего параметра, то управляющий сигнал блока 12 сравнения поступает в блок 13 индикации, в котором вырабатывается сигнал останова работы устройства и индицируется название неисправного узла. Сигнал останова подается на генератор 2 импульсов, который прекращает свою работу, в результате прекраща ется работа всего устройства.

Генератор 2 импульсов работает следующим образом.

Импульсы с выхода элемента 14 по- ступают на вход счетчика 15, который понижает частоту импульсов до значения тактовой частоты . При нажатии тумблера (т) 23 через элемент 24,типа ИЛИ-НЕ снимается отрицательный потенциал, удерживающий в нулевом состоянии триггеры 17 и 21 и счетчик 19 и запрещающий прохождение импуль- через элементы 22, и 22 типа 4И на выход блока.

Первый импульс тактовой частоты с вь,,хода делителя 15 через элемент 20 Tif.na ЗИ поступает на вход триггера 21 и переводит его в единичное состояние. Триггер 21 разрешает прохождение импульсов через элементы 22 и 22,j на выход блока и через элемент 18 типа ЗИ на вход счетчика 19. Начиная с этого момента импульсы тактовой частоты начинают поступать на вход счетчика 19, а на выходе элемента 222 появляется единичньШ потенциал. После прохождения через счетчик 19 некоторого количества тактовы импульсов появляется импульс переполнения, который через элемент 16 типа 2И переводит триггер 17 в 1.

ал на. выходе элемента 222 нуле0

5

0

25

30

35

40

45

50

55

вой (так формируется измерительный импульс) и разрешает прохождение тактовых импульсов через элемент 22 на блока. Эти импульсы используются для управления блоками устройства. После прохождения серии тактовых импульсов через счетчик 19 опять появляется импульс переполнения, который переводит триггер 17 в О. Снова начнется процесс генерации измерительного импульса и т.д.

Блок 3 управления работает следующим образом.

Измерительный импульс поступает на вход блока через элемент 26 типа ИЛИ-НЕ, запрещает прохождение тактовых импульсов через элемент 27 типа 4И на входы триггера 28 и счетчика 29, через элемент 39 типа 211ПИ-НЕ удерживает триггер 28 в состоянии О. После окончания измерительного импульса первый импульс тактовой частоты проходит через элемент 21 па. вход триггера 28 и цереводит его в 1, проходит на вход счетчика 29 и изменяет его состояние на единицу, через элемент 40 типа 2ИЛИ-НЕ сбрасывает триггеры 35 и 37 и регистр 38 в О. Триггер 28 запрещает прохождение импульсов через элемент 27, разрешает прохождение ,через) элемент 34 типа ЗИ, разрешает запись в регистр 38. Второй импульс через элемент 34 переводит триггер 35 в 1, разрешая прохождение импульсов через элемент 36 типа ЗИ и запрещая прохождение импульсов через элемент 34, и записывает информацию с выхода счетчика 29 в регистр 38. Код на выходе регистра 38 является адресом ячейки памяти в блоке 4. Третий импульс поступит на вход триггера 37 и через элемент 39 типа 2И на выход блока. Триггер 3 запрещает прохождение им пульсов через элемент 36. Когда код счетчика 29 соответствует количеству внешних измеренных параметров, дешифратор 31 через элемент 32 типа 2И разрешает прохождение импульса с выхода элемента 38 в блок хранения вычисленных изменений внешних параметров 9.

Блок 4 памяти работает следующим образом.

С входа блока управляющий импульс поступает через элемент 56 типа 2Ш1И

через элемент 42 типа 2И и через элемент 43 типа 2ИЛИ на вход триггера 4 и переводит его в 1. Одновременно через элемент 53 типа 2ИЛИ-НЕ сбрасывает триггер 46 в О. Триггер 44 разрешает запись входной информации по входу V в регистр 50 и прохождение тактовых импульсов через элемент

45типа ЗИ.

Импульс тактовой частоты поступает через элемент 45 на вход триггера

46и переводит его в 1, записывает входную информацию (адрес ячейки, гд хранятся данные) в регистр 50 по входу С. -Триггер 46 разрешает прохождение тактовых импульсов через элемент 48 ти па ЗИ, запрещает их прохождение через элемент 45 и разрешает считывание информации на выход блока.

Третий импульс тактовой частоты .проходит через элемент 48 на выход блока и переводит триггер 44 в состояние О, которое запрещает прохождение импульсов тактовой частоты через элемент 48.

Коммутатор 5 работает следующим образом.

Датчики объекта 1 своими выходами подключены к первым входам ключей 58-60, вторыми входами подключенных к выходам дешифратора 57.

На информационный вход дешифратора 57 подается код адреса того или иного датчика 1. С приходом импульса измерительной частоты на разрешающий вход дешифратор 57 подключает через соответствующий ключ 58-60 датчик 1 на выход блока.

Аналого-цифровой преобразователь 6 (фиг. 6) работает следующим образом.

Генератор частоты, зшравляемый входным напряжением, выполнен по известной схеме на операционном усилителе 61 и таймере 62.

Выходная частота подается на элемент 63 типа ЗИ, управляющее напряжение - на неинвертирующий вход операционного усилителя 61.

С приходом измерительного импульса на входы элемента 63, элемента 66 типа ЗИ и элемента 69 типа ИЛИ-НЕ триггер 71 сбрасывается в О.

Управляющий импульс, поступивший на вход блока 6 через элемент 66 сбрасывает в О счетчик 64 и регист 65 и через элемент 67 типа 2ШШ переводит триггер 68 в 1. Триггер 68

0

5

разрешает прохождение импульсов частоты генератора через элемент 63 на вход счетчика 64, запрещает прохождение управляющих импульсов через элемент 66 и выдает разрешение на входы элемента 70 типа 5И и элемента 72 типа ЗИ.

После окончания измерительного импульса прохождение импульсов через элемент 69 на вход счетчика 64 пре- кращается. Элемент 69 разрешает прохождение тактовых импульсов через элемент 70. Первый же импульс через элемент 70 записывает выходной код счетчика 64 в регистр 65 по входу С и переводит триггер 71 в 1. Триггер 71 запрещает прохождение импульсов через элемент 70 и разрешает их прохождение через элемент 72. Второй тактовый импульс через элемент 72 проходит ни выход блока (управляющий импульс) и через элемент 67 на вход триггера 68. Триггер 68 переходит в О и запрещает прохождеш е тактовьпс импульсов через элемент 72. На этом работа блока заканчивается до прихода следующего измерительного импульса.

Дешифратор 7 работает следующим образом.

Код измеренного сигнала поступает на информационные входьз выходных регистров 71 и 78. На информационный вход дешифратора 74 поступает код датчика. При поступлении кодов адресов датчиков внешних параметров дешифратор 74 разрешает через элемент 75 типа ИЛИ по входу V запись входной информации в регистр 76, а для

0 остальных кодов адресов датчиков через элемент 74 типа ИЛИ - в регистр 78. Управляющий импульс через элемент 90 типа 2ИЛИ-НЕ сбрасывает регистры 76 и 78 и триггер 87 в

5 О и через элемент 81 типа 2И и эле0

5

0

5

мент 82 типа 2ШШ переводит триггер 83 в 1. Триггер 83 запрещает прохождение управляющих импульсов через элемент 81 и разрешает прохождение

50 тактовых импульсов через элемент 84, типа ЗИ. Первый тактовый импульс через элемент 84 записывает входную информацию в регистр 76 или 78(в зависимости от состояния дешифратора

55 74) и через элемент 85 типа 2ИЛИ переводит триггер 86 в 1, Триггер 86 запрещает прохождение импульсов, через элемент 84 и разрешает их прохождение через элемент 91 типа ЗИ.

Второй импульс через элемент 91 и элемент 79 типа 2И или элемент 80 типа 2И (в зависимости от состояния дешифратора 74) проходит на выход блока (управляющий импульс) и одновременно переводит триггер 87 в 1, а триггеры 83 и 86 через элементы 82 и 85 - в О. Триггер 87 запрещает прохождение тактовых импульсов через элемент 91. На этом работа блока заканчивается до прихода очередного управляющего импульса на вход блока.

Второй вычислитель 8 работает следующим образом.

Код измеренного-значения внешнего параметра подается на информационный вход регистра 93, а его номинальное значение - на.вход регистра 92. Управляющий импульс через элемент 96 типа 2И, через элемент 105 типа 2И-Н сбрасывает в О триггеры 101, 102 и 107 и регистр 95, через элемент 97 типа 2ИЛИ переводит триггер 98 в 1. Триггер 98 разрешает по входу запись информации в регистры 92 и 93 и прохождение тактовых импульсов через элемент 99 типа ЗИ и запрещает прохождение управляюш 1х импульсов через элемент 96. Первый тактовый импульс через элемент .99 записывает по входу С информацию в регистры 92 и 93 и переводит триггер 100 в 1. Триггер 100 разрешает по входу V запись в регистр 95 информации с выход сумматора 94 и прохождение тактовых импульсов через элемент 101 типами и запрещает прохождение через элемент 99. Второй тактовый импульс через элемент 101 по входу С записывает информацию с выхода йумматора 94 в регистр 95 и переводит триггер 102 в 1. Триггер 102 запрещает прохождение тактовых импульсов через эле- ент 101 и разрешает их прохождение через элемент 103 типа ЗИ. Третий импульс через элемент 103 проходит на выход блока (управляющий импульс) через элемент 106 типа 2ИГ1И-НЕ, сбрасывает регистры 92 и 93 в О, через элемент 97 переводит триггер 98 в О и переводит триггер 107 в 1. Триггер 107 запрещает прохождение импульсов через элемент 103. На этом работа блока прекращается до прихода на его вход следующего управляющего импульса.

Первый вычислитель 9 работает следующим образом ;

Управляющий импульс, поступающий с входа блока,через элемент 108 типа ЗИЛИ и элемент 117 типа 2ИЛИ-НЕ сбрасывает в О триггеры 114 и 116, через элемент 109 типа 2И изменяет состояние счетчика 128 на единицу, а через элемент 110 типа 2ИЛИ переводит триггер 111 в 1. Выходной код счетчика 128 определяет адрес ячейки регистра (ЗУ) 127, в который записывается входная информация /iX с входа блока. Триггер 111 запрещает даль-, нейшее прохождение управляющих им- с пульсов через элемент 109 и разрешает их прохождение через элемент 112 типа ЗИ. Первый тактовый импульс через элемент 112, элемент 129 по входу V записывает входную информацию в ЗУ 127, а через элемент 1 12 типа 2ШШ переводит триггер 114 в 1.Триггер 114 запрещает прохождение импульсов через Элемент 112 и разрешает их прохождение через элемент 115 типа ЗИ. Второй тактовый импульс через элемент 115 поступает на вход триггера 116 и через элемент 132 типа 2И на выход блока (управляющий импульс) . и переводит триггеры 111 и 114 через элементы 110 и 1-12 в О. Триггер 116 переходит в 1, запрещает прохождение импульсрв через элемент 115 и выдает разрешение в элементы 130 и 120. Описанный процесс повторяется до записи в ЗУ 127 всех значений изменений 5 внешних п&раметров dX,-. Тогда дешифратор 123 выходного кода счетчика 128 разрешает прохождение тактового импульса с выхода элемента 115 также на вход триггера 119 через элемент 118, типа ЗИ. Триггер 119 переходит в 1, запрещает прохождение импульсов через элемент 118, разрешает их прохождение через элемент 126 типа 2И, вьодает разрешение в элемент 130 и элемент 125 типа 2И. Единичные потенциалы с выхода триггера 116 и дешифратора 125 через элемент 121 и элемент 122 типа 2Ш1И-НЕ сбрасывают счет0

5

0

0

5

чик 128 в О. Теперь управляющие

импульсы поступают с входа блока, когда меняется адрес датчика внутреннего параметра, или с входа, когда в блоке сумматора производится очередная операция суммирования. При этом информация считывается из ЗУ 127, а управляющий импульс проходит на выход блока через элемент 126. Выходной код счетчика 128 (поправка в младшие разряды адреса ячейки ЗУ

127 блока хранения данных) через элв мент 120 типа 2И выдается на выход блока. После окончания измерения всех внутренних параметров с входа блока поступает управляющий импульс из блока формирования адреса. Этот импульс через элемент 124 типа 2ИЛИ- НЕ сбрасывает триггер 119 в О, после чего блок готов к новому циклу измерений.

Третий вычислитель 10 работает следующим образом.

Импульс управления через элемент 135 типа 2И и через элемент 154 типа 2И11И-НЕ сбрасывает в О регистры

133,134 и 160, триггеры 138, 142, 145, 147 и 159, счетчик 148 и через элемент 162 регистр 157. Одновременно триггер 136 переводится в 1. Триггер 136 запрещает прохождение управляющих импульсов через элемент 135 и разрешает их прохождение через элементы 137 типа ЗИ. Импульс тактовой частоты через элемент 137 записывает по входу С, информацию лХ; в регистр 133 и информацию Х| в регистр

134,переводит триггер 138 в 1. Триггер 138 разрешает сдвиг по входу V информации в регистра 134, прохождение второго тактового импульса через элемент 139 типа 4И, и запрещает его прохождение через элемент 137. Второй импульс через элемент 139 сдвигает информацию в регистре 134 в сторону старшего разряда. Если после сдвига в старшем разряде окажется .опять О, то поступает следующий импульс и т.д. до тех пор, пока в старшем разряде не окажется 1. Тогда элемент 155 типа ИЛИ-НЕ запрещает прохождение тактовых импульсов через элемент 139, а 1 в старшем разряде регистра 134 разрешает его прохождение через элемент 140 типа ЗИ. При этом каждый импульс сдвига поступает на вход счетчика 148. Импульс тактовой частоты через элемент 140 записывает по входу С в регистр

157информацию из сумматора 156, т.е значение регистра 133, через элемент

158 типа 2И переводит триггер 189 в 1, а через элемент 141 типа 2ИЛИ - триггер 142 в 1. Триггер 159 разрешает по входу V сдвиг информации в регистре 133 и запрещает прохождение импульсов через элемент 158. Триггер il42 разрешает запись по входу V информации из регистра 157 в регистр 160, прохождение импульсов через

0

5

0

5

0

элемент 143 типа ЗИ и запрещает их прохождение через элемент 139, а также запрещает запись информации в регистр 157. Тактовый 1шпульс через элемент 143 записывает по входу С информацию из регистра 157 в регистр 160 и через элемент 144 типа 2ИЛИ переводит триггер 145 в 1. Триггер 145 запрещает прохождение импульсов через элемент 143, разрешает их прохождение через элемент 46 типа ЗИ и выдает разрешение в элемент 161 типа ЗИ. Импульс тактовой частоты через э,лемент 146 переводит триггер 147 в I, через элемент 150 типа 2И и элемент 141 переводит триггер 42 в О, через элемент 162 сбрасывает регистр 157 в О, через элемент 144 переводит триггер 145 в О и через элемент 153 сдвигает на один разряд информацию в регистрах 133 и 134. Триггер 147 запрещает прохождение импульсов через элемент 146. Так как триггер 142 снял запрет на прохождение импульсов через элемент 139, то, если в,старшем разряде регистра 134 оказывается О, импульсы начинают проходить через элемент 139 и описанный процесс повторяется. Если вместо О появляется I, то

импульс проходит череэ элемент 140 и описанный процесс повторяется. Это происходит до тех пор, пока код счетчика сдвигов 148 не оказывается

35 равным количеству разрядов .регистра 134. Тогда дешифратор 149 выдает разрешение на прохождение импульсов с выхода элемента 146 через элемент 152 типа 2И на выход блока (управля0 ющий импульс), одновременно разрешается вывод информации с выхода регистра 157 через элемент 161 на выход блока. Импульс с выхода элемента 152 через элемент 163 типа 2ИЛИ-НЕ сбра5 сывает триггер 136 в О, На этом работа блока заканчивается до прихода следующего управляющего импульса.

Блок 1I суммирования работает следующим образом.

0 Управляющий импульс из дешифратора через элемент 164 типа 2И и элемент 188 типа 2ИЛИ-НЕ сбрасывает счетчик 190 в О, через элемент 189, типа 2ИЛИ-НЕ - триггер 187 в О,

5 через элемент 175 сбрасывает регистр 170 в О

, а также переводит триггер 165 в I. Триггер 165 запрещает прохождение управляющих импульсов через элемент 164, разрешает по входу V

313

запись информации в регистры 170- 172., разрешает прохождение импульсов через элемент 166 типа ЗИ, выдает разрешение в элемент 168 типа 4И и элемент 192 типа ЗИ. Тактовьй импульс через элемент 166, элемент 194 типа 2И и элемент 199 по входу С записывает информацию в регистр 171, поступающую через элементы 192, 174 и 200 на выход блока, поступает на вход триггера 167 и переводит его в 1, Триггер 167 запрещает прохождение импульсов через элемент 166, разрешает их прохождение через элемент 168, выдает разрешение, в элементы 195 и ,197 типа 2И.

Управляющий импульс из блока под- готовки данных через элемент 176 типа 2ИЛИ-НЕ сбрасывает триггеры 178, 180 и 182 в О, через элемент 168 переводит триггер 169 в 1, по вход С записывает информацию в регистр 172, через элемент 189 типа 2ИЛИ-НЕ сбрасывает в О триггер 187, через элемент 175 типа ЗИЛИ-НЕ - в О регистр 170.

Триггер 169 разрешает прохождение импульсов через элемент 177 типа ЗИ. Тактовый импульс через элемент 177 переводит триггер 178 в 1, по вхо ду С записывает информацию с выхода сумматора 173 в регистр 170,изменяет состояние счетчика 190 на единицу.

Триггер 178 запрещает прохождение импульсов через элемент 177 и разрешает их прохождение через элемену 179 типа ЗИ. Тактовый импульс через элемент 179 переводит триггер 180 в 1, через элемент 193 сбрасывает в О регистры 170 и 171.Триггер 180 запрещает прохождение импульсов через элемент 179 и разрешает их прохождение через элемент 181 типа 4И. . Тактовый импульс через элементы 181, 183 (типа 2И) и 200 проходит на выход блока (управляющий импульс), через элементы 195 (типа 2И) и 199 (типа 2ИЛИ) по входу С записывает информацию с выхода регистра 170 в регистр 171, через элемент 196 типа 2ИЛИ сбрасывает в О триггер 169, Следующий импульс с входа блока сбрасывает в О триггеры 178, 180 и 182 и через элемент 168 начинает описанный цикл. Это происходит до тех пор, пока на вьпсоде счетчика 190 не окажется код, соответствующий числу внешних параметров. Тогда дешифратор 191 запрещает прохождение импульса

0

15

20

25

6993

14

с выхода элемента 181 через элементы 183 и 200 на выход блока, но разрешает их прохождение через элемент 185 типа 2И на выход блока (управляющий импульс) и через элемент 186 типа ЗИ на вход триггера 187. Триггер 187 переходит в 1 и разрешает выдачу информации через элемент 179 типа 2И с выхода регистра 170. Импульс с выхода элемента 185 сбрасывает в О триггеры 165 и 167. На этом работа блока заканчивается до прихода следующего управляющего импульса на вход блока (запись очередного изме30

35

40

рительного сигнала У }.

Блок 12 сравнения работает следующим образом.

По управляющему импульсу из блока дешифратора в регистры 201 и 203 записывается инфор мация из блока хранения данных. Управляюпщй импульс с входа блока через элемент 212 типа 2И переводит триггер 213 в 1, через элемент 221 типа 2ИЛИ-НЕ сбрасывает в О регистр 20Д и триггеры 215 и 220. Триггер 213 запрещает прохождение импульсов через элемент 212 . и разрешает их прохождение через элемент 214 типа ЗИ, а также разрешает запись информации по входу V в регистр 204. Первый тактовый импульс через элемент 214 записывает по входу С информацию из блока сумматора в регистр 204 и переводит триггер 215 в 1. Триггер 215 запрещает прохождение импульсов через элемент 214, разрешает их прохождение через э; емент 219 типа ЗИ вьща- ет разрешение в элементы 207 и 210 типа 5И и в элемент 216 типа 4И.

В су шаторах 205 и 208 сравнивается приведенное значение измеренного параметра соответственно с .минимально и максимально допустимыми значениями изменяемого параметра. Если приведенное значение измеренного параметра находится за пределами верхнего или нижнего допуска, тЬ в знаковом разряде сумматора 205 (или 208) появляется разрешающий потенциал, который подается в элемент 207 (или 210). Поэтому импульс тактовой частоты проходит через элемент 207 или

210 на выход блока (управляющий импульс) для останова всего устройства. Если приведенное значение измеренного параметра находится в допуске, то элементы 217 и 218 типа ИЛИ-НЕ выдают разрешения в элемент 216 типа 4И, через который проходит тактовый импульс на выход блока (управляющий импульс) для продолжения работы устройства.

Формула изобретения

Устройство контроля состояния объектов, содержащее коммутатор, пер вые информационные входы которого являются информационными входами устройства, а выход подключен к информационному входу аналого-цифрового пре образователя, первый вычислитель, блок сравнения, подключенный первым выходом к первом информационному входу блока индикации, блок управления, соединенный первым и вторым вы- ходами соответственно с первым информационным и первым управляющим входами блока памяти, а третьим выходом - с первым управляющим входом первого вычислителя, отлича-. ю щ е е с я тем, что, с целью повышения надежности и быстродействия устройства, в него введены второй и третий вычислители, блок суммирования, дешифратор и генератор импульсов подключенный первым и вторым выходами соответственно к входам установки в начальное состояние и синхронизирующим входам аналого-цифрового преобразователя, блока управления, коммутатора, дешифратора, первого, второго и третьего вычислителей, блока индикации, блока сравнения, блока суммирования, блока памяти, а третьим выходом - к первому входу блока управления, управляющему входу коммутатора и первому управляющему входу аналого-цифрового преобразователя, связанного информационными выходами и выходом Конец преобразования с первыми и вторыми соответственно входами дешифратора, подключенного первым выходом к первому информационному входу блока суммирования, вторым выходом - к второму управляющему входу первого вычислителя, а третьими и четвертым выходами - соответствен

0 5 0 5 Q

0

5

но к первым информационным и управляющему входам второго вычислителя, соединенного вторыми информационными входами с первыми выходами блока памяти, а информационными выходами и выходом Конец вычисления - соответственно с информационными входами и третьим управляюш;им входом первого вычислителя, подключенного первыми информационными выходами к вторым информационным входам блока памяти, а вторыми информационными выходами - к первым информационным входам третьего вычислителя, соединенного вторыми информационными входами и управляющим входом соответственно с вторыми выходами и выходом Считьшание блока памяти, а выходом Конец вычисления и информационны} выходами - соответственно с первым управляющим и вторыми информационными входами блока суммирования, подключенного вторым управляющим входом к второму выходу дешифратора, управляющему входу блока индикации и первому управляющему входу блока сравнения, первым и вторым выходами Конец вычисления - со- ответственно к второму управляющему входу блока сравнения и четвертому управляющему входу первого вычислителя, а информационными выходами - к первым информационным входам блока сравнения, связанного выходом Конец сравнения с вторым входом блока управления, а и третьими информационными входами - с третьими и четвертыми выходами блока памяти, подключенного пятыми информационными выходами к вторым информационным входам коммутатора, третьим входам дешифратора и вторым информационным входам блока индикации, управляющим выходом - к второму управляющему входу аналого-цифрового преобразователя, а вторым управляющим входом - к первому выходу Конец вычисления первого вычислителя, соединенного вторым выходом Конец вычисления с третьим входом управления, блокирующий вход генератора импульсов подключен к выходу блока индикации.

/4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики состояний объекта | 1989 |

|

SU1679468A1 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Устройство контроля и диагностики состояний технического объекта | 1987 |

|

SU1504653A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1441399A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для коррекции программ | 1983 |

|

SU1141416A1 |

| Устройство для входного контроля изделий | 1990 |

|

SU1746388A2 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Устройство для регистрации информации | 1989 |

|

SU1603412A1 |

Изобретение относится к области автоматики и вычислительной техники и предназначено для автоматизации контроля состояния сложных пневмогидравлических систем энергетических установок. Цель изобретения - повьшение надежности и быстродействия устройства. Устройство содержит генератор импульсов 2, блок 3 управления, блок памяти 4, коммутатор 5, аналого-цифровой преобразователь 6, дешифратор 7, вычислители 8, 9,10, блок суммирования 11, блок сравнения 12, блок индикации 13. Цель достигается за счет уменьшения поля допуска измеряемых параметров. 12 ил.

г

ton

20

2f

/J

фиг.2

IB

r-Л

19

/2«

Фие. 5

дзие.

57

cpue.S

(ри.б

&U::n

es

91

в7

4

86

tfruB7

С

271

V У

93

С 3}

92

т

//7«Д

г

м

-tajh

срие.в

ПГ7

5

- Й73

F

я«

п

101

т,

- ire

т

in

л

1г2,.

Dm V

D

П

Й7

л

т

115

г-К

фие.9

фиг. 10

фи9.11

| Устройство для контроля параметров | 1975 |

|

SU607190A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-01-15—Публикация

1985-12-02—Подача