1-п;-п-I-п

1 N17 Пк п« ПгI

У г-т-гЧ

К

ff

-о Ш

сл

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент | 1984 |

|

SU1173551A1 |

| Устройство согласования | 1984 |

|

SU1173552A1 |

| Д-триггер | 1984 |

|

SU1221714A1 |

| Триггер | 1983 |

|

SU1150734A1 |

| Логическое устройство | 1984 |

|

SU1213521A1 |

| Логический элемент И-НЕ ИШЛ | 1985 |

|

SU1262720A1 |

| Элемент транзисторно-транзисторной ложки (его варианты) | 1985 |

|

SU1274149A1 |

| Триггер | 1986 |

|

SU1319253A1 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| Аналоговое запоминающее устройство | 1983 |

|

SU1104587A1 |

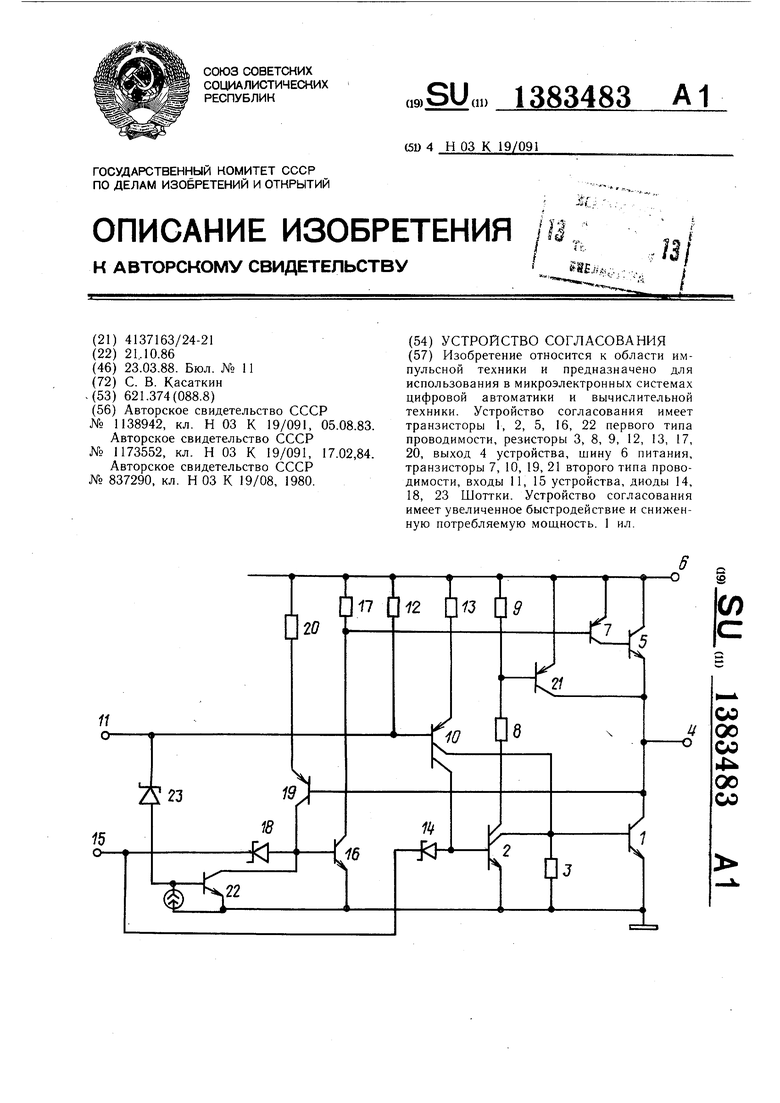

Изобретение относится к области импульсной техники и предназначено для использования в микроэлектронных системах цифровой автоматики и вычислительной техники. Устройство согласования имеет транзисторы 1, 2, 5, 16, 22 первого типа проводимости, резисторы 3, 8, 9, 12, 13, 17, 20, выход 4 устройства, шину 6 питания, транзисторы 7, 10, 19, 21 второго типа проводимости, входы 11, 15 устройства, диоды 14, 18, 23 Шоттки. Устройство согласования имеет увеличенное быстродействие и сниженную потребляемую мощность. 1 ил.

11

О

/Л15

18 -Йfc

к

П8

//

со

00

со

4

00

со

f

r-f

г

Изобретение относится к импульсной технике и предназначено для использования в микроэлектронных системах цифровой автоматики и вычислительной техники.

Цель изобретения - увеличение быстродействия и снижение потребляемой мощности устройства согласования.

На чертеже представлена принципиальная схема предлагаемого устройства согласования.

Устройство согласования содержит первый транзистор 1 первого типа проводимости, эмиттер которого подключен к общей шине, база подключена к первому коллектору второго транзистора 2 первого типа проводимости и через первый резистор 3 - к общей щине, а коллектор подключен к выходу 4 устройства и к эмиттеру третьего транзистора 5 первого типа проводимости, коллектор которого подключен к тине 6 питания, а база подключена к коллектору первого транзистора 7 второго типа проводимости, эмиттер которого подключен к щине б питания, второй кол.лектор транзистора 2 первого типа проводимости через последовательно включенные второй и третий резисторы 8 и 9 подключен к щине 6 питания, эмиттер подключен к общей шине, а база - к первому коллектору второго транзистора

10второго типа проводимости, база которого подключена к управляющему входу

11устройства и через четвертый резистор

12к шине 6 питания, эмиттер подключен через пятый резистор 13 к щине 6 питания, а второй коллектор подключен к первому коллектору транзистора 2 первого типа проводимости, база которого подключена к аноду первого диода 14 Шоттки, катод которого подключен к информационному входу 15 устройства, база транзистора 7 второго типа проводимости подключена к коллектору четвертого транзистора 16 первого типа проводимости, эмиттер которого подключен к обшей щине, коллектор через шестой резистор 17 - к щине 6 питания, а база подключена к аноду второго диода 18 Шоттки и к коллектору третьего транзистора 19 второго типа проводимости, эмиттер которого через седьмой резистор 20 подключен к шине 6 питания, а база подключена к выходу 4 устройства, катод диода 18 Шоггки подключен к информационному входу устройства 15, объединенные между собой выводы резисторов 8 и 9 подключены к базе четвертого транзистора 21 второго типа проводимости, эмиттер которого подключен к щине 6 питания, а коллектор - к выходу 4 устройства, база транзистора 16 первого типа проводимости подключена к коллектору пятого транзистора 22 первого типа проводимости с инжекционным питанием, база которого подключена к аноду третьего диода 23 Шоттки, катод которого подключен к управляющему входу устройства 11.

Устройство работает следующим образом.

Когда на вход 11 управления подается низкий уровень напряжения, соответствующий сигналу логического «О (т.е. управля- ющий этим входом инжекционный транзистор насыщен), устройство работает в состоянии «Включено на выходе 4. Транзистор 10 открыт, суммарный ток его коллекторов определяется как

10 г (Цб-Цэб- икэн.).Вр К|з(Вр+1)

5

0

где IKIO-- суммарный ток коллекторов транзистора 10;

Us - напряжение щины 6 питания; Уэб - падение напряжения на базо-эмит- терном переходе открытого транзистора ( 0,6 В);

UKSH - напряжение между эмиттером и коллектором насыщенного инжек- 0ционного транзистора (,1 В);

Ri3 -сопротивление резистора 13; Вр - коэффициент усиления по току р-п-р транзистора (здесь транзистора 10).

Необходимое соотнощение токов пер- 5 вого и второго коллекторов транзистора 10 задается конструктивно, например, соотношением площадей этих коллекторов.

При сигнале логического «О на входе 11 через диод 23 Шоттки щунтируется на общую щину без транзистора 22, ток инжектора этого транзистора ответвляется управляющим этим входом транзистором, транзистор 22 закрыт.

Если теперь на вход 15 поступит сигнал логического «О, то ток первого коллектора транзистора 10 ответвляется через диод 14 Шоттки из базы транзистора 2, транзистор 2 закрывается, ток второго коллектора транзистора 10 поступает в базу транзистора 1, транзистор I открывается и

0 входит в режим насыщения. Одновременно коллекторный ток транзистора 19 через диод 18 Шоттки ответвляется управляющим входом 15 транзистором из базы транзистора 16. Транзистор 16 запирается, при этом база транзистора 7 через резистор 17 щунтиру ется на щину 6 питания, транзистор 7 также запирается, а следовательно, запирается из- за отсутствия тока в базу транзистора 5. Так как транзистор 2 запирается, то база транзистора 21 через резистор 9 щунтируется на щину 6 питания. Транзистор 21 запирается. На выходе 4 устройства формируется сигнал логического «О, т.е. низкий уровень напряжения 0,1-0,2В, что соответствует логическому «О стандартных ТТЛ- схем. Так как на базу транзистора 19 посту5 пает в этом случае низкий уровень напряжения, равный уровню напряжения на выходе 4, то транзистор 19 открыт, его коллекторный ток определяется выражением

I9

(U6- Цэб-U4)-Bp

R20 ()

где U4 - напряжение на выходе 4 устройства Rao - сопротивление резистора 20;

IK 19 .- коллекторный ток транзистора 19. Если теперь на вход 15 приходит сигнал логической «1 (управляющий этим входом инжекционный транзистор закрыт), ток первого коллектора транзистора 10 поступает в базу транзистора 2, вызывая его отпира- ние, транзистор 2 открывается и входит в режим насыщения, ответвляя из базы транзистора 1 ток второго коллектора транзистора 10, транзистор 1 запирается. Одновременно с этим коллекторный ток транзисто- ра 19 поступает в базу транзистора 16, вызывая его отпирание. Транзистор 16 открывается и работает в режиме усиления тока, его коллекторный ток вызывает отпирание транзистора 7, а следовательно, и транзистора 5. При этом обеспечивается повы- щенный по отнощению к схеме известного устройства ток перезаряда нагрузочной емкости на выходе 4, так как в отличие от известной схемы между коллектором транзистора 16 и базой транзистора 7 в предлагав- мой схеме отсутствует резистор, ограничивающий ток базы транзистора 7.

Так как транзистор 2 открывается, ток его второго коллектора вызывает отпирание транзистора 21, ток коллектора транзистора 21 определяется как

, (Us- Цэб- Цкэн) Вр I,,, .

где IK21 - ток коллектора транзистора 21; Rs - сопротивление резистора 8.

Из условия минимального значения ВР (определяется технологией) сопротивление резистора 8 рассчитывается таким образом, чтобы при логической «1 на выходе 4 (для ТТЛ-схем 2,4 В) обеспечивался необходи... мый вытекающий ток логической «1.

Таким образом, так как транзистор 1 закрывается, а транзисторы 5 и 21 открываются, на выходе 4 устройства формируется сигнал логической «1 (2,4 В). При этом, по мере нарастания напряжения на выходе 4, а следовательно, и на базе тран- зистора 19, ток коллектора транзистора 19 уменьщается (выражение 1) и при достижении уровня U4 Ue- иэб транзистор 19 запирается, а следовательно (из-за отсутствия базовых токов), запираются транзисто- ры 16, 7 и 5. Дальнейщий заряд емкости и нарастание напряжения на выходе 4 обеспечивается коллекторным током транзистора 21. Максимальное напряжение на выходе 4 определяется из соотношения U4 U6- UK, где U - максимальное напряжение на выходе 4, а - максимально возможное напряжение между коллектором и эмиттером транзистора 21 в режиме усиления, величина которого, как правило, составляет 0,3-0,4 В, следовательно, напряжение питания Ue может быть снижено до 3 В.

При подаче на вход 11 сигнала логической «1 база транзистора 10 шунтируется через резистор 12 на шину 6 питания. Транзистор 10 запирается. Базы, транзисторов 1 и 2 независимо от состояния на входе 15 обесточиваются. База транзистора 1 через резистор 3, а база транзистора 21 через резистор 9 шунтируются соответственно на общую шину и шину 6 питания. Транзисторы 1 и 21 запираются. При сигнале логической «1 на входе 11 ток инжектора транзистора 22 поступает в базу транзистора 22, транзистор 22 открывается и входит в режим насыщения, шунтируя при этом на общую шину базу транзистора 16. Независимо от состояния на входе 15 транзистор 16 закрывается, при этом база транзистора 7 шунтируется через резистор 17 на шину 6 питания. Транзистор 7 запирается, а следовательно, запирается и транзистор 5. На выходе устройства устанавливается состояние «Выключено.

Формула изобретения

Устройство согласования, содержащее первый транзистор первого типа проводимости, эмиттер которого подключен к общей шине, база подключена к первому коллектору второго транзистора первого типа проводимости и через первый резистор - к общей шине, а коллектор подключен к выходу устройства и к эмиттеру третьего транзистора первого типа проводимости, коллектор которого подключен к щине питания, а база - к коллектору первого транзистора второго типа проводимости, эмиттер которого подключен к шине питания, второй коллектор второго транзистора первого типа проводимости через последовательно включенные второй и третий резисторы подключен к шине питания, эмиттер - к общей щине, а база - к первому коллектору второго транзистора второго типа проводимости, база которого подключена к управляющему входу устройства и через четвертый резистор - к шине питания, эмиттер подключен через пятый резистор к щине питания, а второй коллектор - к первому коллектору второго транзистора первого типа проводимости, отличающееся тем, что, с целью увеличения быстродействия и снижения потребляемой мощности, база второго транзистора первого типа проводимости подключена к аноду первого диода Шоттки, катод которого подключен к информационному входу устройства, база первого транзистора второго типа проводимости подключена к коллектору четвертого транзистора первого типа проводимости, эмиттер которого подключен к общей шине, коллектор через шее1383483

56

tofl резистор - к шине питания, а база -па проводимости, эмиттер которого подклю- k аноду второго диода Шоттки и коллекто-чен к шине питания, а коллектор - к вы- ру третьего транзистора второго типа про-ходу устройства, база четвертого тран- 8ОДИМОСТИ, эмиттер которого через седьмойзистора первого типа проводимости под- резистор подключен к шине питания, а ключена к коллектору пятого транзистора (5аза - к выходу устройства, катод вто-первого типа проводимости с инжекцион- рого диода Шоттки подключен к информа-ньш питанием, база которого подключена ционному входу устройства, общая точкак аноду третьего диода Шоттки, катод ко- i Toporo и третьего резисторов подключенаторого подключен к управляющему входу К базе четвертого транзистора второго ти-устройства.

| Устройство согласования | 1983 |

|

SU1138942A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство согласования | 1984 |

|

SU1173552A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР № 837290, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-03-23—Публикация

1986-10-21—Подача