Изобретение относится к импульсной технике и предназначено для использования в микроэлектронных системах цифровой автоматики и вычислительной техники.

Цель изобретения - уменьшение потребляемой мощности триггера.

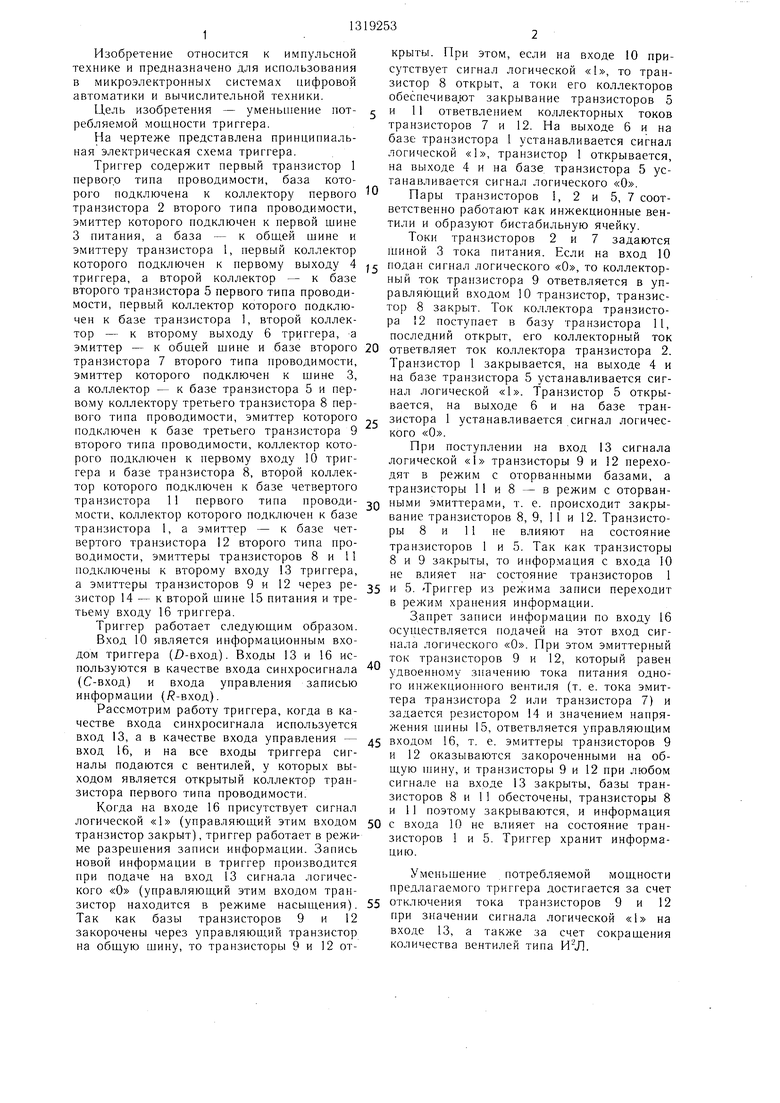

На чертеже представлена принципиальная электрическая схема триггера.

Триггер содержит первый транзистор 1 первого типа проводимости, база которого подключена к коллектору первого транзистора 2 второго типа проводимости, эмиттер которого подключен к первой шине 3 питания, а база - к обпдей шине и эмиттеру транзистора 1, первый коллектор

10

крыты. При этом, если на входе 10 присутствует сигнал логической «1, то транзистор 8 открыт, а токи его коллекторов обеспечивают закрывание транзисторов 5 и 11 ответвлением коллекторных токов транзисторов 7 и 12. На выходе 6 и на базе транзистора I устанавливается сигнал логической «1, транзистор 1 открывается, на выходе 4 и на базе, транзистора 5 устанавливается сигнал логического «О.

Пары транзисторов I, 2 и 5, 7 соответственно работают как инжекционные вентили и образуют бистабильную ячейку.

Токи транзисторов 2 и 7 задаются 1ИИНОЙ 3 тока питания. Если на вход 10

которого подключен к первому выходу 4 j гюдан сигнал логического «О, то коллектор- триггера, а второй коллектор - к базе ный ток транзистора 9 ответвляется в уп- второго транзистора 5 первого типа проводи- равляющий входом 10 транзистор, транзис- мости, первый коллектор которого подклю- тор 8 закрыт. Ток коллектора транзисто- чеп к базе транзистора 1, второй коллек- ра 12 поступает в базу транзистора 11, тор - к второму выходу 6 триггера, апоследний открыт, его коллекторный ток

эмиттер - к общей щине и базе второго 20 ответвляет ток коллектора транзистора 2. транзистора 7 второго типа проводимости. Транзистор 1 закрывается, на выходе 4 и эмиттер которого подключен к щине 3, на базе транзистора 5 устанавливается сиг- а коллектор - к базе транзистора 5 и пер- нал логической «1. Транзистор 5 откры- вому коллектору третьего транзистора 8 пер- вается, на выходе 6 и на базе тран- вого типа проводимости, эмиттер которого - зистора 1 устанавливается сигнал логичес- подключен к базе третьего транзистора 9 кого «О.

второго типа проводимости, коллектор кото-При поступлении на вход 13 сигнала

рого подключен к первому входу 10 триг- логической «1 транзисторы 9 и 12 перехо- гера и базе транзистора 8, второй коллек- дят в режим с оторванными базами, а тор которого подключен к базе четвертого транзисторы 11 и 8 - в режим с оторван- транзистора 11 первого типа проводи- Q пыми эмиттерами, т. е. происходит закры- мости, коллектор которого подключен к базе вание транзисторов 8, 9, 11 и 12. Транзисто- транзистора 1, а эмиттер - к базе четвертого транзистора 12 второго типа проводимости, эмиттеры транзисторов 8 и 11 подключены к второму входу 13 триггера,

а эмиттеры транзисторов 9 и 12 через ре- 35 и 5. -Триггер из режима записи пере.ходит зистор 14 - к второй щине 15 питания и тре- в режим хранения информации, тьему входу 16 триггера.Запрет записи информации по входу 16

Триггер работает следующим образом. осуществляется подачей на этот вход сиг- Вход 10 является информационным вхо- „ала логического «О. При этом эмиттерный дом триггера (D-вход). Входы 13 и 16 ис- ток транзисторов 9 и 12, который равен

, nr f dlJLI IA, Oil J НО

ры и 11 не влияют на состояние транзисторов 1 и 5. Так как транзисторы 8 и 9 закрыты, то ипфор.мация с входа 10 не влияет на- состояние транзисторов

пользуются в качестве входа синхросигнала (С-вход) и входа управления записью информации (/ -вход).

Рассмотрим работу триггера, когда в качестве входа синхросигнала используется

удвоенному значению тока питания одного инжекционного вентиля (т. е. тока эмиттера транзистора 2 или транзистора 7) и задается резистором 14 и значением напряжения 1ИИНЫ 15, ответвляется управляющим

вход 16, и на все входы триггера сигналы подаются с вентилей, у которых выходом является открытый коллектор транзистора первого типа проводимости.

Когда на входе 16 присутствует сигнал

вход 1:3, а в качестве входа управления - 45 входом 16, т. е. эмиттеры транзисторов 9

и 12 оказываются закороченными на общую Hjnny, и транзисторы 9 и 12 при любом сигнале на входе 13 закрыты, базы транзисторов 8 и 11 обесточены, транзисторы 8 и 11 поэтому закрываются, и информация логической «1 (управляющий этим входом 50 с входа 10 не влияет на состояние тран- транзистор закрыт), триггер работает в режи- зисторов 1 и 5. Триггер хранит информа- ме разрешения записи информации. Запись новой информации в триггер производится при подаче на вход 13 сигнала логического «О (управляющий этим входом транзистор находится в режиме насыщения). 55 отключения тока транзисторов 9 и 12 Так как базы транзисторов 9 и 12 ри значении сигнала логической «1 на закорочены через управляющий транзисторвходе 13, а также за счет сокращения

на общую шину, то транзисторы 9 и 12 от-количества вентилей типа H-Jl.

цию.

Уменьшение потребляемой мощности предлагаемого триггера достигается за счет

логической «1 транзисторы 9 и 12 перехо- дят в режим с оторванными базами, а транзисторы 11 и 8 - в режим с оторван- пыми эмиттерами, т. е. происходит закры- вание транзисторов 8, 9, 11 и 12. Транзисто-

и 5. -Триггер из режима записи пере.ходит в режим хранения информации, Запрет записи информации по входу 16

ры и 11 не влияют на состояние транзисторов 1 и 5. Так как транзисторы 8 и 9 закрыты, то ипфор.мация с входа 10 не влияет на- состояние транзисторов

, nr f dlJLI IA, Oil J НО

удвоенному значению тока питания одного инжекционного вентиля (т. е. тока эмиттера транзистора 2 или транзистора 7) и задается резистором 14 и значением напряжения 1ИИНЫ 15, ответвляется управляющим

входом 16, т. е. эмиттеры транзисторов 9

и 12 оказываются закороченными на общую Hjnny, и транзисторы 9 и 12 при любом сигнале на входе 13 закрыты, базы транзисторов 8 и 11 обесточены, транзисторы 8 и 11 поэтому закрываются, и информация с входа 10 не влияет на состояние тран- зисторов 1 и 5. Триггер хранит информа- отключения тока транзисторов 9 и 12 ри значении сигнала логической «1 на входе 13, а также за счет сокращения

цию.

Уменьшение потребляемой мощности предлагаемого триггера достигается за счет

Формула изобретения

Триггер, содержащий первый транзистор первого типа проводимости, база которого подключена к коллектору п-ервого транзистора второго типа проводимости, эмиттер которого подключен к первой шине питания, а база - к общей шине и эмиттеру первого транзистора первого типа проводимости, первый коллектор которого подключен к первому выходу триггера, а второй коллектор - к базе второго транзистора первого типа проводимости, первый коллектор которого подключен к базе первого транзистора первого типа проводимости, второй коллектор - к второму выходу триггера, а эмиттер - к общей шине и базе второго транзистора второго типа проводимости, эмиттер которого подключен к первой шине питания, а коллектор - к базе второго транзистора первого типа проводимости и первому коллектору третьего транзистора первого типа проводимости, эмиттер которого подключен к базе третьего транзистора

Редактор О. Юрковецкая Заказ 2529/54

ВИИИПИ Государственного комитета СССР по делам изобретений и открытий

I 13035, Москва, Ж-35, Раушская- наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

0

второго типа проводимости, коллектор которого подключен к первому входу триггера и базе третьего транзистора первого типа проводимости, второй коллектор которого подключен к базе четвертого транзистора первого тирпа проводимости, коллектор которого подключен к базе первого транзистора первого типа проводимости, а эмиттер - к базе четвертого транзистора второго типа проводимости, эмитт;ер которого соединен с

эмиттером третьего транзистора второго типа проводимости, а коллектор - с базой четвертого транзистора первого типа проводимости, эмиттер которого соединен с эмиттером третьего транзистора первого типа

5 проводимости, отличающийся тем, что, с целью уменьшения потребляемой мощности, в него введены третий вход, вторая нтна питания и резистор, при этом эмиттер третьего транзистора первого типа проводимости подключен к второму входу триг0 гера, а эмиттер третьего транзистора второго типа проводимости подключен к третьему входу триггера и через резистор к второй шине питания.

Составитель А. Янов

Техред И. ВересКорректор А. Зимокосов

Тираж 901 Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггер | 1986 |

|

SU1319254A1 |

| Д-триггер | 1984 |

|

SU1221714A1 |

| Устройство согласования интегральных инжекционных схем с линиями передачи коллективного пользования | 1983 |

|

SU1092726A1 |

| Устройство согласования | 1986 |

|

SU1383483A1 |

| Триггер | 1983 |

|

SU1150734A1 |

| Устройство согласования | 1984 |

|

SU1173552A1 |

| Логический элемент | 1984 |

|

SU1173551A1 |

| Устройство согласования | 1983 |

|

SU1138942A1 |

| Интегральный четырехзначный D-триггер | 1986 |

|

SU1338012A1 |

| Интегральный транзисторно-транзисторный логический элемент | 1980 |

|

SU902261A1 |

Изобретение относите к импульсно технике и может быть иснользовано и микро- электронных сжтемах цифрово автоматики и вычислительной техники. Цель изобретения - уменьшение потребляемой MOIUHOC- ти триггера. Устро(1ство содержит транзисторы второго типа ироводимости 2. 7, 9, 12. Для достижения поставлеииой цели в устрой ство введены резистор 14 и новые связи. 1 ил. t6. Юо оо кгк; Ю Сл

| Инжекционный Д-триггер | 1981 |

|

SU970652A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Д-триггер | 1979 |

|

SU843177A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-06-23—Публикация

1986-01-27—Подача