Изобретение ;Относится к импульсной технике и предназначено для использования в цифровых микроэлектронных устройствах.

Цель изобретения.- уменьшение потребляемой мощности путем отключения тока питания инжектирз ющих транзисторов в режиме записи или режиме хранения

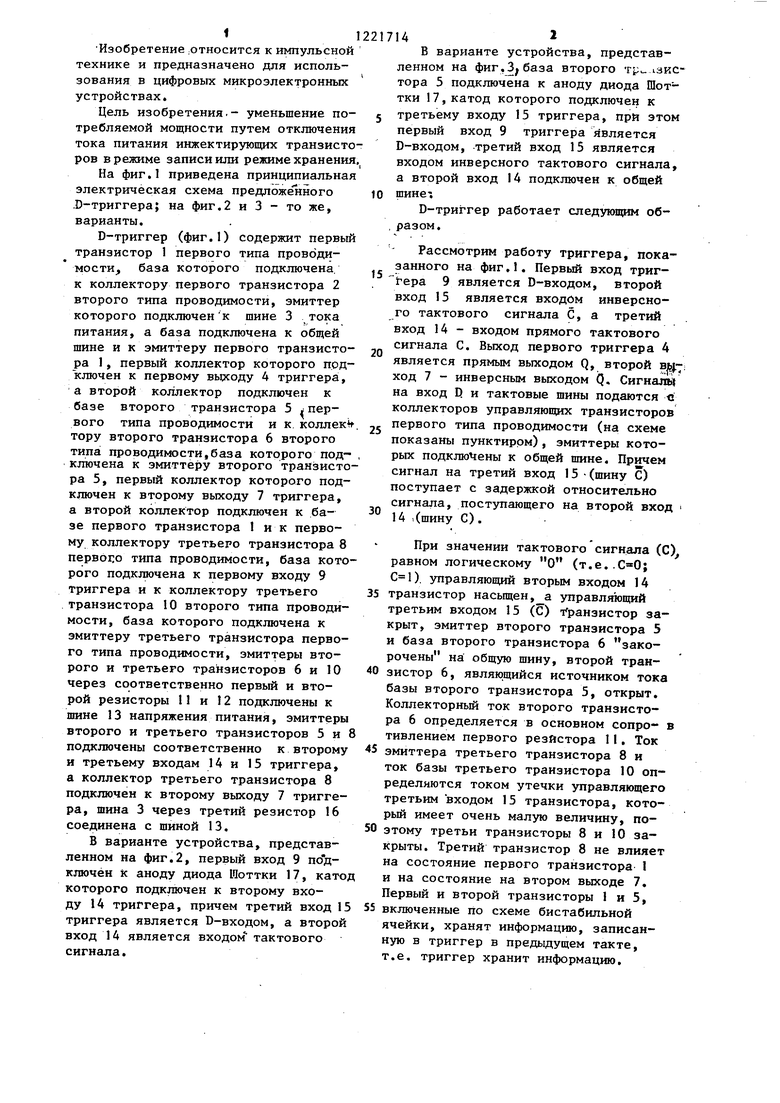

На фиг.1 приведена принципиальная электрическая схема предложенного .D-триггера; на фиг.2 и 3 - то же, варианты.

D-триггер (фиг.1) содержит первый транзистор 1 первого типа проводи- мости, база которого подключена. к коллектору первого транзистора 2 второго типа проводимости, эмиттер которого подключен к шине 3 тока питания, а база подключена к общей шине и к эмиттеру первого транзистора 1, первый коллектор которого подключен к первому вьрсоду 4 триггера, а второй коллектор подключен к базе второго транзистора 5 первого типа проводимости и к коллек тору второго транзистора 6 второго

типа проводимости,база которого под- ключена к эмиттеру второго транзистора 5, первый коллектор которого подключен к второму выходу 7 триггера, а второй коллектор подключен к базе первого транзистора 1 и к первому коллектору третьего транзистора 8 перво1;о типа проводимости, база которого подключена к первому входу 9 триггера и к коллектору третьего транзистора 10 второго типа проводимости, база которого подключена к эмиттеру третьего транзистора первого типа проводимости, эмиттеры второго и третьего транзисторов 6 и 10 через соответственно первый и второй резисторы 1I и 12 подключены к шине 13 напряжения питания, эмиттеры второго и третьего транзисторов 5 и подключены соответственно к второму и третьему входам 14 и 15 триггера, а коллектор третьего транзистора 8 подключен к второму выходу 7 триггера, шина 3 через третий резистор 16 соединена с шиной 13.

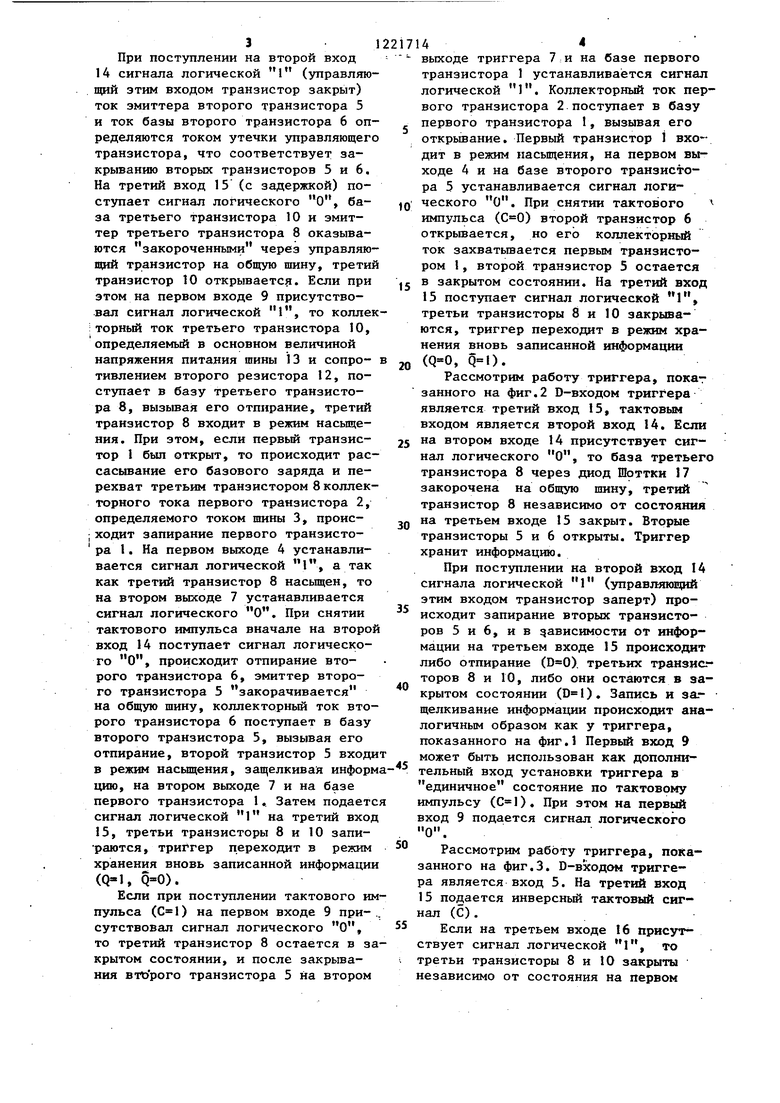

В варианте устройства, представленном на фиг.2, первый вход 9 по д- ключён к аноду диода Шоттки 17, като которого пoдкJПoчeн к второму вхо50 этому третьи транзисторы 8 и 10 з крыты. Третий транзистор 8 не вли на состояние первого транзистора- и на состояние на втором выходе 7 Первый и второй транзисторы 1 и 5

ду 14 триггера, причем третий вход 15 55 включенные по схеме бистабильиой

триггера является D-входом, а второй вход 14 является входом тактового сигнала.

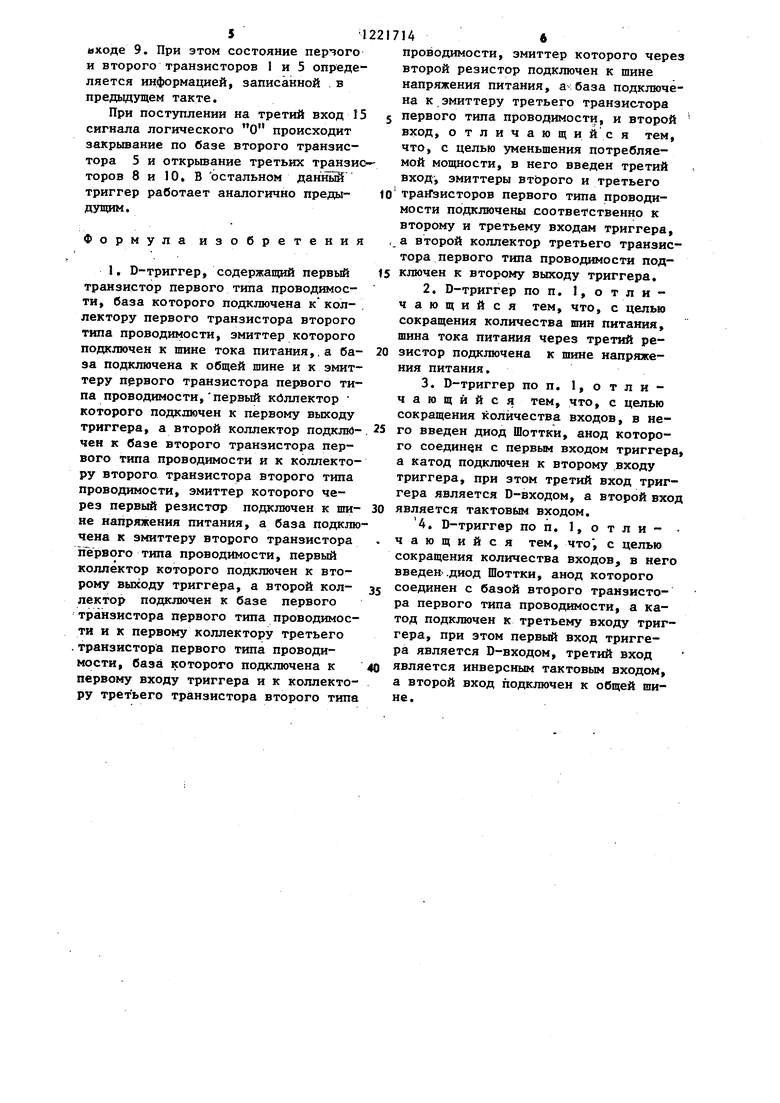

В варианте устройства, представленном на фиг.3;баэа второго тр.. laKC- тора 5 подключена к аноду диода Шоттки 17, катод которого подключен к третьему входу 15 триггера, при этом первый вход 9 триггера Является D-входом, третий вход 15 является входом инверсного тактового сигнала, а второй вход I4 подключен к общей щинел

D-триггер работает следующим образом.

:

Рассмотрим работу триггера, показанного на фиг.1. Первый вход триггера 9 является D-входом, второй вход 15 является входом инверсного тактового сигнала С, а третий вход 14 - входом прямого тактового сигнала С. Выход первого триггера 4 является прямым выходом Q, второй ход 7 - инверсным выходом Q. Сигналь} на вход Р и тактовые шины подаются с коллекторов управляющих транзисторов первого типа проводимости (на схеме показаны пунктиром), эмиттеры которых подключены к общей шине. Причем сигнал на третий вход 15 (шину С) поступает с задержкой относительно сигнала, поступающего на второй вход 14 .(шину С).

При значении тактового сигнала (С равном логическому О (т.е.. ), управляющий вторым входом 14

35 транзистор насьш1ен, а управляющий третьим входом 15 (С) т ранэистор закрыт, эмиттер второго транзистора 5 и база второго транзистора 6 закорочены на общую шину, второй тран40 зистор 6, являющийся источником тока базы второго транзистора 5, открыт. Коллекторный ток второго транзистора 6 определяется в основном сопро- тивлением первого резистора 1I. Ток

45 эмиттера третьего транзистора 8 и ток базы третьего транзистора 10 определяются током утечки управляющего третьим входом 15 транзистора, который имеет очень малую величину, по50 этому третьи транзисторы 8 и 10 закрыты. Третий транзистор 8 не влияет на состояние первого транзистора- 1 и на состояние на втором выходе 7. Первый и второй транзисторы 1 и 5,

55 включенные по схеме бистабильиой

ячейки, хранят информацию, записанную в триггер в предыдущем такте, т.е. триггер хранит информацию.

При поступлении на второй вход 14 сигнала логической 1 (управляющий этим входом транзистор закрыт) ток эмиттера второго транзистора 5 и ток базы второго транзистора 6 определяются током утечки управляющего транзистора, что соответствует за- крьгаанию вторых транзисторов 5 и 6. На третий вход 15 (с задержкой) поступает сигнал логического О, база третьего транзистора 10 и эмиттер третьего транзистора 8 оказываются закороченными через управляющий транзистор на общую шину, третий транзистор 10 открывается. Если при этом на первом входе 9 присутствовал сигнал логической 1, то коллек iторный ток третьего транзистора 10, определяемый в основном величиной напряжения питания шины 13 и сопро- тивлением второго резистора 12, поступает в базу третьего транзистора 8, вызывая его отпирание, третий транзистор 8 входит в режим насыщения. При этом, если первый транзистор 1 был открыт, то происходит рассасывание его базового заряда и перехват третьим транзистором 8 коллекторного тока первого транзистора 2, определяемого током шины 3, происходит запирание первого транзистора 1. На первом выходе 4 устанавливается сигнал логической 1, а так как третий транзистор 8 насьш ен, то на втором выходе 7 устанавливается сигнал логического О. При снятии тактового импульса вначале на второй вход 14 поступает сигнал логического О, происходит отпирание второго транзистора 6, эмиттер второго транзистора 5 закорачивается на общую шину, коллекторный ток второго транзистора 6 поступает в базу второго транзистора 5, вызывая его отпирание, второй транзистор 5 входи в режим насыщения, защелкива) информ цию, на втором выходе 7 и на базе первого транзистора 1. Затем подаетс сигнал логической 1 на третий вход 15, третьи транзисторы 8 и 10 запи- раются, триггер переходит в режим хранения вновь записанной информации (Q-1, ).

Если при поступлении тактового импульса () на первом входе 9 при-. сутствовал сигнал логического О, то третий транзистор 8 остается в закрытом состоянии, и после закрьша- ния BTto poro транзистора 5 на втором

выходе триггера 7,и на базе первого транзистора 1 устанавливается сигнал логической 1. Коллекторный ток первого транзистора 2.поступает в базу первого транзистора 1, вызывая его открьшание. Первый транзистор 1 вхо дит в режим насыщения, на первом выходе 4 и на базе второго транзистора 5 устанавливается сигнал логи Q ческого О. При снятии тактового импульса () второй транзистор 6 открьгоается, но его коллекторный ток захватьшается первым транзистором I, второй транзистор 5 остается

,5 в закрытом состоянии. На третий вход 15 поступает сигнал логической 1, третьи транзисторы 8 и 10 закрываются, триггер переходит в режим хранения вновь записанной информации

20 (. .

Рассмотрим работу триггера, покат занного на фиг.2 D-входом триггера является третий вход 15, тактовым входом является второй вход 14. Если

25 на втором входе 14 присутствует сигнал логического О, то база третьего транзистора 8 через диод Шоттки 17 закорочена на общую шину, третий транзистор 8 независимо от состояния

2Q на третьем входе 15 закрыт. Вторые транзисторы 5 и 6 открыты. Триггер хранит информацию.

При поступлении на второй вход 14 сигнала логической 1 (управляющий этим входом транзистор заперт) происходит запирание вторых транзисторов 5 и 6, ив 53ВИСИМОСТИ от информации на третьем входе 15 происходит либо отпирание (). третьих транзис.- торов 8 и 10, либо они остаются в закрытом состоянии (D 1) . Запись и за.- щелкивание информации происходит аналогичным образом как у триггера, показанного на фиг.1 Первый вход 9 может быть использован как дополни35

40

45

50

тельный вход установки триггера в единичное состояние по тактовому импульсу (). При этом на первый вход 9 подается сигнал логического О.

Рассмотрим работу триггера, показанного на фиг.З. D-входом триггера является вход 5. На третий вход 15 подается инверсный тактовый сигнал (С).

55 Если на третьем входе 16 присутствует сигнал логической 1, то

. третьи транзисторы 8 и 10 закрыты независимо от состояния на первом

«ходе 9. При этом состояние первого и второго транзисторов I и 5 определяется информацией, записанной в предыдущем такте.

При поступлении на третий вход 15 сигнала логического О происходит закрьшание по базе второго транзистора 5 и открывание третьих транзис торов 8 и 10, В остальном даннш триггер работает аналогично преды- дущим.

Формула изобретения

I. D-триггер, содержащий первьй транзистор первого типа проводимости, база которого подключена к коллектору первого транзистора второго типа проводимости, эмиттер которого подключен к шине тока питания,.а ба- за подключена к общей шине и к эмиттеру первого транзистора первого типа проводимости, первый кбллектор которого подключен к первому выходу триггера, а второй коллектор подклйчей к базе второго транзистора первого типа проводимости и к коллектору второго транзистора второго типа проводимости, эмиттер которого через первый резистсф подключен к ши- не напряжения питания, а база подключена к эмиттеру второго транзистора первого типа проводимости, первый коллектор которого подключен к второму выходу триггера, а второй кол- лектор подключен к базе первого транзистора первого типа проводимости и к первому коллектору третьего . транзистора первого типа проводимости, база которого подключена к первому входу триггера и к коллектору третьего транзистора второго типа

проводимости, эмиттер которого через второй резистор подключен к шине напряжения питания, а база подключена к эмиттеру третьего транзистора первого типа проводимости, и второй вход, отличающи и с я тем, что, с целью уменьшения потребляемой мощности, в него введен третий вход, эмиттеры второго и третьего транзисторов первого типа проводимости подключены соответственно к второму и третьему входам триггера, а второй коллектор третьего транзистора первого Типа проводимости подключен к второму выходу триггера,

2,D-триггер по п, 1, о т л и - чающийся тем, что, с целью сокращения количества шин питания, шина тока питания через третий резистор подключена к шине напряжения питания,

3.D-триггер поп, 1, отличающийся тем, что, с целью сокращения количества входов, в него введен диод Шоттки, анод которого соединен с первым входом триггера а катод подключен к второму входу триггера, при этом третий вход триггера является D-входом, а второй вхо является тактовым входом,

4, D-триггер по п, 1, о т л и - чающийся тем, что , с целью сокращения количества входов, в него введен-.диод Шоттки, анод которого соединен с базой второго транзистора первого типа проводимости, а катод подключен к третьему входу триггера, при этом первый вход триггера является D-входом, третий вход является инверсным тактовым входом, а второй вход подключен к общей шине.

iО

tput.S

Редактор Б. .Федотов

Составитель Г. .Погк арева

Техред И.ПоповичКорректор Е. Сярохмоя

Заказ 1618/57Тираж 816 ;Подписюе

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, MockBa, Ж.35, Раушская наб., д. 4/5 -,.

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггер | 1983 |

|

SU1150734A1 |

| Устройство согласования | 1984 |

|

SU1173552A1 |

| Устройство согласования | 1986 |

|

SU1383483A1 |

| D-триггер | 1985 |

|

SU1332380A1 |

| Триггер | 1986 |

|

SU1319254A1 |

| Триггер | 1986 |

|

SU1319253A1 |

| Логический элемент | 1984 |

|

SU1173551A1 |

| @ -Триггер | 1984 |

|

SU1188862A1 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| Многовыходное логическое устройство | 1979 |

|

SU834919A1 |

Изобретение относится к импульсной технике и может использоваться в цифровых микроэлектронных устроит ствах. Цель изобретения - уменьшение потребляемой мощности. Поставленная цель достигается отключением тока питания инжектирующих транзисторов в режиме записи или режиме хранения. D-триггер содержит пять транзисторов 1,2, 5, 6, 8 и 10, шины 3 и 13, входные и выходные клеммы 4, 7„ 9, 14 и 15. В описании изобретения приводятся два варианта схемной реа- лизац;т D-триггера по пп. 3 и 4 формулы изобретения. 3 з.п. ф-лы, 3 ил. (Л ю sj о 7

| Аваев Н.А | |||

| и др | |||

| Большие интегральные схемы с инжекционным пита- | |||

| нием | |||

| М.: Советское радио, 1977, - с | |||

| Кулисный парораспределительный механизм | 1920 |

|

SU177A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Шагурин И.И | |||

| Особенности проектирования цифровых устройств на схемах интегральной инжекционной логики | |||

| Микроэлектроника, т | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Деревянная повозка с кузовом, устанавливаемым на упругих дрожинах | 1920 |

|

SU248A1 |

Авторы

Даты

1986-03-30—Публикация

1984-09-20—Подача