со

00

со

ел

113

Изобретение относится к автоматике и вычислительной технике.

Целью изобретения является повышение точности и быстродействия,

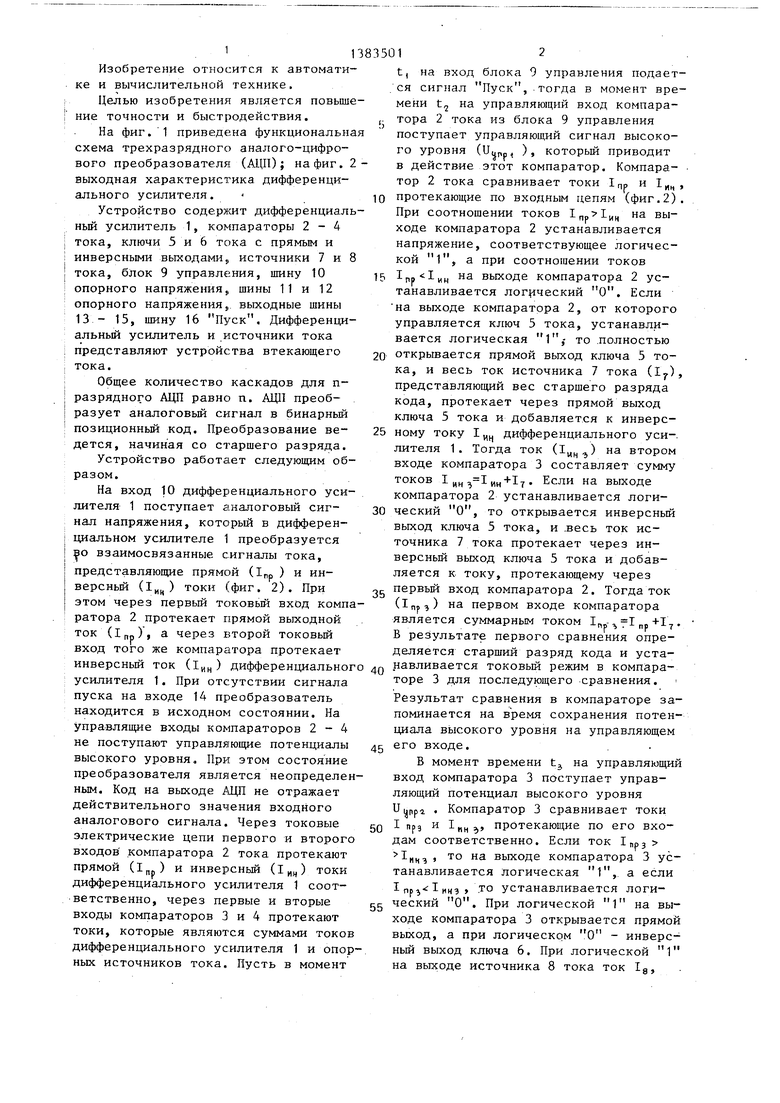

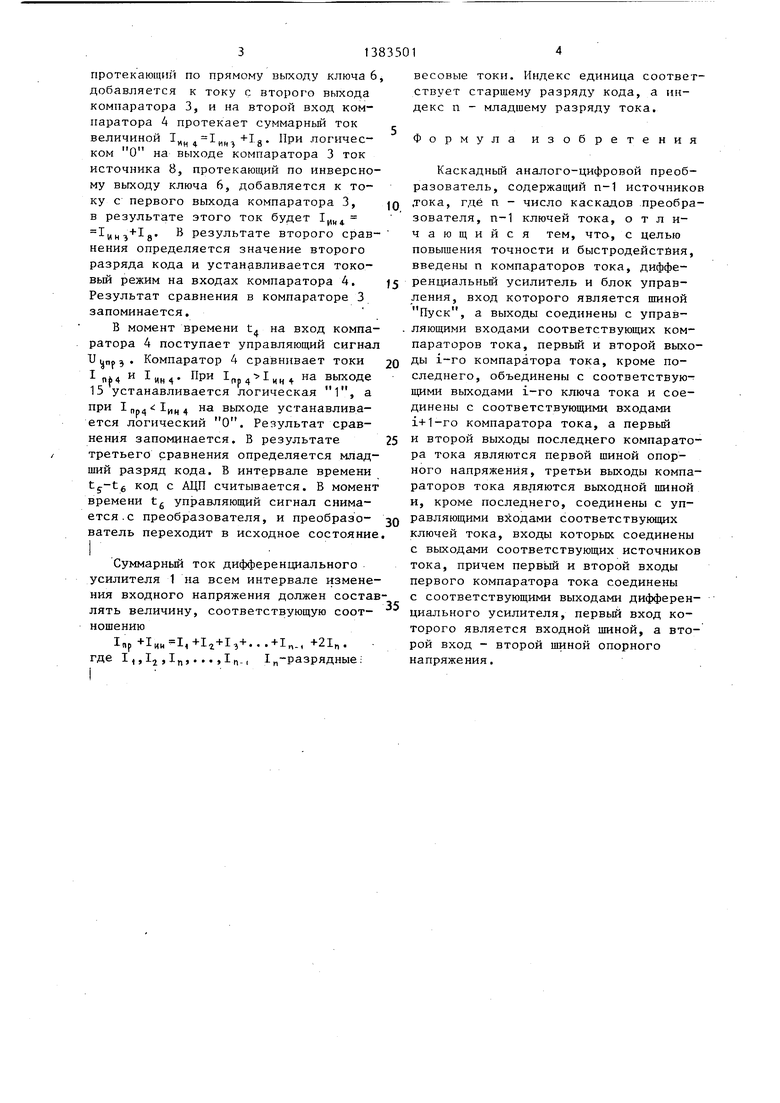

На фиг. 1 приведена функциональная схема трехразрядного аналого-цифрового преобразователя (АЦП); на фиг. 2- выходная характеристика дифференциального усилителя.

Устройство содержлт дифференциаль- ньй усилитель 1, компараторы 2-4 тока, ключи 5 и 6 тока с прямым и инверсными выходами,, источники 7 и 8

тока, блок 9 управления, шину 10 опорного напряжения,, шины 11 и 12 опорного напряжения,, выходные шины 13 - 15, шину 16 Пуск. Дифференциальный усилитель и источники тока представляют устройства втекающего тока.

Общее количество каскадов для п- разрядного АЦП равно п. АЦП преобразует аналоговьй сигнал в бинарньш позиционньй код. Преобразование ведется, начиная со старшего разря,п,а.

Устройство работает следующим образом.

На вход 10 дифференциального усилителя 1 поступает аналоговый сигнал напряжения, который в дифференциальном усилителе 1 преобразуется о взаимосвязанные сигналы тока, представляющие прямой (Inp ) и ин- версньш (IMK) токи (фиг. 2). При этом через первьш токовьй вход компратора 2 протекает прямой выходной ток („), а через второй токовый вход того же компаратора протекает инверсньш ток (1ин) дифференциально усилителя 1. При отсутствии сигнала пуска на входе 14 преобразователь находится в исходном состоянии. На Управлящие входы компараторов 2-4 не поступают управляющие потенциалы высокого уровня. При этом состояние преобразователя является неопределеным. Код на выходе АЦП не отражает действительного значения входного аналогового сигнала. Через токовые электрические цепи первого и второг входов компаратора 2 тока протекают прямой dnp) и инверсный (l) токи дифференциального усилителя 1 соот- ветственно, через первые и вторые входы компараторов 3 и 4 протекают токи, которые являются суммами токо дифференциального усилителя 1 и опоных источников тока. Пусть в момент

.

0

&

12

t, на вход блока 9 управления подается сигнал Пуск,тогда в момент времени на управляющий вход компаратора 2 тока из блока 9 управления поступает управляющий сигнал высокого уровня (UUP-, ), которьш приводит в действие этот компаратор. Компара- тор 2 тока сравнивает токи Iqp и протекающие по входным цепям (фиг.2). При соотношении токов на выходе компаратора 2 устанавливается напряжение, соответствующее логической 1, а при соотношении токов , на выходе компаратора 2 устанавливается логический О. Если на выходе компаратора 2, от которого управляется ключ 5 тока, устанавливается логическая

то .полностью

открывается прямой выход ключа 5 тока, и весь ток источника 7 тока (1у), представляющий вес старшего разряда кода, протекает через прямой выход ключа 5 тока и добавляется к инверсному току I j, дифференциального уси-. лителя 1. Тогда ток (1) на втором входе компаратора 3 составляет сумму токов I ни з -ин - T Если на выходе компаратора 2 устанавливается логический О, то открывается инверсньй выход ключа 5 тока, и .весь ток источника 7 тока протекает через инверсньш выход ключа 5 тока и добавляется к току, протекающему через первьй вход компаратора 2. Тогда ток dnp,) на первом входе компаратора является суммарным током „-,, f I „„+1.. Б результате первого сравнения определяется старший разряд кода и устанавливается токовьш режим в компараторе 3 для последующего сравнения.

Результат сравнения в компараторе запоминается на время сохранения потенциала высокого уровня на управляющем его входе.

В момент времени tj на управляющий вход компаратора 3 поступает управляющий потенциал высокого уровня

и

упр

. Компаратор 3 сравнивает токи

I прз и протекающие по его входам соответственно. Если ток 1прз I.j , то на выходе компаратора 3 устанавливается логическая Г, а если I прэ I имэ .то устанавливается логический О. При логической 1 на выходе компаратора 3 открывается прямой выход, а при логическом О - инверсный выход ключа 6. При логической 1 на выходе источника 8 тока ток Ig,

протекающий по прямому выходу ключа 6 добавляется к току с второго выхода компаратора 3, и на второй вход компаратора 4 протекает суммарный ток величиной . При логическом О на выходе компаратора 3 ток источника 8, протекающий по инверсному выходу ключа 6, добавляется к току с первого выхода компаратора 3, в результате этого ток будет I,+Ig. В результате второго срав- нения определяется значение второго разряда кода и устанавливается токовый режим на входах компаратора 4, Результат сравнения в компараторе 3 запоминается.

В момент времени t на вход компаратора 4 поступает управляющий сигнал иипр3 Компаратор 4 сравнивает токи

I п(,4 и 1инч- Р 1пр4 1ии+ выходе 15 устанавливается логическая 1, а при , на выходе устанавливается логический О. Результат сравнения запоминается, В результате третьего сравнения определяется младший разряд кода. Б интервале времени tj-tg код с АЦП считывается. В момент времени tg управляющий сигнал снимается, с преобразователя, и преобразо- ватель переходит в исходное состояние

1

Суммарный ток дифференциального

усилителя 1 на всем интервале изменения входного напряжения должен состалять величину, соответствующую соотношению

Lnp

+ 1,,+1г + 1,+ ...+1„., +21п.

где I,, ,„,... , I„-разрядные.

весовые токи. Индекс единица соответствует старшему разряду кода, а индекс п - младшему разряду тока.

Формула изобретения

Каскадный аналого-цифровой преобразователь, содержащий п-1 источников .тока, где п - число каскадов преобразователя, п-1 ключей тока, отличающийся тем, что, с целью повышения точности и быстродействия, введены п компараторов тока, дифференциальный усилитель и блок управления, вход которого является шиной Пуск, а выходы соединены с управляющими входами соответствующих компараторов тока, первый и второй выходы i-ro компаратора тока, кроме последнего, объединены с соответствующими выходами i-ro ключа тока и соединены с соответствующими входами i+1-го компаратора тока, а первый и второй выходы последнего компаратора тока являются первой шиной опорного напряжения, третьи выходы компараторов тока ЯВ.ЛЯЮТСЯ выходной шиной и, кроме последнего, соединены с управляющими входами соответствующих ключей тока, входы которых соединены с выходами соответствующих источников тока, причем первьш и второй входы первого компаратора тока соединены с соответствующими выходами дифференциального усилителя, первый вход которого является входной шиной, а второй вход - второй шиной опорного напряжения.

Ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный аналого-цифровой преобразователь | 1989 |

|

SU1762409A2 |

| Аналого-цифровой преобразователь | 1980 |

|

SU1117835A1 |

| Аналого-цифровой преобразователь последовательного приближения | 1981 |

|

SU1018228A1 |

| СИСТЕМА ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА С ВНЕШНЕЙ ДВУНАПРАВЛЕННОЙ ФОРСИРОВКОЙ | 2019 |

|

RU2725137C1 |

| Параллельный аналого-цифровой преобразователь | 1987 |

|

SU1481883A1 |

| СИСТЕМА РЕГУЛИРОВАНИЯ ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА С ВНЕШНЕЙ ФОРСИРОВКОЙ | 2019 |

|

RU2723989C1 |

| СИСТЕМА ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА | 2024 |

|

RU2822126C1 |

| СИСТЕМА ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА С УПРАВЛЯЕМОЙ ДВУНАПРАВЛЕННОЙ ВНЕШНЕЙ ФОРСИРОВКОЙ | 2021 |

|

RU2781107C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ | 2003 |

|

RU2245000C2 |

| Регулируемая реактивная нагрузка | 1989 |

|

SU1682983A1 |

Изобретение относится к автоматике и вычислительной технике и позволяет повысить точностные характеристики и быстродействие. Для этого из устройства, содержащего дифферен- циальньй усилитель, компараторы тока, ключи тока с прямым и инверсным выходами, источники тока, блок управления, исключены такие элементы, вносящие дополнительные погрешности, как вычитатели напряжения и источники опорных напряжений, Кроме того, сравнение в предлагаемом устройстве осуществляется в низкоомных цепях, а для трансформации высокоомной входной цепи в низкоомную использован дифференциальный усилитель. 2 ил.

Фиг.1

8

| Бахтиаров Г.Д | |||

| и др | |||

| цифровые преобразователи | |||

| Аналого- - М.: Советское радио, 1980, с.179-185, рис | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Там же, с | |||

| Вагонетка для движения по одной колее в обоих направлениях | 1920 |

|

SU179A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1988-03-23—Публикация

1985-12-02—Подача