1

Изобретение относится к аналого- дискретным устройствам и может быть использовано в системах обработки и передачи информации и в системах управления.

Цель изобретения - повышение точности и упрощение преобразователя.

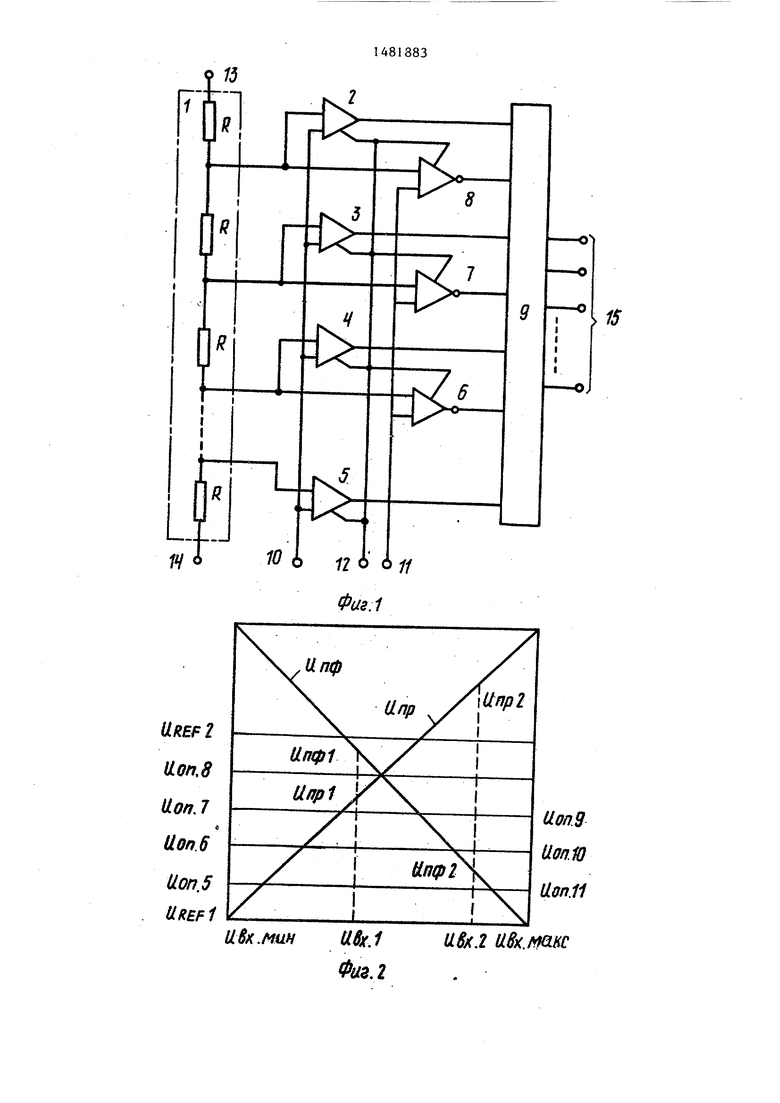

На фиг. 1 приведена блок-схема параллельного аналого-цифрового преобразователя (АЦП)j на фиг. 2 - диаграммы входных и опорных напряжений (по оси абсцисс отложено входное переменное, а по оси ординат - опорные напряжения, прямые линии представляют прямое U и противофазное U „ , напряжения, уровни опорных напряже- ний обозначены горизонтальными линиями, опорные напряжения компараторов обозначены U 005, ..., U вг, „ соответственно, шины опорных напряжений U REF,H U REFa соответственно) .

Аналого-цифровой преобразователь состоит из резистивного делителя I напряжения, группы компараторов 2-8 напряжения младших и старших разрядов унитарного кода, кодирующего логического устройства 9, преобразующего унитарный код в двоичный выходной код, шины 10 прямого входного сигнала, шины 11 противофазного входного сигнала, шины 12 управления (тактирования), первой 13, второй 14 шин опорных напряжений U цЕР1 и U REC соответственно и выходной шины 1 5.

Јь

00

00 00 Ctf

Преобразователь работает следующим образом.

Если прямой входной сигнал или противофазный сигнал на входе преобразователя превышает опорное напряжение, то на иыхопе этогодомпаратора напряжение соответствует Лог. 1 (фиг. 1). При этом компараторы 6-8 группы старших разрядов унитарного кода на своих прямых выходах представляют информацию в обратном коде. Для получения кода старших разрядов в прямом коде необходим информацию с компараторов 6-8 снимать с инверсного выхода, тогда результат сравнения будет представлен в прямом коде. Например, если входное переменное напряжение (фиг. 2) будет U8x1J то прямой сигнал на входной шине I О преобразователя соответствует Unp1 , а напряжение на шине Il противофазного сигнала соответствует Un$i, при этом на выходе компараторов 2-4 напряжение будет соответствовать Лог.1, компаратора 5 - Лог,0 выходные состояния компараторов 6-8 - Лог.О на инверсных выходах.

Если входное переменное напряжение будет Uex,j, то прямой сигнал на шине 10 будет соответствовать U а сигнал на шине 1 1 пр отивофазного сигнала - U, при этом компараторы 2-7 на выходе будут иметь Лог.1, а компаратор 8 - Лог.О. При снятии информации с компараторов групп в прямом коде кодовый кортеж для первого U варианта будет представляться 111011 1 , а для второго варианта U8XU 1001111. Кодовый кортеж в унитарном коде на прямых выходах младшей группы и инверсных выходах старшей группы компараторов будет иметь вид для первого варианта 0000111, а для второго варианта 0111 И 11 .

В предлагаемом преобразователе уменьшено количество резисторов в два раза, в результате чего уменьшается площадь кристалла для монолитного АЦП или уменьшается объем и вес АЦП для дискретного исполнения. С уменьшением площади кристалла и

количества компонентов на кристалле увеличивается процент выхода годных изделий, так как процент выхода годных кристаллов на пластине пропорционален площади кристалла и количеству компонентов. При монолитном изготовлении преобразователя с уменьшением количества резисторов в делителе на0 пряжения увеличивается его линейность, а в результате этого увеличивается процент выхода годных преобразователей как следствие уменьшения брака по дифференциальной и интегральной

5 нелинейностям.

Формула изобретения

Параллельный аналого-цифровой преобразователь, содержащий две группы

0 компараторов, общее число которых 2 М , где п- число разрядов преобразователя, делитель напряжения, первый вход которого соединен с первой шиной опорного напряжения, кодирую5 щее логическое устройство, входы которого соединены с выходами соответствующих компараторов первой и второй групп, входы стробирования которых подключены к управляющей шине, а

0 выходы кодирующего логического устройства являются выходной шиной, первые входы компараторов«первой группы объединены и являются шиной прямого входного сигнала, а вторые входы со5 единены с соответствующими выходами резистивного делителя напряжения отличающийся тем,что, с целью повышения точности и упрощения преобразователя, в него введена шина

0 противофазного входного сигнала, а делитель напряжения выполнен на последовательно соединенных резисторах, причем второй вывод первого резистора является первым входом дели5 теля напряжения, а второй вывод последнего резистора подключен к второй шине опорного напряжения, при этом первые входы компараторов второй группы объединены с вторыми вхо0 дами соответствующих компараторов

первой группы, а вторые входы объединены и подключены к шине противофазного входного сигнала.

Фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный аналого-цифровой преобразователь | 1989 |

|

SU1762409A2 |

| Параллельный аналого-цифровой преобразователь | 1986 |

|

SU1332533A1 |

| Двухтактный аналого-цифровой преобразователь | 1985 |

|

SU1336236A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Последовательно-параллельный аналого-цифровой преобразователь | 1989 |

|

SU1676100A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1464289A1 |

| ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ДИНАМИЧЕСКОГО ТИПА (ВАРИАНТЫ) | 2008 |

|

RU2389133C1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1339890A1 |

| Быстродействующий аналого-цифровой преобразователь | 1985 |

|

SU1254584A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

Изобретение относится к аналого-дискретным устройствам и может быть использовано в системах обработки и передачи информации и в системах управления. Цель изобретения - повышение точности и упрощение устройства. Применено два входных аналоговых сигнала, сдвинутых один относительно другого на 180°. Преобразователь состоит из матрицы резистивного делителя напряжения, групп компараторов напряжения младших и старших разрядов унитарного кода, кодирующего устройства, преобразующего унитарный код в двоичный выходной код, шины прямого входного сигнала, шины противофазного входного сигнала управляющей шины, шин опорных напряжений и выходной шины. Достижение цели обуславливается тем, что количество резисторов делителя напряжения равно половине разрядов унитарного кода, а к входу преобразователя подключены прямой и противофазный входные сигналы. 2 ил.

tt пф

илф1

Unp1

/.

Л

&пфг

i

USx./чин U8x.1 Фаг.1

Unp2

&пфг

Uon.9 UM.10 llon.11

Ufal ивх.мькс

| Гнатек Ю.Р | |||

| Справочник по цифро- аналоговьм и аналого-цифровьм преобразователям | |||

| -М: Радио и связь, 1982, с.327-328 | |||

| Бахтиаров Г.Д | |||

| и др | |||

| Аналого- цифровые преобразователи.- М.: Советское радио, 1980, с | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

Авторы

Даты

1989-05-23—Публикация

1987-10-09—Подача