со 00 со

ел

о сх

Ьледовлтельного кода в параллельный, ЬодепжашиГ группу триггероп 28, распределитель импульсов 5, элемент НЕ 6, ЦoпoлнитeJтьнo введены элементы И.ПИ 9-11, схема поразрядного сравнения.

формирователр импульгл п 8, ( хема поразрядного сравнения 7 содержит группы элементов И 29, 30, группы элементов ИЛИ 31, 32 и элемент ШШ-НК 2, 1 з.п. ф-лы, 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пересчетное устройство | 1980 |

|

SU921093A1 |

| Устройство для контроля резервированного генератора | 1980 |

|

SU907887A1 |

| Устройство для формирования серий импульсов | 1983 |

|

SU1103352A1 |

| Устройство для индикации | 1978 |

|

SU734755A1 |

| Устройство для контроля цифровых объектов | 1982 |

|

SU1072048A1 |

| Устройство для программного управления | 1984 |

|

SU1255993A1 |

| Преобразователь кода грея в параллельный двоичный код | 1978 |

|

SU788104A1 |

| Устройство для измерения периода | 1977 |

|

SU690435A1 |

| Устройство для управления ленточным перфоратором | 1985 |

|

SU1310860A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1343551A1 |

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано в узлах сопряжения цифровых устройств. Целью изобретения является расширение функциональньпс возможностей за счет обеспечения контроля работы преобразователя, В преобразователь по

Изобретение относится к автоматике и вычислительной технике и может быть использовано в узлах согласования и связи устройств вычислительной и измерительной техники.

Целью изобретения является расширение функциональных возможностей за счет обеспечения контроля работы преобразователя.

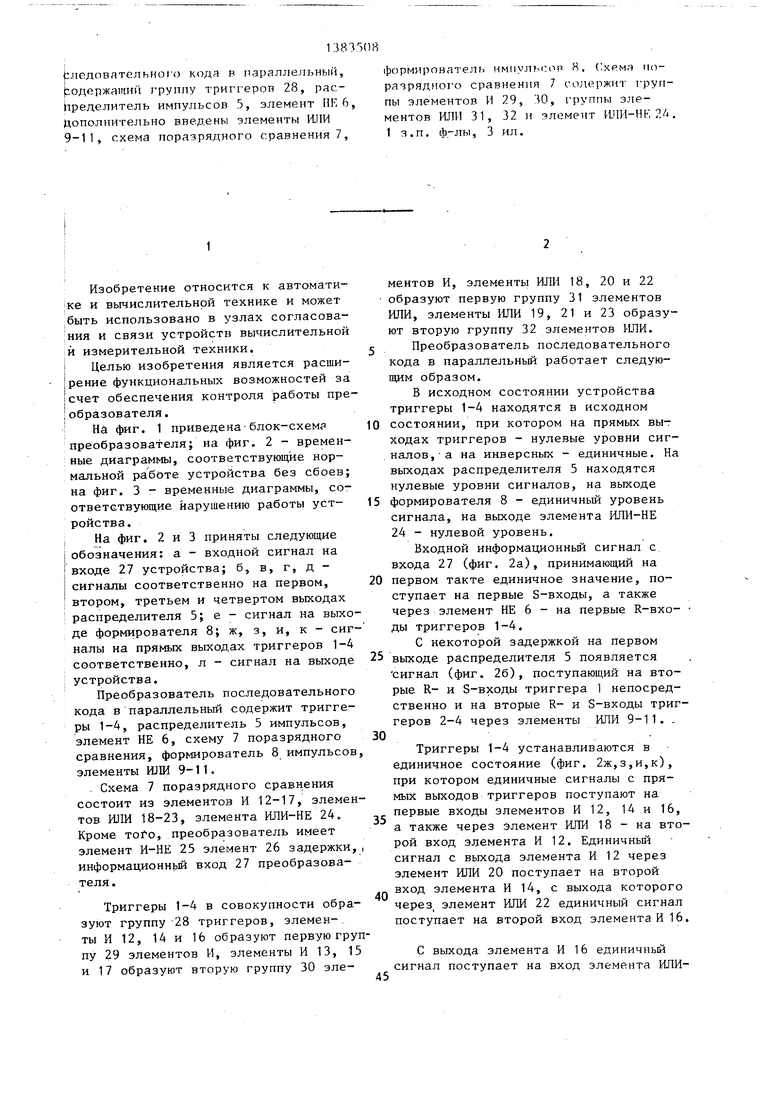

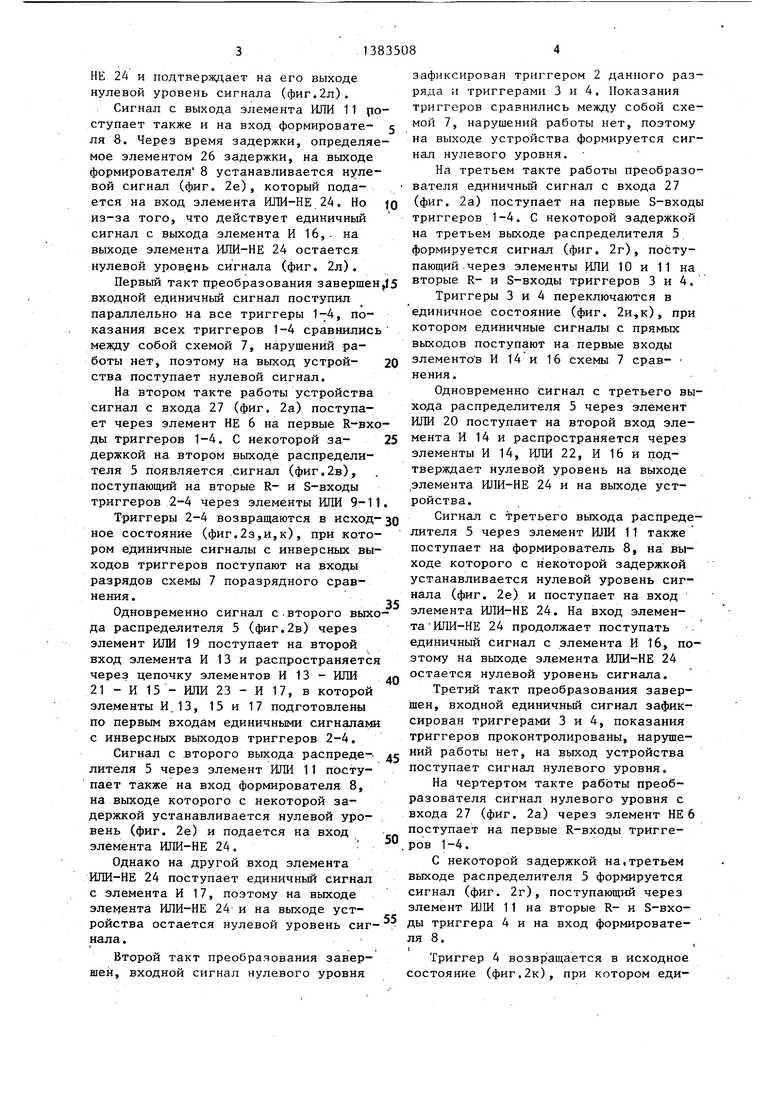

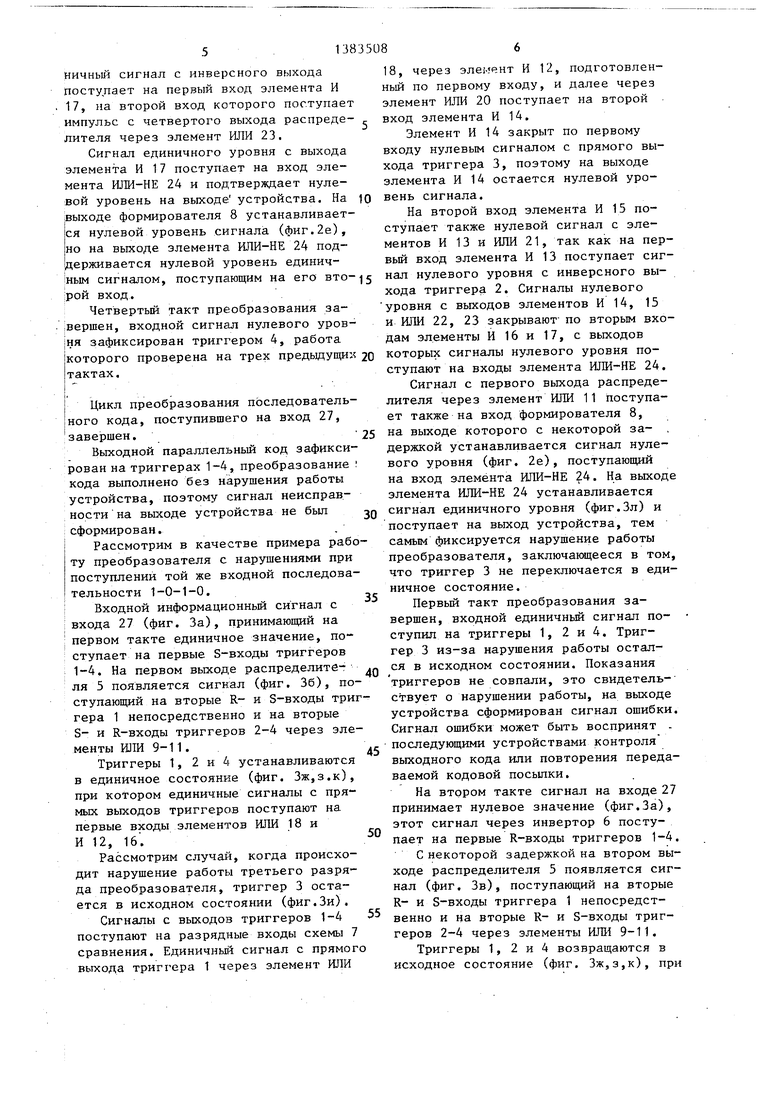

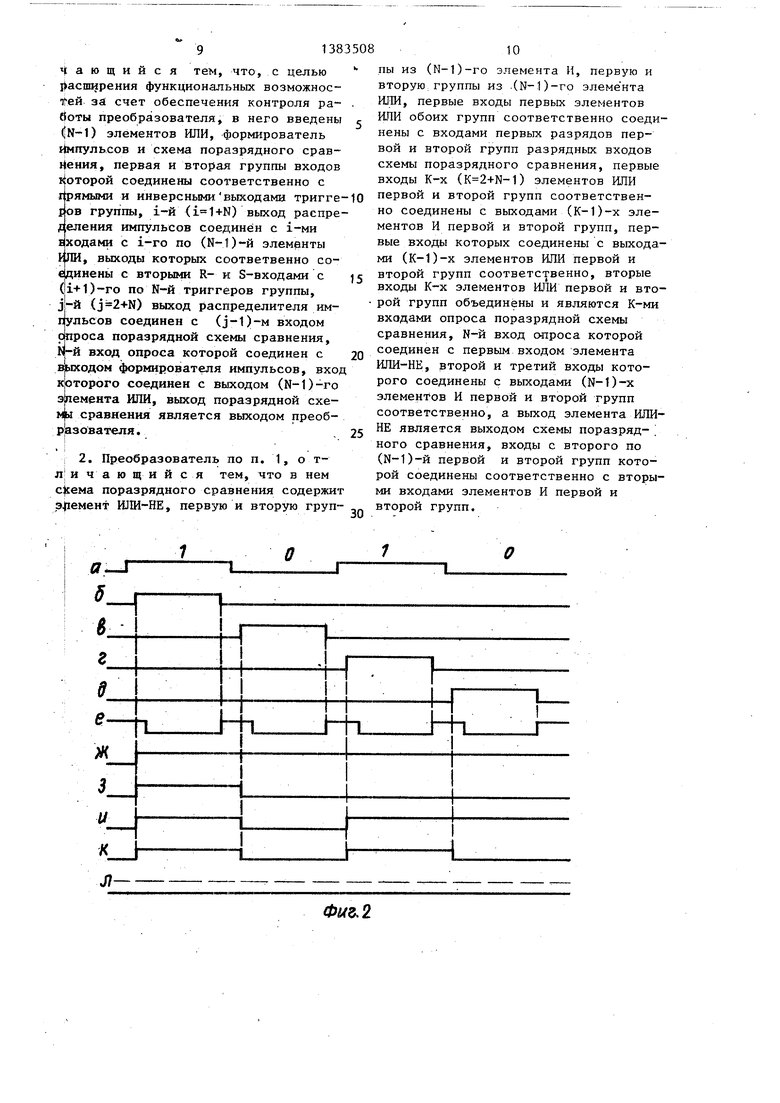

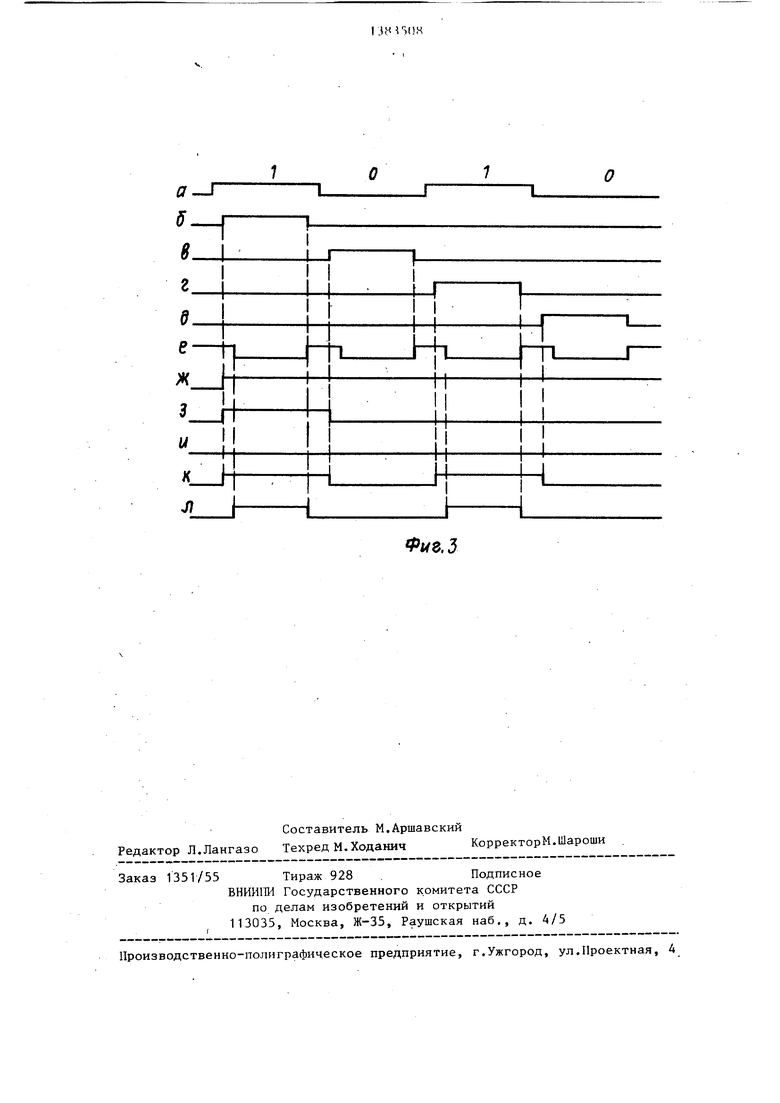

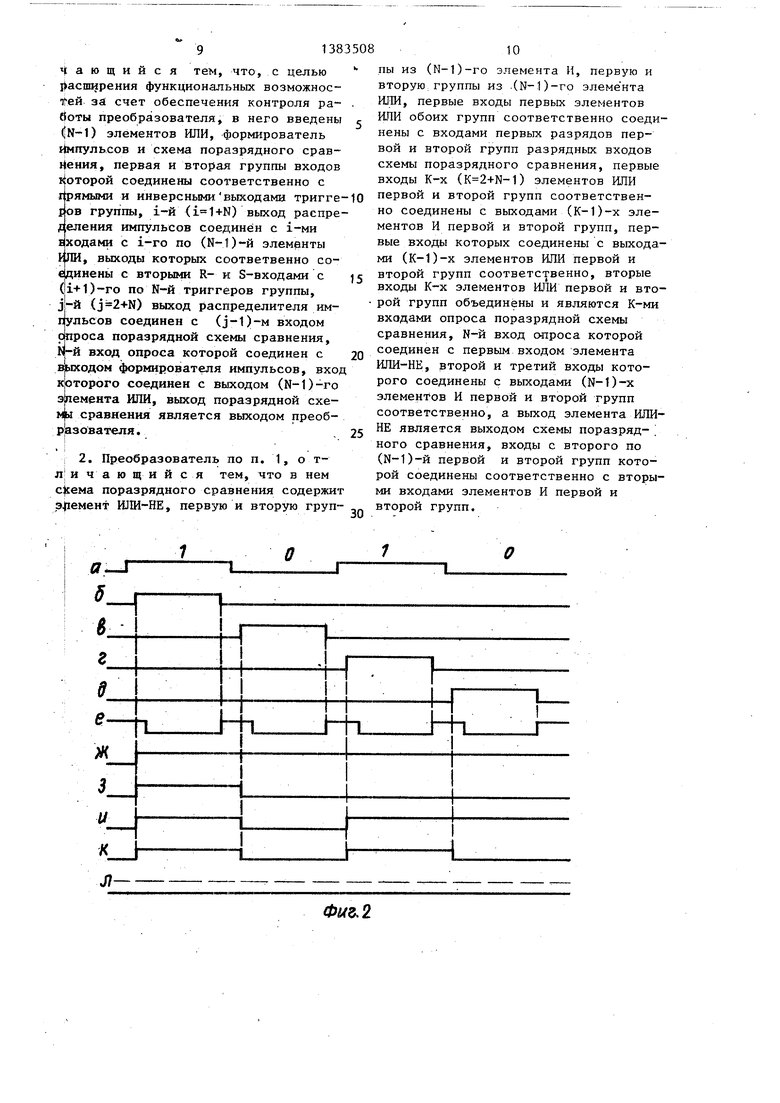

Ни фиг. 1 приведена-блок-схема преобразователя; на фиг. 2 - временные диаграммы, соответствующие нормальной работе устройства без сбоев; на фиг. 3 - временные диаграммы, соответствующие нарушению работы устройства.

На фиг. 2 и 3 приняты следующие обозначения: а - входной сигнал на входе 27 устройства; б, в, г, д - сигналы соответственно на первом, втором, третьем и четвертом выходах распределителя 5; е - сигнал на выходе формирователя 8; ж, з, и, к - сигналы на прямых выходах триггеров 1-4 соответственно, л - сигнал на выходе устройства.

Преобразователь последовательного кода в параллельный содержит триггеры 1-4, распределитель 5 импульсов, элемент НЕ 6, схему 7 поразрядного сравнения, формирователь 8 импульсов элементы ИЛИ 9-11.

. Схема 7 поразрядного сравнения состоит из элементов И 12-17, элементов ИЛИ 18-23, элемента ИЛИ-НЕ 24. Кроме Toto, преобразователь имеет элемент И-НЕ 25 элемент 26 задержки, информационньй вход 27 преобразователя.

Триггеры 1-4 в совокупности образуют группу 28 триггеров, элементы И 12, 14 и 16 образуют первую группу 29 элементов И, элементы И 13, 15 и 17 образуют вторую группу 30 элементов И, элементы ИЛИ 18, 20 и 22 образуют первую группу 31 элементов ИЛИ, элементы ИЛИ 19, 21 и 23 образуют вторую группу 32 элементов ИЛИ.

Преобразователь последовательного кода в параллельньй работает следующим образом.

В исходном состоянии устройства триггеры 1-4 находятся в исходном

состоянии, при котором на прямых вы-г ходах триггеров - нулевые уровни сит- налов,-а на инверсных - единичные. На вьпсодах распределителя 5 находятся нулевые уровни сигналов, на выходе

формирователя 8 - единичный уровень сигнала, на выходе элемента ИЛИ-НЕ 24 - нулевой уровень.

Входной информационньй сигнал с входа 27 (фиг, 2а), принимающий на

первом такте единичное значение, поступает на первые S-входы, а также через элемент НЕ 6 - на первые R-BXO- ды триггеров 1-4.

С некоторой задержкой на первом

выходе распределителя 5 появляется сигнал (фиг. 2б), поступающий на вторые R- и S-входы триггера 1 непосредственно и на вторые R- и S-входы триггеров 2-4 через элементы ИЛИ 9-11. .

30

35

40

45

Триггеры 1-4 устанавливаются в единичное состояние (фиг. 2ж,з,и,к), при котором единичные сигналы с прямых выходов триггеров поступают на первые входы элементов И 12, 14 и 16, а также через элемент ИЛИ 18 - на второй вход элемента И 12, Единичный сигнал с выхода элемента И 12 через элемент ИЛИ 20 поступает на второй вход элемента И 14, с выхода которого через элемент ИЛИ 22 единичный сигнал поступает на второй вход элемента И 16.

С выхода элемента И 16 единичный сигнал поступает на вход элемента ИЛИНЕ 24 и подтверлу1,ает на его выходе нулевой уровень сигнала (фиг.2л). : Сигнал с выхода элемента ИЛИ 11 ро ступает также и на вход формировате- ля 8. Через время задержки, определяемое элементом 26 задержки, на выходе формирователя 8 устанавливается нулевой сигнал (фиг. 2е), который подается на вход элемента ИЛИ-НЕ 24. Но из-за того, что действует единичный сигнал с выхода элемента И 16,- на выходе элемента ИЛИ-НЕ 24 остается нулевой уровень сигнала (фиг. 2л).

Первьш такт преобразования завершен входной единичньш сигнал поступил параллельно на все триггеры 1-4, показания всех триггеров 1-4 сравнились между собой схемой 7, нарушений работы нет, поэтому на выход устрой- ства поступает нулевой сигнал.

На втором такте работы устройства сигнал с входа 27 (фиг. 2а) поступает через элемент НЕ 6 на первые R-BXO ды триггеров 1-4. С некоторой за- держкой на втором выходе распределителя 5 появляется .сигнал (фиг.2в), поступающий на вторые R- и S-входы триггеров 2-4 через элементы ИЛИ 9-11

Триггеры 2-4 возвращаются в исход- ное состояние (фиг.2з,и,к), при котором единичные сигналы с инверсных выходов триггеров поступают на входы разрядов схемы 7 поразрядного сравнения.Одновременно сигнал с второго выхода распределителя 5 (фиг.2в) через элемент ИЛИ 19 поступает на второй вход элемента И 13 и распространяется через цепочку элементов И 13 - ИЛИ 21 - И 15 - ИЛИ 23 - И 17, в которой элементы И.13, 15 и 17 подготовлены по первым входам единичными сигналами с инверсных выходов триггеров 2-4,

Сигнал с второго выхода распреде-- лителя 5 через элемент ИЛИ 11 поступает также на вход формирователя В, на выходе которого с некоторой задержкой устанавливается нулевой уровень (фиг. 2е) и подается на вход элемента ИЛИ-НЕ 24.

Однако на другой вход элемента ИЛИ-НЕ 24 поступает единичный сигнал с элемента И 17, поэтому на выходе элемента ИЛИ-НЕ 24 и на выходе устройства остается нулевой уровень сигнала.

Второй такт преобразования завершен, входной сигнал нулевого уровня

5 g

5 0

5

о

дд

0

5

зафиксирован триггером 2 данного разряда и триггерами 3 и 4. Показания триггеров сравнились между собой схемой 7, нарушений работы нет, поэтому на выходе устройства формируется сигнал нулевого уровня.

На третьем такте работы преобразователя единичный сигнал с входа 27 (фиг. 2а) поступает на первые S-входы триггеров 1-4. С некоторой задержкой на третьем выходе распределителя 5 формируется сигнал (фиг. 2г), поступающий, через элементы ИЛИ 10 и 11 на вторые R- и S-входы триггеров 3 и 4.

Триггеры 3 и 4 переключаются в единичное состояние (фиг. 2и,к), при котором единичные сигналы с прямых выходов поступают на первые входы элементо в И 14 и 16 схемы 7 срав- нения.

Одновременно сигнал с третьего выхода распределителя 5 через элемент ИЛИ 20 поступает на второй вход элемента И 14 и распространяется через элементы И 14, ИЛИ 22, И 16 и подтверждает нулевой уровень на выходе элемента ШШ-НЕ 24 и на выходе устройства.

Сигнал с третьего выхода распределителя 5 через элемент ИЛИ 11 также поступает на формирователь 8, на выходе которого с некоторой задержкой устанавливается нулевой уровень сигнала (фиг. 2е) и поступает на вход элемента ИЛИ-НЕ 24. На вход элемента ШШ-НЕ 24 продолжает поступать единичный сигнал с элемента И 16, поэтому на выходе элемента ИЛИ-НЕ 24 остается нулевой уровень сигнала.

Третий такт преобразования завершен, входной единичный сигнал зафиксирован триггерами 3 и 4, показания триггеров проконтролированы, нарушений работы нет, на выход устройства поступает сигнал нулевого уровня.

На чертертом такте работы преобразователя сигнал нулевого уровня с входа 27 (фиг. 2а) через элемент НЕ 6 поступает на первые R-входы тригге- .ров 1-4.

С некоторой задержкой на,третьем выходе распределителя 5 формируется сигнал (фиг. 2г), поступающий через элемент 11 на вторые R- и S-входы триггера 4 и на вход формирователя 8.

Триггер 4 возвращается в исходное состояние (фиг,2к), при котором единичньй сигнал с инверсного выхода поступает на первый вход элемента И 17, на второй вход которого поступает импульс с четвертого выхода распреде- лителя через элемент ИЛИ 23.

Сигнал единичного уровня с выхода элемента И 17 поступает на вход элемента ШШ-НЕ 24 и подтверждает нулевой уровень на выходе устройства. На :выходе формирователя 8 устанавливает- |ся нулевой уровень сигнала (фиг.2е), |но на вьпсоде элемента ИЛИ-НЕ 24 поддерживается нулевой уровень единичным сигналом, поступающим на его вто|рой вход.

Четвертьй такт преобразования за- |вершен, входной сигнал нулевого уров- |ня зафиксирован триггером 4, работа. JKOTOporo проверена на трех предьщущи: тактах.

j Цикл преобразования последователь- JHoro кода, поступившб;го на вход 27, завершен,

Выходной параллельный код зафиксирован на триггерах 1-4, преобразование кода выполнено без нарушения работы устройства, поэтому сигнал неисправности на выходе устройства не был ;сформирован.

Рассмотрим в качестве примера работу преобразователя с нарушениями при поступлений той же входной последовательности 1-0-1-0.

Входной информационньм сигнал с Входа 27 (фиг. За), принимающий на : первом такте единичное значение, поступает на первые S-входы триггеров 1-4. На первом выходе распределите- ля 5 появляется сигнал (фиг. 36), поступающий на вторые R- и S-входы триггера 1 непосредственно и на вторые S- и R-входы триггеров 2-4 через элементы ИШ 9-11.

Триггеры 1, 2 и 4 устанавливаются в единичное состояние (фиг. Зж,з.к), при котором единичные сигналы с прямых выходов триггеров поступают на. первые входы элементов ИЛИ 18 и И 12, 1б .

Рассмотрим случав, когда происходит нарушение работы третьего разряда преобразователя, триггер 3 OCTSI- ется в исходном состоянии (фиг.Зи).

Сигналы с выходов триггеров 1-4 поступают на разрядные входы схемы 7 сравнения. Единичньв сигнал с прямого выхода триггера 1 через элемент Ш1И

5

0

5

о

д

5

5

5

0

18, через элемент И 12, подготовленный по первому входу, и далее через элемент ИЛИ 20 поступает на второй вход элемента И 14.

Элемент И 14 закрыт по первому входу нулевым сигналом с прямого выхода триггера 3, поэтому на выходе элемента И 14 остается нулевой уровень сигнала.

На второй вход элемента И 15 поступает также нулевой сигнал с элементов И 13 и ИЛИ 21, так как на первый вход элемента И 13 поступает сигнал нулевого уровня с инверсного выхода триггера 2. Сигналы нулевого уровня с выходов элементов И 14, 15 и ИЛИ 22, 23 закрывают- по вторым входам элементы И 16 и 17, с выходов которых сигналы нулевого уровня поступают на входы элемента ИЛИ-НЕ 24.

Сигнал с первого выхода распределителя через элемент ИЛИ 11 поступает также на вход формирователя 8, на выходе которого с некоторой задержкой устанавливается сигнал нулевого уровня (фиг. 2е), поступающий на вход элемента ИЛИ-НЕ 24. На выходе элемента ИЛИ-НЕ 24 устанавливается сигнал единичного уровня (фиг.3л) и поступает на выход устройства, тем самым фиксируется нарушение работы преобразователя, заключающееся в том, что триггер 3 не переключается в единичное состояние.

Первый такт преобразования завершен, входной единичный сигнал поступил на триггеры 1, 2 и 4. Триггер 3 из-за нарушения работы остался в исходном состоянии. Показания триггеров не совпали, это свидетельствует о нарушении работы, на выходе устройства сформирован сигнал ошибки. Сигнал ошибки может быть воспринят . последующими устройствами контроля выходного кода или повторения передаваемой кодовой посылки.

На втором такте сигнал на входе 27 принимает нулевое значение (фиг.За), этот сигнал через инвертор 6 поступает на первые R-входы триггеров 1-4.

С некоторой задержкой на втором выходе распределителя 5 появляется сигнал (фиг. Зв), поступающий на вторые R- и S-входы триггера 1 непосредственно и на вторые R- и S-входы триггеров 2-4 через элементы ИШ1 9-11.

Триггеры 1, 2 и 4 возвращаются в исходное состояние (фиг. Зж,з,к), при

10

котором единичные сигналы с инверсных выходов поступают на первые входы элементов ИЛИ 19 и Н 13, 17

Сигнал единичного уровня с выхода элементов ИЛИ 19 распространяется через элементы И 13 и ИЛИ 21, далее через элемент, И 15, подготовленный по первому входу единичным сигналом с инверсного выхода триггера 3, и далее через элементы ИЛИ 23 и И 17 на второй вход элемента ИЛИ-НЕ 24, подтверждая нулевой уровень сигнала на его выходе (фиг. 3л).

Второй такт преобразования за- . с вершен, входной сигнал нулевого уровня зафиксирован триггерами 1-4, пока зания которых совпали между сббой. На выход устройства поступает сигнал нулевого уровня.

На третьем такте работы преобразователя единичный сигнал с входа 27 (фиг. За) поступает на. первые S-входы триггеров 1-4. С некоторой задержкой на третьем выходе распределителя 5 формируется сигнал (фиг. Зг), поступающий .через элементы ИЛИ 10 и 11 на вторые R- и S-входы триггеров 3 и 4.

Триггер 4 переключается в единичное состояние (фиг. Зк), а триггер 3 из-за нарушения работы остается в исходном состоянии (фиг.Зи), при котором единичный сигнал с его инверсного выхода открывает по первому входу элемент И 15. Импульс с третье20

25

30

в единичное состояние. Показания три геров 3 и 4 не совпали, на выход устройства поступил сигнал нарушения работы устройства.

Дальнейшая работа преобразователя происходит аналогично.

На каждом К-м такте входной сигнал запоминается К-м триггером информационного разряда и (N-K) триггерами последующих разрядов. Показания (N-K-t-1 триггеров сравниваются ме1жду собой, нормальной работе устройства без сбоев и без отказов соответствует совпадение показаний триггеров.

Несовпадение показаний триггеров свидетельствует о нарушении работы элементов преобразователя, о нарушении, которое выявляется оперативно в процессе основной работы, при этом ,сразу же на данном такте преобразова- :ния на выход устройства поступает сигнал неисправности, тем самым влияние нарушения работы может быть нейтрализовано сразу же на данном такте преобразования.

Преобразование первых (N-1) разрядов всегда происходит с более высокой контролирующей способностью, т.е. име ется возможность более полно выявить нарушения работы преобразователя, чем в известном устройстве. Преобразование остальных разрядов (Р+1) в предлагаемом устройстве осуществляется с контролирующей способностью не хуже,

го выхода распределителя 5 через эле-35 известном, мент ИЛИ 21, элемент И 15 и элемент g случае, если входная информация ИЛИ 23 поступает на второй вход элемента И 17, но элемент И 17 закрыт по первому входу нулевым сигналом с инверсного выхода триггера 4. Элемент И 16 также закрыт по второму входу сигналом нулевого уровня с элементов И 14, ИЛИ 22. Поэтому на входах элемента ИЛИ-НЕ 24 действуют сигналы нулевого уровня. Когда и на третьем входе элемента ИЛИ-НЕ 24 с выхода формирователя 8 устанавливается нулевой уровень сигнала (фиг. За), то на выходе элемента ИЛИ-НЕ 24 формируется единичньй сигнал (фиг. 3л), кото- 50 рый поступает на выход 28 устройства и фиксирует возникшее нарушение работы преобразователя.

представляется словами переменной длины, то при поступлении коротких слов лишние разряды преобразователя используются для дополнительного резервирования информационных разрядов и повьш1ают контролирукяцую способность устройства.

Формула изобретения

в единичное состояние. Показания триггеров 3 и 4 не совпали, на выход устройства поступил сигнал нарушения работы устройства.

Дальнейшая работа преобразователя происходит аналогично.

На каждом К-м такте входной сигнал запоминается К-м триггером информационного разряда и (N-K) триггерами последующих разрядов. Показания (N-K-t-1) триггеров сравниваются ме1жду собой, нормальной работе устройства без сбоев и без отказов соответствует совпадение показаний триггеров.

Несовпадение показаний триггеров свидетельствует о нарушении работы элементов преобразователя, о нарушении, которое выявляется оперативно в процессе основной работы, при этом ,сразу же на данном такте преобразова- :ния на выход устройства поступает сигнал неисправности, тем самым влияние нарушения работы может быть нейтрализовано сразу же на данном такте преобразования.

Преобразование первых (N-1) разрядов всегда происходит с более высокой контролирующей способностью, т.е. имеется возможность более полно выявить нарушения работы преобразователя, чем в известном устройстве. Преобразование остальных разрядов (Р+1) в предлагаемом устройстве осуществляется с контролирующей способностью не хуже,

известном, g случае, если входная информация

известном, g случае, если входная информация

представляется словами переменной длины, то при поступлении коротких слов лишние разряды преобразователя используются для дополнительного резервирования информационных разрядов и повьш1ают контролирукяцую способность устройства.

Формула изобретения

известном, g случае, если входная информация

Чающийся тем, что, с целью 1 асширения функциональных возможностей за; счет обеспечения контроля ра- Йоты преобразователя, в него введены (N-1) элементов ИЛИ, формирователь Импульсов и схема поразрядного срав- Нения, первая и вторая группы входов lioTopoA соединены соответственно с прямыми и инверсными выходами тригге ров группы, i-й () выход распре ;пеления импульсов соединён с 1-ми Еходами с i-ro по (К-1)-й элементы ИЛИ, выходы которых соответвенно соединены с вторыми R- и S-входами с (i+l)-ro по N-й триггеров группы, j-й (j 2-«-N) выход распределителя импульсов соединен с (j-l)-M входом опроса поразрядной схемы сравнения, N-й вход опроса которой соединен с кодом формирователя импульсов, вхо которого соединен с выходом (N-l)-ro эпемента ИЛИ, выход поразрядной схемы сравнения является выходом преоб- р рзователя..

: 2. Преобразователь по п. 1, о т- Л; и ч а ю щ и и с я тем, что в нем поразрядного сравнения содержит элемент ИЛИ-НЕ, первую и вторую груп- „

10

пы из (N-l)-ro элемента Н, первую и ВТОРУЮ;группы из .(N-l)-ro элемента ИЛИ, первые входы первых элементов ИЛИ обоих групп соответственно соединены с входами первых разрядов первой и второй групп разрядных входов схемы поразрядного сравнения, первые входы К-х (K 2+N-1) элементов ИЛИ первой и второй групп соответственно соединены с выходами (К-1)-х элементов И первой и второй групп, первые входы которых соединены с выходами (К-1)-х элементов ИЛИ первой и второй групп соответственно, вторые входы К-х элементов ИЛИ первой и второй групп объединены и являются К-ми входами опроса поразрядной схемы сравнения, N-й вход опроса которой соединен с первым входом элемента Ш1И-НЕ, второй и третий входы которого соединены с выходами (N-l)-x элементов И первой и второй групп соответственно, а выход элемента ИЛИ- НЕ является выходом схемы поразряд- , ного сравнения, входы с второго по (М-1)-й первой и второй групп которой соединены соответственно с вторыми входами элементов И первой и второй групп.

«Pi/aJ

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ ПОСЛЕДОВАТЕЛБНОГО | 0 |

|

SU354410A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь последовательного кода в параллельной | 1976 |

|

SU628485A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-03-23—Публикация

1986-10-27—Подача