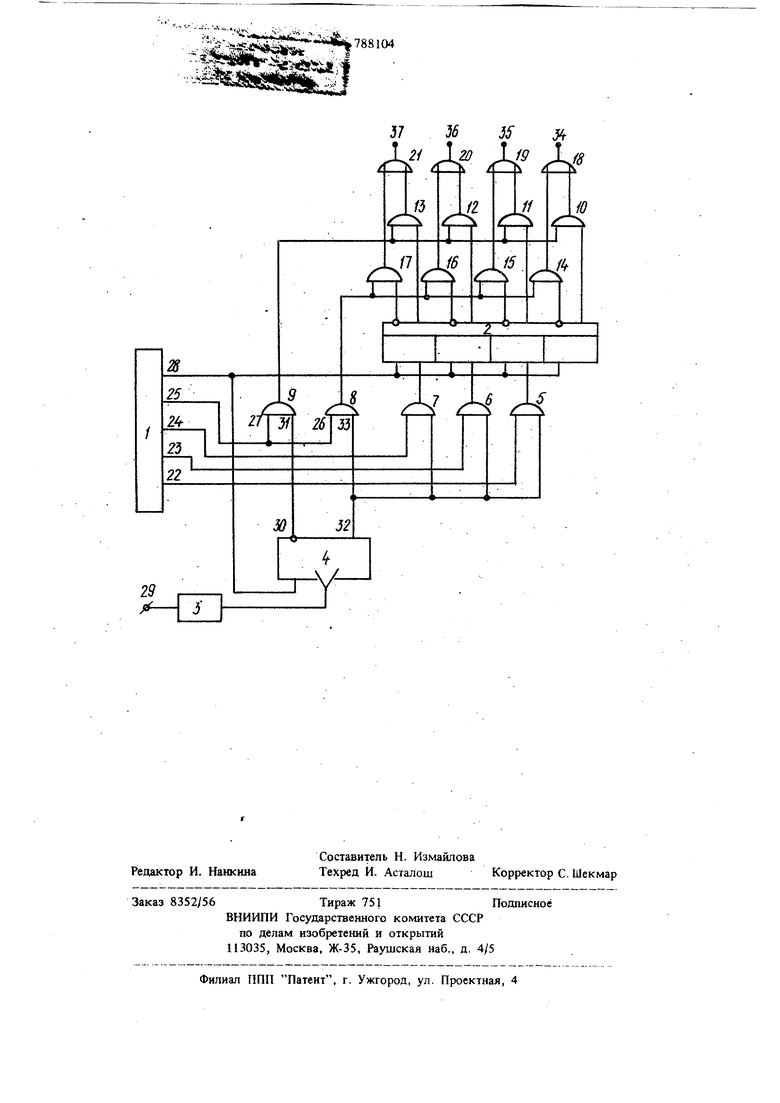

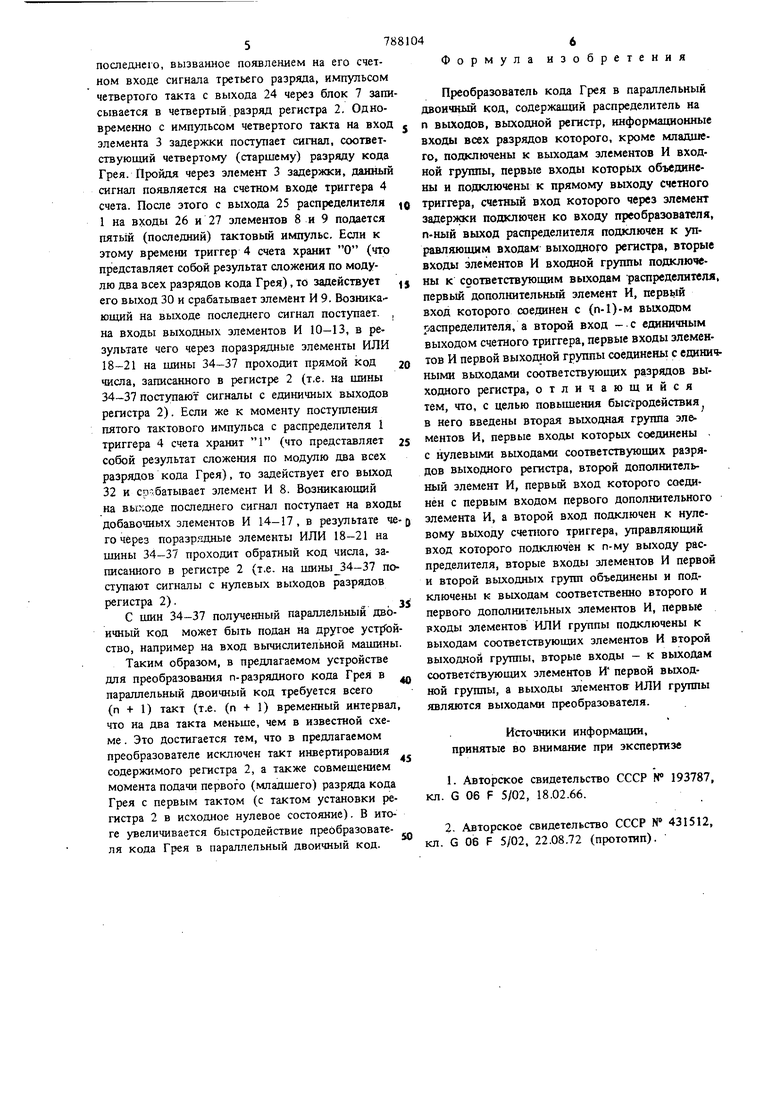

Изобретение С4лосктсл к устройствам автоматики и вычислительной техники, а более конкретно к преобразователям кодов, и может быть использовано при построении цифровых следящих систем, в цепи обратной связи которых используется преобразователь типа перемещение-код. Известен преобразователь кода Грея в двоичный код, содержащий сдвигающий регистр, триггер счета, элемент И, распределитель и ячейку запрета tl. Недостатком известного преобразователя является низкое быстродействие. Наиболее близким к предлагаемому является преобразователь кода Грея, содержащий распределитель, выходной регистр, входные поразрядные элементы И, выходы которых подключены к соответствующ- входам установки 1 выходного регистра, выходные поразрядные схемы И, входы которых соединены с еди ничными выходами соответствующих разрядов выходного регистра, дополнительный элемент И, триггер счета, элемент задержки, вход которого соединен с шиной помчи кода Грея, а выход - Со счетным входом триггера счета, причем управляющие выходы распределителя соединены со входами входных поразрядных элементов И, со входом дополнительного элемента И, со входами всех выходных поразрядных элементов И исо входами установки О всех разрядов-выходного регистра, единичный выход триггера счета соединен со входом дополнительного элемента И и со входами входных поразрядных элементов И, выход дополнительного элемента И соединен со счетными входами всех разрядов выходного регистра, а выходы выходных поразрядных элементов И подключены к соответствующим щинам вьщачи двоичного кода устройства. 2 J . Недостатком устройства является также относительно невысокое быстродействие. Цель изобретегшя - повьпиение быстродействия преобразователя. Поставленная цель достигается тем, что в преобразователь кода Грея в параллельный двоичный код, содержащий распределитель на п выходов, выходной регистр, информационные входы всех разрядов которого, кроме младшего, подключены к выходам элементов И входной группы, первые входы которых объединены и подключены к прямому выходу счетного триггера, счетный вход которого через элемент задержки подключен ко входу преобразователя, п-ный выход распределителя подключен к управляющим входам выходного регистра, вторые входы элементов И входной группы подключены к соответствующим, выходам распределителя, первый дополнительный элемент И, первый вход которого соединен с (n-l)-M выходом распределителя, а второй вход - с единичным выходом счетного триггера,первые входы элементов И первой выходной . группы соединены с единичными выходами соответствующих разрядов выходного регистра, введены вторая выходная группа элементов И, первые входы которых соединены с нулевыми выходами соответствующих разрядов выходного регистра, второй дополнительный элемент И, первый вход которого соединен с первым входом первого дополнительного элемента И, а второй вход подключен к нулевому выходу счетного триггера, управляющий вход которого подключен к п-му выходу распределит;еля, вторые входы элементов И первой и второй выход ных групп объединены и подключены к выходам соответственно второго и первого дополнительных элементов И, первые входы элементов ИЛИ группы подключены к выходам соответствующих элементов И выходной группы, вторые входы - к выходам соответствующих элементов И первой выходной группы, а выходы элементов ИЛИ группы являются выходами преобразователя. Блок-схема предлагаемого устройства приведена на чертеже. Устройство содержит распределитель 1, выходной регистр 2, элемент 3 задержки, счетный триггер 4, входные блоки элементов И старщих

разрядов 5-7 (входной элемент И младшего разряда отсутствует), первый 8 и второй 9 дополнительные элементы И, выходные 10-13 и добавочные 14-17 блоки элементов И и поразрядные элементы ИЛИ 18-21. Управляющие j выходы 22-24 распределителя 1 соединены соответственно со входами входных блоков элементов И 5-7, уцравляющий выход 25 соединен со входом 26 первого 8 и со входом 27 второго 9 дополнительных элементов И, а зшравляющий выход 28 распределителя 1 подключен ко входам установки О всех разрядов выходного регистра 2 и ко входу установки О триггера 4 счета. Вход элемента 3 задержки .соединен с шиной 29 подат кода Грея, а выход - со счетным входом счетного, триггера 4. Нулевой выход 30 счетного триггера 4 подключен ко входу 31 второго дополнительного элемента И 9 а единичный выход 32 счетного триггера 4 7

нал, соответствующий второму разряду кода Грея. Импульсом второго такта с выхода 22 через блок 5 во второй разряд регистра 2 записывается состояние триггера 4, вызванное приходом

ряда регистра 2 всегда находится в нулевом состоянии) . После этой записи на счетном входе триггера 4 появляется сигнал, соответствующий второму разряду кода Грея (уже прошедший через элемент 3 задержки). Состояние триггера 4 счета, вызванное действием этого сигнала, импульсом третьего такта с выхода 23 через блок 6 записывается в третий разряд регистра 2. Одновременно с импульсом третьего такта на вход элемента 3 задержки поступает сигнал, соответствующий третьему разряду кода Грея. Пройдя элемент 3 задержки, данный сигнал появляется на счетном входе триггера 4 счета Сисюяшие 4 ко входу 33 первого дополнительного элемента И 8 и ко входам всех входных блоков элеменч тов И 5-7. Выходы входных блоков элементов И 5-7 соединены со входами установки 1 соответствующих разрядов выходного регистра 2. Единичные выходы всех разрядов выходного регистра 2 соединены со входами соответствующих выходных элементов И 10-13, а нулевые выходы всех разрядов выходного регистра 2 - со входами соответствующих добавочных элементов И 14-17. Выход первого дополнительного элемента И 8 подключен ко входам всех добавочных элементов 1 14-17, а выход второго дополнительного элемента И 9 - ко входам всех выходных блоков элементов И 10-13. Выходы выходных блоков элементов И 10-13 и выходы добавочных элементов И 14-17 через соответствующие поразрядные элементы ИЛИ 18-21 подключены кг шинам 34-37 вьщачи двоичного кода устройства. Устройство работает следующим образом, В первом такте на выходе 28 распределителя 1 появляется импульс, устанавливающий все триггеры выходного регистра 2, а также тригrep 4 счета в исходное нулевое состояние. Одновременно с этим импульсом с шины 29 на вход элемента 3 задержки поступает сигнал, соответствующий первому (младшему) разряду кода Грея: задержка его поступления на счетный вход триггера 4 счета не превышает периода следования тактовых импульсов с распределителя 1, т.е. кодовые сигналы поступают на счетный вход триггера 4 счета в промежутках между подачей импульсов-с распределителя 1. После прохождения элемента 3 задержки сигнал, соответствующий первому разряду кода Грея, появляется на счетном входе триггера 4. Затем на вход блока 5 подается второй тактовый импульс с выхода 22 распределителя 1. Одновременно с ним на вход элемента 3 задержки приходит сигна его счетный вход сигнала первого (младшего) разряда кода Грея (триггер младшего раэпоследнего, вызванное появлением на его счетном входе сигнала третьего разряда, импульсом четвертого такта с выхода 24 через блок 7 запи сывается в четвертый.разряд регистра 2. Одновременно с импульсом четвертого такта на вход элемента 3 задержки поступает сигнал, соответствующий четвертому (старшему) разряду кода Грея. Пройдя через элемент 3 задержки, данный сигнал появляется на счетном входе триггера 4 счета. После этого с выхода 25 распределителя 1 на входы 26 и 27 элементов 8 и 9 подается пятьш (последний) тактовый импульс. Если к этому времени триггер 4 счета хранит О (что представляет собой результат сложения по модулю два всех разрядов кода Грея), то задействует его выход 30 и срабатьтает элемент И 9. Возникающий на выходе последнего сигнал поступает, на входы выходных элементов И 10-13, в результате чего через поразрядные элементы ИЛИ 18-21 на шины 34-37 проходит прямой код числа, записанного в регистре 2 (т.е. на шины 34-37 поступают сигналы с единичных выходов регистра 2). Если же к моменту поступления пятого тактового импульса с распределителя 1 триггера 4 счета хранит 1 (что представляет собой результат сложения по модулю два всех разрядов кода Грея), то задействует его выход 32 и срабатывает элемент И 8. Возтакающий на выходе последнего сигнал поступает на входы добавочных элементов И 14-17, в результате че го через поразрядные элементы ИЛИ 18-21 на шины 34-37 проходит обратный код числа, записанного в регистре 2 (т.е. на шины 34-37 поступают сигналы с нулевых выходов разрядов регистра 2). С шин 34-37 полученный параллельный двоичный код может быть подан на другое устрГой ство, например на вход вычислительной машины Таким образом, в предлагаемом устройстве для преобразования п-разрядного кода Грея в параллельный двоичный код требуется всего (п + 1) такт (т.е. (п -ь 1) временный интервал, что на два такта меньше, чем в известной схеме . Это достигается тем, что в предлагаемом преобразователе исключен такт инвертирования содержимого регистра 2, а также совмещением момента подачи первого (младшего) разряда кода Грея с первым тактом (с тактом установки регистра 2 в исходное нулевое состояние). В итоге увеличивается быстродействие преобразовате ля кода Грея в параллельный двоичный код. Формула и бретения Преобразователь кода Грея в параллельный двоичный код, содержащий распределитель на п выходов, выходной регистр, информационные входы всех разрядов которого, кроме младшего, подключены к выходам элементов И входной группы, первые входы которых объединены и подключены к прямому выходу счетного триггера, счетный вход которого через элемент задержки подключен ко входу преобразователя, п-ный выход распределителя подключен к управляющим входам выходного регистра, вторые входы элементов И входной группы подключены к соответствующим выходам распределителя, первый дополнительный элемент И, первь1й вход которого соединен с (п-1)-м выходом распределителя, а второй вход - с единичным выходом счетного триггера, первые входы элементов И первой выходной группы соединены с единичными выходами соответствующих разрядов выходного регистра, отличающийся тем, что, с целью повьш1ения быстродействия в него введены вторая выходная группа элементов И, первые входы которых соединеиы . с нулевыми выходами соответствующих разрядов выходного регистра, второй дополнительный элемент И, первый вход которого соединен с первым входом первого дополнительного элемента И, а второй вход подключен к нулевому выходу счетного триггера, управляющий вход которого подключён к п-му выходу распределителя, вторые входы элементов И первой и второй выходных групп объединены и подключены к выходам соответственно второго и первого дополнительных элементов И, первые входы злементов ИЛИ группы подключены к выходам соответствующих элементов И второй выходной группы, вторые входы - к выходам соответствующих элементов И первой выходной группы, а выходы элементов ИЛИ группы являются выходами преобразователя. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N 193787, л. G 06 F 5/02, 18.02.66. 2.Авторское свидетельство СССР N 431512, л. G 06 F 5/02, 22.08.72 (прототип).

J7 36 iS у, 2i Ь/ Г/д js

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода Грея в параллельный двоичный код | 1982 |

|

SU1070541A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА ГРЕЯ В ПАРАЛЛЕЛЬНЫЙ ДВОИЧНЫЙ КОД | 2003 |

|

RU2248033C1 |

| Преобразователь кодов | 1985 |

|

SU1259494A1 |

| Преобразователь кода Грея в параллельный двоичный код | 1990 |

|

SU1784963A1 |

| Преобразователь угол-код | 1982 |

|

SU1016807A1 |

| Преобразователь напряжения в код | 1979 |

|

SU841111A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU888102A1 |

| Преобразователь кодов | 1978 |

|

SU744548A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1023334A2 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

Авторы

Даты

1980-12-15—Публикация

1978-06-28—Подача