со

00

ел

to

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования резервированного сигнала времени | 1982 |

|

SU1092459A1 |

| Резервированный генератор импульсов | 1989 |

|

SU1619440A1 |

| УСТРОЙСТВО ДЛЯ ПРИВЯЗКИ ШКАЛ ВРЕМЕНИ | 1992 |

|

RU2046393C1 |

| Устройство для передачи частотно-временных сигналов | 1991 |

|

SU1818619A1 |

| Цифровой частотомер | 2019 |

|

RU2730047C1 |

| СИСТЕМА ОХРАННОЙ СИГНАЛИЗАЦИИ | 1993 |

|

RU2092903C1 |

| СИСТЕМА СИНХРОНИЗАЦИИ ЧАСОВ ПО РАДИОКАНАЛУ | 1985 |

|

SU1840365A1 |

| ИМИТАТОР ИСТОЧНИКОВ РАДИОСИГНАЛОВ | 1994 |

|

RU2094915C1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В НАПРЯЖЕНИЕ | 1987 |

|

RU2056700C1 |

| Адаптивный приемник сигналов минимальной частотной манипуляции | 1989 |

|

SU1835611A1 |

Изобретение м.б. использовано в эталонах времени. Цель изобретения - повьшение надежности и обеспечение непрерывного резервированного сигнала времени и эталонной частоты. Для этого используется для формирования выходного сигнала времени при отсутствии любых п-2 сигналов на входе логического формирователя сигнал любого работоспособного хранителя частоты. При наличии нескольких сигналов, не совпадающих по фазе, выходной сигнал формируется яз сигнала, имеющего наименьшую фазовую задержку. 2 з.п. ф-лы, 5 ил.

Ч)

Изобретение относится к приборостроению, предназначено для получения резервированных сигналов высокой надежности и фазовой стабильности и может быть использовано в эталонах времени.

Цель изобретения - повьппение надежности и обеспечение непрерьшного резервированного сигнала времени и эталонной частоты путем использования для формирования выходного СИГ нала времени при отсутствии любых (п-2) сигналов на входе логического формирователя сигнала любого работоспособного хранителя частоты, причем при Наличии нескольких сигналов, несовпадающих по фазе, выходной сигнал формируется из сигнала, имеющего наименьшую фазовую задержку.

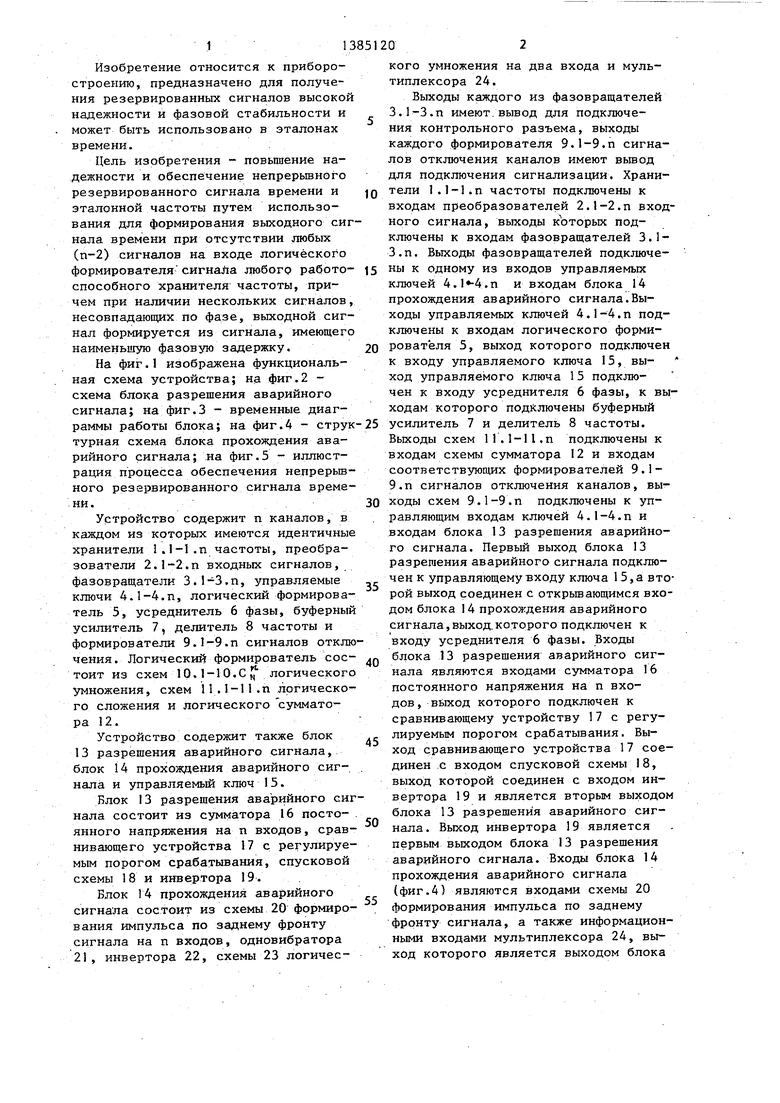

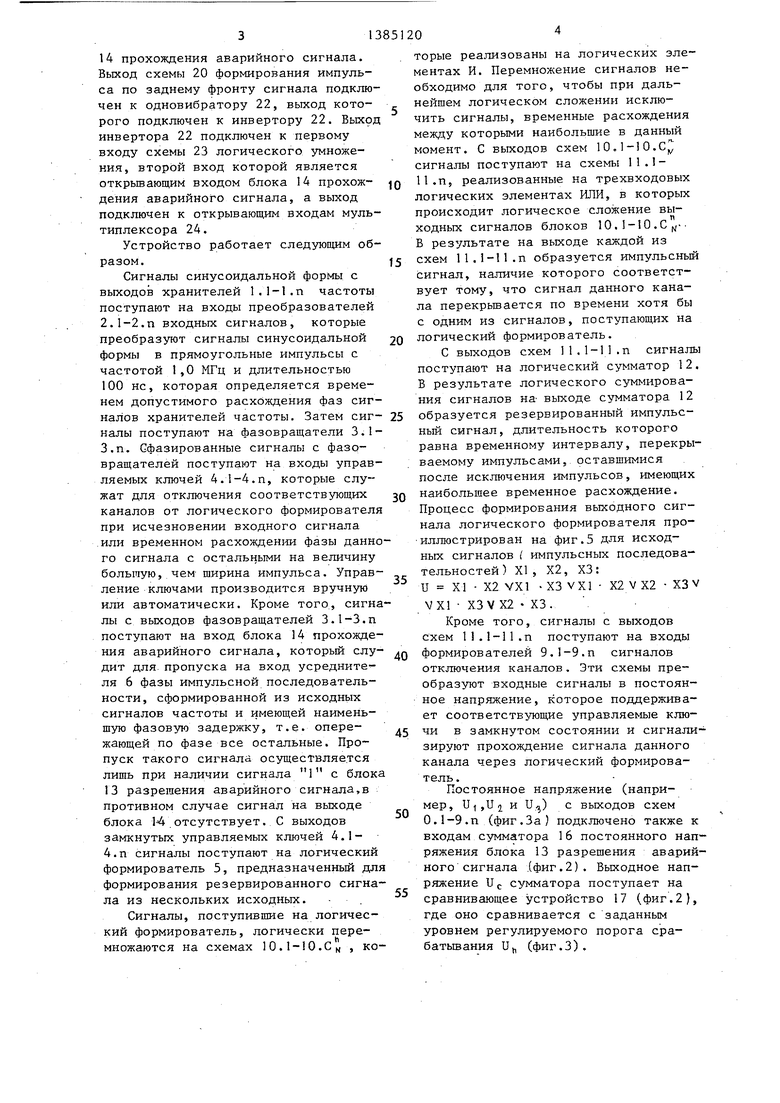

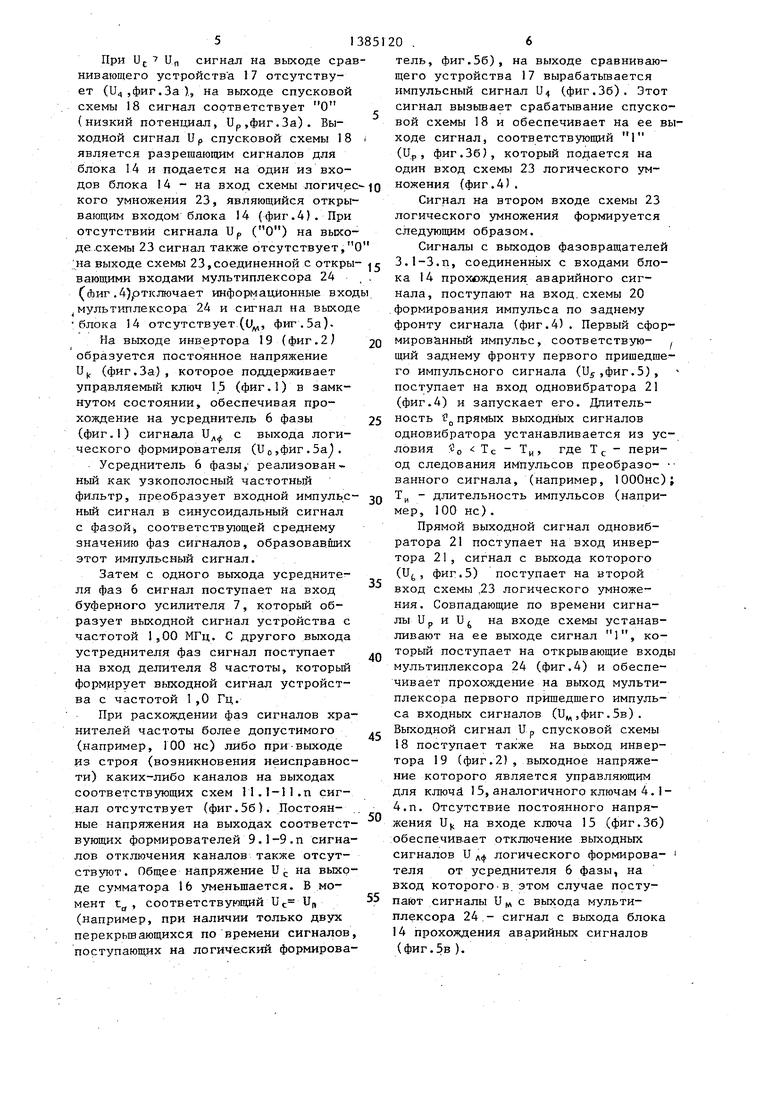

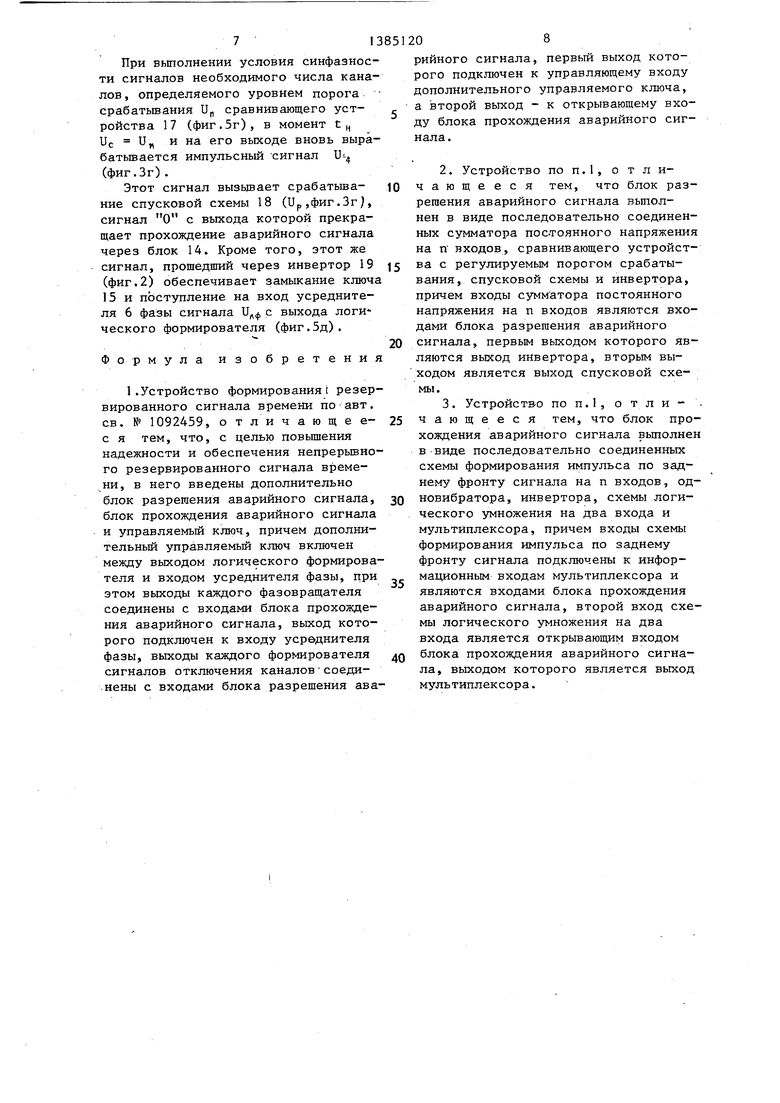

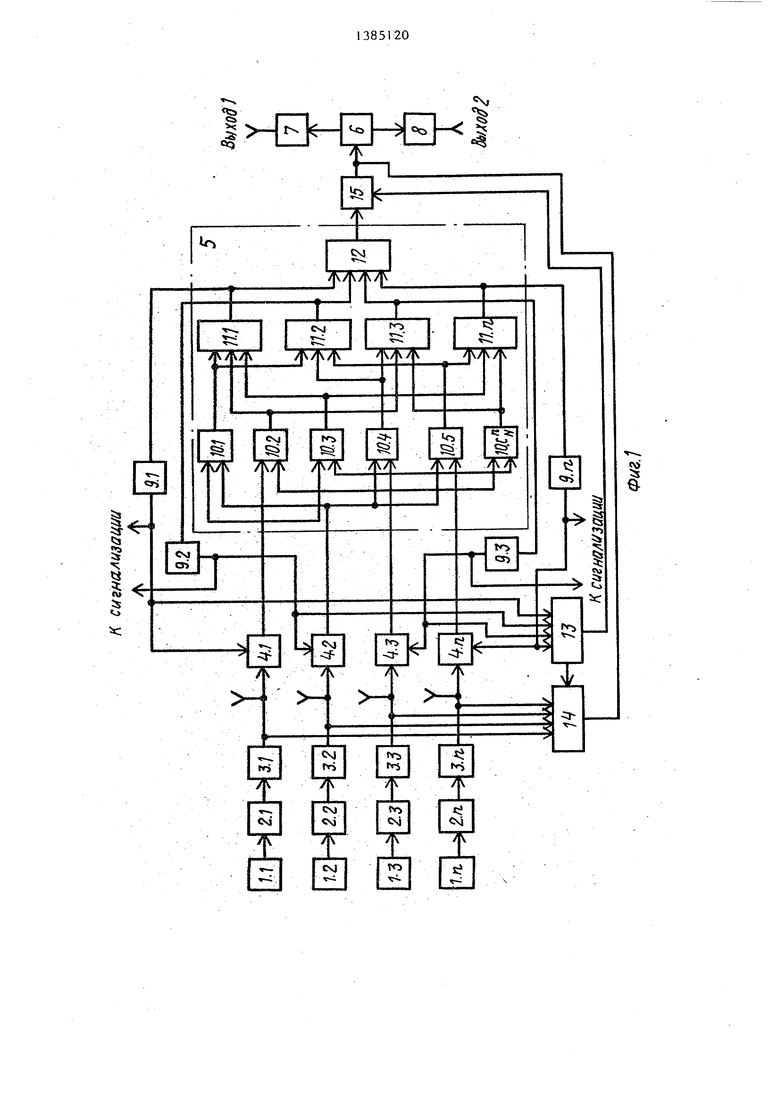

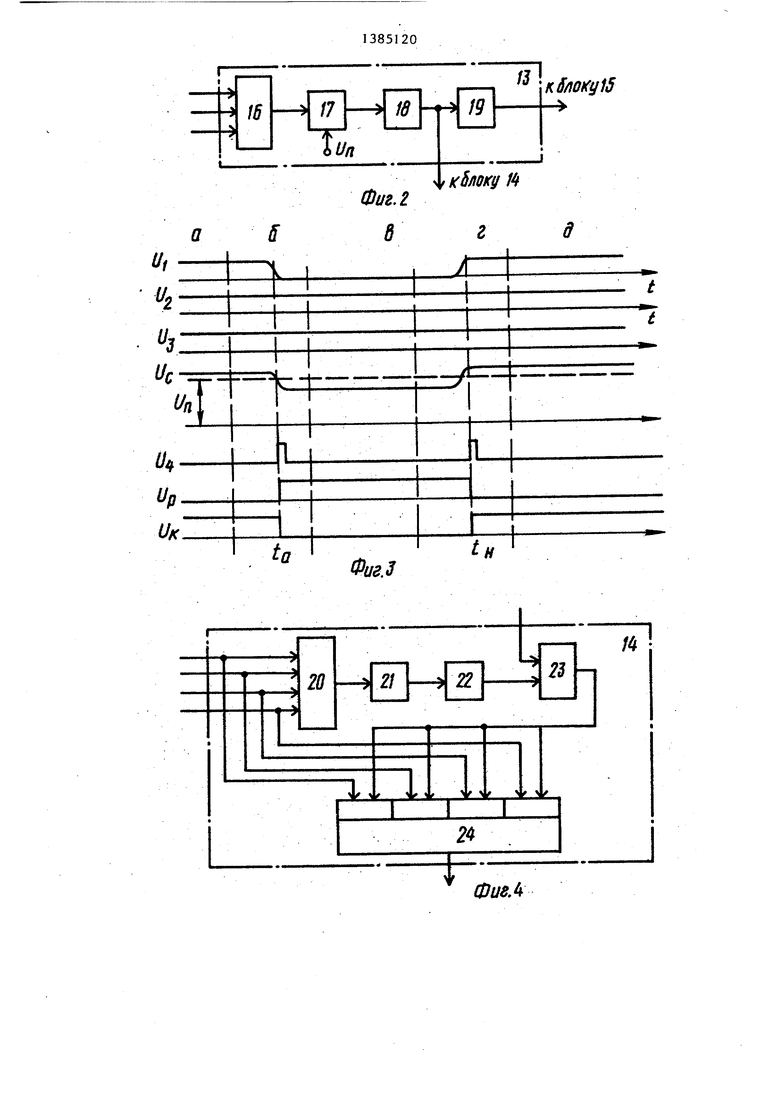

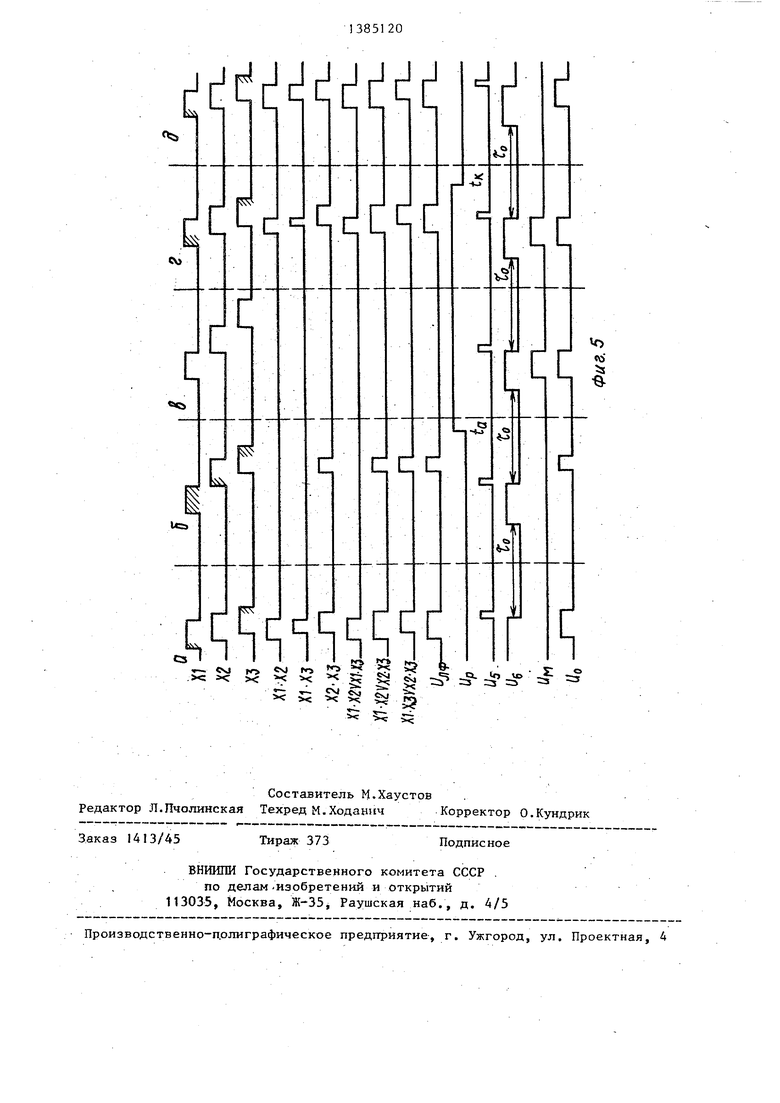

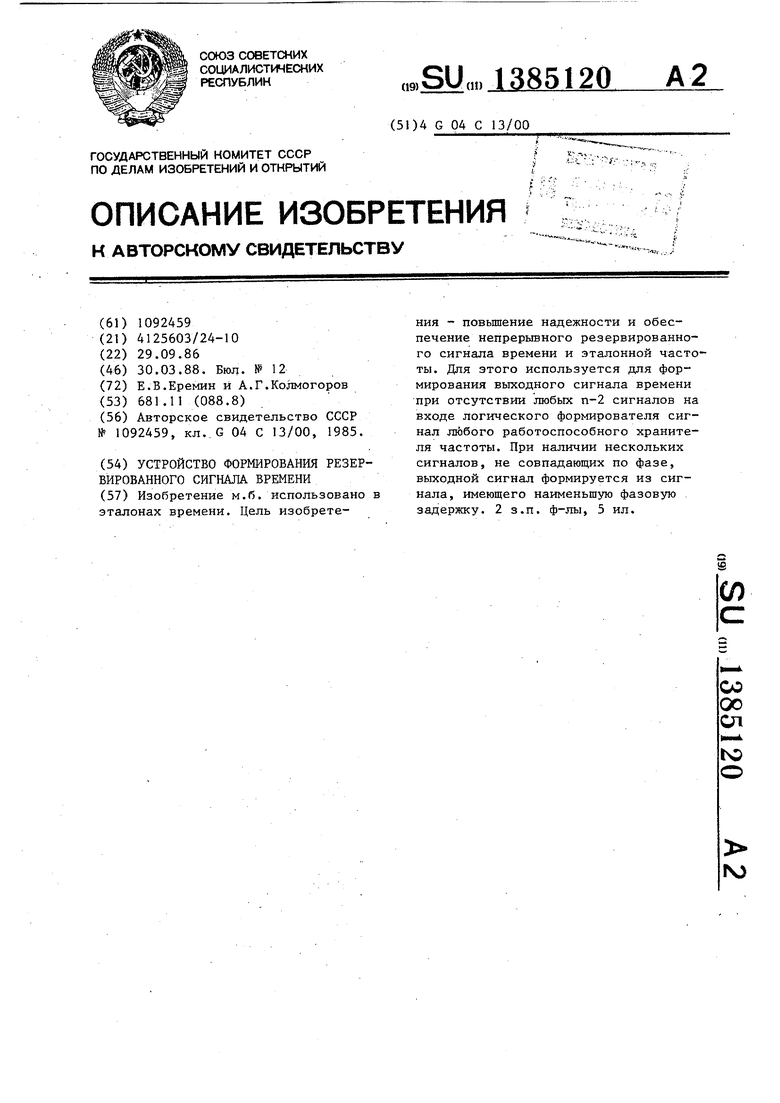

На фиг.1 изображена функциональная схема устройства; нд фиг.2 - схема блока разрешения аварийного сигнала; на фиг.3 - временные диаграммы работы блока; на фиг.4 - струк турная схема блока прохождения аварийного сигнала; на фиг.5 - иллюстрация процесса обеспечения непрерьт- ного резервированного сигнала времени.

Устройство содержит п каналов, в каждом из которых имеются идентичные хранители 1.1-l.n частоты, преобразователи 2.1-2.п входных сигналов, фазовращатели 3.1-З.п, управляемые ключи 4.1-4.П, логический формирователь 5, усреднитель 6 фазы, буферный усилитель 7, делитель 8 частоты и формирователи 9.1-9.п сигналов отклю чения. Логический формирователь состоит из схем 10,1-10.С J логического умножения, схем 11.1-П.п логического сложения и логического сумматора 12.

Устройство содержит также блок 13 разрешения аварийного сигнала, блок 14 прохождения аварийного сигнала и управляемый ключ 15.

Блок 13 разрешения аварийного сиг нала состоит из сумматора 16 постоянного напряжения на п входов, сравнивающего устройства 17 с регулируемым порогом срабатывания, спусковой схемы 18 и инвертора 19.

Блок 14 прохождения аварийного сигнала состоит из схемы 20 формиро- вания импульса по заднему фронту сигнала на п входов, одновибратора 21, инвертора 22, схемы 23 логичес

10

15

20

25

30

35

40

45

50

55

кого умножения на два входа и мультиплексора 24.

Выходы каждого из фазовращателей 3.1-З.п имеют/вывод для подключения контрольного разъема, выходы каждого формирователя 9.1-9.П сигналов отключения каналов имеют вьгоод для подключения сигнализации. Хранители 1.1-1.П частоты подключены к входам преобразователей 2.1-2.П входного сигнала, выходы которых подключены к входам фазовращателей 3.1- З.п. Выходы фазовращателей подключены к одному из входов управляемых ключей 4..п и входам блока 14 прохождения аварийного сигнала.Выходы управляемых ключей 4.1-4.П подключены к входам логического формирователя 5, выход которого подключен к входу управляемого ключа I5, вы- ход управляемого ключа 15 подключен к входу усреднителя 6 фазы, к выходам которого подключены буферный усилитель 7 и делитель 8 частоты. Вьшоды схем П. 1-1 l.n подключены к входам схемы сумматора 12 и входам соответствующих формирователей 9.1- 9.П сигналов отключения каналов, выходы схем 9.1-9.П подключены к управляющим входам ключей 4.1-4.п и входам блока 13 разрешения аварийного сигнала. Первый выход блока 13 разрешения аварийного сигнала подключен к управляющему входу ключа 15, а второй выход соединен с открьшающимся входом блока 14 прохождения аварийного сигнала,выход.которого подключен к входу усреднителя 6 фазы. Входы блока 13 разрешения аварийного сигнала являются входами сумматора 16 постоянного напряжения на п входов, вь1ход которого подключен к сравнивающему устройству 17 с регулируемым порогом срабатывания. Выход сравнивающего устройства 17 соединен с входом спусковой схемы 18, выход которой соединен с входом инвертора 19 и является вторьи выходом блока 13 разрешения аварийного сигнала. Выход инвертора 19 является первым выходом блока 13 разрешения аварийного сигнала. Входы блока 14 прохождения аварийного сигнала (фиг.4) являются входами схемы 20 формирования импульса по заднему фронту сигнала, а также информационными входами мультиплексора 24, выход которого является выходом блока

14 прохождения аварийного сигнала. Выход схемы 20 формирования импульса по заднему фронту сигнала подключен к одновибратору 22, выход которого подключен к инвертору 22. Выход инвертора 22 подключен к первому входу схемы 23 логического умножения, второй вход которой является открьшающим входом блока 14 прохож- дения аварийного сигнала, а выход подключен к открывающим входам мультиплексора 24.

Устройство работает следующим образом.

Сигналы синусоидальной формы с выходов хранителей 1.1-1.п частоты поступают на входы преобразователей 2.1-2.П входных сигналов, которые преобразуют сигналы синусоидальной формы в прямоугольные импульсы с частотой 1,0 МГц и длительностью 100 НС, которая определяется временем допустимого расхождения фаз сигналов хранителей частоты. Затем сиг- налы поступают на фазовращатели 3.1- З.п. Сфазированные сигналы с фазовращателей поступают на входы управляемых ключей 4.1-4.П, которые служат для отключения соответствующих каналов от логического формирователя при исчезновении входного сигнала или временном расхождении фазы данного сигнала с остальными на величину большую, чем ширина импульса. Управление ключами производится вручную или автоматически. Кроме того, сигналы с выходов фазовращателей 3.1-З.п поступают на вход блока 14 прохождения аварийного сигнала, который слу- дит для пропуска на вход усредните - ля 6 фазы импульсной последовательности, сформированной из исходных сигналов частоты и имеющей наименьшую фазовую задержку, т.е. опере- жающей по фазе все остальные. Пропуск такого сигнала осуществляется лишь при наличии сигнала 1 с блока 13 разрешения аварийного сигнала,в противном случае сигнал на выходе блока 14 отсутствует. С выходов замкнутых управляемых ключей 4.1- 4.П сигналы поступают на логический формирователь 5, предназначенный для формирования резервированного сигнала из нескольких исходных. .

Сигналы, поступившие на логический формирователь, логически перемножаются на схемах lO.l-IO.C , ко

Q Q

5

0

торые реализованы на логических элементах И. Перемножение сигналов необходимо для того, чтобы при дальнейшем логическом сложении исключить сигналы, временные расхождения между которыми наибольшие в данный момент. С выходов схем lO.l-lO.C, сигналы поступают на схемы 11.1- 11.п, реализованные на трехвходовых логических элементах ИЛИ, в которых происходит логическое сложение выходных сигналов блоков lO.l-lO.Cfj- В результате на выходе каждой из схем 11.1-11.п образуется импульсный сигнал, наличие которого соответствует тому, что сигнал данного канала перекрьшается по времени хотя бы с одним из сигналов, поступающих на логический формирователь.

С выходов схем 11.1-11.п сигналы поступают на логический сумматор 1 2. В результате логического суммирования сигналов на выходе сумматора 12 образуется резервированный импульсный сигнал, длительность которого равна временному интервалу, перекрываемому импульсами,, оставшимися после исключения импульсов, имеющих наибольшее временное расхождение. Процесс формирования выходного сигнала логического формирователя про- иллюстрирован на фиг.5 для исходных сигналов ( импульсных последовательностей ) XI, Х2, ХЗ: и XI Х2 VX1 ХЗ VX1 Х2 V Х2 ХЗ V VX1 X3VX2 ХЗ.

Кроме того, сигналы с выходов схем 11.1-11.п поступают на входы формирователей 9.1-9.П сигналов отключения каналов. Эти схемы преобразуют входные сигналы в постоянное напряжение, которое поддерживает cooтвeтcтвyюш e управляемые ключи в замкнутом состоянии и сигнализируют прохождение сигнала данного канала через логический формирователь .

Постоянное напряжение (например, Ui,U5i и и.) с выходов схем 0.1-9.п (фиг.За ) подключено также к входам сумматора 16 постоянного напряжения блока 13 разрешения аварийного сигнала .(фиг.2). Выходное напряжение и с сумматора поступает на сравнивающее устройство 17 (фиг.2), где оно сравнивается с заданным уровнем регулируемого порога сра- батьтания U (фиг.З).

51

При Uj. 7 Un сигнал на выходе сравнивающего устройства 17 отсутствует (и ,фиг.3а )., на выходе спусковой схемы 18 сигнал соответствует О (низкий потенциал, Up,фиг.За). Выходной сигнал и р спусковой схемы 18 является разрешающим сигналов для блока 14 и подается на один из входов блока 14 - на вход схемы логичнее кого умножения 23, являющийся открывающим входом блока 14 (фиг.4). При отсутствий сигнала Up (О) на выходе .схемы 23 сигнал также отсутствует, на выходе схемы 23,соединенной с откры Бающими входами мультиплексора 24 (йиг ,4),отключает информационные вход мультиплексора 24 и сигнал на выход блока 14 отсутствует (Ц,, фиг.За).

На выходе инвертора 19 (фиг.2 образуется постоянное напряжение U|, (фиг.За), которое поддерживает управляемый ключ 15 (фиг.1) в замкнутом состоянии, обеспечивая прохождение на усреднитель 6 фазы (фиг.1) сигнала ид с выхода логического формирователя (.5а. . Усреднитель 6 фазы,- реализован ный как узкополосный частотньгй фильтр, преобразует входной импульс- ный сигнал в синусоидальный сигнал с фазой соответствующей среднему значению фаз сигналов, образовавйшх этот импульсный сигнал.

Затем с одного выхода усреднителя фаз 6 сигнал поступает на вход буферного усилителя 7, который образует выходной сигнал устройства с частотой 1,00 МГц. С другого выхода устреднителя фаз сигнал поступает на вход делителя 8 частоты, который формирует выходной сигнал устройства с частотой 1,0 Гц.

При расхождении фаз сигналов хранителей частоты более допустимого (например, 100 не) либо при-выходе из строя (возникновения неисправности) каких-либо каналов на выходах соответствующих схем 11.1-ll.n сигнал отсутствует (фиг.56). Постоян- ные напряжения на выходах соответствующих формирователей 9.1-9.п сигналов отключения каналов также отсутствуют. Общее напряжение U (. на выходе сумматора 16 уменьшается. В момент t, соответствующий (например, при наличии только двух перекрьшающихся по времени сигналов, поступающих на логический формирова

0 5 о

Q

,

5

0

тель, фиг.56), на выходе сравнивающего устройства 17 вырабатьтается импульсный сигнал 04 (фиг.Зб). Этот сигнал вызьшает срабатывание спусковой схемы 18 и обеспечивает на ее выходе сигнал, соответствующий 1 (Up, фиг.Зб), который подается на один вход схемы 23 логического умножения (фиг.4),

Сигнал на втором входе схемы 23 логического умножения формируется следующим образом.

Сигналы с выходов фазовращателей 3.1-З.п, соединенных с входами блока 14 прохождения аварийного сигнала, поступают на вход.схемы 20

сформирования импульса по заднему фронту сигнала (фиг.4). Первый сформированный импульс, соответствую- щий заднему фронту первого пришедшего импульсного сигнала (и5,фиг.5), поступает на вход одновибратора 21 (фиг.4) и запускает его. Дпитель- ность прямых выходных сигналов одновибратора устанавливается из условия Тс - Тц, где Т с- - период следования импульсов преобразо- - ванного сигнала, (например, 1000нс); Т - длительность импульсов (например, 100 не).

Прямой выходной сигнал одновибратора 21 поступает на вход инвертора 2I, сигнал с выхода которого (U( , фиг.5) поступает на второй вход схемы ,23 логического умножения. Совпадающие по времени сигналы и р и и на входе схемы устанавливают на ее выходе сигнал 1, который поступает на открывающие входы мультиплексора 24 (фиг.4) и обеспечивает прохождение на выход мультиплексора первого пришедшего импульса входных сигналов (Un, ,фиг.5в) . Выходной сигнал Up спусковой схемы 18 поступает также на выход инвертора 19 (фиг.2), выходное напряжение которого является управляющим для ключи 15, аналогичного ключам 4.1- 4.п. Отсутствие постоянного напряжения и ц на входе к.шоча 15 (фиг.Зб)

:обеспечив.ает отключение выходных сигналов и дф логического формирова- теля от усреднителя 6 фазы, на вход которого-в. этом случае поступают сигналы и с вьпсода мультиплексора 24.- сигнал с выхода блока 14 прохождения аварийных сигналов (фиг.5в ).

71

При вьшолнении условия синфазнос- ти сигналов необходимого числа каналов, определяемого уровнем порога срабатьшания U сравнивающего уст- ройства 17 (фиг.5г), в момент t Uc и и на его выходе вновь вырабатывается импульсный сигнал Ui. (фиг.Зг).

Этот сигнал вызЕдаает срабатыва- ние спусковой схемы 18 (ир,фиг.3г, сигнал О с выхода которой прекращает прохождение аварийного сигнала через блок 14. Кроме того, этот же сигнал, прощедший через инвертор 19 (фиг.2) обеспечивает замыкание ключа 15 и поступление на вход усреднителя 6 фазы сигнала с выхода логического формирователя (фиг.5д).

Формула изобретения

5 О 0

5

208

рийного сигнала, первый выход которого подключен к управляющему входу дополнительного управляемого ключа,

а второй выход - к открывающему входу блока прохождения аварийного сигнала.

О.5 S S | I I J,

5 5 $ § 0 5J 5J

Составитель М.Хаустов . Редактор Л.Пчолинская Техред М,Ходанич Корректор О.Кундрик

Заказ 1413/45

Тираж 373

ВНИИПИ Государственного комитета СССР .

по делам .изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

| Устройство формирования резервированного сигнала времени | 1982 |

|

SU1092459A1 |

Авторы

Даты

1988-03-30—Публикация

1986-09-29—Подача