(21)4036604/24-24

(22)13.03.86

(46) 30.03.88. Бюл. № 12

(71)Научно-исследовательский и проектный институт по комплексной автоматизации нефтяной и химической промышленности

(72)К. А. Рустамов (53) 62-50(088.8)

(56) Сю Д., Мейер А. Современная теория автоматического управления и ее применение. М.: Машиностроение, 1972, с. 80,. рис. 4.6.

Авторское свидетельство СССР № 1171754, кл. G 05 В 13/02, 1.985.

(54) KB A3 И ИНВАРИАНТНЫ И ФИНИТНЫЙ РЕГУЛЯТОР С ПЕРЕМЕННОЙ СТРУКТУРОЙ

(57) Изобретение относится к технике автоматического управления линейными динамическими объектами, подвергаюш,имися воздействию скачкообразных возмущений, и может быть использовано в системах управления летательными аппаратами и различными технологическими процессами. Цель изобретения - расширение функциональных возможностей регулятора при действии на систему скачкообразных возмущений достигается тем, что введенный узел непрерывно-дискретного интегрирования позволяет после некоторого конечного момента времени достичь инвариантности к внешним возмущениям. 1 ил.

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Регулятор-ограничитель мощности турбоагрегата | 1984 |

|

SU1231559A1 |

| Устройство с размытой логической самоорганизацией для автоматического управления объектом,например ректификационной колонной | 1986 |

|

SU1434402A1 |

| ПРОПОРЦИОНАЛЬНО-ИНТЕГРАЛЬНО-ДИФФЕРЕНЦИАЛЬНЫЙ РЕГУЛЯТОР | 2002 |

|

RU2234116C1 |

| Система для управления периодическим процессом ферментации | 1989 |

|

SU1725203A1 |

| Адаптивное регулирующее устройство | 1982 |

|

SU1064271A1 |

| Система управления с переменной структурой | 1984 |

|

SU1171754A1 |

| Устройство для управления роботом | 1988 |

|

SU1618636A1 |

| Бинарная система управления вынужденным движением | 1983 |

|

SU1117587A1 |

| Система управления | 1983 |

|

SU1168896A1 |

| Система оптимизации режимов работы объекта | 1985 |

|

SU1260916A1 |

со

СХ)

ел

1C

со

Изобретение относится к автоматическому управлению линейными динамическими объектами, подвергающимися воздействию скачкообразных возмущений, и может быть использовано в системах управления летательными аппаратами и различными технологическими процессами.

Цель изобретения - расщирение функциональных возможностей регулятора при действии скачкообразных возмущений.

подается на ключ 4 узла 3 памяти и на первый вход сумматора 13. Узел памяти рабо- TiaeT следующим образом. При командном сигнале V +1 ключ 4 находится в нормально замкнутом положении «d. При этом узел памяти работает как повторитель и входной сигнал axi без изменения проходит на выход элемента 5 памяти. При V -1 ключ 4 переходит в положение б и вход элемента 5 памяти блокируется. При этом

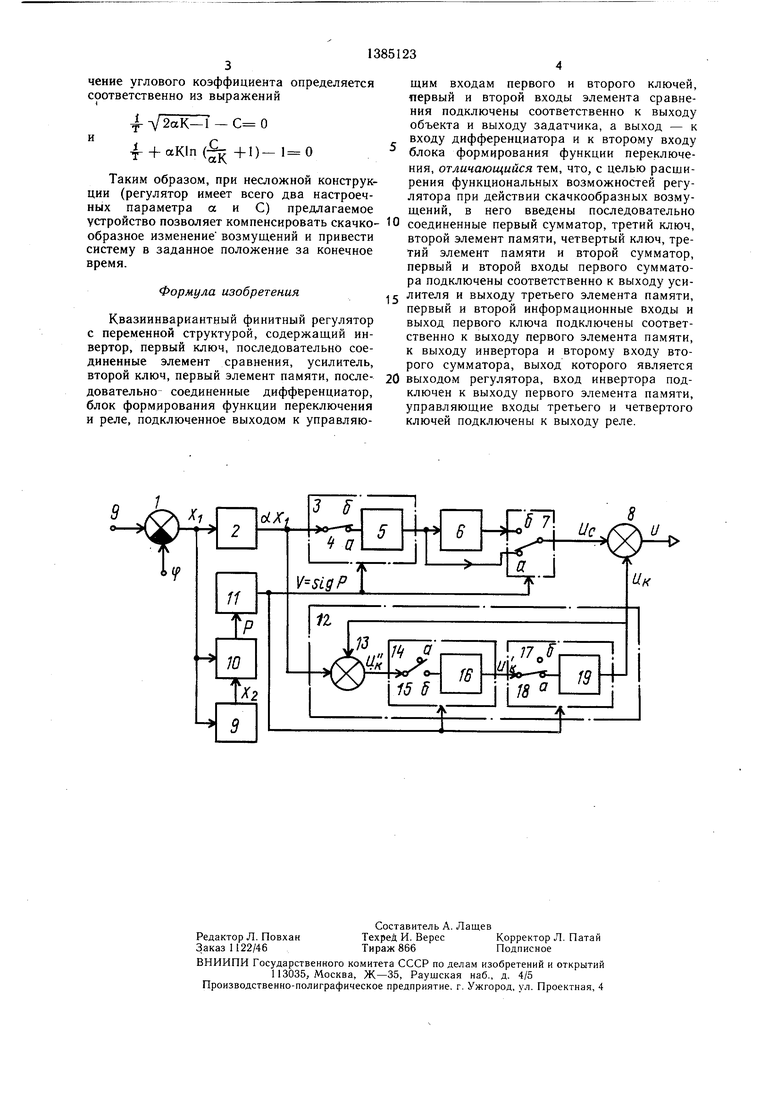

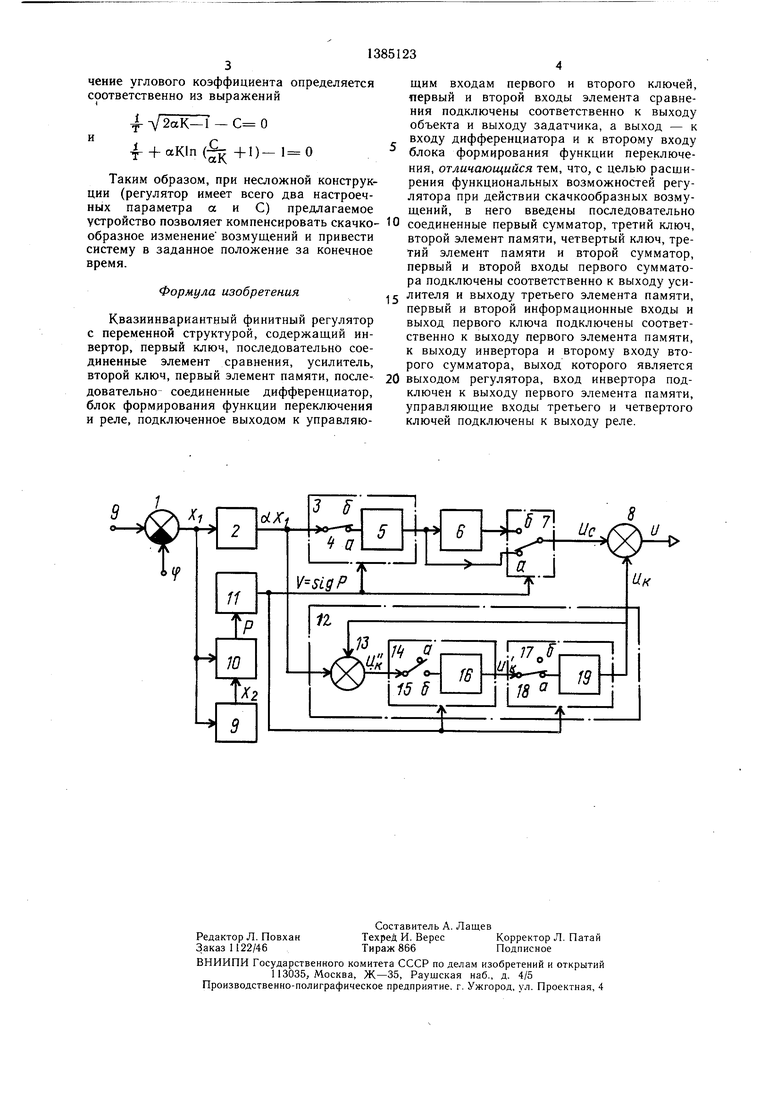

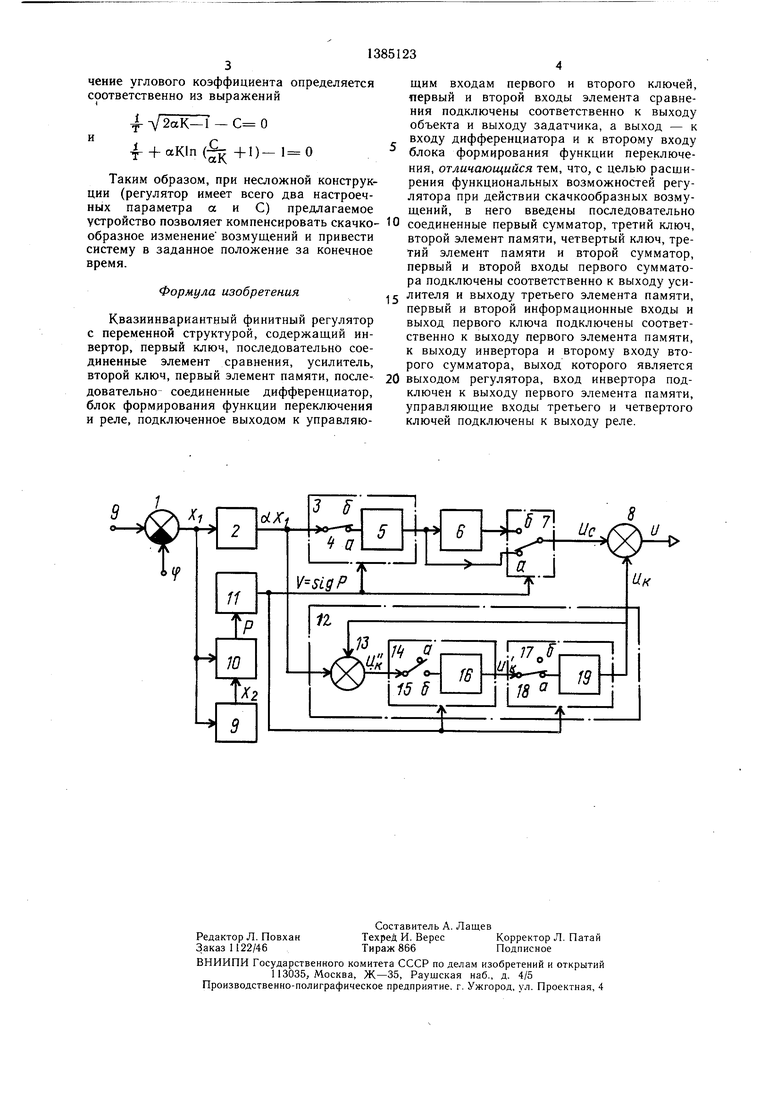

На чертеже представлена блок-схема 0 узел памяти работает в режиме запоми- предлагаемого регулятора.нания и на выходе элемента памяти 5 форРегулятор содержит элемент 1 сравнения, мируется постоянный сигнал ахи, соответствующий значению входного сигнала axi в момент размыкания ключа 4. Выход узла

усилитель 2, первый узел 3 памяти, состоящий из второго ключа 4 и первого элемента

5 памяти, инвертор 6, первый ключ 7, второй 5 памяти через инвертор б напрямую соесумматор 8, дифференциатор 9, блок 10 формирования функции переключения, реле 11, узел 12 непрерывно-дискретного интегрирования, первый сумматор 13, второй узел 14 памяти, третий ключ 15, второй элемент 16

динен соответственно с сигнальными входами «б и «а коммутатора. При командном сигнале V -(-1 ключ коммутатора находится в нормально замкнутом положении «а, а при V переходит в положепамяти, третий узел 17 памяти, четвертый 20 ние «б. Выходной сигнал с коммутатора ключ 18, третий элемент 19 памяти.подается на второй вход сумматора 8, выход

которого является выходом регулятора. Таким образом, статическая составляюВ рассматриваемом случае использования регулятора объектом управления является двойной интегратор, описываемый выражением.

Xi Х2

, где X: - сигнал ошибки;

и -управляющее воздействие, F const- эквивалентное возмущение, вызванное в общем случае действием задания и возмущения по нагрузке. Регулятор работает по следующему алгоритму:

tax:+ а 2 Xis(n); при 1 n-j ff -axis+a 2 xis(n)const, при где a - коэффи циент усиления регулятора;

- значение сигнала ошибки в момент изменения значка V signP от V +1 на V -1.

x is(n) - значение сигнала ошибки в момент изменения значка V signP от V -1 на V +1 в п-м изменении -- такте;,

Р Sxi, S X2-f Сх2, С V2«K . При оптимальной 1Ц4стройке углового коэффициента в системах с предложенным регулятором за N 3 такта достигается инвариантность к внешним возмущениям. Компенсация возмущений дости25

щая управляющего сигнала регулятора формируется по алгоритму

и,

ах|

при V +1, L-axis const при V -1

гается членом 1) а 2 xis(n).

Регулятор работает Следующим образом.

На выходе элемента 1 сравнения на основании поступающей с объекта информации ч и задания g формируется сигнал 55 ошибки X, , который подается на вход усилителя 2. На выходе последнего формируется сигнал управления axi, который

2Q В блоке 10 формирования функции переключения на основании поступающей с элемента 1 сравнения информации xj и с дифференциатора 9 - Х2 формируется сигнал переключения , который подается на вход реле 11, выходной сигнал которого ,3,4... 35 s gnP- Командный сигнал V одновременно подается на управляющие входы узлов 3, 14, 17 памяти для управления ключами 4, 15 и 18 и на управляющий вход коммутатора.

Компенсация возмущений осуществля40 ется узлом 12 непрерывно-дискретного интегрирования, состоящим из последовательно соединенных сумматора 13 и узлов 14 и 17 памяти, образующих узел задержки на такт. Выходной сигнал узла 17 памяти в качестве положительной обратной связи подается на второй вход сумматора 13, а также на первый вход сумматора 8. Первый вход сумматора 13 подключен к выходу усилителя. При V +1 ключи 15 и 18 находятся в нормально замкнутом положении «а, а при V 1 переходят в положение «б.

Узел 12 производит суммирование величины axi только в моменты перехода изображающей точки из области с

в область с V +1 и обеспечивает компенсацию возмущения.

При использовании регулятора в системах управления с консервативными объектами ф Ки и объектами типа интегратор с замедлением Тф+ ф KU оптимальное зна45

50

подается на ключ 4 узла 3 памяти и на первый вход сумматора 13. Узел памяти рабо- TiaeT следующим образом. При командном сигнале V +1 ключ 4 находится в нормально замкнутом положении «d. При этом узел памяти работает как повторитель и входной сигнал axi без изменения проходит на выход элемента 5 памяти. При V -1 ключ 4 переходит в положение б и вход элемента 5 памяти блокируется. При этом

узел памяти работает в режиме запоми- нания и на выходе элемента памяти 5 фор памяти через инвертор б напрямую соединен соответственно с сигнальными входами «б и «а коммутатора. При командном сигнале V -(-1 ключ коммутатора находится в нормально замкнутом положении «а, а при V переходит в положение «б. Выходной сигнал с коммутатора подается на второй вход сумматора 8, выход

25

щая управляющего сигнала регулятора формируется по алгоритму

и,

ах|

при V +1, L-axis const при V -1

чение углового коэффициента определяется соответственно из выражений

4- V2aK-Г - С О

f+ аК1п( +1)

щим входам первого и второго ключей, первый и второй входы элемента сравнения подключены соответственно к выходу объекта и выходу задатчика, а выход - к входу дифференциатора и к второму входу блока формирования функции переключения, отличающийся тем, что, с целью расширения функциональных возможностей регулятора при действии скачкообразных возмущений, в него введены последовательно

Таким образом, при несложной конструкции (регулятор имеет всего два настроечных параметра ее и С) предлагаемое

устройство позволяет компенсировать скачко- Ю соединенные первый сумматор, третий ключ, образное изменение возмущений и привести второй элемент памяти, четвертый ключ, третий элемент памяти и второй сумматор, первый и второй входы первого сумматора подключены соответственно к выходу уси- :.с лителя и выходу третьего элемента памяти, первый и второй информационные входы и выход первого ключа подключены соответственно к выходу первого элемента памяти, к выходу инвертора и второму входу второго сумматора, выход которого является

второй ключ, первый элемент памяти, после- 20 выходом регулятора, вход инвертора под- довательно соединенные дифференциатор, ключен к выходу первого элемента памяти, блок формирования функции переключения управляющие входы третьего и четвертого и реле, подключенное выходом к управляю- ключей подключены к выходу реле.

систему в заданное положение за конечное время.

Формула изобретения

Квазиинвариантный финитный регулятор с переменной структурой, содержащий инвертор, первый ключ, последовательно соединенные элемент сравнения, усилитель.

3 S

щим входам первого и второго ключей, первый и второй входы элемента сравнения подключены соответственно к выходу объекта и выходу задатчика, а выход - к входу дифференциатора и к второму входу блока формирования функции переключения, отличающийся тем, что, с целью расширения функциональных возможностей регулятора при действии скачкообразных возмущений, в него введены последовательно

соединенные первый сумматор, третий ключ, второй элемент памяти, четвертый ключ, третий элемент памяти и второй сумматор, первый и второй входы первого сумматора подключены соответственно к выходу уси- лителя и выходу третьего элемента памяти, первый и второй информационные входы и выход первого ключа подключены соответственно к выходу первого элемента памяти, к выходу инвертора и второму входу второго сумматора, выход которого является

-4ti

.Л

J

UK

Авторы

Даты

1988-03-30—Публикация

1986-03-13—Подача