(Л

со сх ел

1С

00

Изобретение относится к вычислительной технике и может быть использовано при построении арифметико-логических устройств в информационно-измерительных и управляющих системах.

Цель изобретения - упрощение устройства, повыщение быстродействия и точности.

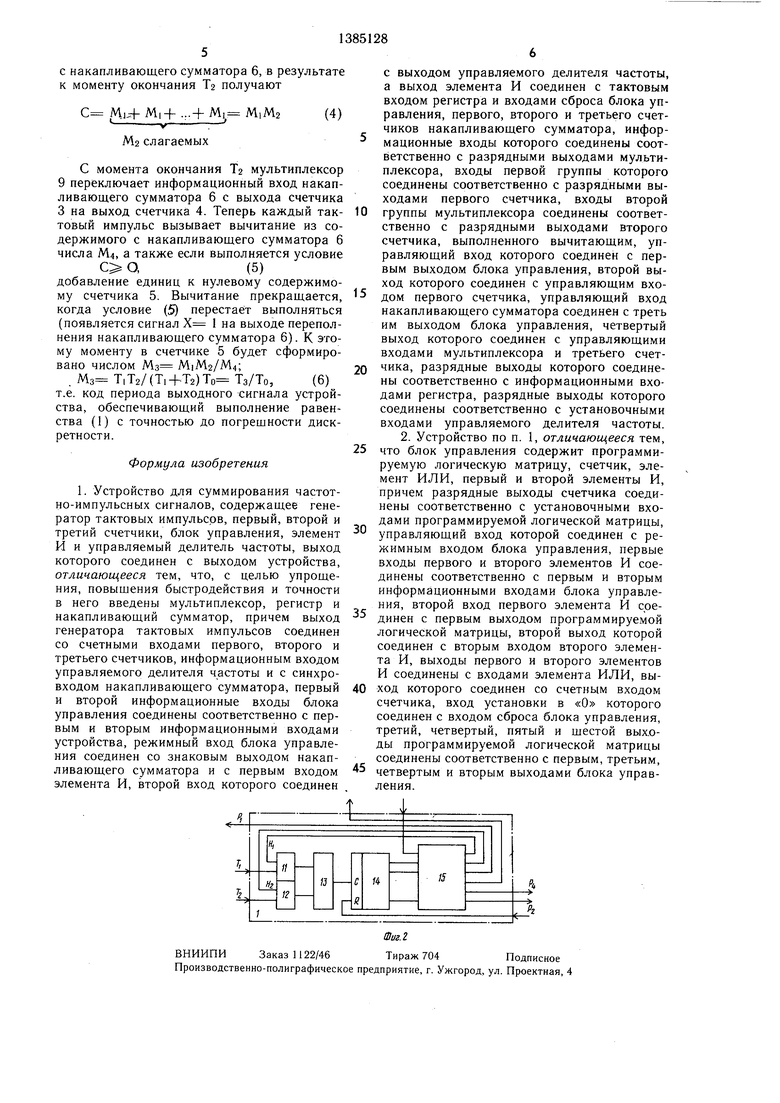

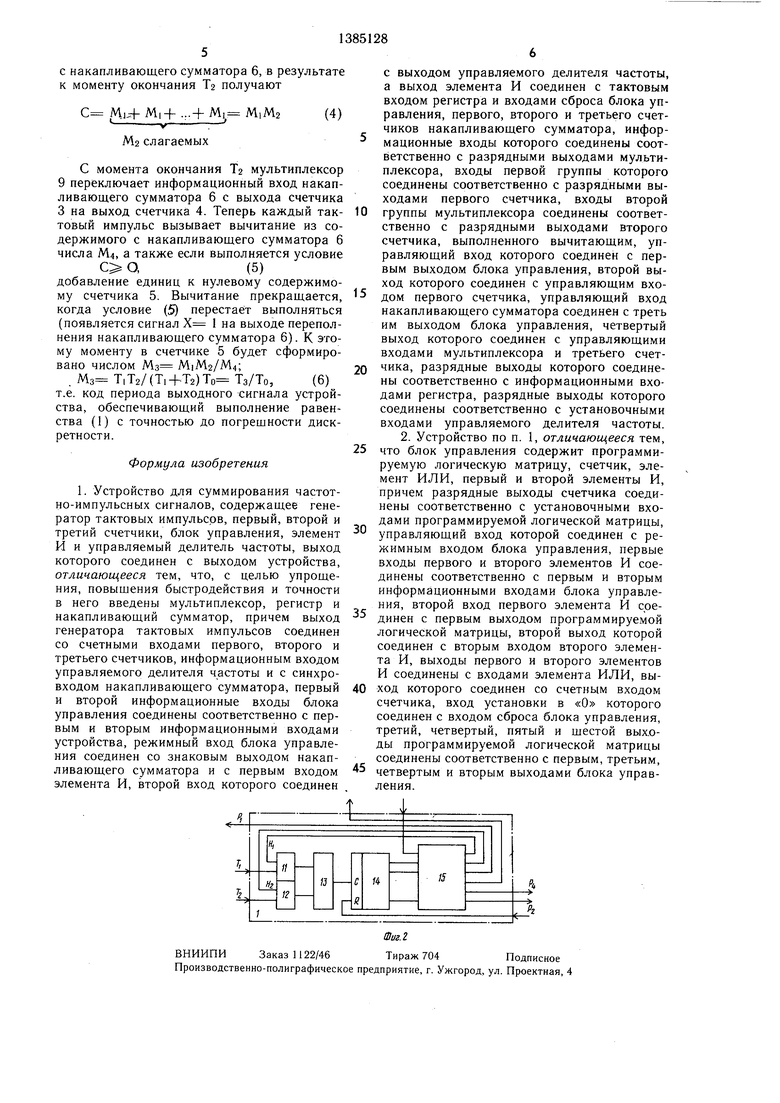

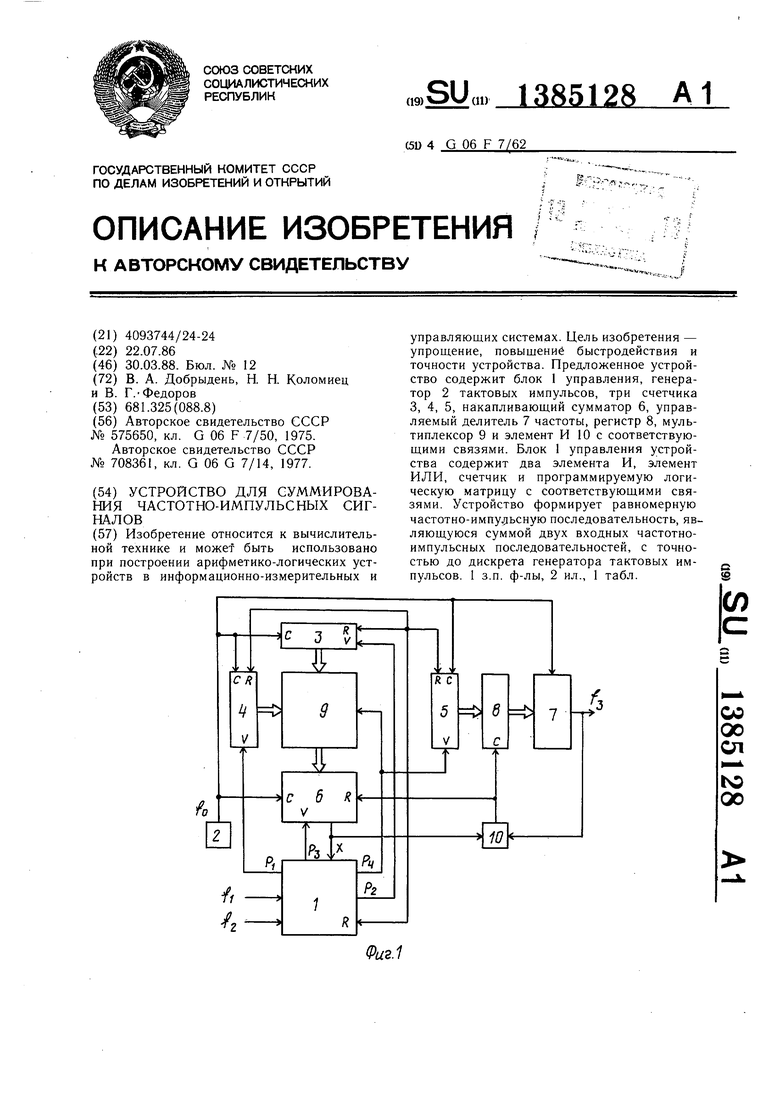

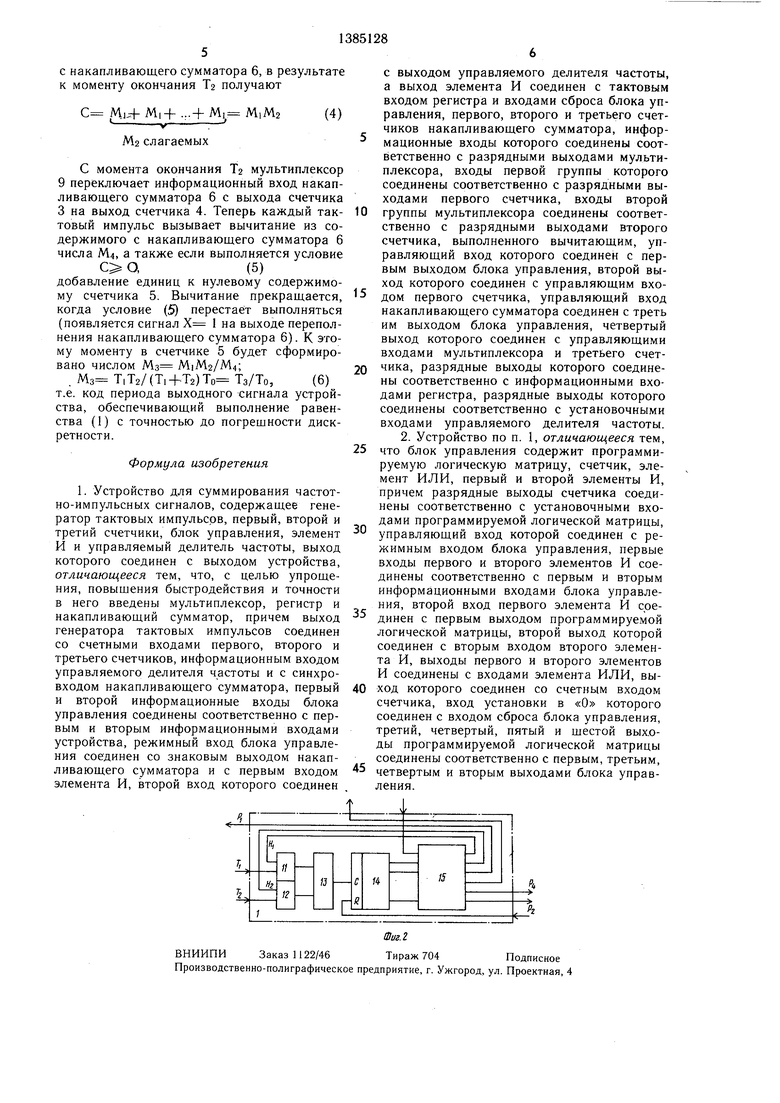

На фиг. 1 представлена функциональная схема устройства для суммирования частотно-импульсных сигналов; на фиг. 2 - функциональная схема блока управления устройства.

Устройство содержит блок 1 управления, генератор 2 тактовых импульсов, первый, второй и третий счетчики 3-5, накапливающий сумматор 6, управляемый делитель 7 частоты, регистр 8, мультиплексор 9 и элемент И 10, причем выход генератора 2 тактовых импульсов соединен с счетными входами первого, второго и третьего счетчиков 3-5, синхровходом накапливающего сумматора 6 и информационным входом управляемого делителя 7 частоты, первый и второй информационные входы блока 1 управления соединены соответственно с первым и вторым информационными входами устройства, режимный вход блока 1 управления соединен с выходом сигнала переполнения накапливающего сумматора бис первым входом элемента И 10, второй вход которого соединен с выходом управляемого делителя 7 частоты и с выходом устройства, а выход элемента И 10 соединен с тактовым входом регистра 8 и с входом сброса блока 1 управления, первого, второго и третьего счетчиков 3-5 и накапливающего сумматора 6, информационные входы которого соединены соответственно с разрядными выходами мультиплексора 9, входы первой группы которого соединены соответственно с разрядными выходами первого счетчика 3, входы второй группы мультиплексора 9 соединены соответственно с разрядными выходами второго счетчика 4, выполненного вычитающим, управляющий вход которого соединен с первым выходом блока

1 управления, второй выход которого соединен с управляющим входом первого счетчика 3, управляющий вход накапливающего сумматора б соединен с третьим выходом блока 1 управления, четвертый выход которого сое- динен с управляющими входами мультиплексора 6 и третьего счетчика 5, разрядные выходы которого соединены соответственно с информационными входами регистра 8, разрядные выходы которого соединены соответственно с установочными входами управляемого делителя 7 частоты.

Блок 1 управления содержит первый и второй элементы И 11, 12, элемент ИЛИ 13, счетчик 14 и программируемую логическую матрицу 15, причем разрядные выходы счетчика 14 соединены соответственно с установочными входами программируемой логической матрицы 15, управляющий вход которой соединен с режимным входом блока Г управления, первые входы первого и второ- 0 го элементов И 11 и 12 соединены соответственно с первым и вторым информационными входами блока I управления, второй вход первого элемента И 11 соединен с первым выходом программируемой логической матрицы 15, второй выход которой соединен с вторым входом второго элемента И 12, выходы первого и второго элементов И 11 и 12 соединены с входами элемента ИЛИ 13, выход которого соединен со счетным входом счетчика 14, вход установл ки в «О которого соединен с входом сброса блока управления, третий, четвертый, пятый и щестой выходы программируемой логической матрицы 15 соединены соответственно с первым, третьим, четвертым и вторым выходами блока 1 управления.

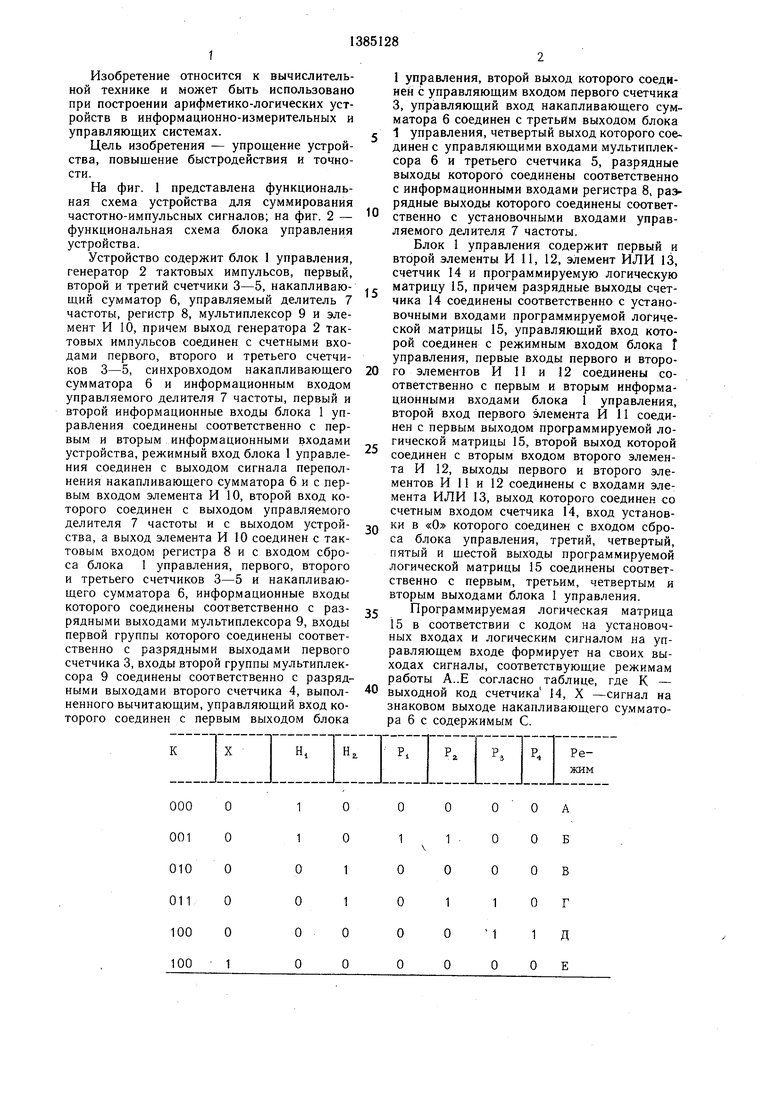

Программируемая логическая матрица 15 в соответствии с кодом на установочных входах и логическим сигналом на управляющем входе формирует на своих выходах сигналы, соответствующие режимам работы А..Е согласно таблице, где К - 0 выходной код счетчика 14, X -сигнал на знаковом выходе накапливающего сумматора 6 с содержимым С.

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор-вычитатель частотно-импульсных сигналов | 1991 |

|

SU1807483A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| Цифровой фильтр | 1986 |

|

SU1387174A1 |

| Устройство для умножения элементов конечного поля GF(2 @ ) при м @ 3 | 1990 |

|

SU1728858A1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ЧАСТОТНОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2212110C1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| Устройство управления | 1984 |

|

SU1229721A1 |

| Преобразователь активной мощности в цифровой код | 1989 |

|

SU1780033A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении арифметико-логических устройств в информационно-измерительных и управляющих системах. Цель изобретения - упрощение, повыщениё быстродействия и точности устройства. Предложенное устройство содержит блок 1 управления, генератор 2 тактовых импульсов, три счетчика 3, 4, 5, накапливающий сумматор 6, управляемый делитель 7 частоты, регистр 8, мультиплексор 9 и элемент И 10 с соответствующими связями. Блок 1 управления устройства содержит два элемента И, элемент ИЛИ, счетчик и программируемую логическую матрицу с соответствующими связями. Устройство формирует равномерную частотно-импульсную последовательность, являющуюся суммой двух входных частотно- импульсных последовательностей, с точностью до дискрета генератора тактовых импульсов. 1 з.п. ф-лы, 2 ил., 1 табл. с S

О

1

о

1

о

о

Режим А - ожидание начала периода Т|. При этом генератор 2, делитель 7 частоты и регистр 8 обеспечивают формирование выходных импульсов устройства с периодом, определяемым содержимым регистра 8, элемент И 10 закрыт по первому входу, счетчики 3, 4, 5 и накапливающий сумматор 6 установлены в «О, на всех выходах управляющего блока 1 управления - нулевой сигнал, к информационному входу сумматора 6 подключен через мультиплексор 9 выход счетчика 3.

В момент прихода первого импульса на первый вход блока 1 управления (момент начала периода Ti) устройство переходит в режим Б.

Режим Б - определение периода TI и первого слагаемого суммы (Ti-j- Т2).

При этом в течение периода Ti тактовые импульсы поступают на входы счетчиков 3 и 4, в результате к моменту поступления второго импульса на первый вход управляющего блока (импульс,а окончания периода Ti) в счетчике 3 будет сформировано числом Mi, а в счетчике 4 - дополнительный код числа -MI, этот импульс переводит устройство в режим В.

Режим В - ожидание начала периода Т2, Режим аналогичен режиму А с тем отличием, что в режиме А устройство реагирует на импульс начала Ti, не реагируя на импульсы, поступающие на второй вход устройства, а в режиме В оно реагирует на импульс начала Та и Hg реагирует на импульсы периода Ть

Режим Г - определение суммы (Ti+Ta) и вычисление произведения ТгТ2. В этом режиме единичный сигнал поддерживается на разрешающих входах счетчика 4 и накапливающегося сумматора 6, заканчивается режим в момент прихода импульса окончания Т2, к этому моменту в счетчике 4 будет сформирован дополнительный код суммы - (М|+ М2) -М4; кроме того, поскольку каждый из М2 тактовых импульсов вызывает прибавление к содержимому накапливающего сумматора 6 числа Mi, из счетчика 3, то в сумматоре 6 будет сформировано произведение Mi M2.

Режим Д - деление произведения Ti T2 на сумму Ti4- Т2. В этом режиме единичный сигнал снимается с разрешающего входа счетчика 4, сохраняется на входе накапливающегося сумматора 6 и устанавливается на входе счетчика 5, а также на управляющем входе мультиплексора 9, так что к информационному входу накапливающего сумматора 6 будет подключен теперь выход счетчика 4. Каждый тактовый импульс вызывает в этом режиме прибавление содержимого счетчика 4 к содержимому с сумматора 6 и увеличение на единицу содержимого счетчика 5. Работа в этом режиме заканчивается, когда на знаковом выходе

сумматора 6 появится сигнал . К этому моменту в счетчик 5 поступит столько импульсов, сколько раз можно вычесть М4 из М| М2 до получения отрицательного

остатка, т.е. целая часть частного Mi M2/M4. С появлением сигнала устройство переходит в режим Е.

Режим Е - ожидание очередного выходного импульса устройства, выполняющего

передачу числа Mj из счетчика 5 в регистр 8 и устанавливающего исходное состояние всех блоков за исключением регистра 8. Это ожидание необходимо для исключения сбоев в работе управляемого делителя 7 частоты. Его выходной импульс, пройдя через открытый в режиме Е элемент И 10, возвращает устройство в режим А. С этого момента период выходных импульсов устройства становится равным новому значению Тз, а устройство начинает следующий цикл определения текущего значения Тз, соответствующего

новым значениям периодов Ti и Т2.

В соответствии с формированием блоком 1 управления выходных сигналов устройство работает следующим образом.

Выходная частота устройства Гз определяется равенством

f3 fl+f2(1)

ИЗ которого следует

13

.ii

fi+f2 1; + 4, , (а)

0

Устройство формирует в счетчике 5 цифровой код Mj Т, /TO периода выходной частоты, передаваемый затем в регистр 8. В результате импульсы на выходе управля5 емого делителя 7 частоты, являющемся выходом устройства, следуют с периодом Тз, т.е. с частотой, определяемой равенством (1), причем значение Тз циклически формируется в соответствии с текущими значениями TI и Т2.

Принцип формирования величины Мз заключается в следующем.

Вначале на счетчике 3 формируется код MI TI/TO периода первого входного сигнала устройства - путем подсчета числа такто5 вых импульсов в течение времени Ti. Одновременно эти же тактовые импульсы поступают на вычитающий вход счетчика 4, вследствие чего в нем формируется дополнительный код числа -М|. После этого тактовые импульсы в течение очередного

0 периода Т2 второго входного сигнала устройства поступают на вход счетчика 4, в котором к концу этого периода будет сформирован дополнительный код числа -М4 -(Mi+M2), где М2 Тг/То, т.е.

М4 (Т,+ Т2)/То.(3)

- Кроме того, каждый тактовый импульс, поступающий в течение этого периода Т2, вызывает прибавление содержимого М| счетчика 3 к нулевому исходному содержимому

с накапливающего сумматора 6, в результате к моменту окончания Т2 получают

С .,.+ Mi MiM2

(4)

М2 слагаемых

С момента окончания Тг мультиплексор 9 переключает информационный вход накапливающего сумматора 6 с выхода счетчика 3 на выход счетчика 4. Теперь каждый так- товый импульс вызывает вычитание из содержимого с накапливающего сумматора 6 числа М, а также если выполняется условие

С О,(5)

добавление единиц к нулевому содержимому счетчика 5. Вычитание прекращается, когда условие (5) перестает выполняться (появляется сигнал Х 1 на выходе переполнения накапливающего сумматора 6). К этому моменту в счетчике 5 будет сформировано числом Мз MiM2/M4;

Мз Т|Т2/(Т,+Т2)То Тз/То,(6)

т.е. код периода выходного сигнала устройства, обеспечивающий выполнение равенства (1) с точностью до погрещности дискретности.

Формула изобретения

ливающего сумматора и с первым входом элемента И, второй вход которого соединен

0

0

5

5

0

5

с выходом управляемого делителя частоты, а выход элемента И соединен с тактовым входом регистра и входами сброса блока управления, первого, второго и третьего счетчиков накапливающего сумматора, информационные входы которого соединены соответственно с разрядными выходами мультиплексора, входы первой группы которого соединены соответственно с разрядными выходами первого счетчика, входы второй группы мультиплексора соединены соответственно с разрядными выходами второго счетчика, выполненного вычитающим, управляющий вход которого соединен с первым выходом блока управления, второй выход которого соединен с управляющим входом первого счетчика, управляющий вход накапливающего сумматора соединен с треть им выходом блока управления, четвертый выход которого соединен с управляющими входами мультиплексора и третьего счетчика, разрядные выходы которого соединены соответственно с информационными входами регистра, разрядные выходы которого соединены соответственно с установочными входами управляемого делителя частоты. 2. Устройство по п. 1, отличающееся тем, что блок управления содержит программируемую логическую матрицу, счетчик, элемент ИЛИ, первый и второй элементы И, причем разрядные выходы счетчика соединены соответственно с установочными входами программируемой логической матрицы, управляющий вход которой соединен с режимным входом блока управления, первые входы первого и второго элементов И соединены соответственно с первым и вторым информационными входами блока управления, второй вход первого элемента И соединен с первым выходом программируемой логической матрицы, второй выход которой соединен с вторым входом второго элемента И, выходы первого и второго элементов И соединены с входами элемента ИЛИ, выход которого соединен со счетным входом счетчика, вход установки в «О которого соединен с входом сброса блока управления, третий, четвертый, пятый и щестой выходы программируемой логической матрицы соединены соответственно с первым, третьим, четвертым и вторым выходами блока управления.

| Частотно-импульсное алгебраическое суммирующее устройство | 1975 |

|

SU575650A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для суммирования частотно-импульсных сигналов | 1977 |

|

SU708361A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-30—Публикация

1986-07-22—Подача