ON О

СЛ

00 XI

Изобретение относится к радиотехнике и может быть использовано в вычислительных, измерительных и преобразовательных устройствах.

Целью изобретения является повышение точности умножения частоты.

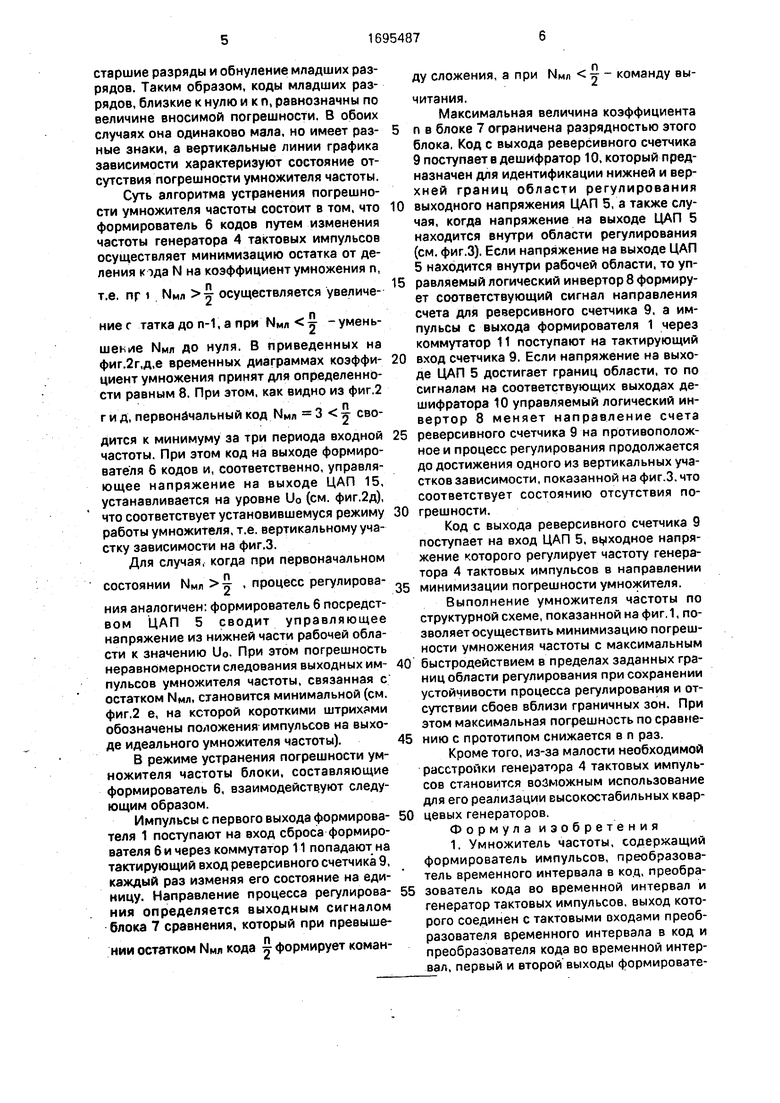

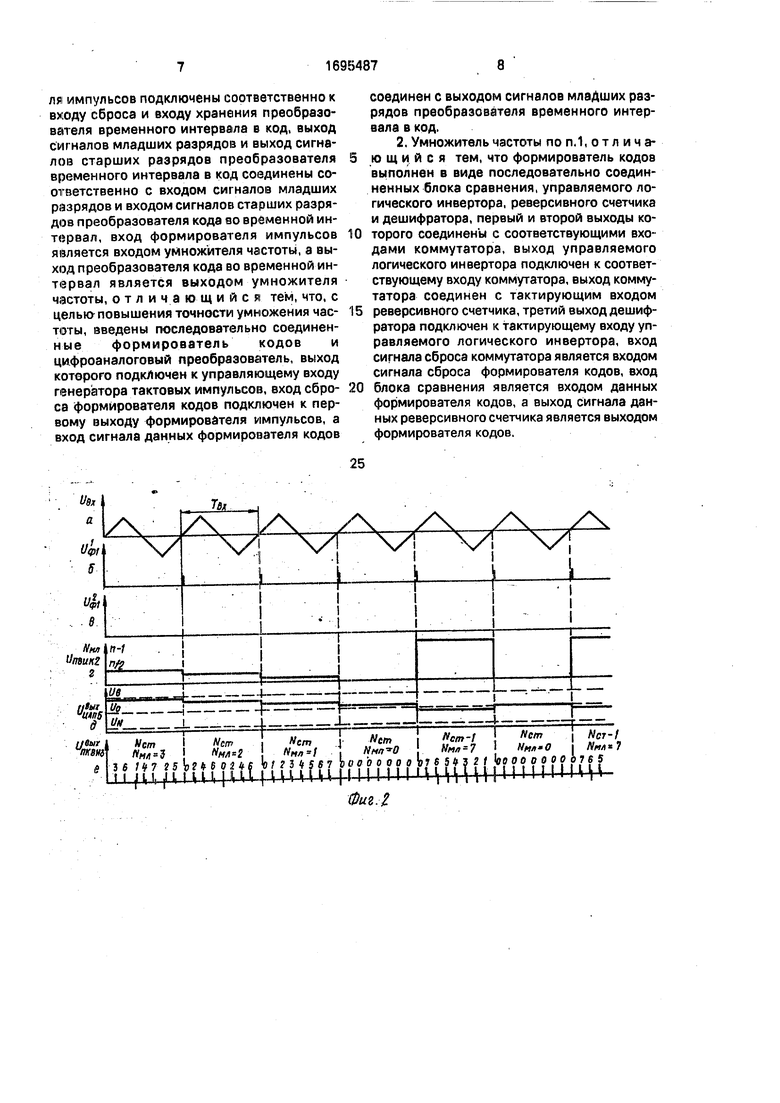

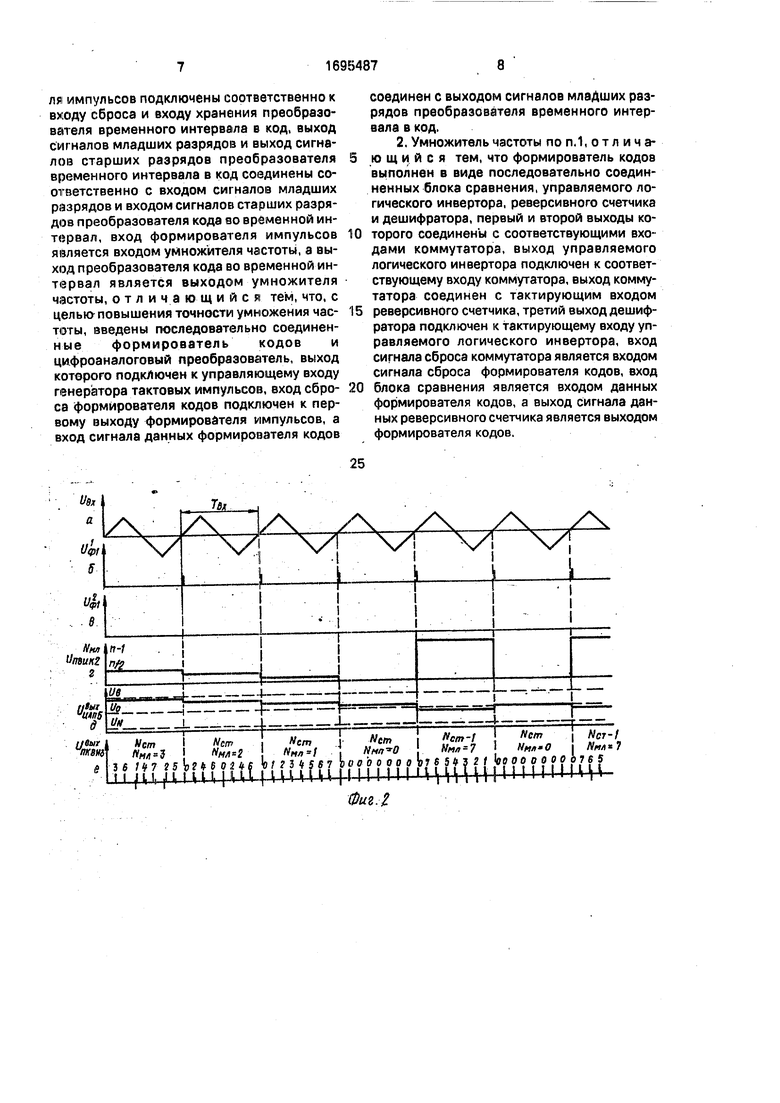

На фиг.1 приведена структурная электрическая схема умножителя частоты; на фиг.2 - временные диаграммы, иллюстрирующие работу умножителя частоты; на фиг.З - функциональная зависимость, поясняющая принцип регулирования частоты при подстройке.

Умножитель частоты содержит формирователь 1 импульсов, преобразователь 2 временного интервала в код, преобразователь 3 кода во временной интервал, генератор 4 тактовых импульсов, цифроаналоговый преобразователь (ЦАП) 5 и формирователь 6 кодов, включающий в себя блок 7 сравнения, управляемый логический инвертор 8, реверсивный счетчик 9, дешифратор 10 и коммутатор 11.

Умножитель частоты работает следующим образом.

При поступлении на вход умножителя частоты входного сигнала с периодом ТВх (см, фиг.2а) на выходах формирователя 1 формируются импульсы с тем же периодом следования, причем импульсы с второго выхода формирователя 1 несколько опережают импульсы с первого выхода (см. фиг. 2б,в).

Эти импульсы поступают соответственно на вход хранения и вход сброса преобразователя 2 временного интервала в код, на тактовый вход которого подается частота заполнения f0 с выхода генератора 4 тактовых импульсов. В конце каждого периода ТВх импульсом блокировки счета с второго выхода формирователя 1 (см. фиг.2в) производится фиксация кода N входного периода в преобразователе 2 временного интервала в код, а затем импульсом с первого выхода формирователя I (см. фиг.2б) осуществляется сброс внутреннего счетчика преобразователя 2, в котором происходит накопление кодового эквивалента N периода входного сигнала

N JLBL n NCT 4-Nr

где n - коэффициент умножения частоты;

NCT старшие разряды кода входного периода;

Ммл - младшие разряды кода входного периода.

При этом

NMyi modnN;

Nc,

где modnN - остаток от деления N на п; - - деление нацело N на п.

Код N с выхода преобразователя 2 временного интервала в код поступает на входы сигналов младших и старших разрядов преобразователя 3, на тактовый вход которого подается частота заполнения f0 с генератора 4. При этом сигналы младших

разрядов Ммл кода N поступают на вход данных формирователя 6 кодов (см. фиг.2г), вход сброса которого тактируется сигналом с первого выхода формирователя 1. Формирователь 6 по этому сигналу формирует управляемый код для цифроаналогового преобразователя 5 (фиг.2д), выходное напряжение которого изменяет частоту f0 генератора 4 таким образом, чтобы свести к минимуму остаток от деления кода N периода входного сигнала на коэффициент умножения частоты п, что равнозначно сведению кода Ымл к нулю или к гН.

На фиг.З, демонстрирующей специфику регулирования частоты тактовых импульсов

умножителя частоты с целью повышения точности умножения, сплошной линией изображена зависимость кода младших разря- дов периода входного сигнала от управляющего сигнала на выходе ЦАП 5 на

соответствующем входе генератора 4 при постоянной частоте входного сигнала умножителя частоты fax. Область регулирования в общем случае ограничена снизу и сверху уровнями напряжений UH и UB, за пределами которых может проявляться повышенная нестабильность или нелинейность регулировочной характеристики или же выход за пределы которых является просто нецелесообразным. Нижняя граница регулирования

ЦАП 5 задается в нем смещением выходного напряжения на величину UH. Верхняя граница при полном использовании разрядности ЦАП 5 определяется величиной его опорного напряжения Don из выражения UB UH + Don.

С ростом управляющего напряжения растет частота тактовых импульсов генератора 4, а вместе с ней растет и величина кода N периода входного сигнала. Периодический характер зависимости кода младших разрядов

от управляющего .напряжения на выходе ЦАП 5 объясняется ограниченностью изменения кода младших разрядов величиной коэффициента умножения п. По достижении этого значения следует перенос единицы «

старшие разряды и обнуление младших разрядов, Таким образом, коды младших разрядов, близкие к нулю и к п, равнозначны по величине вносимой погрешности. В обоих случаях она одинаково мала, но имеет разные знаки, а вертикальные линии графика зависимости характеризуют состояние отсутствия погрешности умножителя частоты. Суть алгоритма устранения погрешности умножителя частоты состоит в том, что формирователь 6 кодов путем изменения частоты генератора 4 тактовых импульсов осуществляет минимизацию остатка от деления кода N на коэффициент умножения п,

т.е. пр 1 Ммл 2 осуществляется увеличение с татка до п-1, а при -уменьшение Ымл до нуля. В приведенных на фиг.2г,д,е временных диаграммах коэффициент умножения принят для определенности равным 8. При этом, как видно из фиг.2

гид, первоначальный код ММл 3 Ј сводится к минимуму за три периода входной частоты. При этом код на выходе формирователя 6 кодов и, соответственно, управляющее напряжение на выходе ЦАП 15, устанавливается на уровне U0 (см. фиг.2д), что соответствует установившемуся режиму работы умножителя, т.е. вертикальному участку зависимости на фиг.З.

Для случая, когда при первоначальном

состоянии Ммл 1 процесс регулирования аналогичен: формирователь б посредством ЦАП 5 сводит управляющее напряжение из нижней части рабочей области к значению Do. При этом погрешность неравномерности следования выходных импульсов умножителя частоты, связанная с остатком Ымл. становится минимальной (см. фиг.2 е, на ксторой короткими штрихами обозначены положения импульсов на выходе идеального умножителя частоты).

В режиме устранения погрешности умножителя частоты блоки, составляющие формирователь 6, взаимодействуют следующим образом.

Импульсы с первого выхода формирователя 1 поступают на вход сброса формирователя 6 и через коммутатор 11 попадают на тактирующий вход реверсивного счетчика 9, каждый раз изменяя его состояние на единицу. Направление процесса регулирования определяется выходным сигналом блока 7 сравнения, который при превышении остатком Ымл кода Ј формирует команду сложения, а при Ымл -х - команду вычитания.

Максимальная величина коэффициента

п в блоке 7 ограничена разрядностью этого блока. Код с выхода реверсивного счетчика 9 поступает в дешифратор 10, который предназначен для идентификации нижней и верхней границ области регулирования

выходного напряжения ЦАП 5, а также случая, когда напряжение на выходе ЦАП 5 находится внутри области регулирования (см. фиг.З). Если напряжение на выходе ЦАП 5 находится внутри рабочей области, то управляемый логический инвертор 8 формирует соответствующий сигнал направления счета для реверсивного счетчика 9, а импульсы с выхода формирователя 1 через коммутатор 11 поступают на тактирующий

вход счетчика 9. Если напряжение на выходе ЦАП 5 достигает границ области, то по сигналам на соответствующих выходах дешифратора 10 управляемый логический инвертор 8 меняет направление счета

реверсивного счетчика 9 на противоположное и процесс регулирования продолжается до достижения одного из вертикальных участков зависимости, показанной на фиг.З, что соответствует состоянию отсутствия погрешности.

Код с выхода реверсивного счетчика 9 поступает на вход ЦАП 5, выходное напряжение которого регулирует частоту генератора 4 тактовых импульсов в направлении

минимизации погрешности умножителя.

Выполнение умножителя частоты по структурной схеме, показанной на фиг.1, позволяет осуществить минимизацию погрешности умножения частоты с максимальным

быстродействием в пределах заданных границ области регулирования при сохранении устойчивости процесса регулирования и отсутствии сбоев вблизи граничных зон. При этом максимальная погрешность по сравнению с прототипом снижается в п раз.

Кроме того, из-за малости необходимой расстройки генератора 4 тактовых импульсов становится возможным использование для его реализации высокостабильных кварцевых генераторов.

Формула изобретения 1, Умножитель частоты, содержащий формирователь импульсов, преобразователь временного интервала в код, преобразователь кода во временной интервал и генератор тактовых импульсов, выход которого соединен с тактовыми входами преобразователя временного интервала в код и преобразователя кода во временной интервал, первый и второй выходы формирователя импульсов подключены соответственно к входу сброса и входу хранения преобразователя временного интервала в код, выход сигналов младших разрядов и выход сигналов старших разрядов преобразователя временного интервала в код соединены соответственно с входом сигналов младших разрядов и входом сигналов старших разрядов преобразователя кода во временной интервал, вход формирователя импульсов является входом умножителя частоты, а выход преобразователя кода во временной интервал является выходом умножителя частоты, отличающийся тем, что, с целью повышения точности умножения частоты, введены последовательно соединенные формирователь кодов и цифроаналоговый преобразователь, выход которого подключен к управляющему входу генератора тактовых импульсов, вход сброса формирователя кодов подключен к первому выходу формирователя импульсов, а вход сигнала данных формирователя кодов

0

5

0

соединен с выходом сигналов младших разрядов преобразователя временного интервала в код.

2. Умножитель частоты по п. 1, о т л и ч а- ю щ и и с я тем, что формирователь кодов выполнен в виде последовательно соедин- ненных блока сравнения, управляемого логического инвертора, реверсивного счетчика и дешифратора, первый и второй выходы которого соединены с соответствующими входами коммутатора, выход управляемого логического инвертора подключен к соответствующему входу коммутатора, выход коммутатора соединен с тактирующим входом реверсивного счетчика, третий выход дешифратора подключен к тактирующему входу управляемого логического инвертора, вход сигнала сброса коммутатора является входом сигнала сброса формирователя кодов, вход блока сравнения является входом данных формирователя кодов, а выход сигнала данных реверсивного счетчика является выходом формирователя кодов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1989 |

|

SU1700742A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Аналого-цифровой фазовращатель | 1988 |

|

SU1584082A1 |

| Умножитель частоты | 1988 |

|

SU1614096A1 |

| Устройство для телеизмерения давления скважинных штанговых насосов | 1990 |

|

SU1711218A1 |

| Умножитель частоты | 1986 |

|

SU1385230A1 |

| Устройство для измерения времени установления выходного напряжения цифроаналоговых преобразователей | 1986 |

|

SU1332530A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1695499A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1986 |

|

SU1513506A2 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1986 |

|

SU1525723A2 |

Изобретение относится к радиотехнике. Цель - повышение точности умножения частоты. Для этого входной сигнал проходит через последовательно соединенные формирователь 1 импульсов, преобразователь 2 временного интервала в код и преобразователь 3 кода во временной интервал, на тактовые входы которых подается сигнал с генератора 4 тактовых импульсов, управляемого напряжением с выхода цифроанало- гового преобразователя 5, вход которого подключен к выходу формирователя 6 кодов, содержащего блок 7 сравнения, на вход которого поступают коды младших разрядов с выхода преобразователя 2, управляющий логический инвертор 8, определяющий направление счета реверсивного счетчика 9, дешифратор 10 и коммутатор 11. Погрешность, связанная с неточностью деления кода периода входного сигнала на коэффициент умножения частоты минимизируется путем регулирования тактовой частоты генератора 4, причем производится двустороннее регулирование этой частоты при помощи реверсивного счетчика 9, дешифратора 10 и коммутатора 11, что позволяет свести остаток от деления к нулю, достигая отсутствие погрешности кратчайшим путем. Коммутатор 11 обеспечивает устойчивость процесса регулирования в пределах рабочей области. Кроме того, из- за малой необходимой расстройки генератора 4, он может быть выполнен в виде высокостабильного кварцевого генератора. 1 з.п. ф-лы, 3 ил. сл с

Фиг. 2

fe.3

| Умножитель частоты | 1978 |

|

SU765818A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-11-30—Публикация

1989-04-25—Подача