1

(21)4362715/24-09

(22)13.Of.88

(46) 23.05.90. Бюл. № 19

(72) Г.Н.Афанасьев, И.В.Волков,

М.П.Игнатьев, В.Я.Порецкий

и В.Н.Федосов

(53) 621.373.42(088.8)

(56) Авторское свидетельство СССР

№1279077, кл. Н 03 В 23/00,15.04.85.

Авторское свидетельство СССР (Г 1133646, кл. Н 03 В 19/00,28.02.83.

О4) ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ (57) Изобретение относится к радиотехнике. Цель изобретения - упрощение . Цифровой синтезатор частот содержит г-р 1 тактовых импульсов, феобразователь 2 код-частота, счетчик 3, преобразователь 4 кодов, ДАЛ 5 и 6, блок 8 программируемой памяти. Цел} достигается путем уменьшения объема прог раммируемой памяти с помощью введенных ДАЛ 7, управляемого, источника 9 опорного напряжения и формирователя 10 кода частоты. 1 з.п. ф-лы, 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Частотный модулятор | 1989 |

|

SU1626320A1 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385238A2 |

| Синтезатор частот | 1989 |

|

SU1730720A1 |

| Цифровой синтезатор изменяющейся частоты | 1982 |

|

SU1107262A1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1356222A1 |

| Цифровой синтезатор частот | 1990 |

|

SU1748251A1 |

Изобретение относится к радиотехнике. Цель изобретения - упрощение устройства. Цифровой синтезатор частот содержит г-р 1 тактовых импульсов, преобразователь 2 код-частота, счетчик 3, преобразователь 4 кодов, ЦАП 5 и 6, блок 8 программируемой памяти. Цель достигается путем уменьшения объема программируемой памяти с помощью введенных ЦАп 7, управляемого источника 9 опорного напряжения и формирователя 10 кода частоты. 1 з.п. ф-лы, 2 ил.

&

i (Л

ел

сг

оэ

Ј

сл

Јъ

Фиг.1

Изобретение относится к радиотехнике и может использоваться в а втома тизированных стендах для формирования сигнала изменяющейся частоты с программируемой амплитудно-частотной характеристикой.

Целью изобретения является упрощение путем уменьшения объема программируемой памяти.

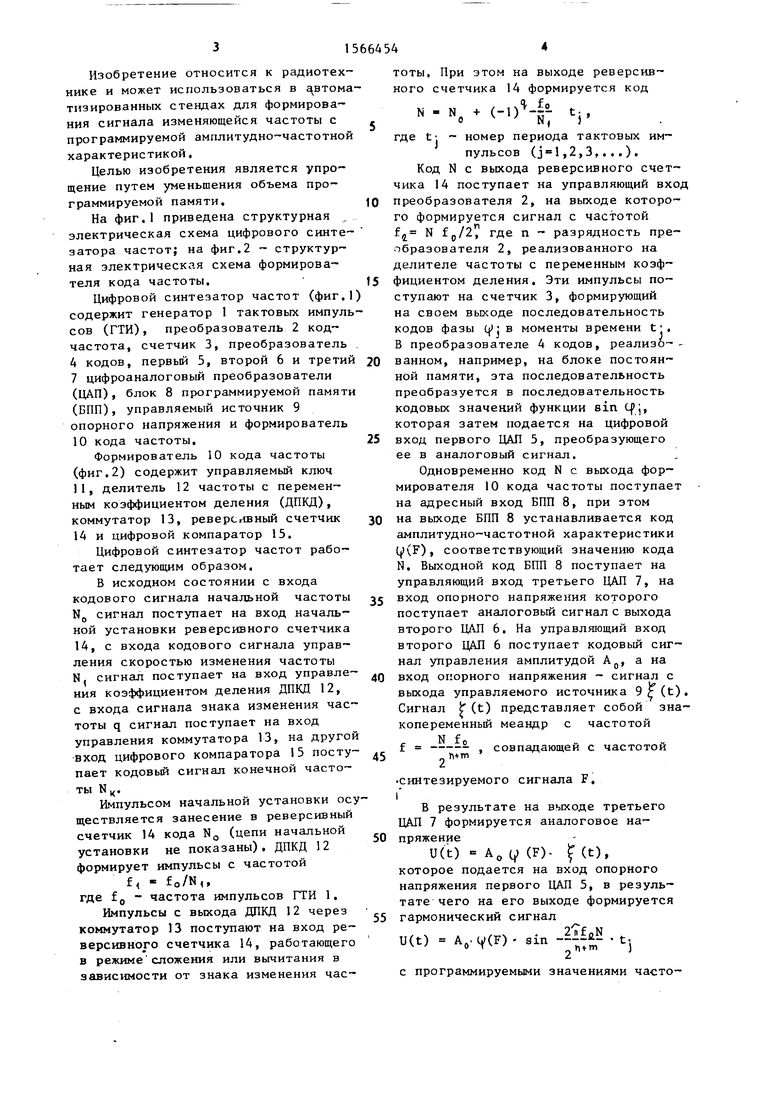

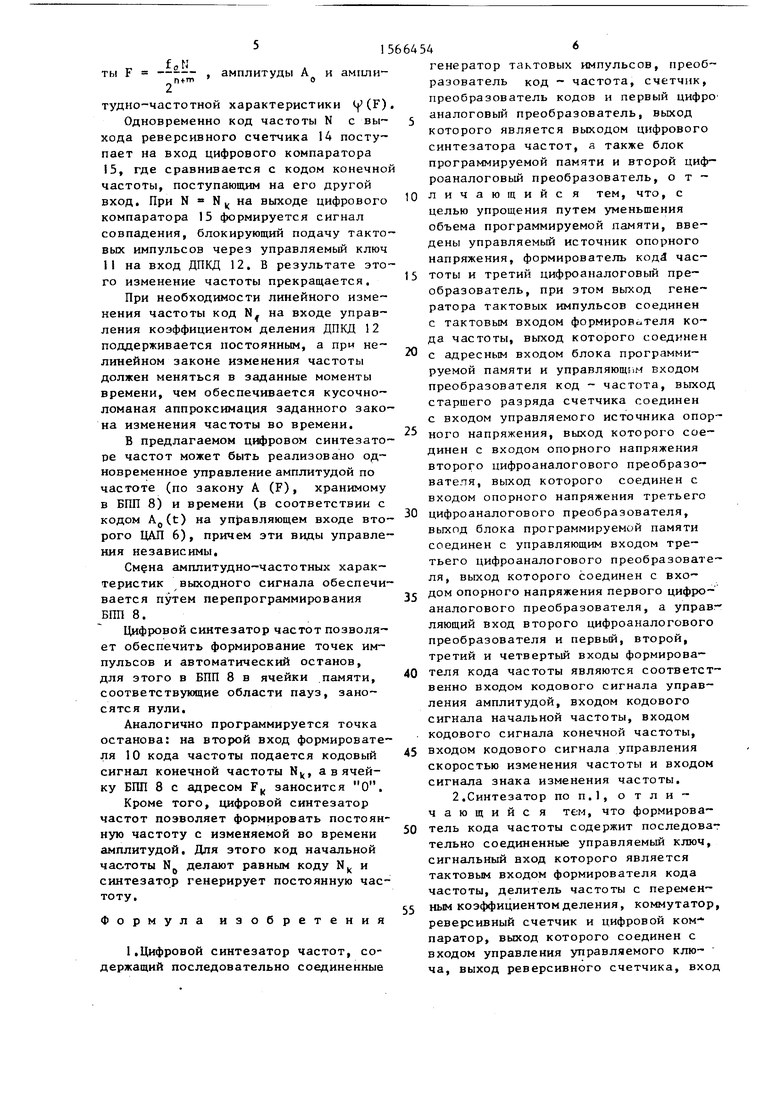

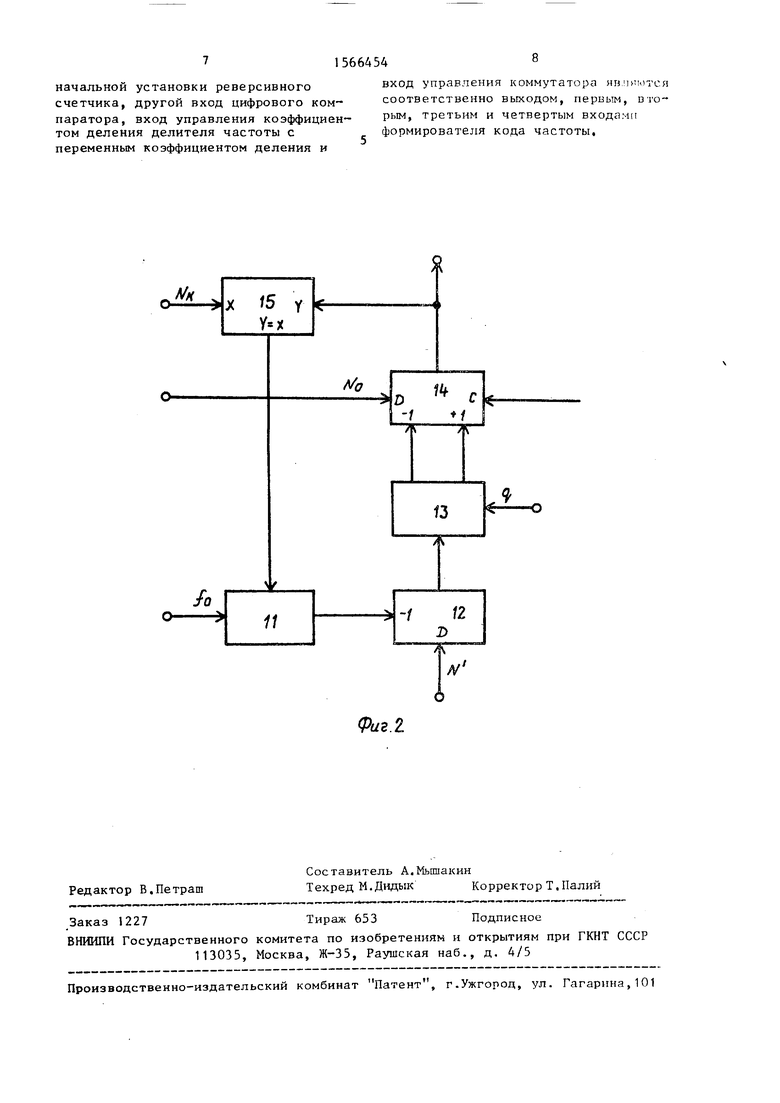

На фиг.1 приведена структурная электрическая схема цифрового синтезатора частот; на фиг.2 - структурная электрическая схема формирователя кода частоты.

Цифровой синтезатор частот (фиг.1 содержит генератор 1 тактовых импульсов (ГТИ), преобразователь 2 код- частота, счетчик 3, преобразователь 4 кодов, первый 5, второй 6 и третий 7 цифроаналоговый преобразователи (ЦАП), блок 8 программируемой памяти (БПП), управляемый источник 9 опорного напряжения и формирователь 10 кода частоты,

Формирователь 10 кода частоты (фиг.2) содержит управляемый ключ 11, делитель 12 частоты с переменным коэффициентом деления (ДПКД), коммутатор 13, реверсивный счетчик 14 и цифровой компаратор 15.

Цифровой синтезатор частот работает следующим образом.

В исходном состоянии с входа кодового сигнала начальной частоты N0 сигнал поступает на вход начальной установки реверсивного счетчика 14, с входа кодового сигнала управления скоростью изменения частоты N, сигнал поступает на вход управле- ния коэффициентом деления ДПКД 12, с входа сигнала знака изменения частоты q сигнал поступает на вход управления коммутатора 13, на другой вход цифрового компаратора 15 посту- пает кодовый сигнал конечной частоты N к.

Импульсом начальной установки осуществляется занесение в реверсивный счетчик 14 кода N0 (цепи начальной установки не показаны). ДПКД 12 формирует импульсы с частотой

f - fo/N,, где f0 - частота импульсов ГТИ 1.

Импульсы с выхода ДПКД 12 через коммутатор 13 поступают на вход реверсивного счетчика 14, работающего в режиме сложения или вычитания в зависимости от знака изменения частоты. При этом на выходе реверсивного счетчика 14 формируется код

И-. ( V где t - номер периода тактовых импульсов (,2,3,...).

Код N с выхода реверсивного счетчика 14 поступает на управляющий вх преобразователя 2, на выходе которого формируется сигнал с частотой f4 N f0/2 где п - разрядность преобразователя 2, реализованного на делителе частоты с переменным коэффициентом деления. Эти импульсы поступают на счетчик 3, формирующий на своем выходе последовательность кодов фазы ($ - в моменты времени t . В преобразователе 4 кодов, реализованном, например, на блоке постоянной памяти, эта последовательность преобразуется в последовательность кодовых значений функции sin , которая затем подается на цифровой вход первого ЦАП 5, преобразующего ее в аналоговый сигнал.

Одновременно код N г выхода формирователя 10 кода частоты поступае на адресный вход БПП 8, при этом на выходе БПП 8 устанавливается код амплитудно-частотной характеристики ty(F), соответствующий значению кода N. Выходной код БПП 8 поступает на управляющий вход третьего ЦАП 7, на вход опорного напряжения которого поступает аналоговый сигнал с выхода второго ЦАП 6. На управляющий вход второго ЦАП 6 поступает кодовый сигнал управления амплитудой А0, а на вход опорного напряжения - сигнал с выхода управляемого источника 9 t (t) Сигнал t (t) представляет собой знакопеременный меандр с частотой

f , совпадающей с частотой

2tnm

синтезируемого сигнала F. I

В результате на выходе третьего ЦДЛ 7 формируется аналоговое напряжение

U(t) А0 (F)- f (t), которое подается на вход опорного напряжения первого ЦАП 5, в результате чего на его выходе формируется гармонический сигнал

U(t) Ae.f(F). sin - 7l- thtm

)

с программируемыми значениями частоты F

f«N

, амплитуды А и амплиrum

тудно-частотной характеристики (F).

Одновременно код частоты N с вы- хода реверсивного счетчика 14 посту™ пает на вход цифрового компаратора 15, где сравнивается с кодом конечной частоты, поступающим на его другой вход. При N N к на выходе цифрового компаратора 15 формируется сигнал совпадения, блокирующий подачу тактовых импульсов через управляемый ключ 11 на вход ДПКД 12. В результате это

го изменение частоты прекращается.

При необходимости линейного изменения частоты код N на входе управления коэффициентом деления ДПКД 12 поддерживается постоянным, а при нелинейном законе изменения частоты должен меняться в заданные моменты времени, чем обеспечивается кусочно- ломаная аппроксимация заданного закона изменения частоты во времени.

В предлагаемом цифровом синтезаторе частот может быть реализовано одновременное управление амплитудой по частоте (по закону A (F), хранимому в БПП 8) и времени (в соответствии с кодом A0(t) на управляющем входе второго ЦАП 6), причем эти виды управления независимы.

Смена амплитудно-частотных характеристик выходного сигнала обеспечивается путем перепрограммирования БПП 8.

Цифровой синтезатор частот позволяет обеспечить формирование точек импульсов и автоматический останов, для этого в БПП 8 в ячейки памяти, соответствующие области пауз, заносятся нули.

Аналогично программируется точка останова: на второй вход формирователя 10 кода частоты подается кодовый сигнал конечной частоты Nk, а в ячейку БПП 8 с адресом Fk заносится О.

Кроме того, цифровой синтезатор частот позволяет формировать постоянную частоту с изменяемой во времени амплитудой. Для этого код начальной частоты NO делают равным коду Nk и синтезатор генерирует постоянную частоту.

Формула изобретения

(.Цифровой синтезатор частот, содержащий последовательно соединенные

5 Ю 15

20

30

,

35

45

50546

генератор тактовых импульсов, преобразователь код - частота, счетчик, преобразователь кодов и первый цифро аналоговый преобразователь, выход которого является выходом цифрового синтезатора частот, а также блок программируемой памяти и второй циф- роаналоговый преобразователь, отличающийся тем, что, с целью упрощения путем уменьшения объема программируемой памяти, введены управляемый источник опорного напряжения, формирователь кода частоты и третий цифроаналоговый преобразователь, при этом выход генератора тактовых импульсов соединен с тактовым входом формирователя кода частоты, выход которого соединен с адресным входом блока программируемой памяти и управляющим входом преобразователя код - частота, выход старшего разряда счетчика соединен с входом управляемого источника опорного напряжения, выход которого соединен с входом опорного напряжения второго цифроаналогового преобразователя, выход которого соединен с входом опорного напряжения третьего цифроаналогового преобразователя, выход блока программируемой памяти соединен с управляющим входом третьего цифроаналогового преобразователя, выход которого соединен с входом опорного напряжения первого цифро- аналогового преобразователя, а управляющий вход второго цифроаналогового преобразователя и первый, второй, третий и четвертый входы формирователя кода частоты являются соответственно входом кодового сигнала управления амплитудой, входом кодового сигнала начальной частоты, входом кодового сигнала конечной частоты, входом кодового сигнала управления скоростью изменения частоты и входом сигнала знака изменения частоты.

начальной установки реверсивного счетчика, другой вход цифрового компаратора, вход управления коэффициентом деления делителя частоты с переменным коэффициентом деления и

X 15 у

А/О

/о

о

11

вход управления коммутатора нвчг отся соответственно выходом, первым, вторым, третьим и четвертым входами формирователя кода частоты.

S

-1 /

f3

Ч

-/ 12

Фиг.г

Авторы

Даты

1990-05-23—Публикация

1988-01-13—Подача