гЗШ

с/

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Дисплейный процессор | 1981 |

|

SU1292031A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для отображения информации | 1978 |

|

SU746629A1 |

| Устройство для записи цифровой информации | 1988 |

|

SU1597904A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1275520A1 |

| Преобразователь код-временной интервал | 1986 |

|

SU1401589A1 |

| Устройство для управления замещением информации | 1975 |

|

SU651413A1 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Цифровой рекурсивный фильтр | 1988 |

|

SU1578720A1 |

| Устройство для контроля постоянной памяти | 1982 |

|

SU1083235A1 |

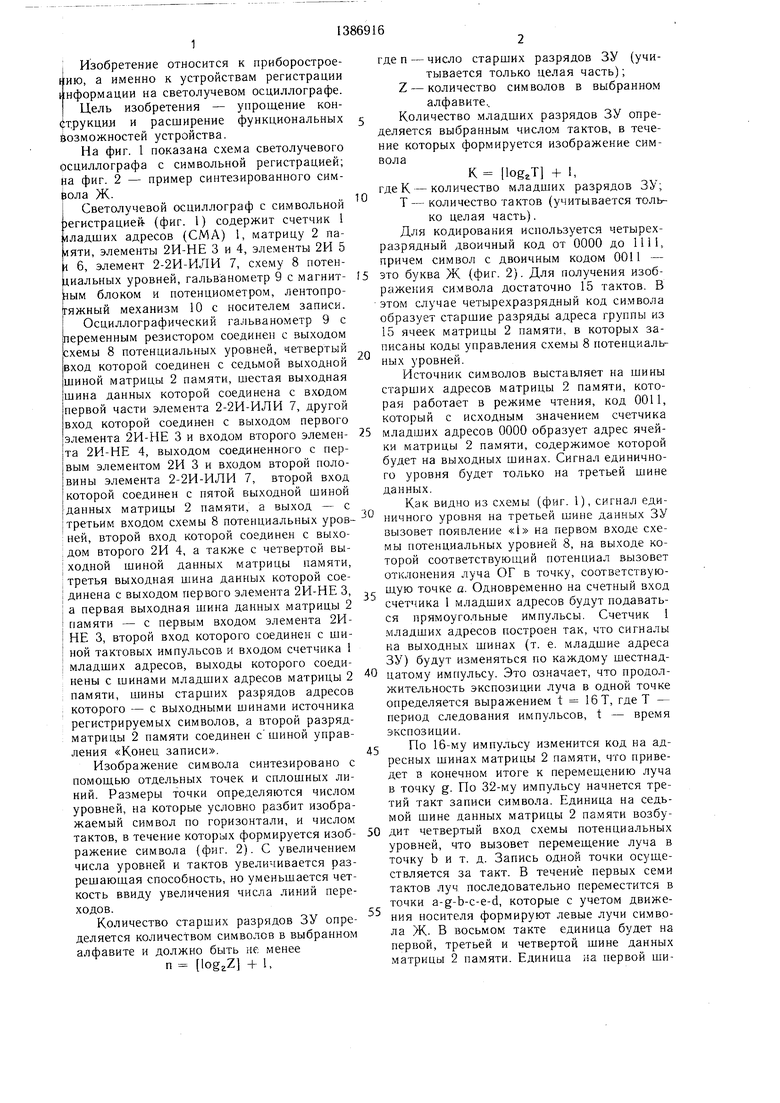

Изобретение относится к области приборостроения, в частности к устройства. регистрации информации на светолучевом осциллографе. Изобретение позволяет упростить конструкцию и расширить функциональные возможности предложенного осциллографа с си.мвольной регистрацией. На чертеже показаны счетчик 1 младших разрядов, .матрица 2 памяти, элементы 2Й-НЕ 3 и 4, элементы И 5 и 6, элемент 2-2И-ИЛИ 7, блок 8 потенциальны.х уровней, гальванометр 9 с магнитным блоко.м и потенцио.метром и лентопротяжный механизм 10 с носителем записи. В предложенном осциллографе обеспечивается возможность формирования изображения символов с различными геометри- чески.ми размерами. При этом изображаемые си.мволы определяются кодами, записанными в матрицу 2 памяти. Изображение каждого символа синтезируется с помощью отдельных точек и сплошных линий. 2 ил. «э

/11

/)/Г

т

„ конец записи

&1

д

о: а а

Изобретение относится к приборостроению, а именно к устройствам регистрации 1:нформации на светолучевом осциллографе.

Цель изобретения - упрощение кон- (;:т.рукцим и расширение функциональных 1 озможностей устройства.

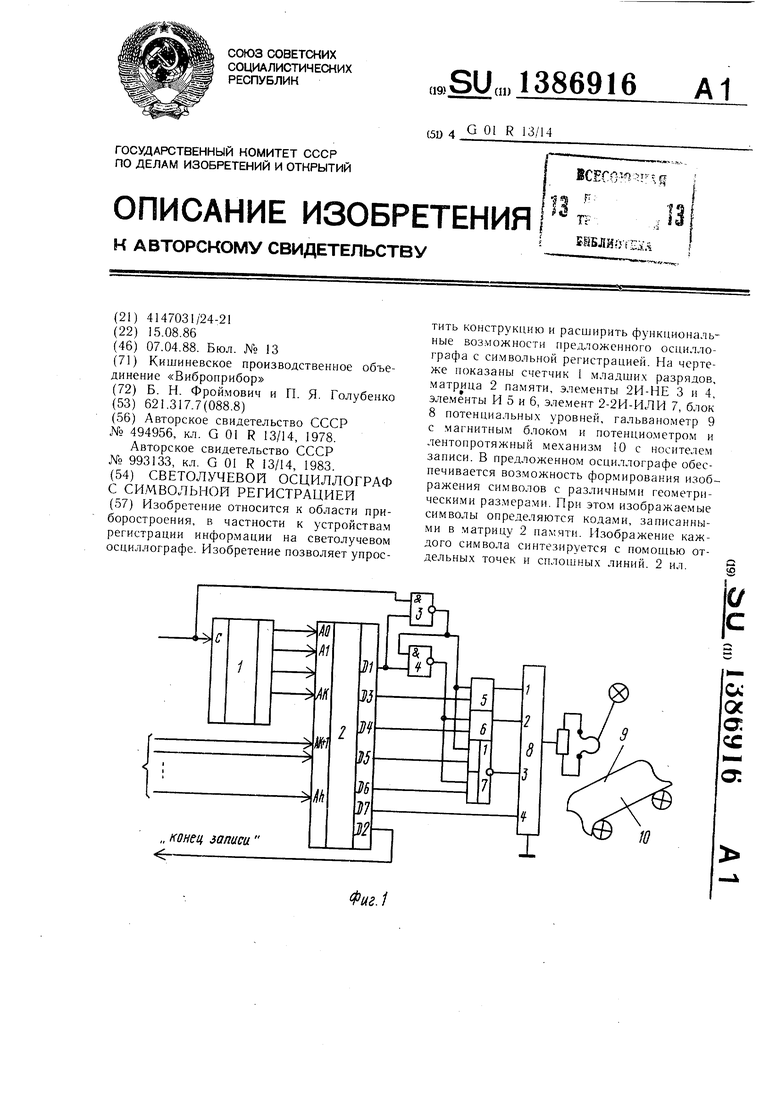

На фиг. 1 показана схема светолучевого осциллографа с символьной регистрацией; (la фиг. 2 - пример синтезированного сим- 1юла Ж.

Светолучевой осциллограф с символьной )егистрацией- (фиг. 1) содержит счетчик 1 лладших адресов (СМА) 1, матрицу 2 па- пяти, элементы 2И-НЕ 3 и 4, элементы 2И 5 - 6, элемент 2-2И-ИЛИ 7, схему 8 потен10

где п - число старших разрядов ЗУ (учитывается только целая часть); Z - количество символов в выбранном

алфавите..

Количество младших разрядов ЗУ определяется выбранным числом тактов, в течение которых формируется изображение символа

К + ,

где К - количество младших разрядов ЗУ; Т - количество тактов (учитывается только целая часть).

Для кодирования используется четырехразрядный двоичный код от 0000 до 1111, причем символ с двоичным кодом ООП -

циальных уровней, гальванометр 9 с магнит-15 это буква Ж (фиг. 2). Для получения изоб- ным блоком и потенциометром, лентопро- ражения символа достаточно 15 тактов. В яжный механизм 10 с носителем записи.этом случае четырехразрядный код символа

Осциллографический гальвано.метр 9 с образует старшие разряды адреса группы из переменным резистором соединен с выходом15 ячеек матрицы 2 памяти, в которых захемь 8 потенциальных уровней, четвертый писаны коды управления схемы 8 потенциальвход которой соединен с седьмой выходной - лт,ппиой шиной матрицы 2 памяти, шестая выходная шина данных которой соединена с входом

первой части элемента 2-2И-ИЛИ 7, другой вход которой соединен с выходом первого

ных уровней.

Источник символов выставляет на шины старших адресов матрицы 2 памяти, которая работает в режиме чтения, код ООП, который с исходным значением счетчика

элемента 2И-НЕ 3 и входом второго элемен- 25 младших адресов 0000 образует адрес ячейки матрицы 2 памяти, содержимое которой будет на выходных шинах. Сигнал единичного уровня будет только на третьей шине данных.

Как видно из схемы (фиг. I), сигнал единичного уровня на третьей шине данных ЗУ вызовет появление «1 на первом входе схемы потенциальных уровней 8, на выходе которой соответствующий потенциал вызовет отклонения луча ОГ в точку, соответствуюта 2И-НЕ 4, выходом соединенного с первым элементом 2И 3 и входом второй половины элемента 2-2И-ИЛИ 7, второй вход которой соединен с пятой выходной шиной данных матрицы 2 памяти, а выход - с третьим входом схемы 8 потенциальных уровней, второй вход которой соединен с выходом второго 2И 4, а также с четвертой вы- Iходной шиной данных матрицы памяти, третья выходная шина данных которой сое30

I динена с выходом первого элемента 2И-НЕ 3, Шую точке а. Одновременно на счетный вход

а первая выходная шина данных матрицы 2 счетчика 1 младших адресов будут подаватьI памяти - с первым входом элемента 2И-ся прямоугольные импульсы. Счетчик 1

I НЕ 3, второй вход которого соединен с ши-.младших адресов построен так, что сигналы

I ной тактовых импульсов и входом счетчика 1на выходных шинах (т. е. младшие адреса

I младших адресов, выходы которого соеди-ЗУ) будут изменяться по каждому шестнаднены с шинами младших адресов матрицы 2 цатому импульсу. Это означает, что продолпамяти, шины старших разрядов адресов которого - с выходными шинами источника регистрируемых символов, а второй разряд- матрицы 2 памяти соединен с шиной управления «Конец записи.

Изображение символа синтезировано с помощью отдельных точек и сплошных линий. Размеры точки определяются числом уровней, на которые условно разбит изображаемый символ по горизонтали, и числом

45

жительность экспозиции луча в одной точке определяется выражением t 16Т, где Т - период следования импульсов, t - время экспозиции.

По 16-му импульсу изменится код на адресных шинах матрицы 2 памяти, что приведет в конечном итоге к перемещению луча

в точку g. По 32-му импульсу начнется третий такт записи символа. Единица на седьмой шине данных матрицы 2 памяти возбутактов, в течение которых формируется изоб- 50 дит четвертый вход схемы потенциальных ражение символа (фиг. 2). С увеличением уровней, что вызовет перемещение луча в

точку b и т. д. Запись одной точки осуществляется за такт. В течение первых семи

числа уровней и тактов увеличивается раз- решаюшая способность, но уменьшается четкость ввиду увеличения числа линий переходов.

тактов луч последовательно переместится в точки a-g-b-c-e-d, которые с учетом движеКоличество старших разрядов ЗУ опре- ния носителя формируют левые лучи симвр- деляется количеством символов в выбранном ла Ж. В восьмом такте единица будет на

первой

алфавите и должно быть не менее п +1,

третьей и четвертой шине данных матрицы 2 памяти. Единица на первой ши

где п - число старших разрядов ЗУ (учитывается только целая часть); Z - количество символов в выбранном

алфавите..

Количество младших разрядов ЗУ определяется выбранным числом тактов, в течение которых формируется изображение символа

К + ,

где К - количество младших разрядов ЗУ; Т - количество тактов (учитывается только целая часть).

Для кодирования используется четырехразрядный двоичный код от 0000 до 1111, причем символ с двоичным кодом ООП -

писаны коды управления схемы 8 потенциаль - лт,ппиой

ных уровней.

Источник символов выставляет на шины старших адресов матрицы 2 памяти, которая работает в режиме чтения, код ООП, который с исходным значением счетчика

45

жительность экспозиции луча в одной точке определяется выражением t 16Т, где Т - период следования импульсов, t - время экспозиции.

По 16-му импульсу изменится код на адресных шинах матрицы 2 памяти, что приведет в конечном итоге к перемещению луча

тактов луч последовательно переместится в точки a-g-b-c-e-d, которые с учетом движепервой

третьей и четвертой шине данных матрицы 2 памяти. Единица на первой шине данных матрицы 2 памяти разрешит прохождение прямоугольных импульсов через элементы 2И-НЕ 3 и 4, причем, когда на выходе первого элемента 2И-НЕ 3 будет присутствовать единица, на выходе второго элемента 2И-НЕ 4 будет ноль, и наоборот.

На выходах схемы 8 потенциальных уровней попеременно восемь раз в течение такта будет появляться единица, что приведет к перемещению луча между точками а и g восемь раз за такт, а на носителе останется след в виде прямой линии. В последующие семь тактов будет сформировано изображение правых лучей символа Ж. В щестнадца10

дом схемы потенциальных уровней, отличающийся тем, что, с целью упрощения конструкции и расширения функциональных воз- можносте-й, он содержит счетчик младщих разрядов, матрицу памяти и два элемента 2И-НЕ, причем четвертый вход схемы потенциальных уровней соединен с седьмым выходом матрицы памяти, шестой выход которой соединен с первым входом элемента 2-2И-ИЛИ, четвертый вход которого соединен с выходом первого элемента 2И-НЕ, входом первого элемента 2И и входом второго элемента 2И-НЕ, выход которого соединен с одним из входов второго элемента 2И и вторым входом элемента 2-2И-ИЛИ,

том такте единица будет только на второй 15третий вход которого соединен с пятым вышине матрицы 2 памяти, которая соединенаходом матрицы памяти, а выход соединен с с шиной «Конец записи. Использование это-третьим входом схемы потенциальных уров- го сигнала позволяет формировать изобра-ней, второй вход которой соединен с выхо- жение символов с различными геометричес-дом второго элемента 2И, второй вход кото20

кими размерами за разное число тактов. При этом изображаемые символы определяются кодами, записанными в матрицу 2 памяти.

. Формула изобретения

Светолучевой осциллограф с символьной 25 регистрацией, содержащий осциллографи- ческий гальванометр, лентопротяжный механизм, схему потенциальных уровней, два логических элемента 2И и логический элерого соединен с четвертым выходом матрицы памяти, третий выход которой соединен с вторым входом первого элемента 2И, а первый выход матрицы памяти соединен с первыми входами элементов 2И-НЕ, второй вход первого элемента 2И-НЕ соединен с щиной тактовых импульсов и входом счетчика младших адресов, выходы которого соединены с входами младщих адресов матрицы памяти, входы старших адресов которой соединены с шиной регистрируемых символов, а второй

рого соединен с четвертым выходом матрицы памяти, третий выход которой соединен с вторым входом первого элемента 2И, а первый выход матрицы памяти соединен с первыми входами элементов 2И-НЕ, второй вход первого элемента 2И-НЕ соединен с щиной тактовых импульсов и входом счетчика младших адресов, выходы которого соединены с входами младщих адресов матрицы памяти, входы старших адресов которой соединены с шиной регистрируемых символов, а второй

мент 2-2И-ИЛИ, причем вход осциллогра- выход матрицы памяти соединен с шиной ко- фического гальванометра соединен с выхо- нец записи.

дом схемы потенциальных уровней, отличающийся тем, что, с целью упрощения конструкции и расширения функциональных воз- можносте-й, он содержит счетчик младщих разрядов, матрицу памяти и два элемента 2И-НЕ, причем четвертый вход схемы потенциальных уровней соединен с седьмым выходом матрицы памяти, шестой выход которой соединен с первым входом элемента 2-2И-ИЛИ, четвертый вход которого соединен с выходом первого элемента 2И-НЕ, входом первого элемента 2И и входом второго элемента 2И-НЕ, выход которого соединен с одним из входов второго элемента 2И и вторым входом элемента 2-2И-ИЛИ,

5третий вход которого соединен с пятым выходом матрицы памяти, а выход соединен с третьим входом схемы потенциальных уров- ней, второй вход которой соединен с выхо- дом второго элемента 2И, второй вход кото

рого соединен с четвертым выходом матрицы памяти, третий выход которой соединен с вторым входом первого элемента 2И, а первый выход матрицы памяти соединен с первыми входами элементов 2И-НЕ, второй вход первого элемента 2И-НЕ соединен с щиной тактовых импульсов и входом счетчика младших адресов, выходы которого соединены с входами младщих адресов матрицы памяти, входы старших адресов которой соединены с шиной регистрируемых символов, а второй

выход матрицы памяти соединен с шиной ко- нец записи.

| Светолучевой осциллограф | 1972 |

|

SU494956A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Световой осциллограф с цифровой регистрацией | 1981 |

|

SU993133A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-04-07—Публикация

1986-08-15—Подача