Изобретение относится к области магнитной записи, а именно к устройствам для записи цифровой информации.

Цель изобретения - упрощение устройства.

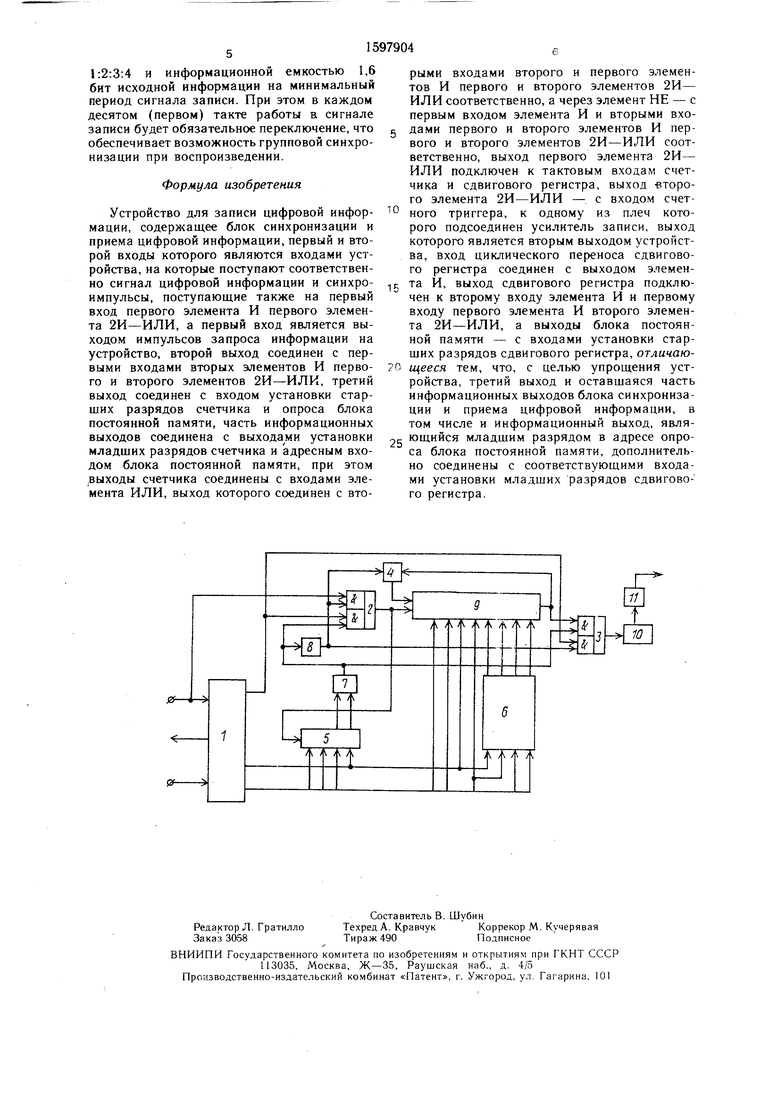

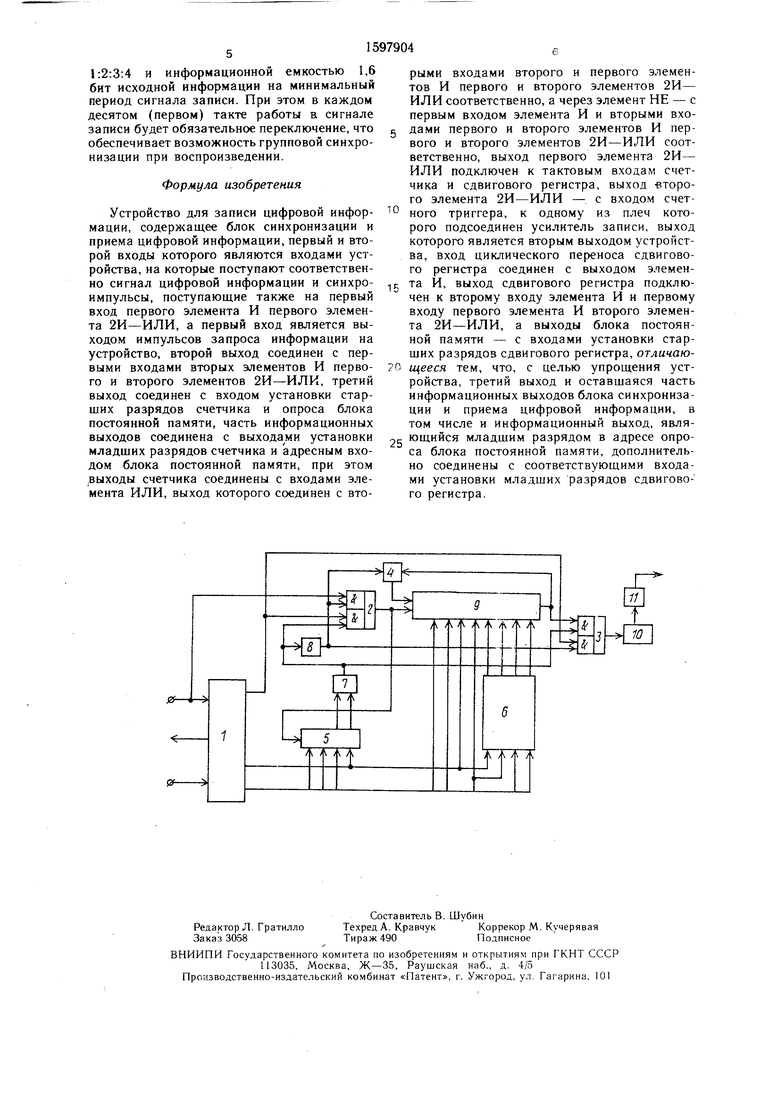

На чертеже приведена функциональная схема устройства для записи цифровой информации.

Устройство для записи цифровой информации содержит блок 1 синхронизации и приема цифровой информации, первый и второй входы которого являются входами устройства, на которые поступают соответственно сигнал цифровой информации и синхроимпульсы, поступающие также на первый вход первого элемента И первого элемента 2И-ИЛИ-2, а первый выход соединен с первыми входами второго элемента И первого 2 и второго 3 элементов 2И-ИЛИ, третий выход соединен с входом установки старших разрядов счетчика 5 и опроса блока 6 постоянной памяти, часть информационных выходов соединена с входами установки.млад- ших разрядов счетчика 5 и адресным входом блока о постоянной памяти, при этом выходы счетчика 5 соединены с входами элемента ИЛИ 7, выход которого соединен с вторыми входами второй и первой схем И первого и второго элементов 2И-ИЛИ 2 и 3 соответственно, а через элемент НЕ 8 - с первым входом элемента И 4 и вторыми входами первого и второго элементов И, первого 2 и второго 3 элементов 2И-ИЛИ соответственно, кроме того, выход первого элемента 2И-ИЛИ подключен к тактовым входам счетчика 5 и сдвигового регистра 9, а выход второго элемента 2И-ИЛИ соединен с выходом счетного триггера 10, к одному из плеч которого подсоединен, усилитель 11 записи, выход которого является вторым выходом устройства, вход циклического переноса сдвигового регистра 9 соединен с выходом элемента И 4, выход подключен к второму входу элемента И 4 и первому входу первой схемы и второго элемента 2И-ИЛИ 3, а выход блоков 6 постоянной памяти с входами установки старших разрядов сдвигового регистра 9 и, досл

со

;&

полнительно, третий выход и оставшаяся часть информационных выходов блока 1 синхронизации и приема цифровой информации, в том числе и информационный выход, являющийся младшим разрядом в адрес опроса блока б постоянной памяти, подключены к соответствуюш,им им входам установки младших разрядов сдвигового регистра 9.

Устройство обеспечивает формирование сигнала записи с информационной емкостью 1,6 бит на минимальный период с возможностью осуш,ествления как тактовой, так и групповой самосинхронизации сигнала воспроизведения. Функционально сигнал записи формируется путем разбиения исходной информации на группы по восемь разрядов. Полученные группы подвергаются преобразованию в десятичные кодовые группы, из которых формируют сигнал записи по способу без возврата к нулю. В процессе преобразования сначала по трем из восьми разрядов исходной информации формируют четырехразрядный базовый код, к которому добавляют значения трех разрядов преобразуемого кода, включая в их число один из в начале использованных разрядов и приписывая на определенном месте кодовые «О и «1, затем осуществляют циклический сдвиг в соответствии с кодовым значением оставшихся трех разрядов исходной информации, получая в результате девятиразрядный код, из которого формируется сигнал записи.

Синхроимпульсы и сигналы информации, поступающие на входы блока 1 синхронизации и приема цифровой информации, обеспечивают также формирование импульсов тактовой и групповой синхронизации устройства (соответственно второй и третий выходы блока 1 синхронизации и приема цифровой информации) и параллельного восьмиразрядного кода исходной информации, выдаваемого одновременно с импульсом групповой синхронизации.

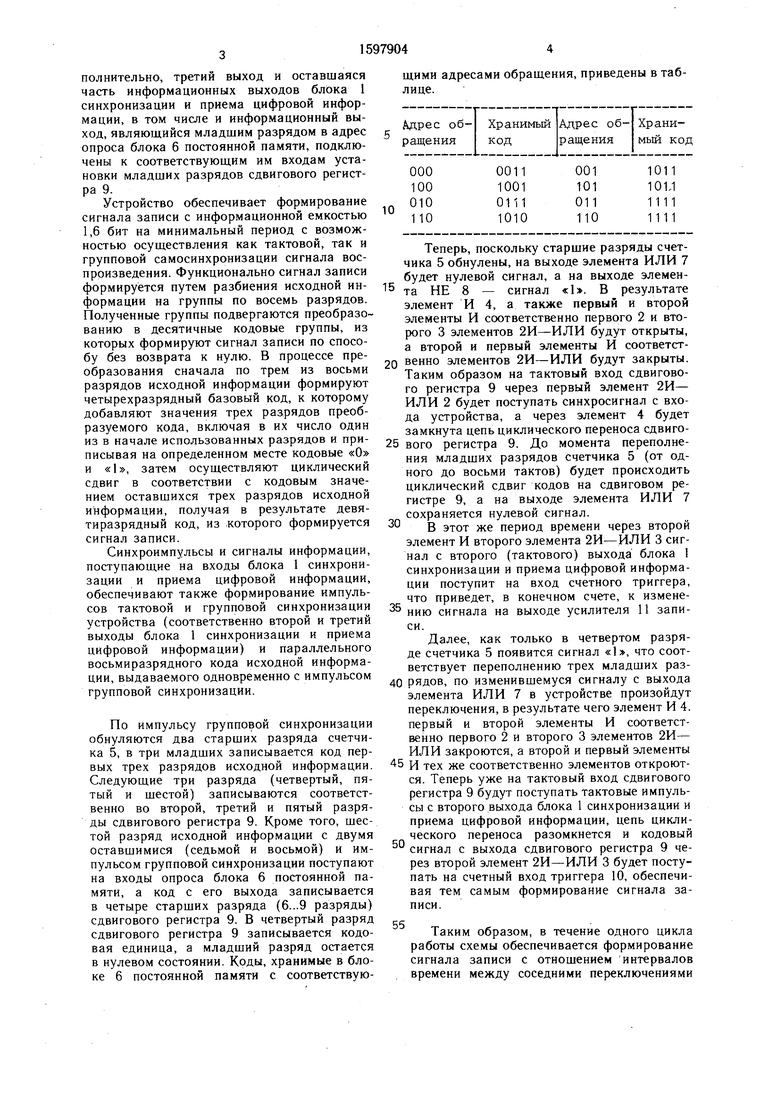

По импульсу групповой синхронизации обнуляются два старших разряда счетчика 5, в три младших записывается код первых трех разрядов исходной информации. Следующие три разряда (четвертый, пятый и шестой) записываются соответственно во второй, третий и пятый разряды сдвигового регистра 9. Кроме того, шестой разряд исходной информации с двумя оставшимися (седьмой и восьмой) и импульсом групповой синхронизации поступают на входы опроса блока 6 постоянной памяти, а код с его выхода записывается в четыре старших разряда (6...9 разряды) сдвигового регистра 9. В четвертый разряд сдвигового регистра 9 записывается кодовая единица, а младший разряд остается в нулевом состоянии. Коды, хранимые в блоке 6 постоянной памяти с соответствующими адресами обращения, приведены в таблице.

Теперь, поскольку старшие разряды счетчика 5 обнулены, на выходе элемента ИЛИ 7 будет нулевой сигнал, а на выходе элемента НЕ 8 - сигнал «Ь. В результате элемент И 4, а также первый и второй элементы И соответственно первого 2 и второго 3 элементов 2И-ИЛИ будут открыты, а второй и первый элементы И соответст- 0 венно элементов 2И-ИЛИ будут закрыты. Таким образом на тактовый вход сдвигового регистра 9 через первый элемент 2И- ИЛИ 2 будет поступать синхросигнал с входа устройства, а через элемент 4 будет замкнута цепь циклического переноса сдвиго- 5 вого регистра 9. До момента переполнения младших разрядов счетчика 5 (от одного до восьми тактов) будет происходить циклический сдвиг кодов на сдвиговом регистре 9, а на выходе элемента ИЛИ 7 сохраняется нулевой сигнал. В этот же период времени через второй элемент И второго элемента 2И-ИЛИ 3 сигнал с второго (тактового) выхода блока 1 синхронизации и приема цифровой информации поступит на вход счетного триггера, что приведет, в конечном счете, к измене- нию сигнала на выходе усилителя 11 записи.

Далее, как только в четвертом разряде счетчика 5 появится сигнал «1, что соответствует переполнению трех младших раз- 40 рядов, по изменившемуся сигналу с выхода элемента ИЛИ 7 в устройстве произойдут переключения, в результате чего элемент И 4. первый и второй элементы И соответственно первого 2 и второго 3 элементов 2И- ИЛИ закроются, а второй и первый элементы 45 И тех же соответственно элементов откроются. Теперь уже на тактовый вход сдвигового регистра 9 будут поступать тактовые импульсы с второго выхода блока 1 синхронизации и приема цифровой информации, цепь циклического переноса разомкнется и кодовый сигнал с выхода сдвигового регистра 9 через второй элемент 2И-ИЛИ 3 будет поступать на счетный вход триггера 10, обеспечивая тем самым формирование сигнала записи.

50

55

Таким образом, в течение одного цикла работы схемы обеспечивается формирование сигнала записи с отношением интервалов времени между соседними переключениями

10

1:2:3:4 и информационной емкостью 1,6 рыми входами второго и первого элемен- бнт исходной информации на минимальный тов И первого и второго элементов 2И- период сигнала записи. При этом в каждомИЛИ соответственно, а через элемент НЕ - с

десятом (первом) такте работы в сигналепервым входом элемента И и вторыми вхозаписи будет обязательное переключение, что g дами первого и второго элементов И пер- обеспечивает возможность групповой синхро-вого и второго элементов 2И-ИЛИ соответственно, выход первого элемента 2И- ИЛИ подключен к тактовым входам счетчика и сдвигового регистра, выход -второго элемента 2И-ИЛИ - с входом счетного триггера, к одному из плеч которого подсоединен усилитель записи, выход которого является вторым выходом устройства, вход циклического переноса сдвигового регистра соединен с выходом элеменио сигнал цифровой информации и синхро- та И, выход сдвигового регистра подклю- импульсы, поступающие также на первый чен к второму входу элемента И и первому

входу первого элемента И второго элемента 2И-ИЛИ, а выходы блока постоянной памяти - с входами установки старших разрядов сдвигового регистра, отличаювыми входами вторых элементов И перво- 20 щееся тем, что, с целью упрощения уст- го и второго элементов 2И-ИЛИ, третийройства, третий выход и оставшаяся часть

информационных выходов блока синхронизации и приема цифровой информации, в том числе и информационный выход, являвыходов соединена с выхода ми установки ющийся младшим разрядом в адресе опро- младщих разрядов счетчика и адресным вхо-са блока постоянной памяти, дополнительдом блока постоянной памяти, при этомно соединены с соответствующими входавыходы счетчика соединены с входами эле-мн установки младших разрядов сдвиговомеита ИЛИ, выход которого соединен с вто-го регистра.

низации при воспроизведении.

Формула изобретения

Устройство для записи цифровой информации, содержащее блок синхронизации и приема цифровой информации, первый и второй входы которого являются входами устройства, на которые поступают соответственвход первого элемента И первого элемента 2И-ИЛИ, а первый вход является выходом импульсов запроса информации на устройство, второй выход соединен с первыход соединен с входом установки старших разрядов счетчика и опроса блока постоянной памяти, часть информационных

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения цифровой информации многодорожечной магнитной записи | 1989 |

|

SU1686475A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1988 |

|

SU1606996A1 |

| Устройство для сопряжения | 1983 |

|

SU1129603A1 |

| Устройство для цифровой магнитной записи | 1990 |

|

SU1764084A1 |

| Устройство коррекции сигнала воспроизведения цифровой магнитной записи | 1988 |

|

SU1554022A1 |

| Устройство для записи цифровой информации | 1984 |

|

SU1157569A1 |

| Устройство обнаружения кодов групповой синхронизации | 1990 |

|

SU1812628A1 |

| Устройство для воспроизведения цифровой информации | 1984 |

|

SU1167645A1 |

| Устройство для поиска информации | 1989 |

|

SU1686464A1 |

| Устройство для формирования сигнала прерывания | 1987 |

|

SU1432522A1 |

Изобретение касается магнитной записи, в частности устройств для записи цифровой информации. Цель - упрощение конструкции. В устройстве перекодированию подвергаются только три из восьми разрядов исходной информации (на два разряда меньше, чем в известном). При этом разрядность кодированной части также уменьшается до 4 разрядов вместо восьми. В результате существенно уменьшается объем постоянной памяти и, следовательно, улучшается эксплуатационные характеристики (потребление электроэнергии, надежность). 1 ил.

| Устройство для записи цифровой информации | 1984 |

|

SU1157569A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Авторское свидетельство СССР № 1485305, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-10-07—Публикация

1988-10-28—Подача