Изобретение относится к вычислительной технике и может быть применено для контроля постоянных запоминающих устройств с импульсным или потенциальным представлением информации.

Известно устройство для контроля постоянных блоков памяти, содержащее блок управления, два последовательно соединенных- п-разрядных двоичных счетчика, коммутатор и эталонный блок памяти 1.

В данном устройстве недостаточна достоверность контроля, так как сравнение информации нз контролируемого и эталонного блоков постоянной памяти происходит по каждому адресу, но только в том случае, когда перед ним считывается информация из ячейки с наибольщим адресом.

Наиболее близким по технической сущности к предлагаемому является устройство для контроля постоянных блоков памяти, содержащее генератор импульсов, выход которого подключен к счетному входу счетчика, первый и второй выходы счетчика подключены к управляющим входам коммутатора, информационные входы первой и второй групп которого подключены соответственно к выходам первой и второй групп счетчика, выход коммутатора подключен к входам эталонного блока памяти и является выходом устройства, выход эталонного блока памяти подключен к первому входу блока сравнения, второй вход которого является входом устройства, выход блока сравнения подключен к входу блока индикации.

При работе генератора устройства младщий 0-й разряд счетчика после каждого импульса меняет свое значение, вследствие чего на выходах элементов 2 И-ИЛИ появляется содержимое п младщих или п старших разрядов счетчика: одно значение п старших разрядов чередуется со всеми 2 значениями п младших разрядов, потом следующее значение п старших разрядов, и т.д. 1-й цикл 0-0-1-0-2-0-3-0-...

-О-()-О- 2-й цикл 0-1 - 1 - 1-2-1-3-1-...

- 1 -() -1- 3-й цикл 0-2-1-2-2-2-3-2-...

-2-()-2-

4-й цикл 0-3-1-3-2-3-3-3-... -3-()-3-

2 цик 0-()-i-()-... - () -() -(2 -1), т.е. всего (2 2) 2 обращений 2.

Однако алгоритм устройства дважды реализует поставленную цель - считать и сравнить информацию по двум любым следующим друг за другом адресам i-j (j-i), что приводит к больщим временным затратам (например, обращение по двум адресам О-1 первого цикла повторяется во втором, 0-2 - в третьем и т.д.).

Цель изобретения - увеличение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для контроля постоянной памяти, содержащее генератор импульсов, выход которого подключен к счетному входу счетчика, первый и второй выходы счетчика подключены к управляющим входам первого коммутатора, одни и другие информационные входы которого подключены соответственно к выходам первой :i второй группы счетчика, эталонный блок памяти, выход которого подключен к одному из входов блока сравнения, другой вход блока сравнения является входом устройства, выход бло5 ка сравнения подключен к входу блока индикации, дополнительно введены дешифратор, второй коммутатор, блоки элементов И, выходы первого из которых подключены к установочным входам счетчика, выходы второго блока элементов И подключены к

0 входам сброса счетчика, одни входы первого и второго блоков элементов И подключены к первому выходу дешифратора и к первому управляющему входу второго коммутатора, второй управляющий вход которого под5 ключен к второму выходу дешифратора, одни и другие информационные входы второго коммутатора подключены соответственно к выходам первого коммутатора и выходам второй группы счетчика, один вход дешифратора подключен к второму выходу счет0 чика, другие входы дешифратора подключены к выходам первой и третьей групп счетчика, другие входы первого и второго блоков элементов И подключены соответственно к входам второй и четвертой групп счетчика, выходы второго коммутатора подключе5 ны к входам эталонного блока памяти и являются выходами устройства, выход блока сравнения подключен к входу генератора.

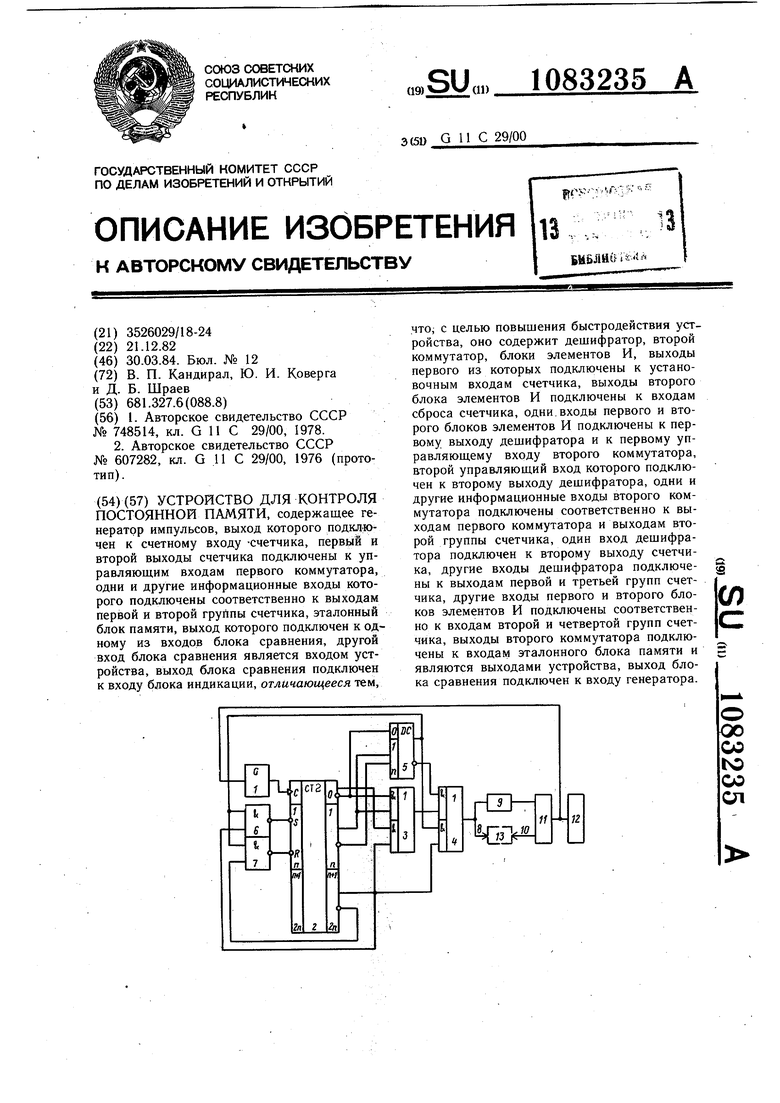

На чертеже показана структурная схе0 ма устройства.

Устройство содержит генератор 1 импульсов, {2п-f 1)-разрядный синхронный двоичный счетчик 2 (где п - количество адресных входов проверяемого блока памяти) , имеющий нулевые и единичные выходы

5 всех разрядов и приоритетные инверсные единичные и нулевые установочные входы п младщих разрядов, коммутаторы 3 и 4, дешифратор 5 (дешифратор начального состояния (п + 1) младщих разрядов с 0-го по 1-й счетчика 2), блоки 6 и 7 элементов И, выходы 8, эталонный блок 9 памяти, входы 10, блок 11 сравнения и блок 12 индикации, контролируемый блок 13 памяти.

В исходном состоянии все разряды счетчика 2 находятся в нулевом состоянии. На

5 нулевом выходе младшего 0-го разряда счетчика 2 разрешаюший, а на единичном - запрещающий уровень сигнала. Запрещающий уровень сигнала на нулевом выходе

дешифратора 5 блокирует первые информационные входы коммутатора 4, а разрешающий уровень на единичном выходе дешифратора 5 пропускает по вторым информационным входам на выходы коммутатора 4 значения старших разрядов счетчика. На входах эталонного 9 и проверяемого 13 блоков памяти устанавливается нулевой код адреса (00...00), по которому происходит считывание информации и ее сравнение. При несовпадении информации блок 11 сравнения вырабатывает сигнал, поступаюш;,ий на блок 12 индикации и генератор 1, останавливаюш,ий его. В первом такте, кроме этого, вследствие наличия разрешающего уровня на единичном выходе дешифратора 5 вырабатывается в блоке 6 и блоке 7 элементов И парафазный сигнал установки п младших разрядов счетчика 2 и происходит перепись (в соответствии с весом) п старших в п младшие разряды счетчика 2 (код 00...00).

При совпадении считанной с обоих блоков 9 и 13 информации на выходе блока 11 сравнения сигнал вырабатывается и импульс генератора 1 устанавливает нулевой младший разряд счетчика 2 в единичное состояние. На его нулевом выходе появляется запрещающий, а на единичном выходе разрешающий уровень сигнала. Изменяется также и значение выходов дешифратора 5: на нулевом выходе устанавливается разрешающий, на единичном - запрешающий уровень сигнала, который блокирует выработку в блоке 6 и блоке 7 элементов И парафазных сигналов установки.

На выходы коммутатора 4 через их первые информационные входы коммутатора 3 йновь проходит значение п старших разрядов счетчика 2, т.е. после обращения по нулевому адресу в первом такте во втором такте обращение производится опять по нулевому адресу (00...00). После этого вновь происходит считывание из обоих блоков памяти 9 и 13, сравнивание информации, и в случае неидентичности следующий импульс генератора 1 увеличивает значение счетчика 2 на единицу: нулевой разряд опять устанавливается в нулевое, а первый - в единичное состояние. Значения выходных сигналов дешифратора 5 в этом такте не меняются, установки п младших разрядов счетчика 2 не происходит и информация на выходы коммутатора 4 вновь проходит через первые информационные входы. Однако в третьем такте на выходы коммутатора 4 через первые инфЬрмационные входы коммутатора 3 проходит значение п младших разрядов счетчика 2, т.е. первый код адреса (00...01). Опять повторяется цикл считыва ния информации, ее сравнение и при совпадении данных следующий импульс генератора 1 вновь увеличивает значение счетчика 2 на единицу.

В четвертом такте младший нулевой разряд счетчика 2 снова устанавливается в единичное состояние: на его нулевом выходе появляется запрещающий, а на единичном - разрешающий уровень сигнала, который пропускает на выходы коммутатора 4 через вторые информационные входы коммутатора 3 значение п старших разрядов - опять нулевой код адреса (00...00). Значение сигнала на выходах дешифратора 5 не изме0 няется и установки п младших разрядов счетчика 2 не происходит. В следующем такте обращение к обоим блокам 9 и 13 произойдет по второму адресу (код 00...10), затем вновь по нулевому адресу (код 00...00), затем по третьему адресу (код .,.11) и т.д.

5 Считывание информации из обоих блоков памяти в течение остальных тактов первого цикла будет происходить поочередно в зависимости от состояния 0-го младшего разряда счетчика 2 по кодам адресов, со0 ответствующим выходам п младших или п старших разрядов счетчика 2 (последнее обращение цикла будет по адресу, соответствующему п старщим разрядам) и принудительной установки п младших разрядов счетчика 2 не будет.

В каждом первом такте К-го цикла проверки в (п -f 1) младщих (с 0-го по п-й) разрядах установятся нули, а значение старших п разрядов счетчика 2 увеличится на

0 единицу. При этом запрещающий уровень нулевого выхода дещифратора 5 заблокирует прохождение информации с первых информационных входов, а разрешающий уровень единичного выхода дешифратора 5 пропустит через вторые информационные входы

на выходы коммутатора 4 значение пстарших разрядов счетчика 2 и разрешит выработку в блоке 6 и блоке 7 элементов И парафазных сигналов установки п младших разрядов счетчика 2. Произойдет принудительная установка п младших разрядов в значение, определяемое п старшими разрядами счетчика 2.

В каждом втором такте К-го цикла проверки 0-1i младший разряд счетчика 2 устанавливается в единичное состояние. На

5 его нулевом выходе - запрещающий, а на единичном - разрешающий уровень. На нулевом выходе дешифратора 5 устанавливается разрещающий, а на единичном - запрещающий уровень. Принудительной установки п младших разрядов счетчика 2

0 не произойдет. Значение п старших разрядов счетчика 2 через вторые информационные входы коммутатора 3 и первые информационные входы коммутатора 4 пройдет на адресные входы блоков 9 и 13.

В каждом третьем и последующих так5тах К-го цикла проверки значения выходов дешифратора 5 не изменится. Принудительной установки п младших разрядов счетчика 2 не будет. После прихода каждого очередного импульса генератора 1 значение нулевого младшего разряда счетчика 2 изменяется на противоположное, вследствие чего на выходы коммутатора 4 с первых их информационных входов будет приходить значение п младших,, или п старших разрядов счетчика 2.

Последовательность перебора адресов будет следующей (адреса показаны в десятичном виде):

1-й цикл (0-0-1-0-2-0-3-0... -О-()-О-

2-й цикл -1 - 1-2-1-3-1-.;. - 1 -() -1 -

3-й цикл -2-2-3-2-...-2-

- ()-2-

4-йцикл .

-3- - (2 П-32 - цикл -() -(2-1). Таким образом каждый i-й адрес, соответ ствующий значению п младших разрядов счетчика . 2, будет прочитываться после j-ro (значение п старших разрядов) и каждый j-й после 1-го. Причем вследствие принудительной установки п младших разрядов счетчика 2 в начале каждого цикла по значению п старших разрядов счетчика i всегда будет не меньше j.

При этом в первом цикле будет 22 обрашений, во второй - 2 (), в третьем 2 (), в четвертом 2 () и т.д., в последнем 2 (()) 2.

Всего обраш,ений к блоку памяти будет 2 2 rf 2, что меньше по сравнению с прототипом- (при п 3 примерно в 2 раза). Следовательно, быстродействие предлагаемого устройства будет примерно в 2 раза выше.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1991 |

|

SU1807516A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| Ассоциативное оперативное запоминающее устройство | 1988 |

|

SU1667155A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1995 |

|

RU2106009C1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСТОЯННОЙ ПАМЯТИ, содержащее генератор импульсов, выход которого подключен к счетному входу -счетчика, первый и второй выходы счетчика подключены к управляющим входам первого коммутатора, одни и другие информационные входы которого подключены соответственно к выходам первой и второй гру11пы счетчика, эталонный блок памяти, выход которого подключен к одному из входов блока сравнения, другой вход блока сравнения является входом устройства, выход блока сравнения подключен к входу блока индикации, отличающееся тем. что, с целью повышения быстродействия устройства, оио содержит дешифратор, второй коммутатор, блоки элементов И, выходы первого из которых подключены к установочным входам счетчика, выходы второго блока элементов И подключены к входам сброса счетчика, одни.входы первого и второго блоков элементов И подключены к первому выходу дешифратора и к первому управляющему входу второго коммутатора, второй управляющий вход которого подключен к второму выходу дешифратора, одни и другие информационные входы второго коммутатора подключены соответственно к выходам первого коммутатора и выходам второй группы счетчика, один вход дешифратора подключен к второму выходу счетчиS ка, другие входы дешифратора подключе ны к выходам первой и третьей групп счет(Я чика, другие входы первого и второго блоков элементов И подключены соответственно к входам второй и четвертой групп счетчика, выходы второго коммутатора подключены к входам эталонного блока памяти и являются выходами устройства, выход блока сравнения подключен к входу генератора. оо оо N3 00 СП

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля постоянной памяти | 1978 |

|

SU748514A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля постоянных блоков памяти | 1976 |

|

SU607282A1 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1984-03-30—Публикация

1982-12-21—Подача