Ж

916

г-$

Л

ю

«-

ел ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1988 |

|

SU1569966A1 |

| Специализированный процессор для цифровой фильтрации | 1989 |

|

SU1631558A1 |

| ЦИФРОВОЙ ФИЛЬТР | 1990 |

|

RU2024183C1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Многочастотный цифровой фильтр | 1987 |

|

SU1474827A1 |

| Цифровой рекурсивный фильтр | 1985 |

|

SU1328925A1 |

| Цифровой фильтр | 1988 |

|

SU1584084A2 |

| Цифровой фильтр | 1988 |

|

SU1569957A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки сигналов. Цель изобретения - повышение точности фильтрации и быстродействия цифрового рекурсивного фильтра (ЦРФ). ЦРФ содержит умножители 1 и 2, блок памяти 3, регистры 4, 5, 6, сумматор 9, накопитель 10, блок 12 управления, шины данных 13 и 14, входы 21 - 23 задания общего порядка, промежуточного порядка и прореживания. Поставленная цель достигается за счет введения в ЦРФ регистра 7, накопителя 11 и коммутатора 8. Блок 12 управления работает синхронно с тактовой частотой синхронизации входных данных на тактовом входе. Работа ЦФР осуществляется в соответствии с микропрограммой реализации фильтра второго порядка, записанной в виде соответствующего управления. 1 з.п. ф-лы, 3 ил.

18

ш

27 22 2J

Vt

Фиг1

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки сигналов.

Цель изобретения - повышение точности фильтрации к быстродействия цифрового рекурсивного фильтра.

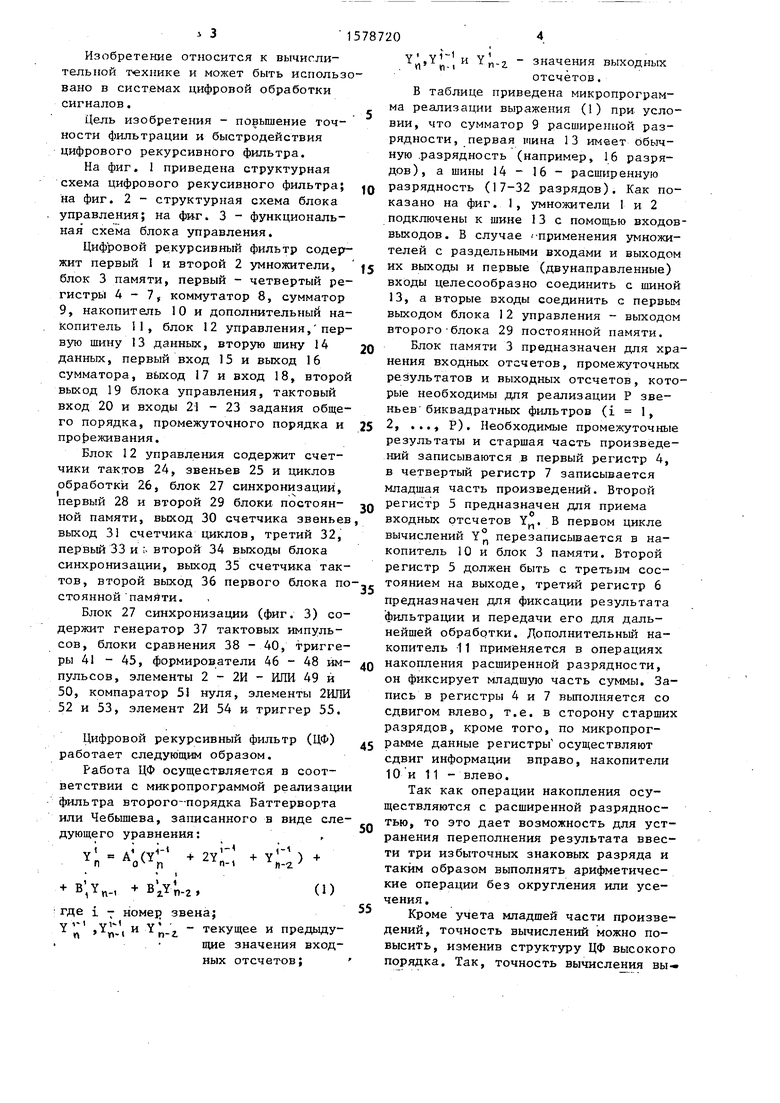

На фиг. 1 приведена структурная схема цифрового рекусивного фильтра; на фиг. 2 - структурная схема блока управления; на фиг. 3 - функциональная схема блока управления.

Цифровой рекурсивный фильтр содержит первый 1 и второй 2 умножители, блок 3 памяти, первый - четвертый регистры 4-7, коммутатор 8, сумматор 9, накопитель 10 и дополнительный накопитель II, блок 12 управления, первую шину 13 данных, вторую шину 14 данных, первый вход 15 и выход 16 сумматора, выход 17 и вход 18, второй выход 19 блока управления, тактовый вход 20 и входы 21-23 задания общего порядка, промежуточного порядка и прореживания.

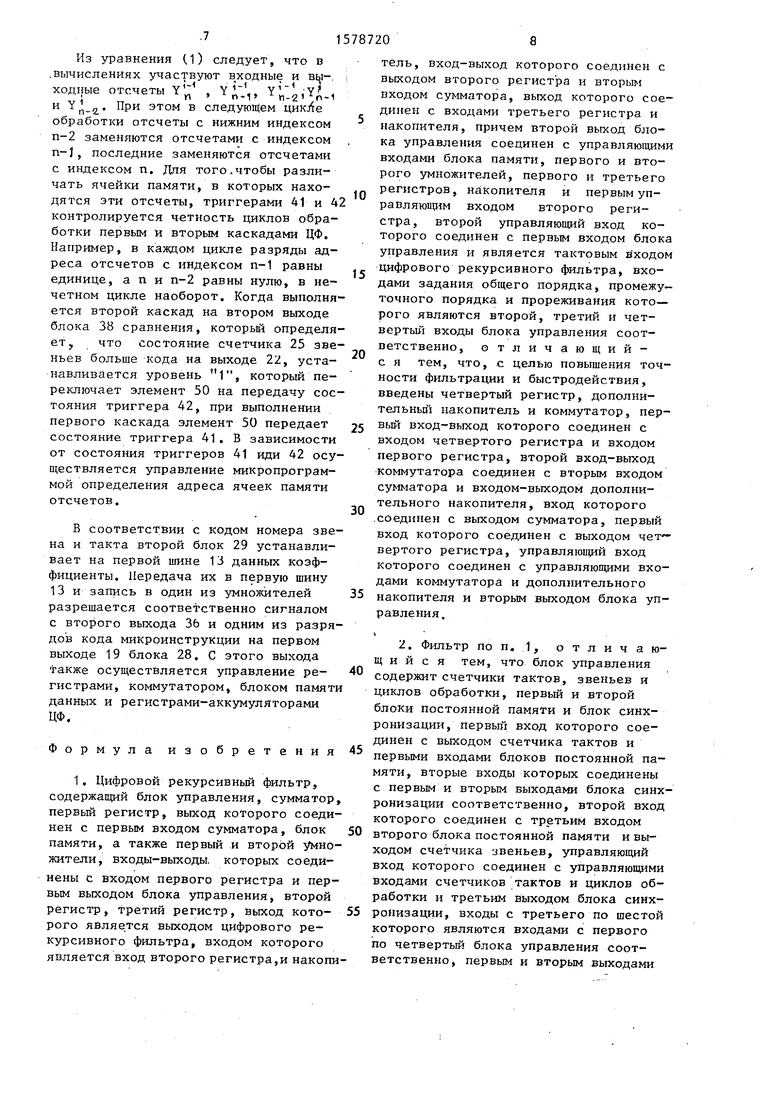

Блок 12 управления содержит счетчики тактов 24, звеньев 25 и циклов обработки 26, блок 27 синхронизации, первый 28 и второй 29 блоки постоянной памяти, выход 30 счетчика звеньев выход 31 счетчика циклов, третий 32, первый 33 и :- второй 34 выходы блока синхронизации, выход 35 счетчика тактов, второй выход 36 первого блока по-,, тоянием на выходе, третий регистр 6

стояннои памяти.

Блок 27 синхронизации (фиг. 3) содержит генератор 37 тактовых импульсов, блоки сравнения 38 - 40, триггеры 41 - 45, формирователи 46 - 48 импульсов, элементы 2 - 2И - ИЛИ 49 и 50, компаратор 51 нуля, элементы 2ИЛИ 52 и 53, элемент 2И 54 и триггер 55.

Цифровой рекурсивный фильтр (ЦФ) работает следующим образом.

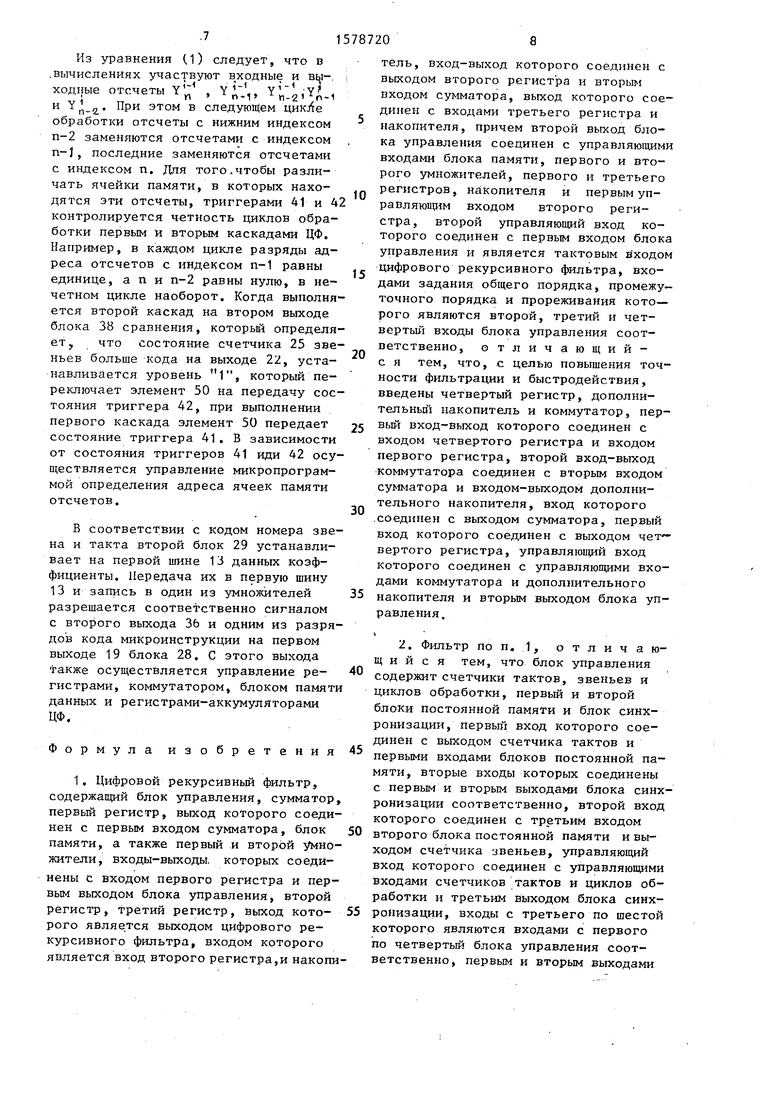

Работа ЦФ осуществляется в соответствии с микропрограммой реализации фильтра второго-порядка Баттерворта или Чебышева, записанного в виде следующего уравнения:,

40

45

50

предназначен для фиксации результат фильтрации и передачи его для дальнейшей обработки. Дополнительный на копитель 11 применяется в операциях накопления расширенной разрядности, он фиксирует младшую часть суммы. З пись в регистры 4 и 7 выполняется с сдвигом влево, т.е. в сторону старш разрядов, кроме того, по микропрограмме данные регистры осуществляют сдвиг информации вправо, накопител 10 и 11 - влево.

Так как операции накопления осуществляются с расширенной разряднос тью, то это дает возможность для ус ранения переполнения результата вве ти три избыточных знаковых разряда таким образом выполнять арифметичес кие операции без округления или усе чения .

+ 2Y

,-

П-1

+ Y )

Х-«

.

n-г

О)

i 7 номер, звена;

YЈ и уп-г текущее и предыдущие значения входных отсчетов;

10

15

787204

Y ,( и У.г - значения выходных отсчётов.

В таблице приведена микропрограмма реализации выражения (1) при условии, что сумматор 9 расширенной разрядности, первая тина 13 имеет обычную разрядность (например, 16 разрядов), а шины 14 - 16 - расширенную разрядность (17-32 разрядов). Как показано на фиг. 1, умножители 1 и 2 подключены к шине 13 с помощью входов- выходов. В случае -применения умножителей с раздельными входами и выходом их выходы и первые (двунаправленные) входы целесообразно соединить с шиной 13, а вторые входы соединить с первым выходом блока 12 управления - выходом второго-блока 29 постоянной памяти.

Блок памяти 3 предназначен для хранения входных отсчетов, промежуточных результатов и выходных отсчетов, которые необходимы для реализации Р звеньев биквадратных фильтров (i 1, 2, . .., Р). Необходимые промежуточные результаты и старшая часть произведений записываются в первый регистр 4, в четвертый регистр 7 записывается младшая часть произведений. Второй регистр 5 предназначен для приема входных отсчетов Yn. В первом цикле

20

25

30

вычислений Y перезаписывается в накопитель 10 и блок 3 памяти. Второй регистр 5 должен быть с третьим сос0

5

0

5

предназначен для фиксации результата фильтрации и передачи его для дальнейшей обработки. Дополнительный накопитель 11 применяется в операциях накопления расширенной разрядности, он фиксирует младшую часть суммы. Запись в регистры 4 и 7 выполняется со сдвигом влево, т.е. в сторону старших разрядов, кроме того, по микропрограмме данные регистры осуществляют сдвиг информации вправо, накопители 10 и 11 - влево.

Так как операции накопления осуществляются с расширенной разрядностью, то это дает возможность для устранения переполнения результата ввести три избыточных знаковых разряда и таким образом выполнять арифметические операции без округления или усечения .

Кроме учета младшей части произведений, точность вычислений можно повысить, изменив структуру ЦФ высокого порядка. Так, точность вычисления вы-

ражения (1) определяется коэффициентом А , величина которого зависит от полосы пропускания ЦФ Ч, причем чем уже полоса пропускания, тем меньше А}.. Увеличить этот коэффициент можно, если Фильтрацию осуществлять рядом последовательно включенных каскадов ЦФ с промежуточным прореживанием частоты между ними. Тогда относитель ная частота среза последующего уцет определяться прореженной частотой дискретизации сигнала па выходе предыдущего каскада. Параметры ЦФ предыдущих каскадов можно выбирать из условия обеспечения прореживания частоты дискретизации и подавления на заданном уровне высокочастотных составляющих сигнала. Например, фильтр Бат- терворта с частотой среза 0,1 4-го порядка обеспечивает прореживание частоты дискретизации в два раза на уровне подавления 66 дБ, такой же фильтр 2-го порядка - на уровне 40 дБ. Блок 12 управления позволяет осуществлять фильтрацию с помощью одного арифметического устройства, реализуя при этом ряд последовательно включенных звеньев, принадлежащих двум каскадам ЦФ с промежуточным прореживанием частоты дискретизации между ними.

Блок 12 управления работает синхронно с тактовой частотой синхронизации входных данных на тактовом входе 20. При включении питания с помощью формирователя 48 и блоков ИЛИ 52 и 53 счетчики 24 - 26 сбрасываются. Выполнение микропрограммы синхронизирует тактовая частота на выходе генератора 37, счетчик 24 тактов управляет следовательностыо записанных в первом блоке 28 микрокоманд. Счетчик 25 звеньев управляет последовательностью реализуемых биквадратных звеньев (1), счетчик 26 циклов фильтрации - порядком ЦФ, который является переменной величиной (под порядком подразумевается число звеньев) и зависит от номера цикла обработки. С помощью кодов на входах 21 и 22 задается общее число звеньев и число звеньев в первом каскаде.

Допустим, что триггеры 43 - 45 сброшены. По фронту тактовой частоты на тактовом входе 20 формирователь 46 генерирует импульс, который устанавливает триггер 44, триггер 43 своего состояния не меняет. По первому фрон1578720

0

5

0

5

ту частоты генератора 37 устанавливается триггер 45 и разрешает работу счетчика 24 тактов, который синхронизирует выполнение микрокоманд согласно алгоритму в таблице. После выполнения заданного кодом на входе 22 числа звеньев с помощью блоков 38 сравнения и элемента 49 формирователь 47 генерирует импульс, стробирующий счетчик 26 циклов обработки и сбрасывающий через элемент 52 счетчики 24 и 25. По фронту этого импульса состояние триггера 43 перезаписывается в триггер 44 и таким образом устанавливает триггеры 44 и 45 в ноль, что приводит к останову ЦФ до прихода следующего фронта частоты на тактовом входе 20. Если выполнено заданное кодом на входе 23 число звеньев первого каскада, то на выходе блока 40 срав- - нения устанавливается уровень 1, который с помощью элемента 49 разрешает выполнение всех звеньев ЦФ. Контроль числа звеньев при этом выполняется блоком ЗУ сравнения. Сигнал сброса формирователем 47 генерируется по заднему фронту сигнала на выходе блока 39 сравнения.

Во время выполнения всех звеньев может поступить фронт частоты дискретизации на тактовый вход 20, который импульсом с выхода формирователя 46 производит запись состояния триггера 44 в триггер 43 и таким образом уста5 навливает его в 1. По импульсу формирователя 47 в триггер 44 производится перезапись 1, и работа ЦФ продолжается. С помощью блоков 2И 54 и 2ИЛИ ЬЗ после выполнения всех зве ньев счетчик 26 циклов обработки сбрасывается. По каждому фронту частоты дискретизации входных данных во второй регистр 5 производится запись отсчета, который затем обрабаты5 вается. Как следует из алгоритма работы ЦФ, ветвления микропрограммы выполняются при вычислении первого и последнего звеньев. Для выполнения этих ветвлений предназначены компаратор 51 нуля, блоки 38 и ЗУ сравне-1 ния и элемент 49. Они формируют признаки, по которым изменяется адресация ячеек первого блока постоянной памяти 28 и осуществляются соответст5 вующие ветвления. Триггером 55 выполняется управление работой умножителей в зависимости от четности выполняемого звена.

0

0

Из уравнения (.1) следует, что в вычислениях участвуют входные и выходные отсчеты , Y., Y1 Ј,, и . При этом в следующем цикАе обработки отсчеты с нижним индексом п-2 заменяются отсчетами с индексом n-J, последние заменяются отсчетами с индексом п. Для того,чтобы различать ячейки памяти, в которых находятся эти отсчеты, триггерами 41 и 4 контролируется четность циклов обработки первым и вторым каскадами ЦФ. Например, в каждом цикле разряды адреса отсчетов с индексом п-1 равны

единице, а п и п-2 равны нулю, в нечетном цикле наоборот. Когда выполняется второй каскад на втором выходе блока 38 сравнения, которьй определяет, что состояние счетчика 25 звеньев больше кода на выходе 22, устанавливается уровень 1, который переключает элемент 50 на передачу состояния триггера 42, при выполнении первого каскада элемент 50 передает состояние триггера 41. В зависимости от состояния триггеров 41 иди 42 осуществляется управление микропрограммой определения адреса ячеек памяти отсчетов.

В соответствии с кодом номера звена и такта второй блок 29 устанавливает на первой шине 13 данных коэффициенты. Передача их в первую шину 13 и запись в один из умножителей разрешается соответственно сигналом с второго выхода 36 и одним из разрядов кода микроинструкции на первом выходе 19 блока 28. С этого выхода также осуществляется управление регистрами, коммутатором, блоком памяти данных и регистрами-аккумуляторами ЦФ.

Формула изобретения 45

0

5

0

5

5

0

0

5

тель, вход-выход которого соединен с выходом второго регистра и вторым входом сумматора, выход которого соединен с входами третьего регистра и накопителя, причем второй выход блока управления соединен с управляющими входами блока памяти, первого и второго умножителей, первого и третьего регистров, накопителя и первым управляющим входом второго регистра, второй управляющий вход которого соединен с первым входом блока управления и является тактовым входом цифрового рекурсивного фильтра, входами задания общего порядка, промежуточного порядка и прореживания кото- рого являются второй, третий и четвертый входы блока управления соответственно, о тличающий- с я тем, что, с целью повышения точности фильтрации и быстродействия, введены четвертый регистр, дополнительный накопитель и коммутатор, первый вход-выход которого соединен с входом четвертого регистра и входом первого регистра, второй вход-выход коммутатора соединен с вторым входом сумматора и входом-выходом дополнительного накопителя, вход которого соединен с выходом сумматора, первый вход которого соединен с выходом чет вертого регистра, управляющий вход которого соединен с управляющими входами коммутатора и дополнительного накопителя и вторым выходом блока управления,

которого являются первый выход первого и выход второго блоков постоянной памяти соответственно, второй выход первого блока постоянной памяти соеПримеча ния: АСС - накопитель, Р - регистр, ОЗУ - блок памяти данных,

УМН 1(2) - умножитель первый или второй, (-)-содержимое,

Фиг. 2

динен с четвертым входом второго блока постоянной памяти, а выход счетчика циклов обработки соединен с седь« мым входом блока синхронизации.

| Патент США № 4117541, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-07-15—Публикация

1988-06-28—Подача