Изобретение относится к автоматике и вычислительной технике и может быть использовано при тестовом контроле логических блоков.

Цель изобретения - повышение быстродействия.

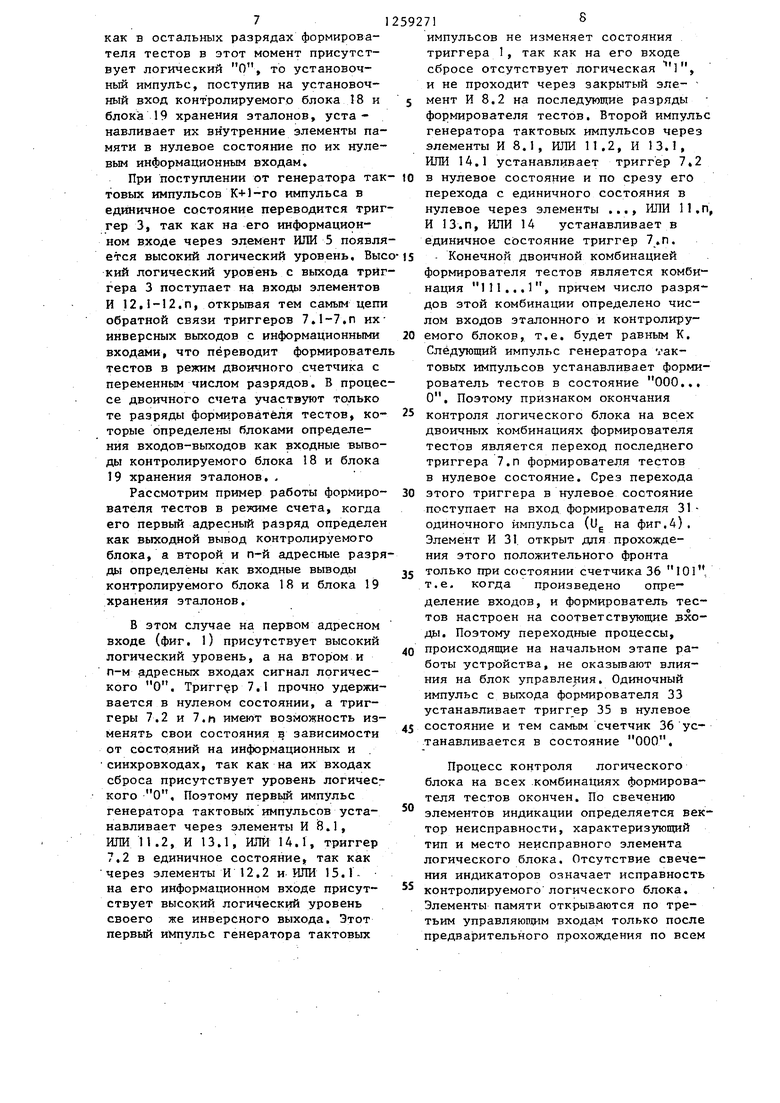

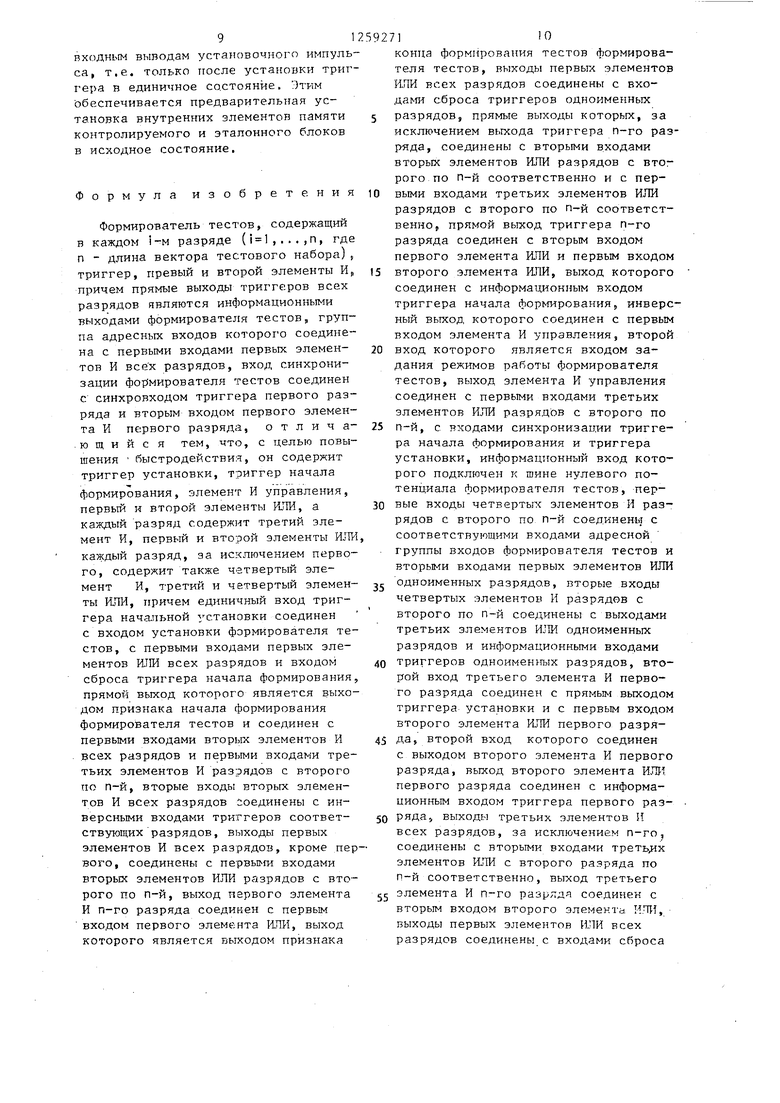

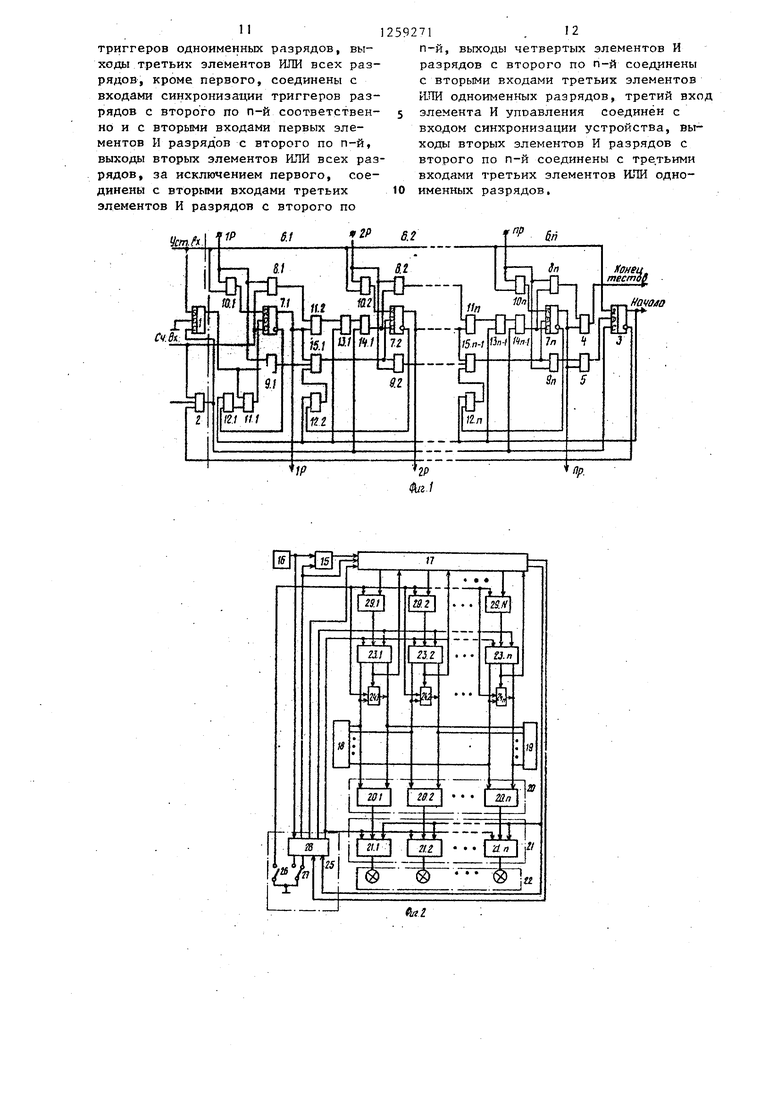

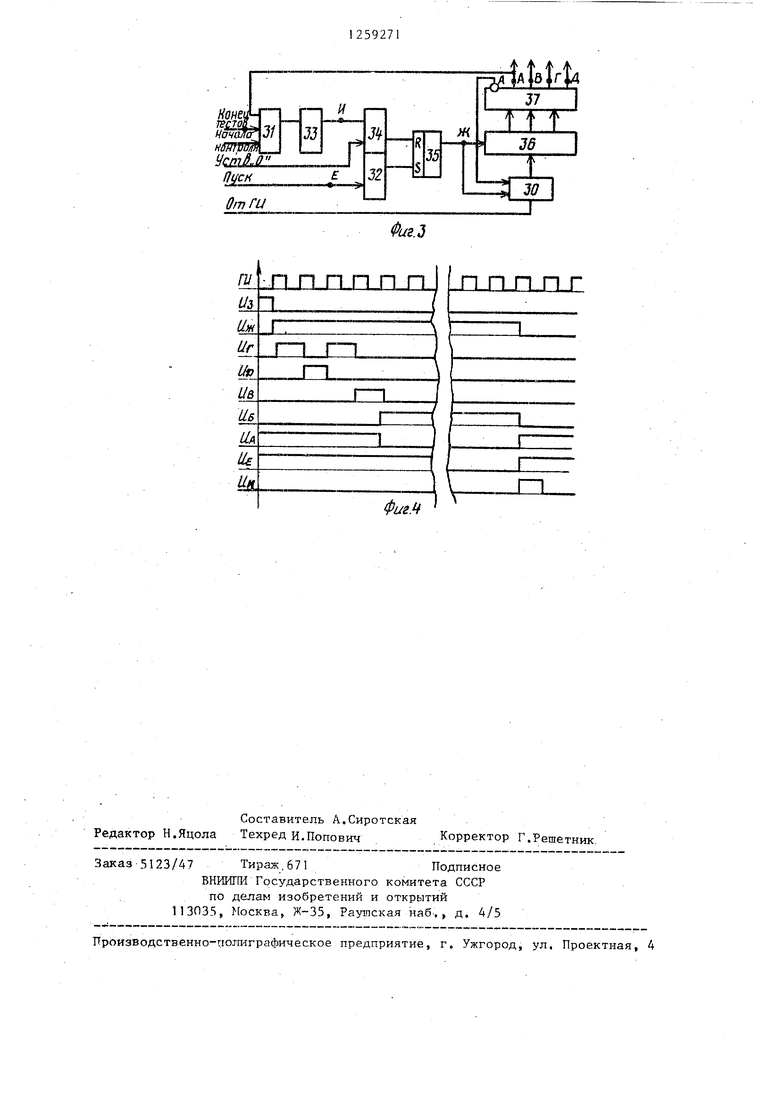

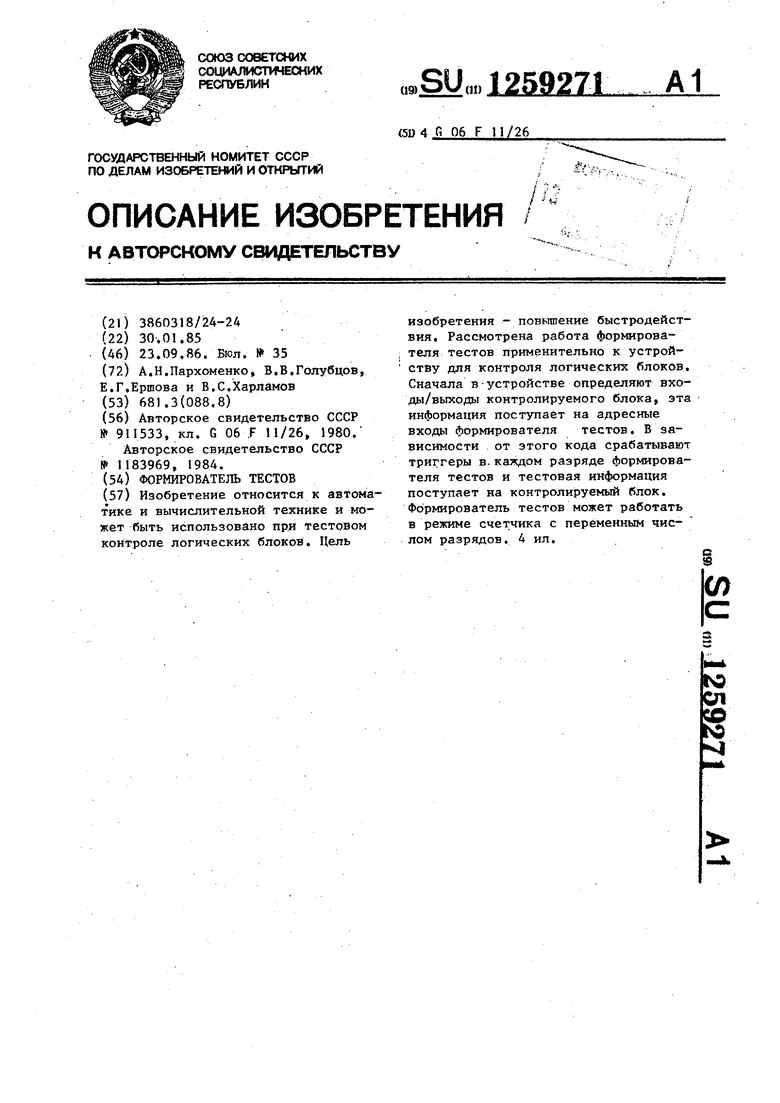

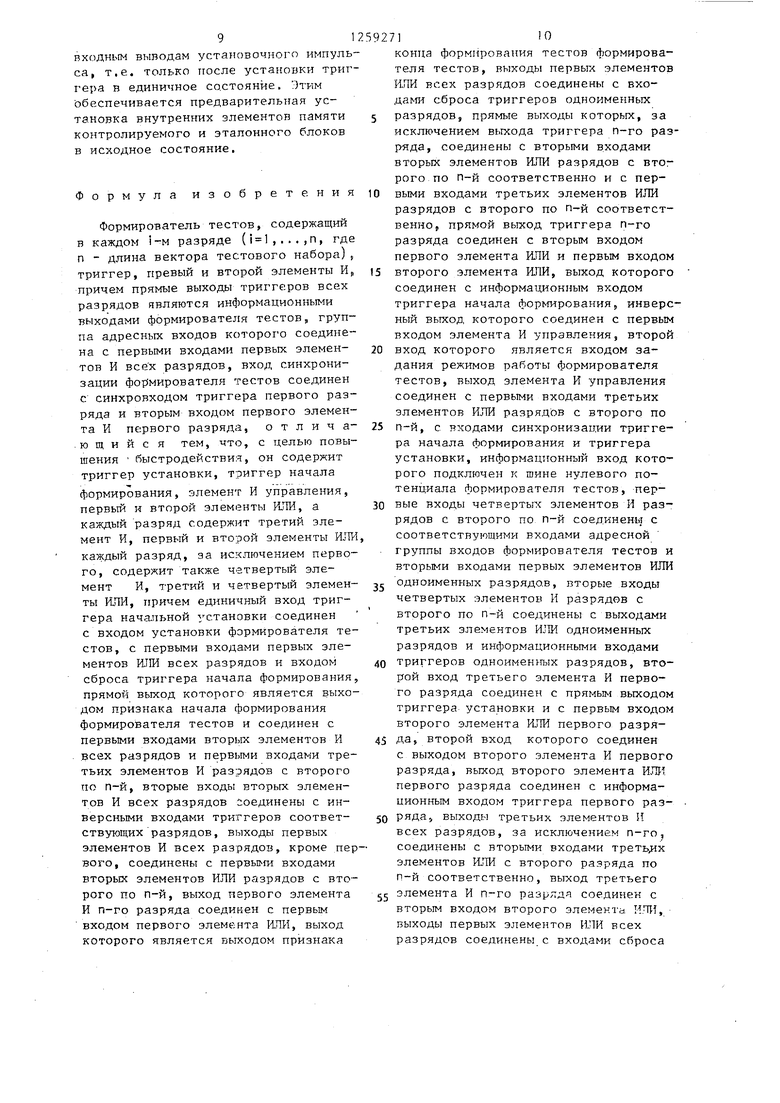

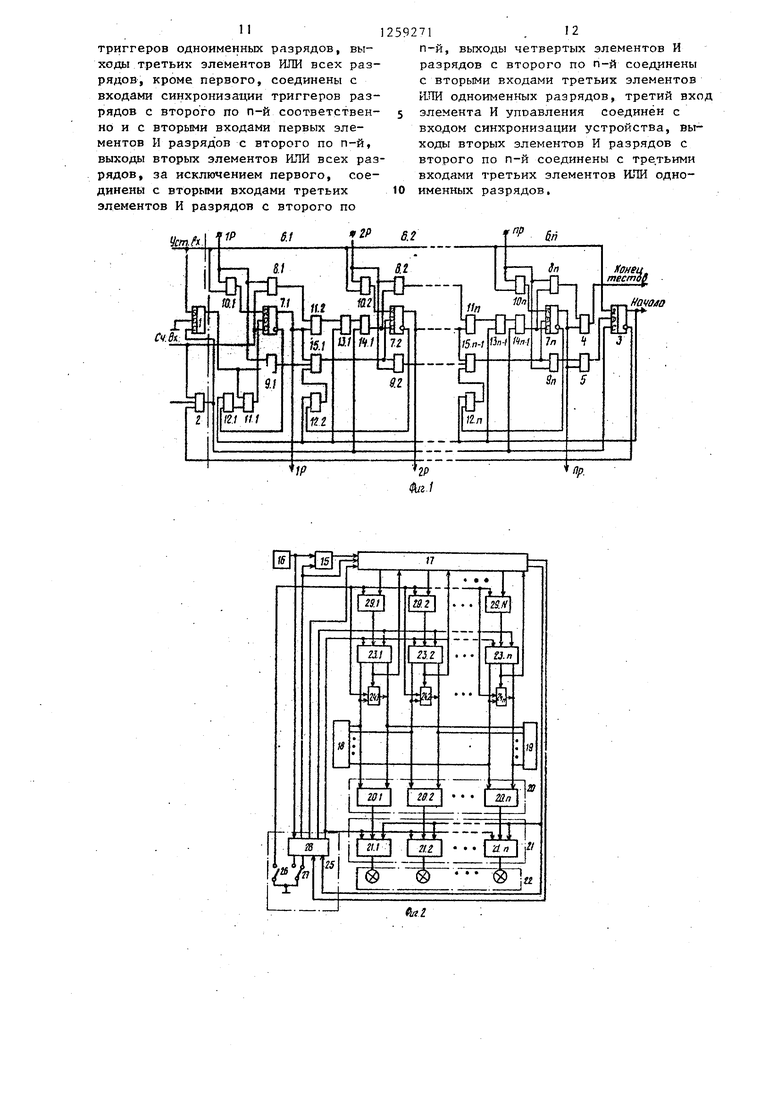

На фиг, I показана функциональная схема формирователя тестов, на фиг, 2 - пример использования формирователя тестов при тестовом контроле логических блоков, на фиг, 3 - блок-схема блока управления; на фиг. 4 - временная диаграмма работы блока управления.

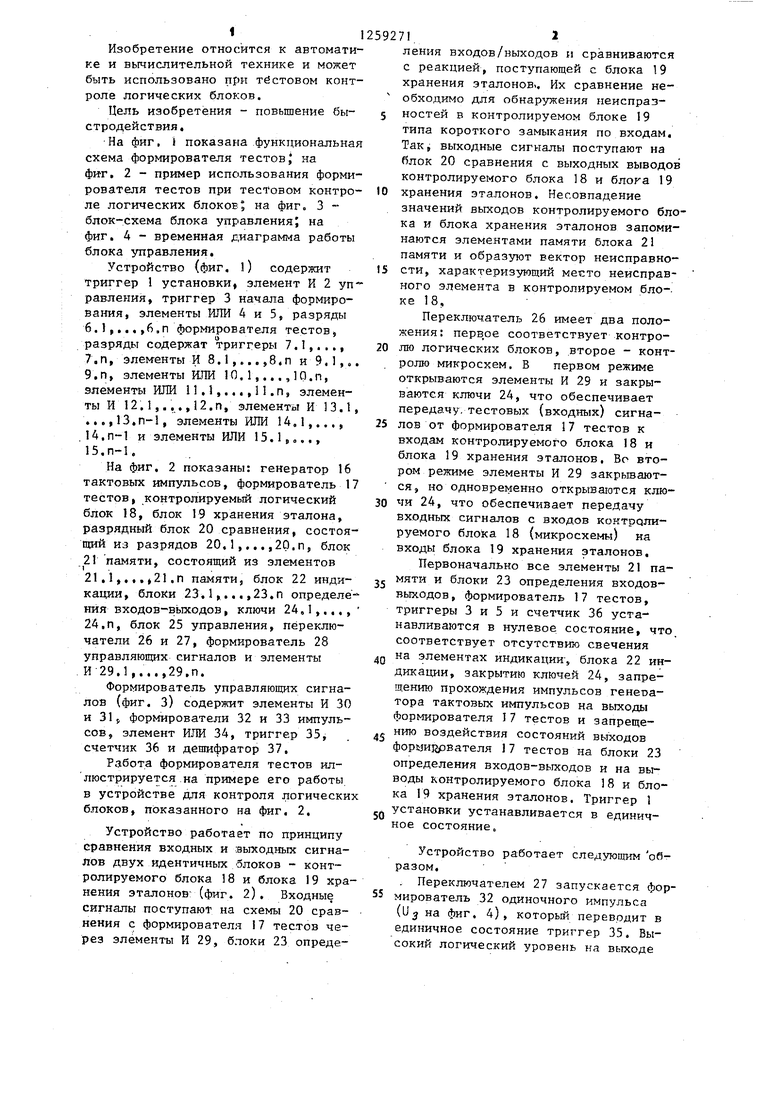

Устройство (фиг. l) содержит триггер 1 установки элемент И 2 уп равления, триггер 3 начала формирования, элементы ИЛИ 4 и 5, разряды 6.1,...,6.п формирователя тестов разряды содержат триггеры 7.1,..., 7.п, элем-енты И 8.1,...,8,п и 9,1,. 9.П, элементы РШИ 10.1,...,IQ.n, элементы ИЛИ 11.5,...,П.п, элементы И 12.1,...,12.п, элементы И 13.1 ...,13.п-1, элементы ИЛИ 14.1,..,, 14.П-1 и элементы ИЛИ 15.1,0.., 15.П-1.

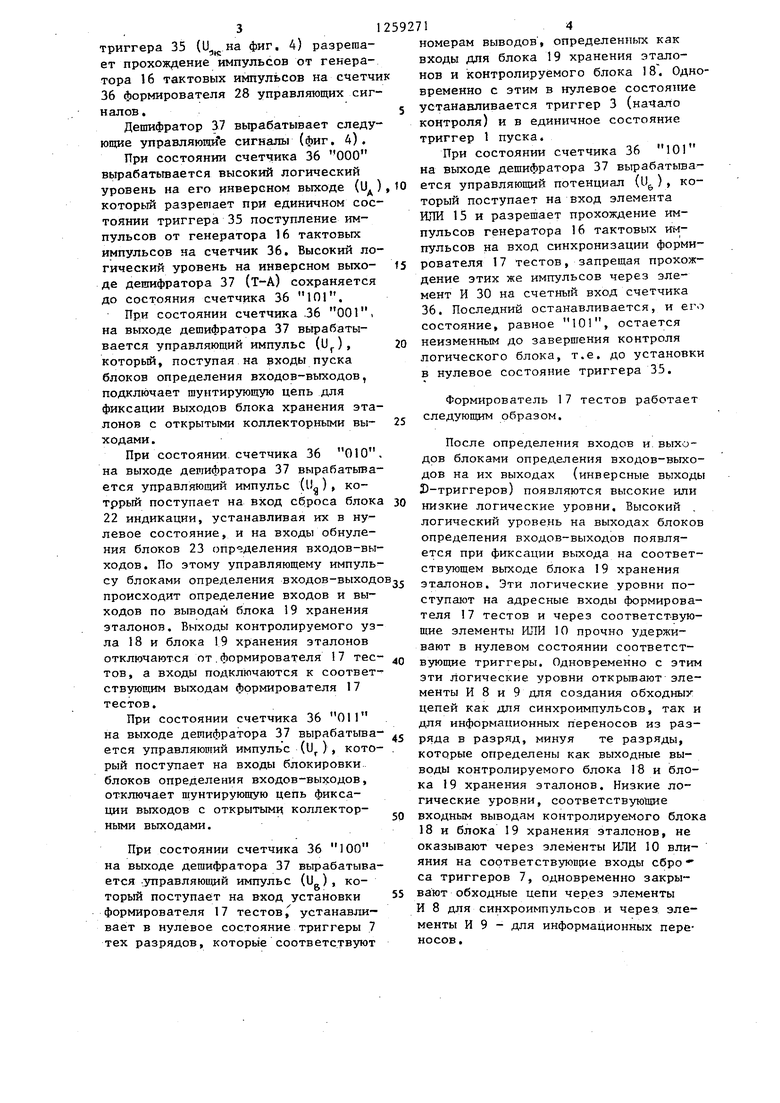

На фиг. 2 показаны: генератор 16 тактовьгк импульсов, формирователь 17 тестов, контролируемый логический блок 18, блок 19 хранения эталона, разрядный блок 20 сравнения, состоящий из разрядов 20.1,...,20.п, блок

21 памяти, состоящий из элементов 1 .

21.1,...21.п памяти, блок 22 индикации , блоки 23.1,....23. п определе кия входов-вьпсодов, ключи 2А, 1,... , 24.п, блок 25 управления, переключатели 26 и 27, формирователь 28 управляющих сигналов и элементы И 29.1,...,29.п.

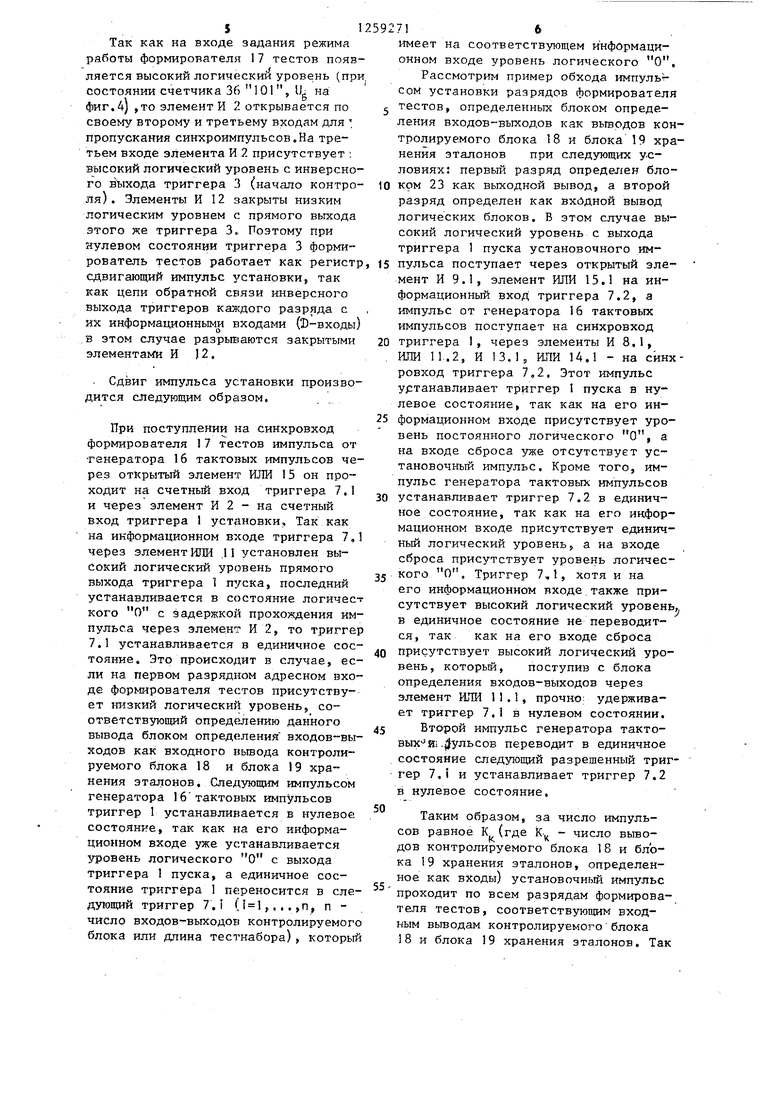

Формирователь управляющих сигналов (фиг. З) содержит элементы И 30 и 315 формирователи 32 и 33 импульсов, элемент ИЖ 34, триггер 35, счетчик 36 и дешифратор 37.

Работа формирователя тестов иллюстрируется на примере его работы в устройстве для контроля логически блоков, показанного на фиг. 2.

Устройство работает по принципу сравнения входных и вьпсодных сигналов двух идентичных блоков - контролируемого блока 18 и блока 19 хранения эталонов; (фиг. 2). Входные сигналы поступают на схемы 20 сравнения с формирователя 17 тестов через элементы И 29, блоки 23 определения входов/ньпсодов и сравниваются с реакцией, поступающей с блока 19 хранения эталонов-. Их сравнение не- обходимо для обнаружения неиспразностей в контролируемом блоке 19 типа короткого замыкания по входам. Так, выходные сигналы поступают на блок 20 сравнения с выходных выводов контролируемого блока 18 и блока 19

хранения эталонов. Несовпадение

значений выходов контролируемого блока и блока хранения эталонов запоминаются элементами памяти блока 21 памяти и образуют вектор неисправности, характеризующий место неисправного элемента в контролируемом бло-. ке 18,

Переключатель 26 рдаеет два положения: перв,ое соответствует контролю логических блоков, второе - контролю микросхем. В первом режиме открываются элементы И 29 и закрываются ключи 24, что обеспечивает передачу, тестовых (входнь х) сигналов от формирователя 17 тестов к входам контролируемого блока 18 и блока 19 хранения эталонов. Во втором режиме элементы И 29 закрьшают- ся, но одновременно открываются ключи 24, что обеспечивает передачу входных сигналов с входов контролируемого блока 18 (микросхемы) на входы блока 19 хранения эталонов. Первоначально все элементы 21 памяти и блоки 23 определения входов- выходов, формирователь 17 тестов, триггеры 3 и 5 и счетчик 36 устанавливаются в нулевое состояние, что соответствует отсутствию свечения

на элементах индикации-, блока 22 индикации, закрытию ключей 24, запрещению прохождения импульсов генепа- тора тактовьк импульсов на выходы формирователя I7 тестов и запрещекию воздействия состояний выходов фор1аи1грвателя 17 тестов на блоки 23 определения входов-выходов и на выводы контролируемого блока 18 и блока 19 хранения эталонов. Триггер 1

установки устанавливается в единичное состояние.

Устройство работает следующим образом.

. Переключателем 27 запускается фор- мирователь 32 одиночного импульса (и на фиг. 4), которьй переводит в единичное состояние триггер 35. Высокий логический уровень на выходе

триггера 35 (U., на фиг. 4) разрегаа- ет прохождение импульсов от генератора 16 тактовых импульсов на счетчи 36 формирователя 28 управляющих сигналов ,

Дешифратор 37 вырабатывает следующие управляющи е сигналы (фиг, 4).

При состоянии счетчика 36 000 вырабатьтается высокий логический уровень на его инверсном выходе (U который разрешает при единичном состоянии триггера 35 поступление импульсов от генератора 16 тактовых импульсов на счетчик 36. Высокий логический уровень на инверсном выхо- де дешифратора 37 (Т-А) сохраняется до состояния счетчика 36 101.

При состоянии счетчика .36 001, на выходе дешифратора 37 вьфабаты- вается управляющий импульс (U), который, поступая на входы пуска блоков определения входов-выходов, подключает шунтирующую цепь для фиксации выходов блока хранения эталонов с открытыми коллекторными вы- ходами.

При состоянии счетчика 36 010 на выходе дешифратора 37 вырабатьгоа- ется управляющий импульс (l. a) ко- тррый поступает на вход сброса блока 22 индикации, устанавливая их в нулевое состояние, и на входы обнуления блоков 23 определения входов-выходов. По этому управляющему импульсу блоками определения входов-выходо происходит определение входов и выходов по выводам блока 19 хранения эталонов. Выходы контролируемого узла 18 и блока 19 хранения эталонов отключаются от.формирователя 17 тес- тов, а входы подключаются к соответствующим выходам формирователя 17 тестов.

При состоянии счетчика 36 011 на выходе дешифратора 37 вырабатыва- ется управляющий импульс (11 ) , кото- рый поступает на входы блокировки, блоков определения входов-выходов, отключает шунтирующую цепь фиксации выходов с открытыми коллекторными выходами.

При состоянии счетчика 36 100 на выходе дешифратора 37 вьфабатыва- ется ..управляющий импульс (U ) , который поступает на вход установки формирователя 17 тестов, устанавливает в нулевое состояние триггеры 7 тех разрядов, которые соответствуют

5

Ю 15

20 25

зо о

5

0

номерам выводов , определенных как входы для блока 19 хранения эталонов и контролируемого блока 18. Одновременно с этим в нулевое состояние устанавливается триггер 3 (начапо контроля) и в единичное состояние триггер 1 пуска.

При состоянии счетчика 36 101 на выходе дешифратора 37 вырабатывается управляющий потенциал (U) , который поступает на вход элемента ИЛИ 15 и разрешает прохождение импульсов генератора 16 тактовых импульсов на вход синхронизации формирователя 17 тестов , запрещая прохождение этих же импульсов через элемент И 30 на счетный вход счетчика 36. Последний останавливается, и его состояние, равное 101, остается неизменным до завершения контроля логического блока, т.е. до установки в нулевое состояние триггера 35.

Формирователь 17 тестов работает следуюш 1м образом.

После определения входов и выходов блоками определения входов-выходов на их выходах (инверсные выходы -триггеров) появляются высокие или низкие логические уровни. Высокий логический уровень на выходах блоков определения входов-выходов появляется при фиксации выхода на соответствующем выходе блока 19 хранения эталонов. Эти логические уровни поступают на адресные входы формирователя 17 тестов и через соответствующие элементы ИЛИ 10 прочно удерживают в нулевом состоянии соответствующие триггеры. Одновременно с этим эти Логические уровни открывают элементы И 8 и 9 для создания обходных цепей как для синхроимпульсов, так и для информационных переносов из разряда в разряд, минуя те разряды, которые определены как выходные выводы контролируемого блока 18 и блока 19 хранения эталонов. Низкие логические уровни, соответствуюПще входным выводам контролируемого блока 18 и блока 19 хранения эталонов, не оказывают через элементы ИЛИ 10 влияния на сортветствуюп(ие входы сбро са триггеров 7, одновременно закрывают обходные цепи через элементы И 8 для синхроимпульсов и через элементы И 9 - для информационных переносов .

51

Так как на входе задания режима работы формирователя 17 тестов появляется высокий логический уровень (прИ состоянии счетчика 36 101, U на фиг, 4) ,то элемент И 2 открывается по своему второму и третьему входам для , пропускания синхроимпульсов.На третьем входе элемента И 2 присутствует : высокий логический уровень с инверсного выхода триггера -5 (начало контро- ля). Элементы И 12 закрыты низким логическим уровнем с прямого выхода этого же триггера 3. Поэтому при нулевом состоянии триггера 3 формирователь тестов работает как регистр сдвигающий импульс установки, так как цепи обратной сиязи инверсного выхода триггеров казсдого разряда с их информационными входами (В-входы) .в этом случае разрьтаются закрытыми элементами И )2,

. Сдвиг импульса установки производится следующим образом.

При поступлении на синхровход

формирователя 17 тестов импульса от генератора 16 тактовых импульсов через открытый элемент ИЛИ 15 он проходит на счетньй вход триггера 7.1 и через элемент И 2 - на счетный вход триггера 1 установки. Так как на информационном входе триггера 7,1 че{)ез элемент ИЛИ .11 установлен высокий логический уровень прямого выхода триггера 1 пуска, последний устанавливается в состояние логичест кого О с задержкой прохождения импульса через элемент И 2, то триггер 7.1 устанавливается в единичное состояние. Это происходит в случае, если на первом разрядном адресном зхо- де формирователя тестов присутствует низкий логический уровень, соответствующий опред«У1ению данного вывода блоком определения входов-выходов как входного вьшода контролируемого блока 18 и блока 19 хранения эталонов. Следующим импульсом генератора 16 тактовых импульсов триггер 1 устанавливается в нулевое состояние, так как на его информационном входе уже устанавливается уровень логического О с выхода триггера 1 пуска, а единичное состояние триггера 1 переносится в еле- дующий триггер 7.1 ...,n, п - число входов-выходов контролируемого блока или длина тестнабора), который

s 0

5

5

0

имеет на соответствующем информационном входе уровень логического О.

Рассмотрим пример обхода импуль - сом установки разрядов формирователя тестов, определенных блоком определения входов-выходов как выводов контролируемого блока 18 и блока 19 хранения эталонов при следующих условиях: первый разряд определен блоком 23 как выходной вывод, а второй разряд определен как входной вывод логических блоков. В этом случае высокий логический уровень с выхода триггера I пуска установочного импульса поступает через открытый элемент И 9.1, элемент ИЛИ 15.1 на информационный вход триггера 7.2, а импульс от генератора 16 тактовых импульсов поступает на синхровход триггера 1, через элементы И 8.1, ИЛИ П..2, И 13.1, ИЛИ 14.1 - на синхровход триггера 7,2. Этот импульс устанавливает триггер 1 пуска в нулевое состояние, так как на его информационном входе присутствует уровень постоянного логического О, а на входе сброса отсутствует установочный импульс. Кроме того, импульс генератора тактовых импульсов устанавливает триггер 7.2 в единичное состояние, так как на его информационном входе присутствует единичный логический уровень, а на входе сброса присутствует уровень логического О, Триггер 7,1, хотя и на его информационном входе.также присутствует высокий логический уровень,, в единичное состояние не переводится, так как на его входе сброса присутствует высокий логический уровень, который, поступив с блока определения входов-выходов через элемент ИЛИ 11.1, прочно: удерживает триггер 7.1 в нулевом состоянии.

Второй импульс генератора такто- .ульсов переводит в единичное состояние следующий разрешенный триггер 7.1 и устанавливает триггер 7.2 в нулевое состояние.

Таким образом, за число импульсов равное К (где К- - число выводов контролируемого блока 18 и блока 19 хранения эталонов, определенное как входы) установочный импульс проходит по всем разрядам формирователя тестов, соответствую1щм входным вьтодам контролируемого блока 18 и блока 19 хранения эталонов. Так

как в остальных разрядах формирователя тестов в этот момент присутствует логический О, то установочный импульс, поступив на установочный вход контролируемого блока 18 и блока 19 хранения эталонов, устанавливает их внутренние элементы памяти в нулевое состояние по их нулевым информационным входам.

При поступлении от генератора так- товых импульсов К+1-го импульса в едшичное состояние переводится триггер 3, так как на его информационном входе через элемент ИЛИ 5 появляется высокий логический уровень, Высо кий логический уровень с выхода триггера 3 поступает на входы элементов И 12,1-12.п, открывая тем самым цепи обратной связи триггеров 7.1-7,п их- инверсных выходов с информационными входами, что переводит формирователь тестов в режим двоичного счетчика с переменным числом разрядов. В процессе двоичного счета участвуют только те разряды формирователя тестов, которые определены блоками определения входов-выходов как входные выводы контролируемого блока 18 и блока 19 хранения эталонов. ,

Рассмотрим пример работы формирователя тестов в режиме счета, когда его первый адресный разряд определен как выходной вывод контролируемого блока, а второй и п-й адресные разряды определены как входные выводы контролируемого блока 18 и блока 19 хранения эталонов.

В этом случае на первом адресном входе (фиг, 1) присутствует высокий логический уровень, а на втором и п-м адресных входах сигнал логического О, Триггер 7,1 прочно удерживается в нулевом состоянии, а триггеры 7,2 и 7.h имеют возможность изенять свои состояния в зависимости от состояний на информационных и

синхровходах, так как на их входах сброса присутствует уровень логического О, Поэтому первый импульс генератора тактовых импульсов устанавливает через элементы И iB.l, ИЛИ 11,2, И 13.1, ИЛИ 14,1, триггер 7.2 в единичное состояние, так как

ерез элементы И 12,2 иЯЛИ 15,1- на его информационном входе присутствует высокий логический уровень своего же инверсного выхода. Этот первый импульс генератора тактовых

импульсов не изменяет состояния триггера 1, так как на его входе сбросе отсутствует логическая 1, и не проходит через закрытый эле- мент И 8,2 на последующие разряды формирователя тестов, Второй импульс генератора тактовых импульсов через элементы И 8.1, ИЛИ 11,2, И 13,1, ИЛИ 14.1 устанавливает триггер в нулевое состояние и по срезу его перехода с единичного состояния в нулевое через элементы ,,,, ИЛИ 11.П, И 13.П, ИЛИ 14 устанавливает в единичное состояние триггер 7.п. - Конечной двоичной комбинацией формирователя тестов является комбинация 111,,., причем число разря дов этой комбинации определено числом входов эталонного и контролкруемого блоков, т,е, будет равным К, Следующий импульс генератора vaK- товых импульсов устанавливает формирователь тестов в состояние 000,.. О, Поэтому признаком окончания

контроля логического блока на всех двоичных комбинациях формирователя тестов является переход последнего триггера 7,п формирователя тестов в нулевое состояние. Срез перехода этого триггера в нулевое состояние поступает на вход формирователя 31 - одиночного импульса (Ug на фиг.4), Элемент И 31. открыт для прохождения этого положительного фронта только при состоянии счетчика 36 101, т.е. когда произведено определение входов, и формирователь тестов настроен на соответствующие входы. Поэтому переходные процессы,

происходящие на начальном этапе работы устройства, не оказьшают влияния на блок управления. Одиночный импульс с выхода формирователя 33 устанавливает триггер 35 в нулевое

состояние и тем самым счетчик 36 устанавливается в состояние 000,

Процесс контроля логического блока на всех .комбинациях формирователя тестов окончен. По свечению элементов индикации определяется вектор неисправности, характеризующий тип и место неисправного элемента логического блока. Отсутствие свечения индикаторов означает исправность контролируемого логического блока. Элементы памяти открываются по третьим управляют ™ входам только после предварительного прохождения по всем

входным выводам установочного импульса, т.е. только после установки триггера в единичное со.стоянйе. Згум обеспечивается предварительная установка внутренних элементов памяти контролируемого и эталонного блоков в исходное состояние.

ормула изобретения ю

Формирователь тестов, содержащий каждом i-M разряде (,.,.,n, где - длина вектора тестового набора), риггер, правый и второй элементы И,, |5 причем прямые выходы триггеров всех разрядов являются информационными выходами формирователя тестов, группа адресных входов которого соединена с первыми входами первых элемен- 20 тов И всех разрядов, вход синхронизации формирователя тестов соединен с синхровходом триггера первого разряда и вторым входом первого элемента И первого разряда, о т л и ч а- 25 ю щ и и с я тем, что, с целью повышения быстродействия, он содержит триггер установки, триггер начала формирования, элемент И управления, первый и второй элементы ИЛИ, а 30 каждый разряд содержит третий элемент И, первый и второй элементы ИЛИ, каждый разряд, за исключением первого, содержит также четвертый элемент И, третий и четвертый элемен- 35 ты ИЛИ, причем единичный вход триггера начальной установки соединен с входом установки формирователя тестов, с первыми входами первых элементов ИЛИ всех разрядов и входом /ю сброса триггера начала формирования, прямой выход которого является выходом признака начала формирования формирователя тестов и соединен с первыми входами вторых элементов И 45 .всех разрядов и первыми входами третьих элементов И разрядов с второго по п-й, вторые входы вторых элементов И всех разрядов соединены с инверсными входами триггеров соответ- 50 ствующих разрядов, выходы первых элементов И всех разрядов, кроме первого, соединены с первыми входами вторых элементов ИЛИ разрядов с второго по п-й, выход первого элемента 55 И п-го разряда соединен с первым входом первого элемента НИИ, выход которого является выходом признака

конца формирования тестов формирователя тестов, въгходы первых элементов КПИ всех разрядов соединены с входами сброса триггеров одноименных разрядов, прямые выходы которых, за исключением выхода триггера п-го разряда, соединены с вторыми в.ходами вторых элементов ИЛИ разрядов с второго по п-й соответственно и с первыми входами третьих элементов ИЛИ разрядов с второго по п-й соответственно, прямой выход триггера п-го разряда соединен с вторым входом первого элемента ИЛИ и первым входом второго элемента ИЛИ, выход которого соединен с информационным входом триггера начала формирования, инверсный выход которого соединен с первым входом элемента И управления, второй вход которого является входом задания режимов работы формирователя тестов, выход элемента И управления соединен с первьми входами третьих элементов ИЛИ разрядов с второго по п-й, с входами синхронизации триггера начала формирования и триггера установки, информационный вход которого подключен к шине нулевого потенциала формирователя тестов, первые входы четвертых элементов И разрядов с второго по п-й соединены с соответствующими входами адресной группы входов формирователя тестов и вторыми входами первых элементов ИЛИ одноименных разрядов, вторые входы четвертых элементов И разрядов с второго по п-й соединены с выходами третьих элементов ИЛИ одноименных разрядов и информационными входами триггеров одноименгеях разрядов, второй вход третьего элемента И первого разряда соединен с прямым выходом триггера установки и с первым входом второго элемента ИЛИ первого разряда, второй вход которого соединен с выходом второго элемента И первого разряда, выход второго элемента ИЖ первого разряда соединен с информационным входом триггера первого разряда, выходы третьих элементов И всех разрядов, за исключением п-го, соединены с вторыми входами третьд1х элементов ИЛИ с второго разряда по п-й соответственно, выход третьего элемента И п-го разряда соединен с вторым входом второго элемента ИЛ1Т, выходы первых элементов ИЛИ всех разрядов соединены с входами сброса

11 1

триггеров одноименных разрядов, выходы третьих элементов ИЛИ всех разрядов, кроме первого, соединены с входами синхрониза-ции триггеров разрядов с второго по п-й соответственно и с вторыми входами первых элементов И разрядЪв с второго по п-й, выходы вторых элементов ИЛИ всех разрядов, за исключением первого, соединены с вторыми входами третьих элементов И разрядов с второго по

59271, 12

п-й, выходы четвертых элементов И разрядов с второго по п-й соединены с вторыми входами третьих элементов ИЛИ одноименных разрядов, третий вход 5 элемента И управления соединён с входом синхронизации устройства, выходы вторых элементов И разрядов с второго по п-й соединены с тре,тьими входами третьих элементов ИЛИ одноименных разрядов,

10

Й-/П.А.

ГР

СчМ

Р &п

k

Hwoao

Составитель А,Сиротская Редактор Н.Яцола Техред и.Попович Корректор Г.Решетник.

Заказ 5123/47 Тираж,671Подписное

ВНИИГМ Государственного комитета СССР

по делам изобретений и открытий 113П35, осква, Ж-35, Раушская наб.. , д. 4/5

ПрЬизводственно-похмграфическое предприятие, г, Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования тестовых воздействий | 1987 |

|

SU1476473A1 |

| Устройство для контроля логических узлов | 1982 |

|

SU1020829A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Многоканальное устройство тестового контроля логических узлов | 1985 |

|

SU1265778A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

| Устройство для контроля субблока логического блока | 1986 |

|

SU1327111A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1553980A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при тестовом контроле логических блоков. Цель изобретения - повьшение быстродействия. Рассмотрена работа формирователя тестов применительно к устройству для контроля логических блоков. Сначала вустройстве определяют входы/выходы контролируемого блока, эта информация поступает на адресные входы формирователя тестов. В зависимости от этого кода срабатывают триггеры в. казздом разряде формирователя тестов и тестовая информация поступает на контролируемый блок. Формирователь тестов может работать в режиме счетчика с переменным числом разрядов. 4 ил.

| Устройство для формирования тестовых воздействий | 1980 |

|

SU911533A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1183969, 1984. | |||

Авторы

Даты

1986-09-23—Публикация

1985-01-30—Подача