СлЭ СХ) О)

со оо со

143

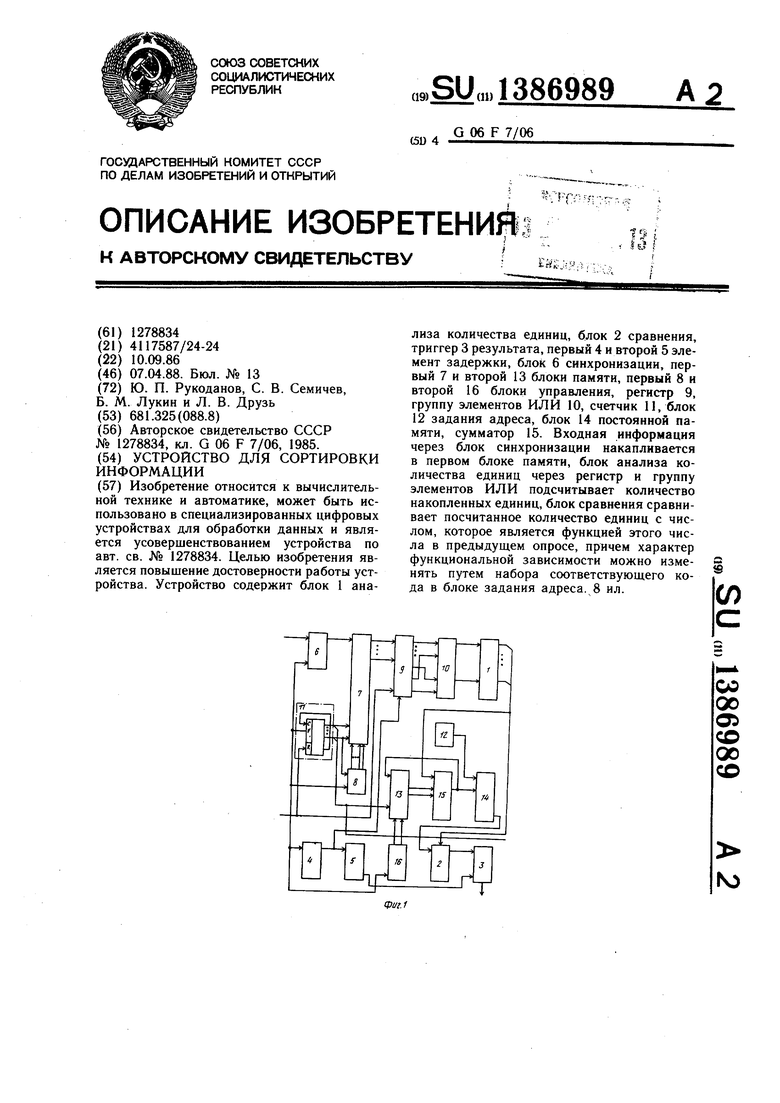

Изобретение относится к автоматике и вычислительной технике, может быть использовано в специализированных цифровых устройствах для обработки данных и является усовершенствованием изобретения по авт. св. № 1278834.

Цель изобретения - повышение достоверности работы устройства.

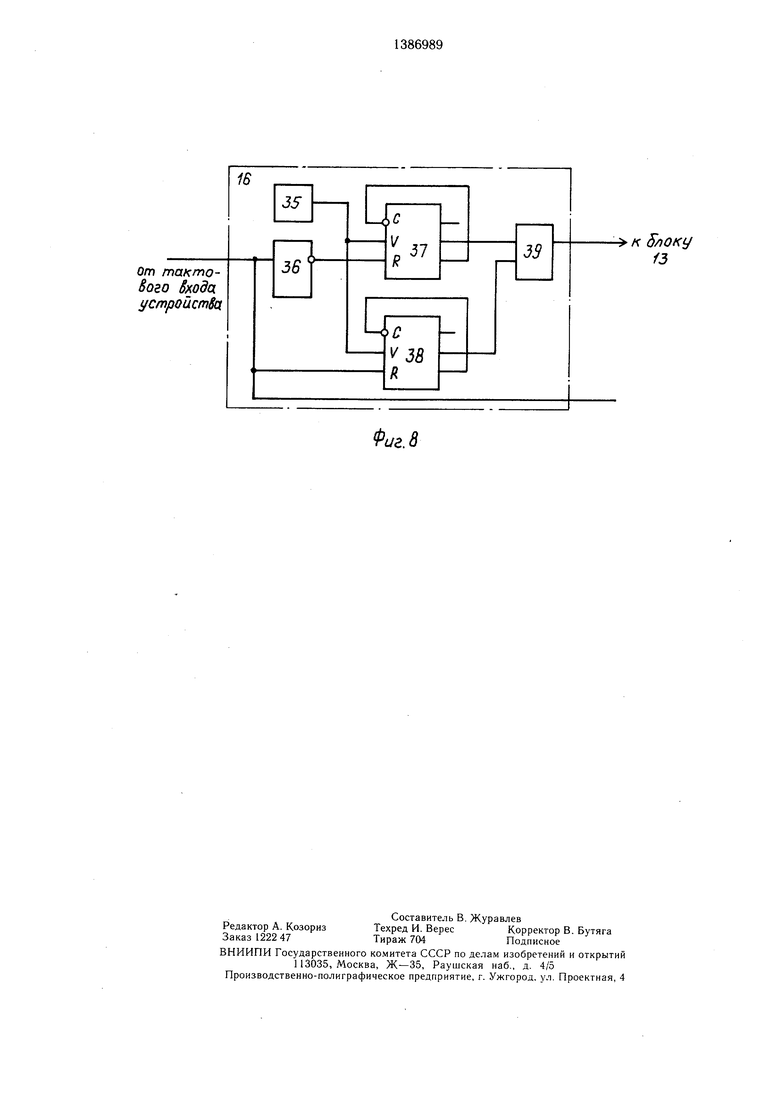

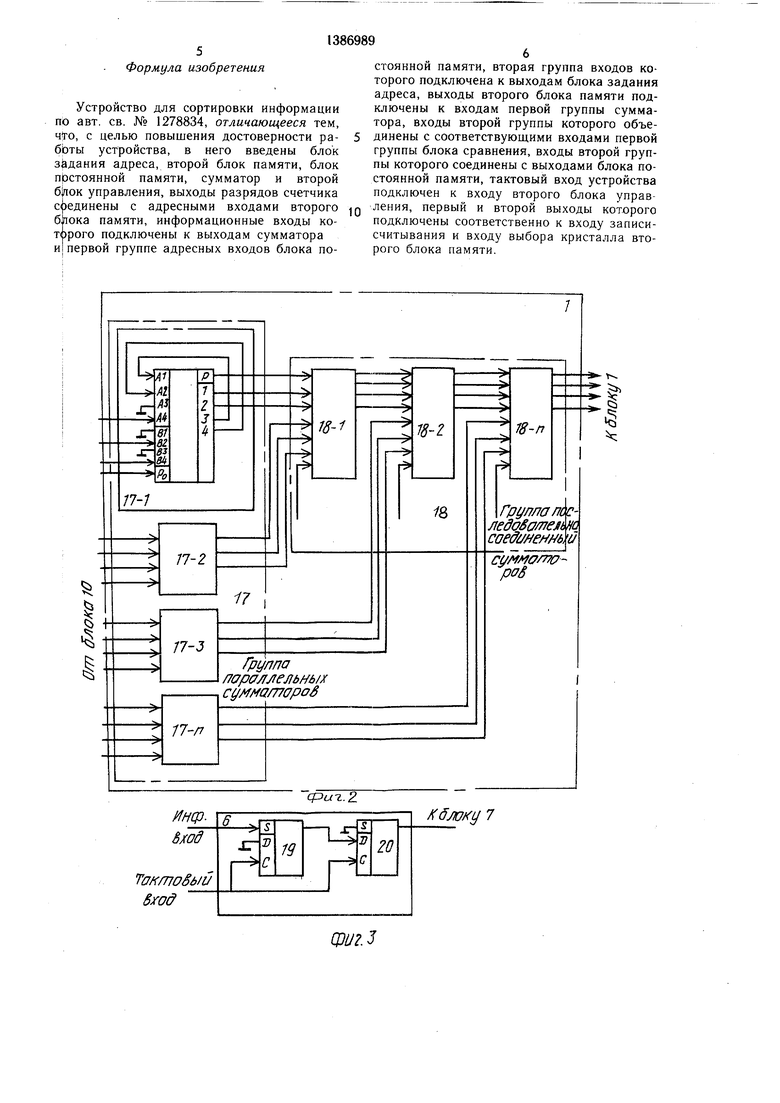

На фиг. 1 показана блок-схема устройства для сортировки информации; на фиг. 2 - схема блока анализа количества единиц; на фиг. 3 - схема блока синхронизации; на фиг. 4 - схема первого блока памяти; на фиг. 5 - схема первого блока управления; на фиг. б - схема регистра; на фиг. 7 - схема блока задания

564 ИП2, выдает на выходе потенциал логического «О, так как нуль меньше числа, поданного на вторую группу входов блока 2 сравнения. После окончания импульса запуска, который приходит на установоч5 ный вход устройства, на информационный вход устройства начинает поступать информация в виде меняюш,ихся во времени нулей и единиц. Входная информация синхронизируется тактовыми импульсами в блоке син10 хронизации D-триггерами 19 и 20. Входная информация разделена во времени на п временных каналов. Для каждого временного канала в блоке 7 памяти отведена соответ- ствуюшая ячейка памяти в каждом из элементов 21 памяти. При первом импульсе

адреса; на фиг. 8 - схема второго блока 5 запуска информация записывается в элемент управления.21 памяти блока 7 памяти, номер которого

Устройство (фиг. 1) содержит блок 1 ана- определяется кодом на выходах счетчика лиза количества единиц, блок 2 сравнения, 22 первого блока 8 управления. Этот код триггер 3 результата, первый 4 и второй 5 обуславливает сигнал на одном из выходов элементы задержки, блок б синхронизации б, -,„ дешифратора 23.

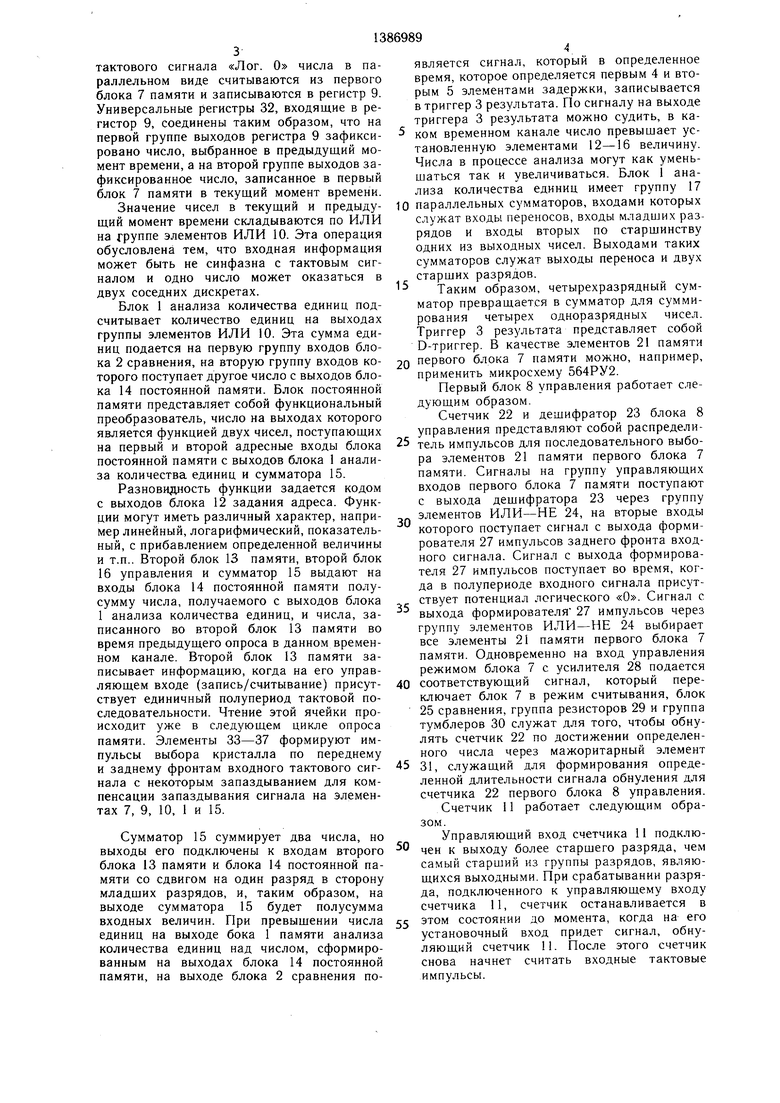

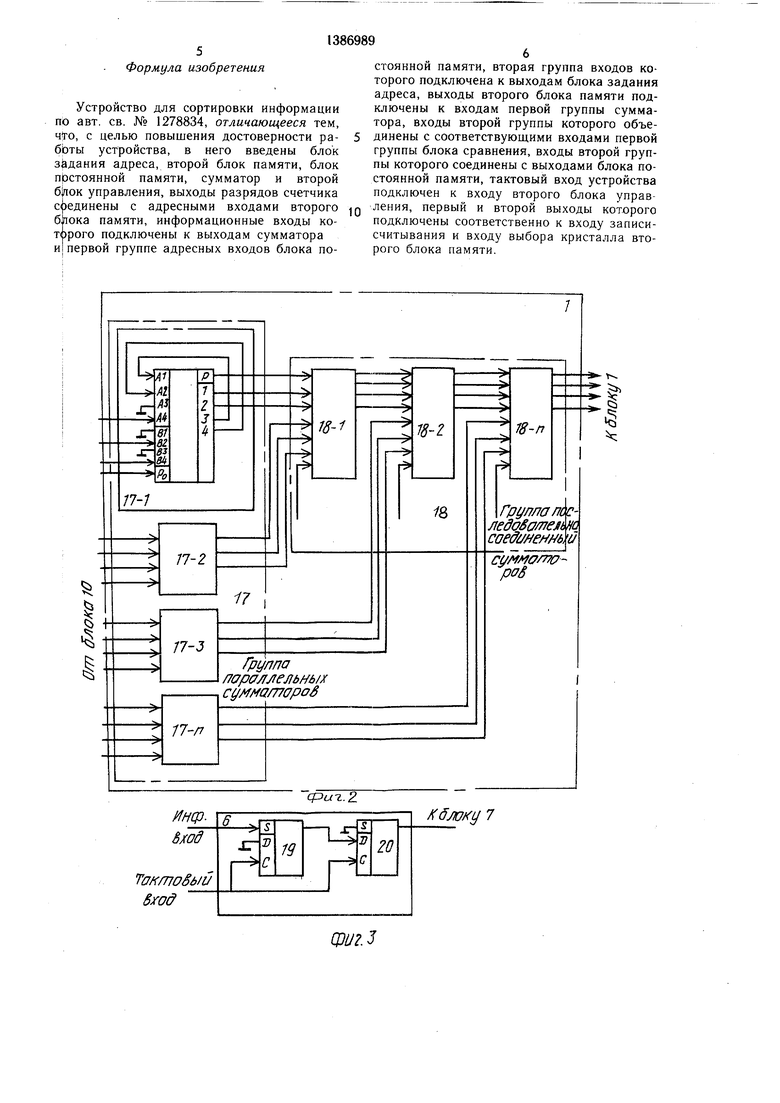

Сигнал на выходе блока 8 управления является сигналом выбора кристалла для элемента 21 памяти первого блока 7 памяти. Таким образом, информация первого времен1 первый блок 7 памяти, первый блок 8 управ- I ления, регистр 9, группу элементов ИЛИ 10, I счетчик 11, блок 12 задания адреса, второй I 13 блок памяти, блок 14 постоянной памяти, I сумматор 15 и второй блок 16 управления. I Блок 1 анализа количества единиц (фиг. 2) содержит группу 17 параллельных : сумматоров и группу 18 последовательно соединенных сумматоров.

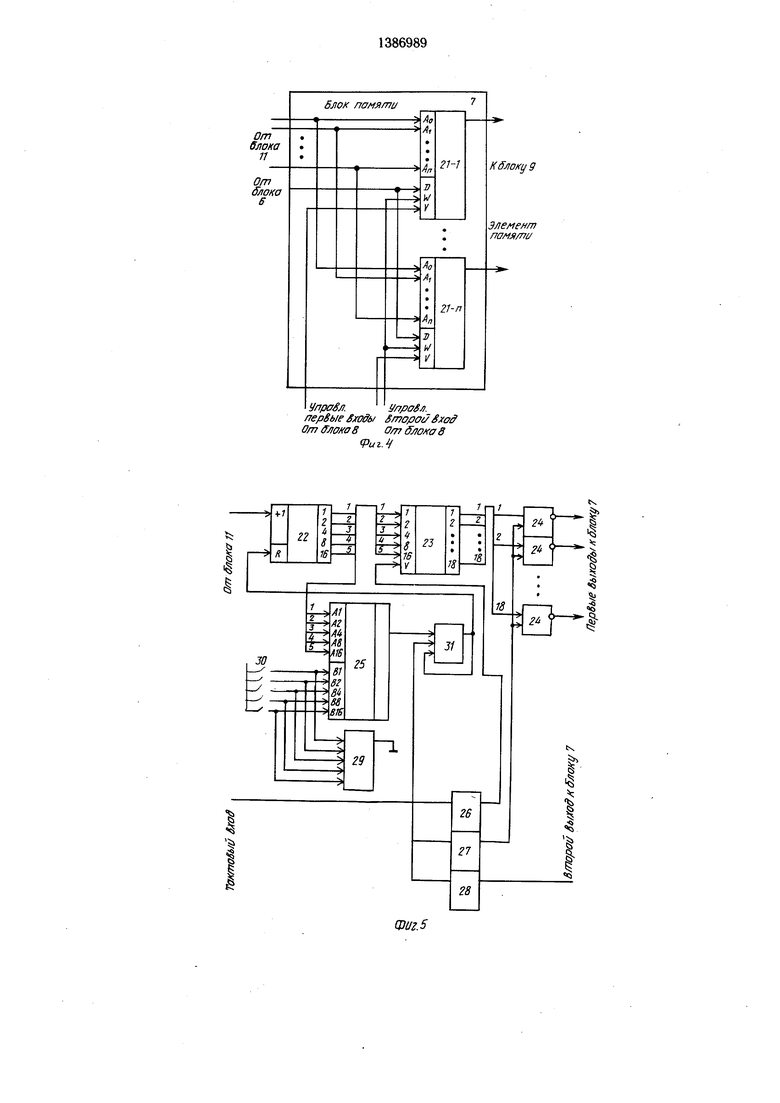

Блока 6 синхронизации (фиг. 3) содер- : жит два D-триггера 19 и 20. ; Первый блок 7 памяти (фиг. 4) содержит : группу элементов 21 памяти. Первый блог 8 управления (фиг. 5) содержит счетчик 22, дешифратор 23, группу элементов ИЛИ- НЕ 24, блок 25 сравнения, формирователь 26 импульсов по переднему фронту сигнала, формирователь 27 импульсов по заднему фронту сигнала, усилитель 28, группу 29 резисторов, группу 30 тумблеров, можоритар- ный элемент 31.

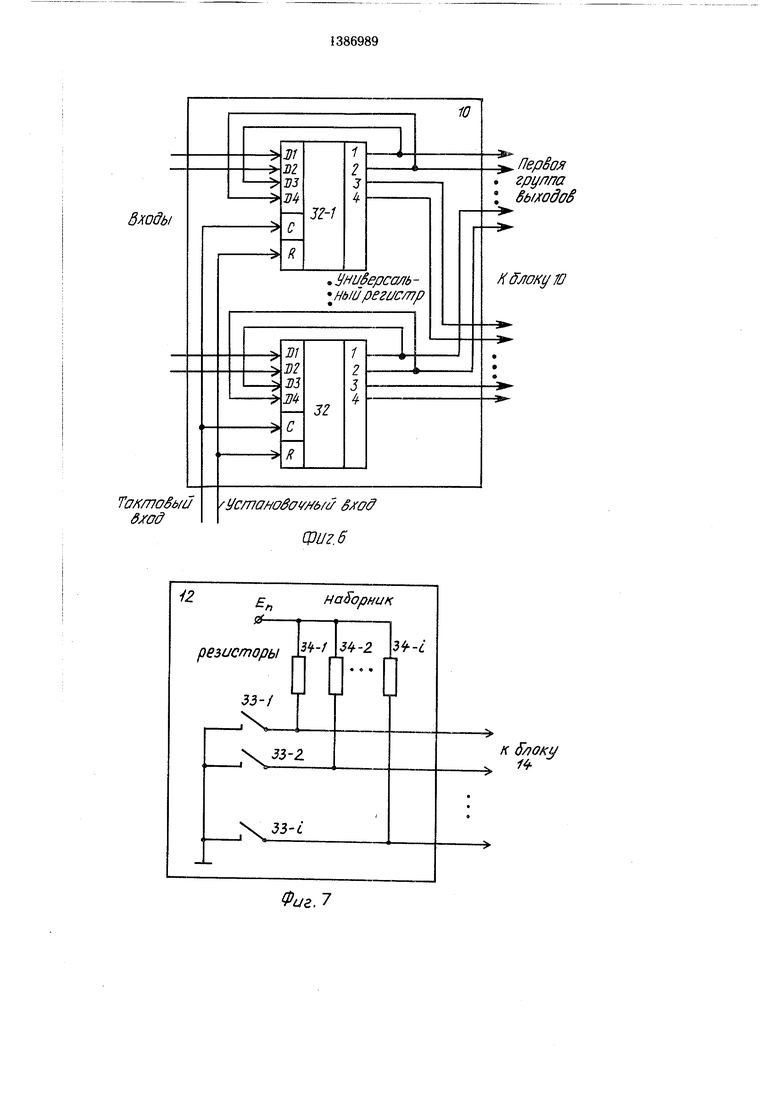

Регистр 9 (фиг. 6) состоит из универсальных регистров 32---1,...,32-т.

Блок 12 задания адреса (фиг. 7) содержит тумблеры 33-1, ..., 33-i, резисторы 34-1, ..., 34-i.

Второй блок 16 управления (фиг. 8) содержит генератор 35, элемент НЕ 36, форного канала записывается по первому адре- 25 су 00...00 в один из элементов памяти, номер которого определяется кодом на выходах счетчика 22 первого блока 8 управления. Этот процесс происходит в тот полупериод тактового сигнала, когда в тактовом сигнале присутствует потенциал логи- 30 ческой «1. Когда наступает потенциал логического «О в полупериоде входного тактового сигнала, первый блок 8 управления переключает блок 7 памяти таким образом, что блок 7 переключается з режим чтения, и выбранными оказываются все элементы 21 памяти. В следующий полупериод тактового сигнала «Лог. 1 происходит запись информации второго временного канала (код 00...00 на выходе счетчика) в тот же элемент 21 памяти блока 7 памяти.

Таким же образом информация со всех временных каналов записывается по соответствующему адресу в элемент 2(памяти первого блока 7 памяти. После этого на установочный вход устройства приходит слемирователи 37 и 38 импульсов, а также эле- 45 дующий импульс установки, от заднего

мент ИЛИ 39.

Устройство работает следуюпдим образом.

При включении устройства на установоч. ный вход устройства (а следовательно, на

установочные входы счетчика 11 и регистфронта старшего разряда счетчика 11 в счетчик 22 первого блока 8 управления записывается единица, в результате чего в режиме записи выбирается следующий по номеру элемент 21 памяти первого блока 7 пара 9) поступает импульс, устанавливающий 50 мяти. В течение некоторого определенного

счетчик 11 и регистр 9 в состояние, когда на их выходах устанавливается потенциал логических «О. На выходах группы элементов ИЛИ 10 также устанавливаются потенциалы логических «О, поэтому и на выхо- с дах блока I анализа количества единиц устанавливаются также потенциалы логических «О. Блок 2 сравнения, который может быть выполнен, например, на микропромежутка времени информацией заполняются все элементы 21 памяти первого блока 7 памяти. В блок 7 памяти записывается п чисел, количество которых определяется разрядностью счетчика 11. Разрядность этих чисел определяется количеством элементов 21 памяти первого блока 7 памяти и разрядностью счетчика 22 первого блока 8 управления. В определенный полупериод

1386989

564 ИП2, выдает на выходе потенциал логического «О, так как нуль меньше числа, поданного на вторую группу входов блока 2 сравнения. После окончания импульса запуска, который приходит на установочный вход устройства, на информационный вход устройства начинает поступать информация в виде меняюш,ихся во времени нулей и единиц. Входная информация синхронизируется тактовыми импульсами в блоке синхронизации D-триггерами 19 и 20. Входная информация разделена во времени на п временных каналов. Для каждого временного канала в блоке 7 памяти отведена соответ- ствуюшая ячейка памяти в каждом из элементов 21 памяти. При первом импульсе

запуска информация записывается в элемент 21 памяти блока 7 памяти, номер которого

ного канала записывается по первому адре- 5 су 00...00 в один из элементов памяти, номер которого определяется кодом на выходах счетчика 22 первого блока 8 управления. Этот процесс происходит в тот полупериод тактового сигнала, когда в тактовом сигнале присутствует потенциал логи- 0 ческой «1. Когда наступает потенциал логического «О в полупериоде входного тактового сигнала, первый блок 8 управления переключает блок 7 памяти таким образом, что блок 7 переключается з режим чтения, и выбранными оказываются все элементы 21 памяти. В следующий полупериод тактового сигнала «Лог. 1 происходит запись информации второго временного канала (код 00...00 на выходе счетчика) в тот же элемент 21 памяти блока 7 памяти.

Таким же образом информация со всех временных каналов записывается по соответствующему адресу в элемент 2(памяти первого блока 7 памяти. После этого на установочный вход устройства приходит следующий импульс установки, от заднего

фронта старшего разряда счетчика 11 в счетчик 22 первого блока 8 управления записывается единица, в результате чего в режиме записи выбирается следующий по номеру элемент 21 памяти первого блока 7 памяти. В течение некоторого определенного

мяти. В течение некоторого определенного

промежутка времени информацией заполняются все элементы 21 памяти первого блока 7 памяти. В блок 7 памяти записывается п чисел, количество которых определяется разрядностью счетчика 11. Разрядность этих чисел определяется количеством элементов 21 памяти первого блока 7 памяти и разрядностью счетчика 22 первого блока 8 управления. В определенный полупериод

3

тактового сигнала «Лог. О числа в параллельном виде считываются из первого блока 7 памяти и записываются в регистр 9. Универсальные регистры 32, входящие в ре- гистор 9, соединены таким образом, что на первой группе выходов регистра 9 зафиксировано число, выбранное в предыдущий момент времени, а на второй группе выходов зафиксированное число, записанное в первый блок 7 памяти в текущий момент времени.

является сигнал, который в определенное время, которое определяется первым 4 и вторым 5 элементами задержки, записывается в триггер 3 результата. По сигналу на выходе триггера 3 результата можно судить, в ка- 5 ком временном канале число превыщает установленную элементами 12-16 величину. Числа в процессе анализа могут как уменьшаться так и увеличиваться. Блок 1 анализа количества единиц имеет группу 17

Значение чисел в текущий и предыду- 10 параллельных сумматоров, входами которых

щий момент времени складываются по ИЛИ на группе элементов ИЛИ 10. Эта операция обусловлена тем, что входная информация может быть не синфазна с тактовым сигналом и одно число может оказаться в двух соседних дискретах.

Блок 1 анализа количества единиц подсчитывает количество единиц на выходах группы элементов ИЛИ 10. Эта сумма единиц подается на первую группу входов бло15

служат входы переносов, входы младших разрядов и входы вторых по старшинству одних из выходных чисел. Выходами таких сумматоров служат выходы переноса и двух старших разрядов.

Таким образом, четырехразрядный сумматор превращается в сумматор для суммирования четырех одноразрядных чисел. Триггер 3 результата представляет собой D-триггер. В качестве элементов 21 памяти

ка 2 сравнения, на вторую группу входов ко- 20 первого блока 7 памяти можно, например

торого поступает другое число с выходов блока 14 постоянной памяти. Блок постоянной памяти представляет собой функциональный преобразователь, число на выходах которого является функцией двух чисел, поступающих

применить микросхему 564РУ2.

Первый блок 8 управления работает следующим образом.

Счетчик 22 и дешифратор 23 блока 8 управления представляют собой распределина первый и второй адресные входы блока 25 тель импульсов для последовательного выбопостоянной памяти с выходов блока 1 анализа количества единиц и сумматора 15.

Разновидность функции задается кодом с выходов блока 12 задания адреса. Функции могут иметь различный характер, наприра элементов 21 памяти первого блока 7 памяти. Сигналы на группу управляющих входов первого блока 7 памяти поступают с выхода дешифратора 23 через группу элементов ИЛИ-НЕ 24, на вторые входы

мер линейный, логарифмический, показатель-которого поступает сигнал с выхода форминый, с прибавлением определенной величины и т.п.. Второй блок 13 памяти, второй блок 16 управления и сумматор 15 выдают на входы блока 14 постоянной памяти полусумму числа, получаемого с выходов блока 1 анализа количества единиц, и числа, записанного во второй блок 13 памяти во время предыдущего опроса в данном временном канале. Второй блок 13 памяти записывает информацию, когда на его управляющем входе (запись/считывание) присутствует единичный полупериод тактовой последовательности. Чтение этой ячейки происходит уже в следующем цикле опроса памяти. Элементы 33-37 формируют импульсы выбора кристалла по переднему и заднему фронтам входного тактового сигнала с некоторым запаздыванием для компенсации запаздывания сигнала на элементах 7, 9, 10, 1 и 15.

Сумматор 15 суммирует два числа, но выходы его подключены к входам второго блока 13 памяти и блока 14 постоянной памяти со сдвигом на один разряд в сторону младших разрядов, и, таким образом, на выходе сумматора 15 будет полусумма входных величин. При превышении числа единиц на выходе бока 1 памяти анализа количества единиц над числом, сформированным на выходах блока 14 постоянной памяти, на выходе блока 2 сравнения по35

40

рователя 27 импульсов заднего фронта входного сигнала. Сигнал с выхода формирователя 27 импульсов поступает во время, когда в полупериоде входного сигнала присутствует потенциал логического «О. Сигнал с выхода формирователя 27 импульсов через группу элементов ИЛИ-НЕ 24 выбирает все элементы 21 памяти первого блока 7 памяти. Одновременно на вход управления режимом блока 7 с усилителя 28 подается соответствующий сигнал, который переключает блок 7 в режим считывания, блок 25 сравнения, группа резисторов 29 и группа тумблеров 30 служат для того, чтобы обнулять счетчик 22 по достижении определенного числа через мажоритарный элемент

45 31, служащий для формирования определенной длительности сигнала обнуления для счетчика 22 первого блока 8 управления. Счетчик 11 работает следующим образом.

Управляющий вход счетчика 11 подклю чен к выходу более старщего разряда, чем самый старший из группы разрядов, являющихся выходными. При срабатывании разряда, подключенного к управляющему входу счетчика 11, счетчик останавливается в

55 этом состоянии до момента, когда на его установочный вход придет сигнал, обнуляющий счетчик 11. После этого счетчик снова начнет считать входные тактовые импульсы.

является сигнал, который в определенное время, которое определяется первым 4 и вторым 5 элементами задержки, записывается в триггер 3 результата. По сигналу на выходе триггера 3 результата можно судить, в ка- ком временном канале число превыщает установленную элементами 12-16 величину. Числа в процессе анализа могут как уменьшаться так и увеличиваться. Блок 1 анализа количества единиц имеет группу 17

15

служат входы переносов, входы младших разрядов и входы вторых по старшинству одних из выходных чисел. Выходами таких сумматоров служат выходы переноса и двух старших разрядов.

Таким образом, четырехразрядный сумматор превращается в сумматор для суммирования четырех одноразрядных чисел. Триггер 3 результата представляет собой D-триггер. В качестве элементов 21 памяти

20 первого блока 7 памяти можно, например

первого блока 7 памяти можно, например

применить микросхему 564РУ2.

Первый блок 8 управления работает следующим образом.

Счетчик 22 и дешифратор 23 блока 8 управления представляют собой распределитель импульсов для последовательного выботель импульсов для последовательного выбора элементов 21 памяти первого блока 7 памяти. Сигналы на группу управляющих входов первого блока 7 памяти поступают с выхода дешифратора 23 через группу элементов ИЛИ-НЕ 24, на вторые входы

которого поступает сигнал с выхода форми5

0

рователя 27 импульсов заднего фронта входного сигнала. Сигнал с выхода формирователя 27 импульсов поступает во время, когда в полупериоде входного сигнала присутствует потенциал логического «О. Сигнал с выхода формирователя 27 импульсов через группу элементов ИЛИ-НЕ 24 выбирает все элементы 21 памяти первого блока 7 памяти. Одновременно на вход управления режимом блока 7 с усилителя 28 подается соответствующий сигнал, который переключает блок 7 в режим считывания, блок 25 сравнения, группа резисторов 29 и группа тумблеров 30 служат для того, чтобы обнулять счетчик 22 по достижении определенного числа через мажоритарный элемент

5 31, служащий для формирования определенной длительности сигнала обнуления для счетчика 22 первого блока 8 управления. Счетчик 11 работает следующим образом.

Управляющий вход счетчика 11 подклю чен к выходу более старщего разряда, чем самый старший из группы разрядов, являющихся выходными. При срабатывании разряда, подключенного к управляющему входу счетчика 11, счетчик останавливается в

5 этом состоянии до момента, когда на его установочный вход придет сигнал, обнуляющий счетчик 11. После этого счетчик снова начнет считать входные тактовые импульсы.

Формула изобретения

Устройство для сортировки информации по авт. св. № 1278834, отличающееся тем, что, с целью повышения достоверности ра- бЬты устройства, в него введены блок задания адреса, второй блок памяти, блок постоянной памяти, сумматор и второй 6jnoK управления, выходы разрядов счетчика соединены с адресными входами второго бЬока памяти, информационные входы которого подключены к выходам сумматора И первой группе адресных входов блока по

стоянной памяти, вторая группа входов которого подключена к выходам блока задания адреса, выходы второго блока памяти подключены к входам первой группы сумматора, входы второй группы которого объединены с соответствующими входами первой группы блока сравнения, входы второй группы которого соединены с выходами блока постоянной памяти, тактовый вход устройства подключен к входу второго блока управления, первый и второй выходы которого подключены соответственно к входу записи- считывания и входу выбора кристалла второго блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сортировки информации | 1985 |

|

SU1278834A1 |

| Устройство для считывания информации с перфоносителя | 1987 |

|

SU1495827A1 |

| Устройство для сортировки чисел | 1987 |

|

SU1441385A1 |

| Устройство для контроля памяти | 1981 |

|

SU985831A1 |

| Устройство для сортировки цифровых сигналов | 1990 |

|

SU1805464A1 |

| Цифровой демодулятор сигналов относительной фазовой манипуляции | 1986 |

|

SU1374443A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1001182A1 |

| Устройство для считывания информации с перфоносителя | 1986 |

|

SU1388914A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Медианный рекурсивный фильтр | 1988 |

|

SU1654837A1 |

Изобретение относится к вычислительной технике и автоматике, может быть использовано в специализированных цифровых устройствах для обработки данных и является усовершенствованием устройства по авт. св. № 1278834. Целью изобретения является повышение достоверности работы устройства. Устройство содержит блок I анализа количества единиц, блок 2 сравнения, триггер 3 результата, первый 4 и второй 5 элемент задержки, блок 6 синхронизации, первый 7 и второй 13 блоки памяти, первый 8 и второй 16 блоки управления, регистр 9, группу элементов ИЛИ 10, счетчик II, блок 12 задания адреса, блок 14 постоянной памяти, сумматор 15. Входная информация через блок синхронизации накапливается в первом блоке памяти, блок анализа количества единиц через регистр и группу элементов ИЛИ подсчитывает количество накопленных единиц, блок сравнения сравнивает посчитанное количество единиц с числом, которое является функцией этого числа в предыдущем опросе, причем характер функциональной зависимости можно изменять путем набора соответствующего кода в блоке задания адреса. 8 ил. i (Л

сри-г.2.

CPU 2.3

первые S/nopOi/Sxo От fJiOffoS o/n SjJOffa 8 Риг.

KffMny 9

Элемент noMfi/riL/

5}(оды

iZ

HaSopHUK

резисторы

ЭЗ-/

.

m-f Ш-2

.

33-2.

Фиг.7

Первая рулпа 6bfj(odoS

HffjJOHyju

к /}OKtJ

1

- К 5/)Оку f3

Риг. 8

| Устройство для сортировки информации | 1985 |

|

SU1278834A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-07—Публикация

1986-09-10—Подача