Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств ЭВМ я создании устройств цифровой фильтрации для обработки статистической информации.

Целью изобретения является повышение быстродействия медианного рекурсивного фильтра.

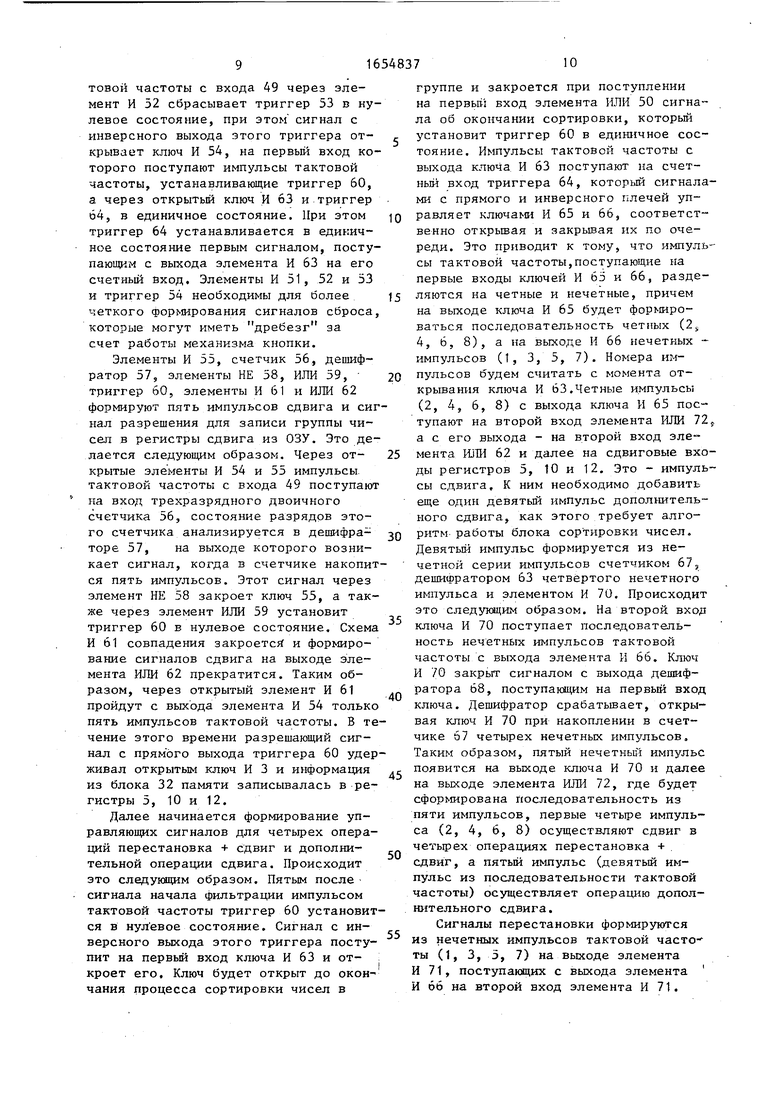

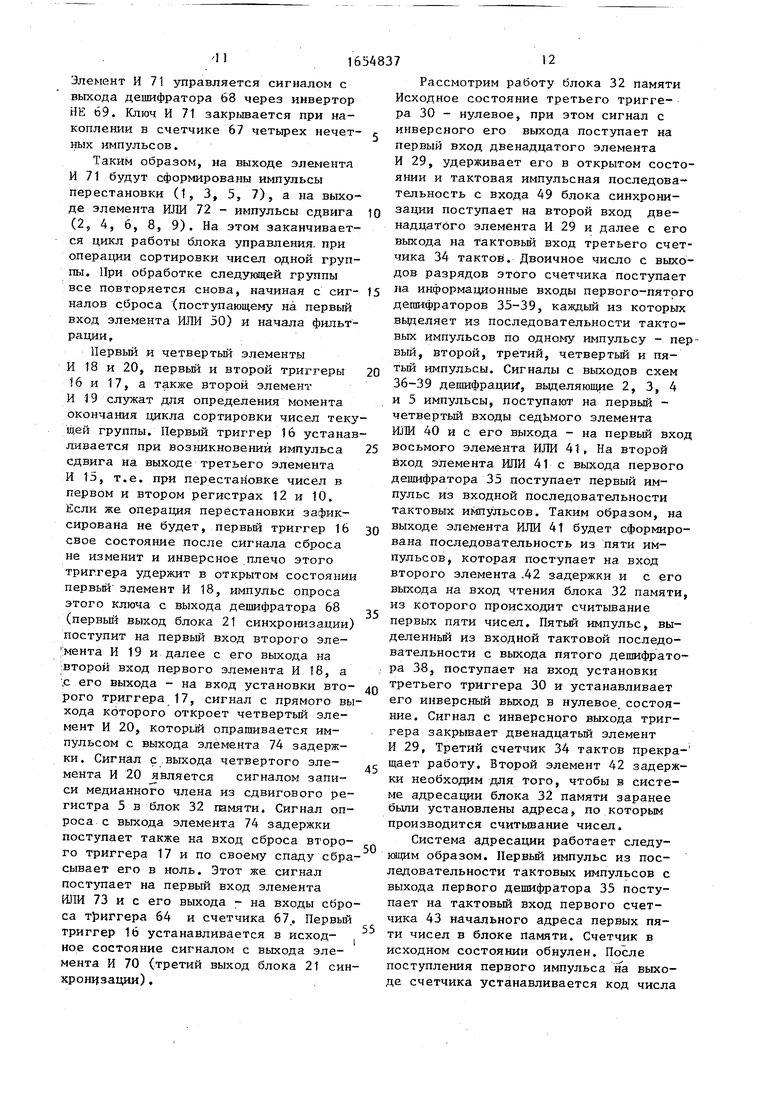

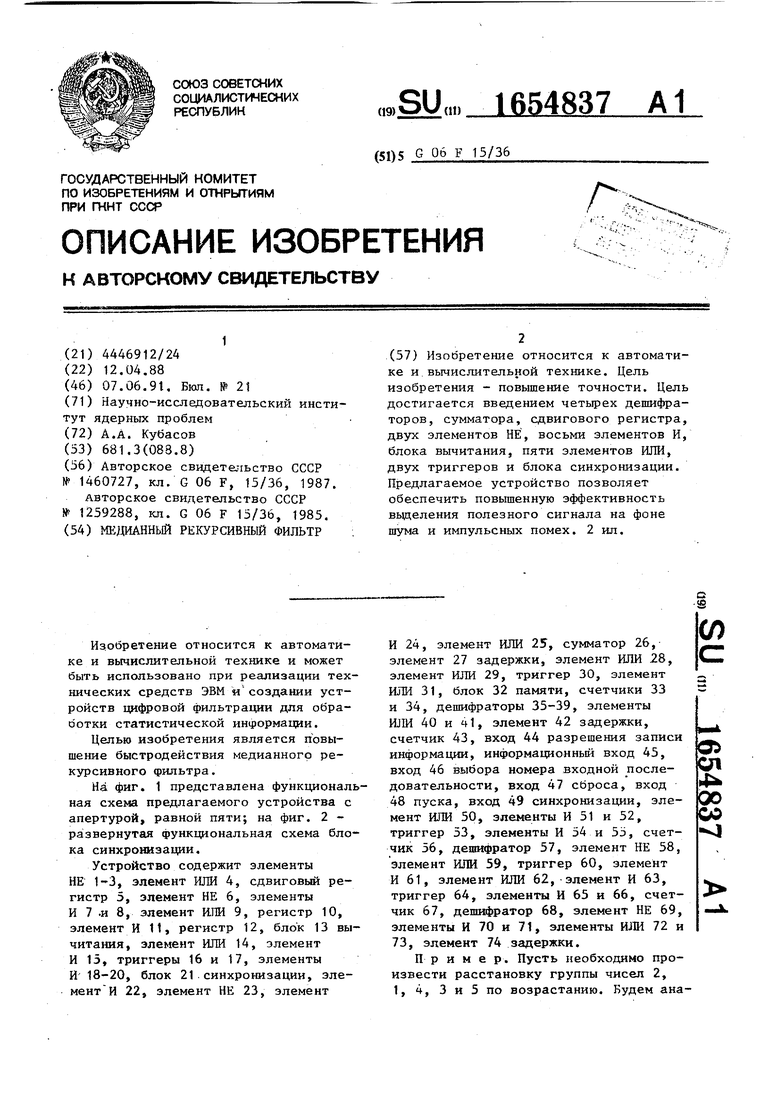

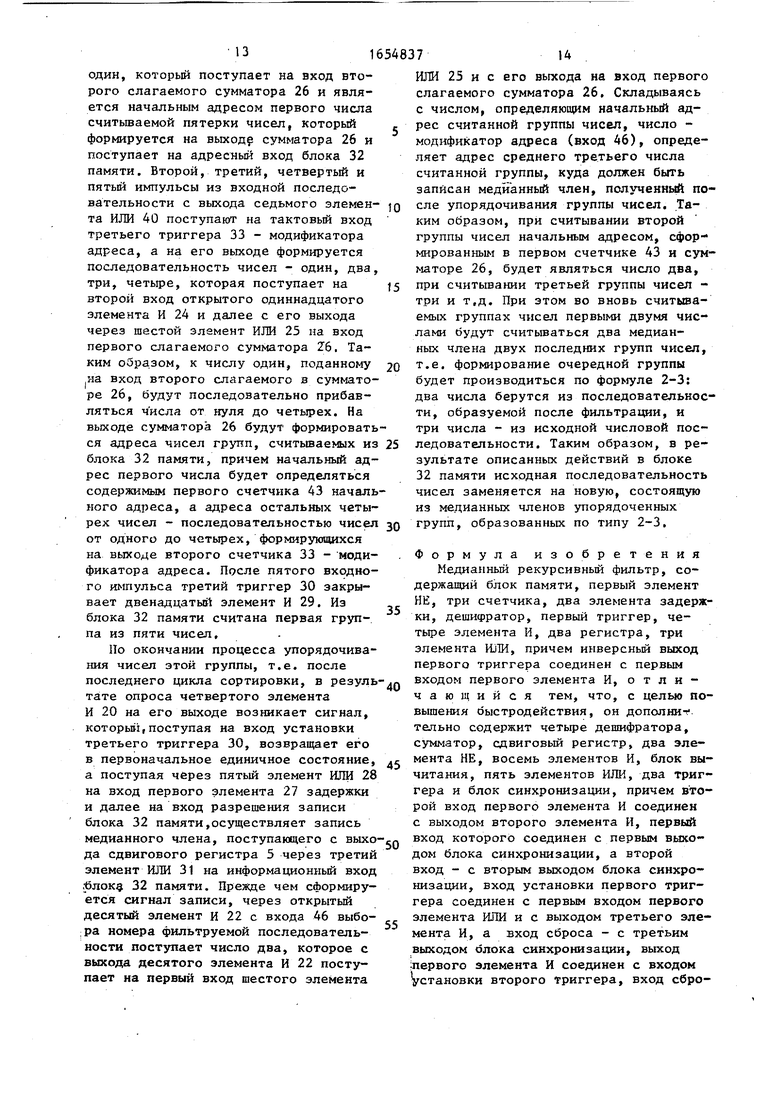

На фиг. 1 представлена функциональная схема предлагаемого устройства с апертурой, равной пяти; на фиг. 2 - развернутая функциональная схема блока синхронизации.

Устройство содержит элементы НЕ 1-3, элемент ИЛИ 4, сдвиговый регистр 5, элемент НЕ 6, элементы И 7 -и 8, элемент ИЛИ 9, регистр 10, элемент И 11, регистр 12, блок 13 вычитания, элемент ИЛИ 14, элемент И 15, триггеры 16 и 17, элементы И 18-20, блок 21 синхронизации, элемент И 22, элемент НЕ 23, элемент

И 24, элемент ИЛИ 25, сумматор 26, элемент 27 задержки, элемент ИЛИ 28, элемент ИЛИ 29, триггер 30, элемент ИЛИ 31, блок 32 памяти, счетчики 33 и 34, дешифраторы 35-39, элементы ИЛИ 40 и 41, элемент 42 задержки, счетчик 43, вход 44 разрешения записи информации, информационный вход 45, вход 46 выбора номера входной последовательности, вход 47 сброса, вход 48 пуска, вход 49 синхронизации, элемент ИЛИ 50, элементы И 51 и 52, триггер 53, элементы И 54 и 55, счетчик 56, дешифратор 57, элемент НЕ 58, элемент ИЛИ 59, триггер 60, элемент И 61, элемент ИЛИ 62, элемент И 63, триггер 64, элементы И 65 и 66, счетчик 67, дешифратор 68, элемент НЕ 69, элементы И 70 и 71, элементы ИЛИ 72 и 73, элемент 74 задержки.

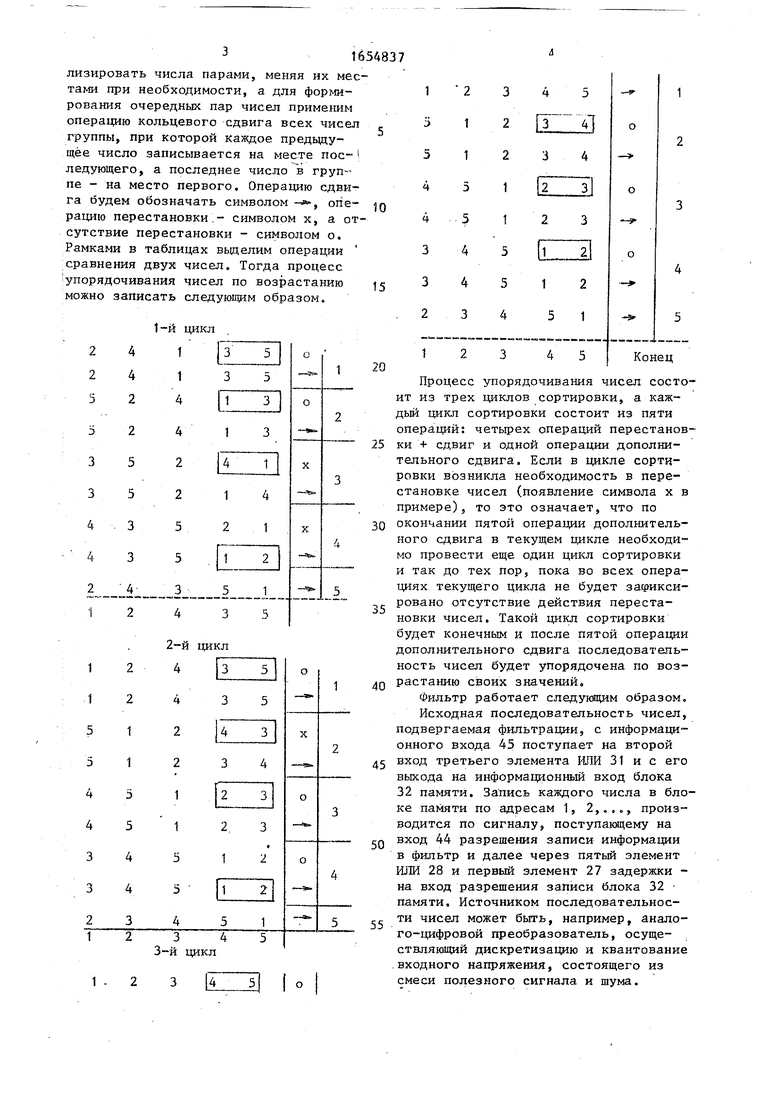

Пример. Пусть необходимо произвести расстановку группы чисел 2, 1, 4, 3 и 5 по возрастанию. Будем ана(Л

с

а ел

Јь 00 СО J

3165

лизировать числа парами, меняя их местами при необходимости, а для формирования очередных пар чисел применим операцию кольцевого сдвига всех чисел группы, при которой каждое предьзду- щёе число записывается на месте пос-1 ледующего, а последнее число в группе - на место первого. Операцию сдвига будем обозначать символом , операцию перестановки - символом х, а отсутствие перестановки - символом о. Рамками в таблицах выделим операции сравнения двух чисел. Тогда процесс упорядочивания чисел по возрастанию можно записать следующим образом.

1-й цикл

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для индикации | 1989 |

|

SU1667150A1 |

| Устройство для вывода графической информации | 1985 |

|

SU1339625A1 |

| Интерполятор | 1985 |

|

SU1413600A1 |

| Цифровой интерполятор | 1985 |

|

SU1259217A1 |

| Устройство для ранжирования чисел | 2022 |

|

RU2792182C1 |

| Устройство для вывода графической информации | 1987 |

|

SU1437908A1 |

| Устройство для сопряжения между абонентами | 1987 |

|

SU1411759A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Устройство для ввода информации | 1983 |

|

SU1109732A1 |

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - повышение точности. Цель достигается введением четырех дешифраторов, сумматора, сдвигового регистра, двух элементов НЕ, восьми элементов И, блока вычитания, пяти элементов ИЛИ, двух триггеров и блока синхронизации. Предлагаемое устройство позволяет обеспечить повышенную эффективность выделения полезного сигнала на фоне шума и импульсных помех. 2 ил.

2-й цикл

1-2 3 |4 5| | о |

5

0

5

0

5

0

5

Процесс упорядочивания чисел состоит из трех циклов сортировки, а каждый цикл сортировки состоит из пяти операций: четырех операций перестановки + сдвиг и одной операции дополнительного сдвига. Если в цикле сортировки возникла необходимость в перестановке чисел (появление символа х в примере), то это означает, что по окончании пятой операции дополнительного сдвига в текущем цикле необходимо провести еще один цикл сортировки и так до тех пор, пока во всех операциях текущего цикла не будет зафиксировано отсутствие действия перестановки чисел. Такой цикл сортировки будет конечным и после пятой операции дополнительного сдвига последовательность чисел будет упорядочена по возрастанию своих значений.

Фильтр работает следующим образом.

Исходная последовательность чисел, подвергаемая фильтрации, с информационного входа 45 поступает на второй вход третьего элемента ИЛИ 31 и с его выхода на информационный вход блока 32 памяти. Запись каждого числа в блоке памяти по адресам 1, 2,.,., производится по сигналу, поступающему на вход 44 разрешения записи информации в фильтр и далее через пятый элемент ИЛИ 28 и первый элемент 27 задержки - на вход разрешения записи блока 32 памяти. Источником последовательности чисел может быть, например, аналого-цифровой преобразователь, осуществляющий дискретизацию и квантование входного напряжения, состоящего из смеси полезного сигнала и шума.

10

20

51654837

Апертура фильтра равна пяти. Это означает, что исходная реализация разбивается на перекрывающиеся на одно число группы по пять чисел каждая, в каждой группе производится расстановка ее членов по возрастанию, определяется медианный член, который записывается в блок памяти на место среднего члена исходной группы.-В результате такой записи медианных членов в блок памяти исходная числовая последовательность будет заменяться на фильтрованную. При этом каждая очередная группа чисел будет состоять из трех чисел исходной реализации и двух чисел - медианных членов двух предыдущих групп.

Фильтрация начинается со считывания из блока 32 памяти первых пяти чисел и записи их по порядку в первый 12 и во второй 10 регистры и в третий, второй и первый разряды сдвигового регистра 5. Регистры 10 и 12 - одноразрядные и являются продолжением трехразрядного сдвигового регистра 5. С шестого выхода блока 21 синхронизации на первый вход восьмого элемента И 3 поступает сигнал, открывающий этот ключ. Числа, считываемые из блока 32 памяти, поступают на второй вход восьмого элемента И 3 и с его выхода через второй вход второго элемента ИЛИ 4 на информационный вход сдвигового регистра 5. При этом шестой элемент И 2 закрыт сигналом, поступающим на его первый вход с выхода первого элемента НЕ 1. Считываемые из блока 32 памяти числа переписываются из разряда в разряд сдвигового регист- 4Q pa 5 и далее через открытый по второму входу девятый элемент И 8 и четвертый элемент ИЛИ 9 записываются во второй регистр 10,а с его выхода - в первый регистр 12. Таким образом, первые пять чисел, считанные из блока 32 памяти, разместятся по порядку в регистрах 12, 10 и 5. Цикл считывания первой группы чисел из блока памяти за-

25

30

35

45

раций: перестановка содержимого первого и второго регистров 12 и 10 и в( случае, если число во втором регистре 10 больше числа, находящегося в первом регистре 12, сдвига к кольцу на один разряд вправо содержимого всех регистров 5, Ю и 12. Происходит это |Следующим образом. Число, содержащееся во втором регистре 10, поступает на вход уменьшаемого блока 13 вычитания. На вход вычитаемого этого блока поступает число с выхода первого регистра 12. Если число в регистре 10 больше числа в регистре 12, то сигнал с выхода блока 13 вычитания через открытый пятый элемент И 11, поступая на первый вход седьмого элемента И 7, открывает его, а поступая через второй инвертор НЕ 6 на второй вход, закрывает девятый элемент И 8. С седьмого выхода блока 21 синхронизации сигнал перестановки через открытый третий элемент И 15 поступает на первый вход первого элемента ИЛИ 14 и далее на входы синхронизации второго 10 и первого 12 регистров. При этом содержимое второго регистра 10 переписывается в первьй регистр 12, а прежнее содержимое регистра 12 через открытый седьмой элемент И 7 и четвертый элемент ИЛИ 9 записывается во второй регистр 10. Таким образом, числа, ранее находившиеся в регистрах 10 и 12, поменяются местами. Если содержимое второго регистра 10 не больше содержимого первого регистра 12, то операция перестановки не производится, так как с выхода блока 13 вычитания запрещающий сигнал поступает на первый вход третьего элемента И 15, закрывает его, и на выходе этого элемента не возникает сигнал сдвига, поступающий на его третий вход с седьмого выхода блока 21 синхронизации.

Далее следует операция кольцево - го сдвига на один разряд вправо содержимого всех регистров 5, 10 и 12.

кончен. При этом с шестого выхода бло- 50 Сдвиг осуществляется по большому колька 21 синхронизации на первый вход восьмого элемента И 3 поступит запрещающий сигнал, а сигнал с выхода первого элемента НЕ. 1, поступая на первый вход шестого элемента И 2 и вторые входы пятого и третьего элементов И 11 и 15, откроет их. Далее начина- ( ется цикл упорядочивания первых пяти чисел, который состоит из двух опе55

цу: сдвиговый регистр 5 - девятый элемент И 8 - четвертый элемент ИЛИ 9 - второй регистр 10 - первый регистр 12, шестой элемент И 2, второй элемент ИЛИ 4 и сдвиговый регистр 5. Такой сдвиг обеспечивается сигналом, формируемым на седьмом выходе блока 21 синхронизации и поступающим на тактовый вход сдвигового регистра 5, на

0

0

Q

5

0

5

5

раций: перестановка содержимого первого и второго регистров 12 и 10 и в( случае, если число во втором регистре 10 больше числа, находящегося в первом регистре 12, сдвига к кольцу на один разряд вправо содержимого всех регистров 5, Ю и 12. Происходит это |Следующим образом. Число, содержащееся во втором регистре 10, поступает на вход уменьшаемого блока 13 вычитания. На вход вычитаемого этого блока поступает число с выхода первого регистра 12. Если число в регистре 10 больше числа в регистре 12, то сигнал с выхода блока 13 вычитания через открытый пятый элемент И 11, поступая на первый вход седьмого элемента И 7, открывает его, а поступая через второй инвертор НЕ 6 на второй вход, закрывает девятый элемент И 8. С седьмого выхода блока 21 синхронизации сигнал перестановки через открытый третий элемент И 15 поступает на первый вход первого элемента ИЛИ 14 и далее на входы синхронизации второго 10 и первого 12 регистров. При этом содержимое второго регистра 10 переписывается в первьй регистр 12, а прежнее содержимое регистра 12 через открытый седьмой элемент И 7 и четвертый элемент ИЛИ 9 записывается во второй регистр 10. Таким образом, числа, ранее находившиеся в регистрах 10 и 12, поменяются местами. Если содержимое второго регистра 10 не больше содержимого первого регистра 12, то операция перестановки не производится, так как с выхода блока 13 вычитания запрещающий сигнал поступает на первый вход третьего элемента И 15, закрывает его, и на выходе этого элемента не возникает сигнал сдвига, поступающий на его третий вход с седьмого выхода блока 21 синхронизации.

Далее следует операция кольцево - го сдвига на один разряд вправо содержимого всех регистров 5, 10 и 12.

Сдвиг осуществляется по большому коль

цу: сдвиговый регистр 5 - девятый элемент И 8 - четвертый элемент ИЛИ 9 - второй регистр 10 - первый регистр 12, шестой элемент И 2, второй элемент ИЛИ 4 и сдвиговый регистр 5. Такой сдвиг обеспечивается сигналом, формируемым на седьмом выходе блока 21 синхронизации и поступающим на тактовый вход сдвигового регистра 5, на

второй вход первого элемента ИЛИ 14 и с его выхода на входы синхронизации первого и второго регистров 12 и 10. Поскольку операция сдвига следует после операции перестановки содержимых регистров 10 и 12, в результате которой должно выполняться условие: число второго регистра 10 не больше числа первого регистра 12, то на выходе блока 13 вычитания появится сигнал, закрывающий пятый элемент И 11 и седьмой элемент И 7, а через второй элемент НЕ 6 открывающий девятый элемент И 8. Таким образом будет обеспечена возможность сдвига содержимого регистров по большому кольцу, после чего вновь будет проделана паря операций перестановка - сдвиг, В одном цикле сортировки проводится четыре пары операций перестановка - сдвиг после чего следует пятая операция дополнительного сдвига,

Каждая операция перестановки сопровождается сигналом сдвига на выходе третьего элемента И 15, который, поступая на вход установки первого триггера 16, переводит его в единичное состояние, а сигнал с его инверсного выхода закрывает первый элемент И 18. Это означает, что по окончании текущего цикла необходимо выполнить еще один цикл сортировки.Состояние второго триггера 17 опрашивается сигналом с выхода второго элемента И 19, поступающего на второй вход первого элемента И 18, управляемого сигналом с инверсного плеча первого триггера t60 До окончании каждого цикла сортировки первый триггер 16 устанавливается в нулевое состояние сигналом, поступающим на его вход сброса с третьего выхода блока 21 синхронизации. После окончания пятой операции дополнительного цикла сдвига, в течение которого не было зафиксировано ни одной операции перестановки, т.е. первый триггер 16 не устанавливался в единичное состояние (имеется в виду неиспользуемый прямой его выход), в,трех разрядах сдвигового регистра 5 и в регистрах 10 и 12 будут находиться пять чисел, расположенных по возрастанию их значений. Третий, медианный, член с выхода сдвигового регистра 5 поступает через третий элемент ИЛИ 31 в блок 32 памяти на место третьего члена первой группы чисел, считанной из памяти и подвергшейся сортировке. Из

я г,

е . 0и ое

10

15

20

25

6548378

блока .32 памяти считывается (Вторая группа чисел, записанная по адресам 2-6, заносится в регистры 5, 10 и 12 сдвига и циклы перестановки повторяются вновь.

Блок 21 синхронизации (фиг, 2), формирующий временную диаграмму работы фильтра, работает следующим образом.

Перед началом работы фильтра на вход 47 сигнала предварительного сбро са фильтра подается сигнал внешнего сброса, открывающий через элемент ИЛИ 50 и ключ И 51 и устанавливающий в нулевое состояние триггеры 60 и 64, Это же происходит и по сигналу записи в блок 32 памяти медианного члене, поступающего с выхода четвертого элемента И 20 (фиг . 1) на вход сброса блока 21 синхронизации (вход 47, фиг. 2) т.е. перед записью в регистры 5, 10 и 12 очередной группы чисел из блока 32 памяти. Все операции по сортировке чисел выполняются по сигналам тактовой частоты, поступающим на тактовый вход 49 блока синхронизации. Длительность сигналов сброса, поступающих на оба входа элемента ИЛИ 50, должна быть больше периода следования сигналов тактовой частоты. Например, сигнал внешнего сброса, поступа - ющий на вход 47, может формироваться нажатием кнопки. Таким образом, первый импульс тактовой частоты, следующий после появления сигнала сброса на выходе элемента ИЛИ 50, проходит через схему И 51 совпадения и устанавливает триггер 53 в единичное состояние.

Временная диаграмма в блоке управления начинает формироваться после поступления на вход 48 сигнала начала фильтрации. Эта команда может быть сформирована, например, нажатием кнои ки. Длительность этого сигнала больше периода следования импульсов тактовой частоты. Сигнал начала фильтрации должен следовать после окончания импульса сброса, поступающего на вход 47. Оба эти сигнала нужны один раз - перед началом фильтрации. Сигнал сбро30

35

40

45

50

са, поступающий на первый вход элемента ИЛИ 50 с входа 75 сброса блока 21 синхронизации формируется перед считыванием каждой группы чисел из блока памяти. Сигнал начала фильтра- . ции поступает на второй вход элемента И 52, открывает его и импульс тактовой частоты с входа 49 через элемент И 52 сбрасывает триггер 53 в нулевое состояние, при этом сигнал с инверсного выхода этого триггера открывает ключ И 54, на первый вход которого поступают импульсы тактовой частоты, устанавливающие триггер 60, а через открытый ключ И 63 и триггер 64, в единичное состояние. При этом триггер 64 устанавливается в единичное состояние первым сигналом, поступающим с выхода элемента И 63 на его счетный вход. Элементы И 51, 52 и 53 и триггер 54 необходимы для более четкого формирования сигналов сброса, которые могут иметь дребезг за счет работы механизма кнопки.

Элементы И 55, счетчик 56, дешифратор 57, элементы НЕ 58, ИЛИ 59, триггер 60, элементы И 61 и ИЛИ 62 формируют пять импульсов сдвига и сигнал разрешения для записи группы чисел в регистры сдвига из ОЗУ. Это делается следующим образом. Через открытые элементы И 54 и 55 импульсы тактовой частоты с входа 49 поступают на вход трехразрядного двоичного счетчика 56, состояние разрядов этого счетчика анализируется в дешифраторе 57, на выходе которого возникает сигнал, когда в счетчике накопится пять импульсов. Этот сигнал через элемент НЕ 58 закроет ключ 55, а также через элемент ИЛИ 59 установит триггер 60 в нулевое состояние. Схема И 61 совпадения закроется и формирование сигналов сдвига на выходе элемента ИЛИ 62 прекратится. Таким образом, через открытый элемент И 61 пройдут с выхода элемента И 54 только пять импульсов тактовой частоты. В течение этого времени разрешающий сигнал с прямого выхода триггера 60 удерживал открытым ключ И 3 и информация из блока 32 памяти записывалась в регистры 5, 10 и 12.

Далее начинается формирование управляющих сигналов для четырех операций перестановка + сдвиг и дополнительной операции сдвига. Происходит это следующим образом. Пятым после сигнала начала фильтрации импульсом тактовой частоты триггер 60 установится в нул евое состояние. Сигнал с инверсного выхода этого триггера поступит на первый вход ключа И 63 и откроет его. Ключ будет открыт до окончания процесса сортировки чисел в

0

5

0

5

0

5

0

5

0

5

группе и закроется при поступлении на первый вход элемента ИЛИ 50 сигнала об окончании сортировки, который установит триггер 60 в единичное состояние. Импульсы тактовой частоты с выхода ключа И 63 поступают на счетный вход триггера 64, который сигналами с прямого и инверсного плечей управляет ключами И 65 и 66, соответственно открывая и закрывая их по очереди. Это приводит к тому, что импульсы тактовой частоты,поступающие на первые входы ключей И 65 и 66, разделяются на четные и нечетные, причем на выходе ключа И 65 будет формироваться последовательность четных (2 4, 6, 8), а на выходе И 66 нечетных - импульсов (1, 3, 5, 7). Номера импульсов будем считать с момента открывания ключа И 63.Четные импульсы (2, 4, 6, 8) с выхода ключа И 65 поступают на второй вход элемента ИЛИ 72, а с его выхода - на второй вход элемента ИЛИ 62 и далее на сдвиговые входы регистров 5, 10 и 12. Это - импульсы сдвига, К ним необходимо добавить еще один девятый импульс дополнительного сдвига, как этого требует алгоритм работы блока сортировки чисел. Девятый импульс формируется из нечетной серии импульсов счетчиком 67s дешифратором 63 четвертого нечетного импульса и элементом И 70. Происходит это следующим образом. На второй вход ключа И 70 поступает последовательность нечетных импульсов тактовой частоты с выхода элемента И 66. Ключ И /0 закрыт сигналом с выхода дешифратора 68, поступающим на первый вход ключа. Дешифратор срабатывает, открывая ключ И 70 при накоплении в счетчике 67 четырех нечетных импульсов. Таким образом, пятый нечетный импульс появится на выходе ключа И 70 и далее на выходе элемента ИЛИ 72, где будет сформирована последовательность из пяти импульсов, первые четыре импульса (2, 4, 6, 8) осуществляют сдвиг в четырех операциях перестановка + сдвиг, а пятый импульс (девятый импульс из последовательности тактовой частоты) осуществляет операцию дополнительного сдвига.

Сигналы перестановки формируются из нечетных импульсов тактовой часто- ты (1, 3, 5, 7) на выходе элемента И 71, поступающих с выхода элемента И 66 на второй вход элемента И 71.

11

Элемент И 71 управляется сигналом с выхода дешифратора 68 через инвертор НЕ 69. Ключ И 71 закрывается при накоплении в счетчике 67 четырех нечетных импульсов.

Таким образом, на выходе элемента И 71 будут сформированы импульсы перестановки (1, 3, 5, 7), а на выходе элемента ИЛИ 72 - импульсы сдвига (2, 4, 6, 8, 9). На этом заканчивается цикл работы блока управления при операции сортировки чисел одной группы. При обработке следующей группы все повторяется снова, начиная с сигналов сброса (поступающему на первый вход элемента ИЛИ 50) и начала фильтрации.

Первый и четвертый элементы И 18 и 20, первый и второй триггеры 16 и 17, а также второй элемент И 19 служат для определения момента окончания цикла сортировки чисел текущей группы. Первый триггер 16 устанав165

ливается при возникновении импульса сдвига на выходе третьего элемента И 15, т.е. при перестановке чисел в первом и втором регистрах 12 и 10. Если же операция перестановки зафиксирована не будет, первый триггер 16 свое состояние после сигнала сброса не изменит и инверсное плечо этого триггера удержит в открытом состоянии первый элемент И 18, импульс опроса этого ключа с выхода дешифратора 68 (первый выход блока 21 синхронизации) поступит на первый вход второго эле- мента И 19 и далее с его выхода на второй вход первого элемента И 18, а .с его выхода - на вход установки второго триггера 17, сигнал с прямого выхода которого откроет четвертый элемент И 20, который опрашивается импульсом с выхода элемента 74 задержки. Сигнал с выхода четвертого элемента И 20 является сигналом записи медианного члена из сдвигового регистра 5 в блок 32 памяти. Сигнал опроса с выхода элемента 74 задержки поступает также на вход сброса второго триггера 17 и по своему спаду сбрасывает его в ноль. Этот же сигнал поступает на первый вход элемента ИЛИ 73 и с его выхода - на входы сброса триггера 64 и счетчика 67.. Первый триггер 16 устанавливается в исходное состояние сигналом с выхода элемента И 70 (третий выход блока 21 синхронизации) ,

10

15

20

25

4837 2

Рассмотрим работу блока 32 памяти Исходное состояние третьего триггера 30 - нулевое, при этом сигнал с инверсного его выхода поступает на первый вход двенадцатого элемента И 29, удерживает его в открытом состоянии и тактовая импульсная последовательность с входа 49 блока синхронизации поступает на второй вход двенадцатого элемента И 29 и далее с его выхода на тактовый вход третьего счетчика 34 тактов. Двоичное число с выходов разрядов этого счетчика поступает на информационные входы первого-пятрго дешифраторов 35-39, каждый из которых выделяет из последовательности тактовых импульсов по одному импульсу - пер вый, второй, третий, четвертый и пятый импульсы. Сигналы с выходов схем 36-39 дешифрации , выделяющие 2, 3, 4 и 5 импульсы, поступают на первый - четвертый входы седьмого элемента ИЛИ 40 и с его выхода - на первый вход восьмого элемента ИЛИ 41, На второй вход элемента ИЛИ 41 с выхода первого дешифратора 35 поступает первый импульс из входной последовательности тактовых импульсов. Таким образом, на выходе элемента ИЛИ 41 будет сформирована последовательность из пяти импульсов, которая поступает на вход второго элемента .42 задержки и с его выхода на вход чтения блока 32 памяти, из которого происходит считывание первых пяти чисел. Пятый импульс, выделенный из входной тактовой последовательности с выхода пятого дешифратора 38, поступает на вход установки третьего триггера 30 и устанавливает его инверсный выход в нулевое, состояние. Сигнал с инверсного выхода триггера закрывает двенадцатый элемент И 29, Третий счетчик 34 тактов прекра- щает работу. Второй элемент 42 задержки необходим для того, чтобы в системе адресации блока 32 памяти заранее были установлены адреса, по которым производится считывание чисел.

Система адресации работает следующим образом. Первый импульс из последовательности тактовых импульсов с выхода первого дешифратора 35 поступает на тактовый вход первого счетчика 43 начального адреса первых пяти чисел в блоке памяти. Счетчик в исходном состоянии обнулен. После поступления первого импульса на выходе счетчика устанавливается код числа

30

35

40

45

50

55

один, который поступает на вход второго слагаемого сумматора 26 и является начальным адресом первого числа считываемой пятерки чисел, который формируется на выход сумматора 26 и поступает на адресный вход блока 32 памяти. Второй, третий, четвертый и пятый импульсы из входной последовательности с выхода седьмого элемента ИЛИ 40 поступают на тактовый вход третьего триггера 33 - модификатора адреса, а на его выходе формируется последовательность чисел - один, два, три, четыре, которая поступает на второй вход открытого одиннадцатого элемента И 24 и далее с его выхода через шестой элемент ИЛИ 25 на вход первого слагаемого сумматора Z6. Таким образом, к числу один, поданному на вход второго слагаемого з сумматоре 26, будут последовательно прибавляться числа от нуля до четырех. На выходе сумматора 26 будут формироваться адреса чисел групп, считываемых из блока 32 памяти, причем начальный адрес первого числа будет определяться содержимым первого счетчика 43 начального адреса, а адреса остальных четырех чисел - последовательностью чисел от одного до четырех, формирующихся на выходе второго счетчика 33 - модификатора адреса. После пятого входного импульса третий триггер 30 закрывает двенадцатый элемент И 29. Из блока 32 памяти считана первая группа из пяти чисел.

По окончании процесса упорядочивания чисел этой группы, т.е. после последнего цикла сортировки, в резуль тате опроса четвертого элемента И 20 на его выходе возникает сигнал, которыи,поступая на вход установки третьего триггера 30, возвращает его в первоначальное единичное состояние, а поступая через пятый элемент ИЛИ 28 на вход первого элемента 27 задержки и далее на вход разрешения записи блока 32 памяти,осуществляет запись медианного члена, поступающего с выхода сдвигового регистра 5 через третий элемент ИЛИ 31 на информационный вход .блока 32 памяти. Прежде чем сформируется сигнал записи, через открытый десятый элемент И 22 с входа 46 выбора номера фильтруемой последовательности поступает число два, которое с выхода десятого элемента И 22 поступает на первый вход шестого элемента

o

5

0

5

Q с

0

5

0

5

ИЛИ 25 и с его выхода на вход первого слагаемого сумматора 26. Складываясь с числом, определяющим начальный адрес считанной группы чисел, число - модификатор адреса (вход 46), определяет адрес среднего третьего числа считанной группы, куда должен быть записан медианный член, полученный после упорядочивания группы чисел. Таким образом, при считывании второй группы чисел начальным адресом, сформированным в первом счетчике 43 и сумматоре 26, будет являться число два, при считывании третьей группы чисел - три и т.д. При этом во вновь считываемых группах чисел первыми двумя числами будут считываться два медианных члена двух последних групп чисел, т.е. формирование очередной группы будет производиться по формуле 2-3: два числа берутся из последовательности, образуемой после фильтрации, и три числа - из исходной числовой последовательности. Таким образом, в результате описанных действий в блоке 32 памяти исходная последовательность чисел заменяется на новую, состоящую из медианных членов упорядоченных групп, образованных по типу 2-3.

Формула изобретения Медианный рекурсивный фильтр, содержащий блок памяти, первый элемент НЕ, три счетчика, два элемента задержки, дешифратор, первый триггер, четыре элемента И, два регистра, три элемента ИЛИ, причем инверсный выход первого триггера соединен с первым входом первого элемента И, отличающийся тем, что, с целью повышения быстродействия, он дополни- тельно содержит четыре дешифратора, сумматор, сдвиговый регистр, два элемента НЕ, восемь элементов И, блок вычитания, пять элементов ИЛИ, два триггера и блок синхронизации, причем второй вход первого элемента И соединен с выходом второго элемента И, первый вход которого соединен с первым выходом блока синхронизации, а второй вход - с вторым выходом блока синхронизации, вход установки первого триггера соединен с первым входом первого элемента ИЛИ и с выходом третьего элемента И, а вход сброса - с третьим выходом блока синхронизации, выход первого элемента И соединен с входом VcTaHOBKH второго триггера, вход сброса которого соединен с первым входом четвертого элемента И и четвертым выходом блока синхронизации, а выход - вторым входом четвертого элемента И, первый вход третьего элемента И соединен с выходом вычитателя и первым Входом пятого элемента И, второй вход которого соединен с вторым входом i третьего элемента И, первым входом шестого элемента И и выходом первого Элемента НЕ, выход четвертого элемента И соединен с входом сброса блока Синхронизации, выход пятого элемента И - с входом второго элемента НЕ и первым входом седьмого элемента И, второй вход шестого элемента И - с вторым входом седьмого элемента И, Входом вычитаемого блока вычитания и выходом первого регистра, информаци- онный вход которого соединен с выходом второго регистра и входом умень- йаемого блока вычитания, а вход синхронизации - с входом синхронизации Второго регистра и выходом первого Элемента ИЛИ, второй вход которого соединен с тактовым входом сдвигового регистра и пятым выходом блока синхронизации, выход шестого элемента И Соединен с первым входом второго эле- мента ИЛИ, второй вход которого соединен с выходом восьмого элемента И, а выход - с информационным входом Сдвигового регистра, выход которого

соединен с первыми входами третьего

Элемента ИЛИ и девятого элемента И, второй вход которого соединен с выходом второго элемента НЕ, а выход - с Первым входом четвертого элемента ИЛИ второй вход которого соединен с выхо- дом седьмого элемента И, а выход - с информационным входом второго регистра, первый вход восьмого элемента И соединен с входом первого элемента НЕ и шестым выходом блока синхрониза- ции, а второй вход - с выходом блока памяти, второй вход третьего элемента ИЛИ соединен с информационным входом медианного фильтра, а выход - с информационным входом блока памяти, первый вход пятого элемента ИЛИ соединен с входом разрешения записи информации фильтра, второй вход - с входом третьего элемента НЕ, с первым

0

5

о з п

входом десятого элемента И и с выходом четвертого элемента И, подключенным к входу сброса третьего триггера, выход пятого элемента ИЛИ соединен с входом первого элемента задержки, выход которого соединен с входом разрешения записи блока памяти, второй вход десятого элемента И соединен с входом выбора номера фильтруемой последовательности фильтра, а выход - |с первым входом шестого элемента ИЛИ, второй вход которого соединен с выходом одиннадцатого элемента И, а выход - с входом первого слагаемого сумматора, вход второго слагаемого которого соединен с выходом первого счетчика, а выход сумматора соединен с адресным входом блока памяти, выход третьего элемента НЕ соединен с первым входом одиннадцатого элемента И, второй вход которого соединен с выходом второго счетчика, тактовый вход которого соединен с выходом седьмого элемента ИЛИ и первым входом восьмого элемента ИЛИ, второй вход которого соединен с тактовым входом первого счетчика и выходом первого дешифратора, а выход восьмого элемента ИЛИ соединен с входом второго элемента задержки, выход которого соединен с входом чтения блока памяти, инверсный выход третьего триггера соединен с первым входом двенадцатого элемента И, второй вход которого соединен с тактовым входом блока синхронизации и является входом фильтра, а выход двенадцатого элемента И соединен с тактовым входом третьего счетчика, выход которого соединен с информационными входами дешифраторов, выход второго дешифратора соединен с первым входом седьмого элемента ИЛИ, второй вход которого соединен с выходом третьего дешифратора, третий вход седьмого элемента ИЛИ соединен с выходом четвертого дешифратора, а четвертый вход - с выходом пятого дешифратора и входом установки третьего триггера, вход начала работы фильтра соединен с входом запуска блока синхронизации, третий вход третьего элемента И соединен с седьмым выходом блока синхронизации.

| Устройство для определения медианы | 1987 |

|

SU1460727A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для анализа случайных чисел | 1985 |

|

SU1259288A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-07—Публикация

1988-04-12—Подача