(89) BG 33401/BG 46425/31.01.80 148) 30.09.80

(21)7772150/24-24

(22)12.11.81

(46 P7.04.88. Бюл. №.13 (71) ВМЕИ Ленин (BG) (.72) Бонн Янков Янков и Лилян Илиев Николов (BG)

(53)68J.325 (088.8)

(54)ТРАНСЛЯТОР ЯЗЬЖОВ-ПРОГРА 1МИРО- ВАНИЯ

(57) Изобретение относится к вычислительной технике и предназначена для аппаратной трансляции языков программирования. Цель изобретения - расширение функциональных возможностей транслятора за счет транслирования различных языков произвольной конструкции. Транслятор содержит блок 1 микропрограммного управления, входной и вьходной счетчики

а мгг аая мал

РО-

чековия - лильравки

3S

3, 4, счетчик 5 адреса текущего символа, блок 6 оперативной памяти текущего символа, счетчик 9 внутренней метки, счетчик 10 промежуточного результата, реверсивные счетчики операндов 13 и операторов 17, регистр 20 адреса, блок 7 постоянной памяти пра-- вил трансляции, счетчик 8 адреса правила трансляции, блок регистров стековой памяти операндов 11 и операторов 15, блоки стековой памяти операндов 12 и операторов 16, мультиплексор операндов 14, дешифратор 18 операторов, блок 19 постоянной памяти функции предшествия, два регистра 21, 22 функции предшествия, схему 23 сравнения и регистр 24 текущего символа. Обмен между блоками осуществляется через шину 2 данных по соотве тствующим управляющим сигналам блока 1. 6 ил.

$

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синтаксически-управляемого перевода | 1982 |

|

SU1062721A1 |

| Устройство для обработки выражений языков программирования | 1974 |

|

SU519715A1 |

| Система для трансляции с проблемноориентированного языка | 1976 |

|

SU674028A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| ПЕРЕЗАПУСКАЕМЫЕ ТРАНСЛИРОВАННЫЕ КОМАНДЫ | 2001 |

|

RU2263949C2 |

| ФОРМУЛЬНЫЙ ПРОЦЕССОР С РАСШИРЕННЫМ СЛОВОМ СОСТОЯНИЯ | 1999 |

|

RU2149444C1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737510A1 |

| ФОРМУЛЬНЫЙ ПРОЦЕССОР С КОМАНДОПОДОБНЫМИ ЛОГИЧЕСКИМИ УПРАВЛЯЮЩИМИ ЭЛЕМЕНТАМИ | 1997 |

|

RU2143726C1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

Т т т

X 31 S2

i:o00

РР

«г/

Изобретение относится к вычислительной технике и может быть использовано для аппаратной трансляции языков программирования.

Известно вычислительное устройство, позволяющее осуществлять трансляцию языков программирования преимущественно программными средствами (Заявка Великобритании № 1407761, кл. G 06 F 15/20, .1975).

Однако устррйство имеет низкую скорость трансляции программ, написанных на проблемно-ориентированных языках, так как применение программ для трансляции ухудшает скорость трансляции.

Наиболее близким по технической сущности к изобретению является уст- ройство, содержащее блок микропрограммного управления, входной счетчик, выходной счетчик, счетчик адреса текущего символа, блок оперативной памяти текущего символа, счетчик внутренней метки, счетчик промежу точного результата, реверсивные счетчики операндов и операторов и регист адреса, причем выход счетчика адреса текущего символа подключен к адресному входу блока оперативной памяти текущего символа (Авторское свидетельство СССР № 674028, кл. G 06 F 15/38, 1976).

Недостатком известного устройства является то, что оно не позволяет изменять входные и выходные языки, т.е. реализовать трансляцию нескольких языков на одной аппаратуре. Кроме того, с помощью устройства могут быть транслированы только выражения в языках -высокого уровня.

Целью изобретения является расширение функциональных возможностей за счет транслирования различных языков произвольной конструкции.

Поставленная цель достигается путем перенастройки транслятора для работы с различными входными и объектными языками посредством смены содержимого постоянных запоминающих устройств.

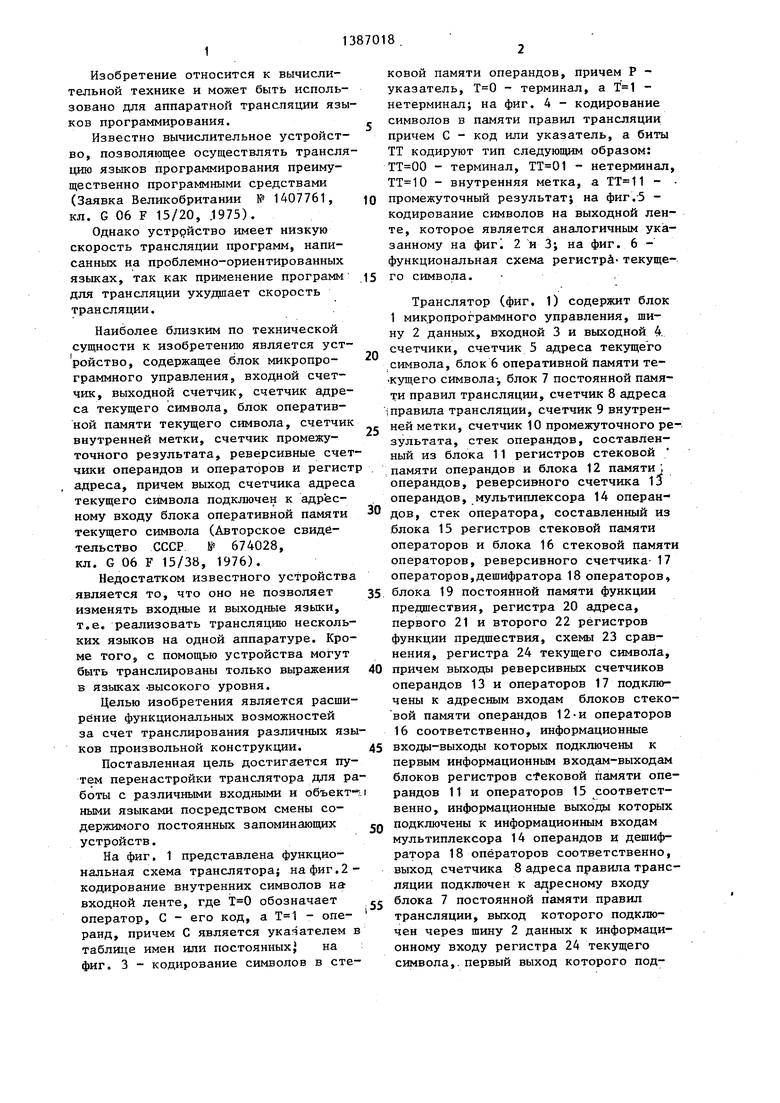

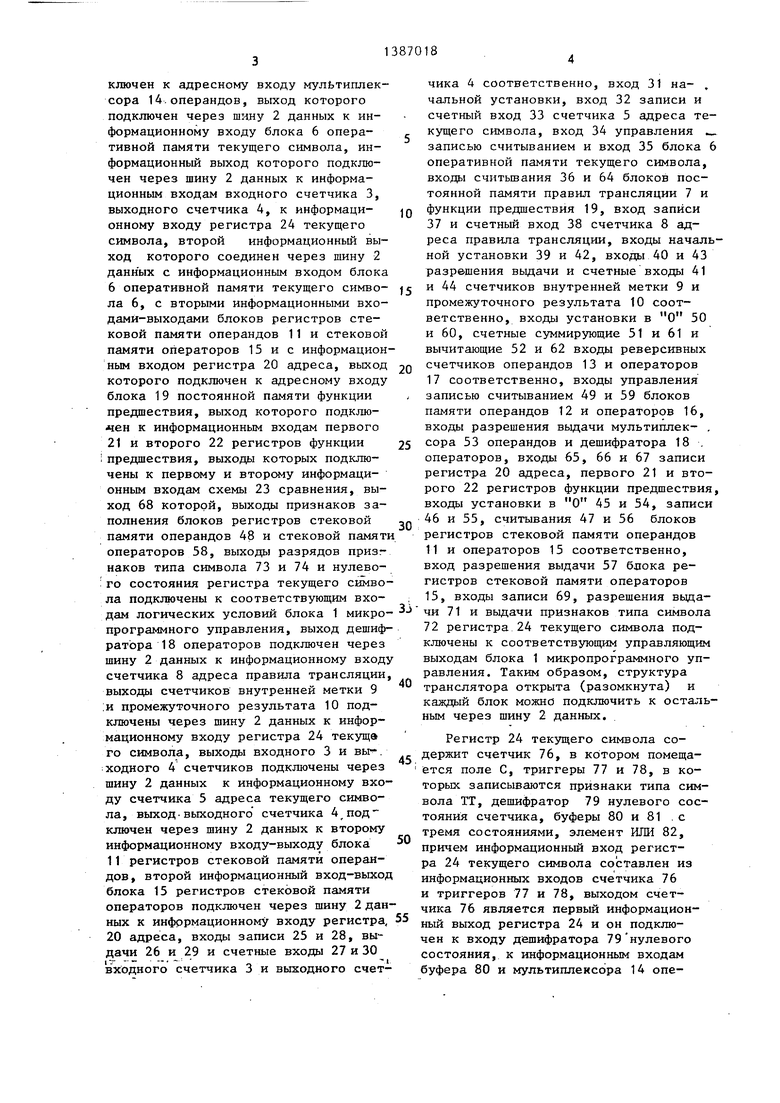

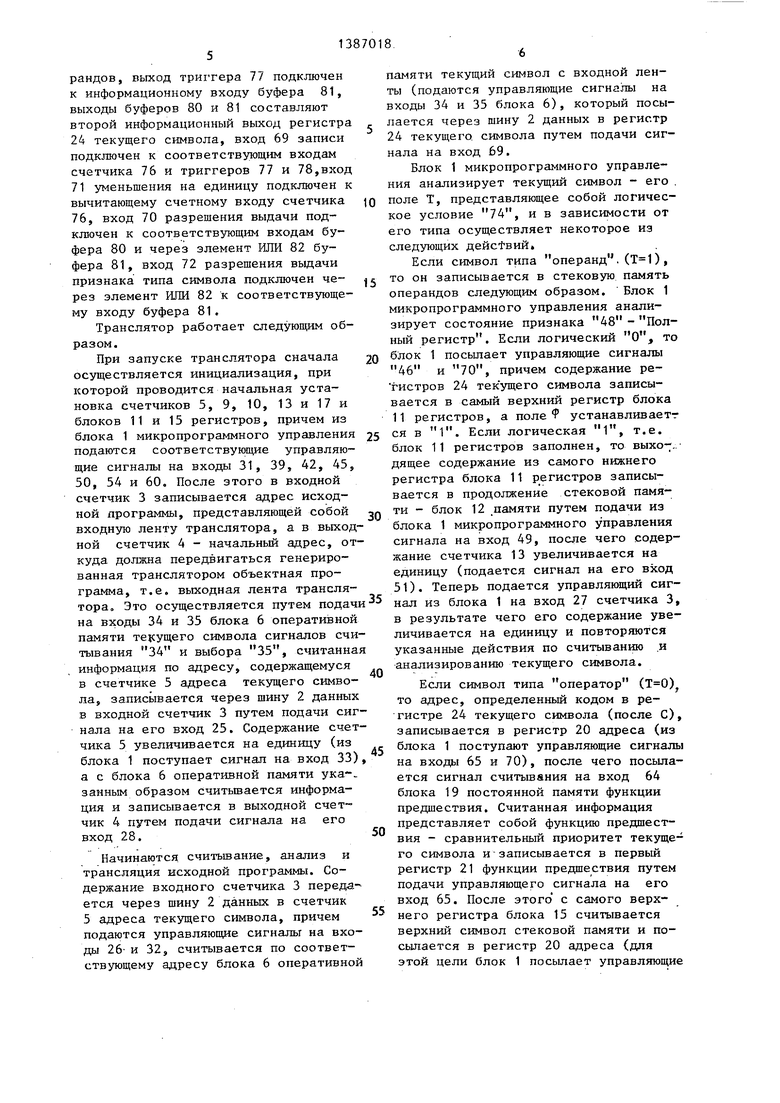

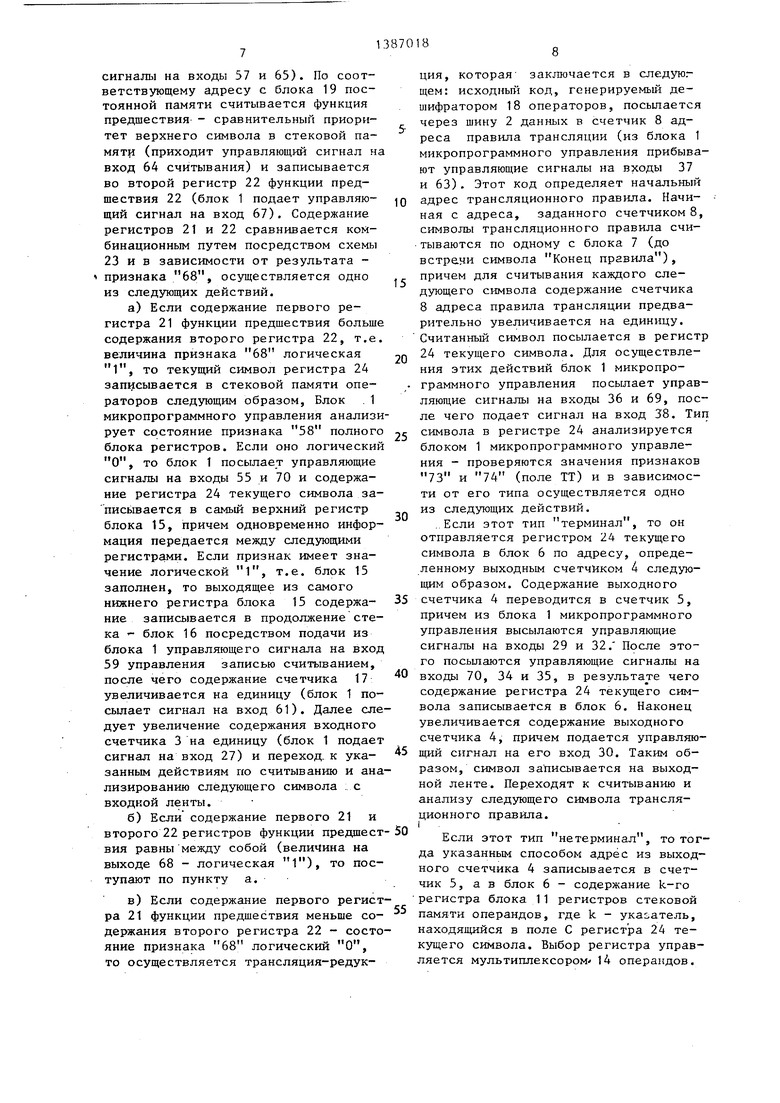

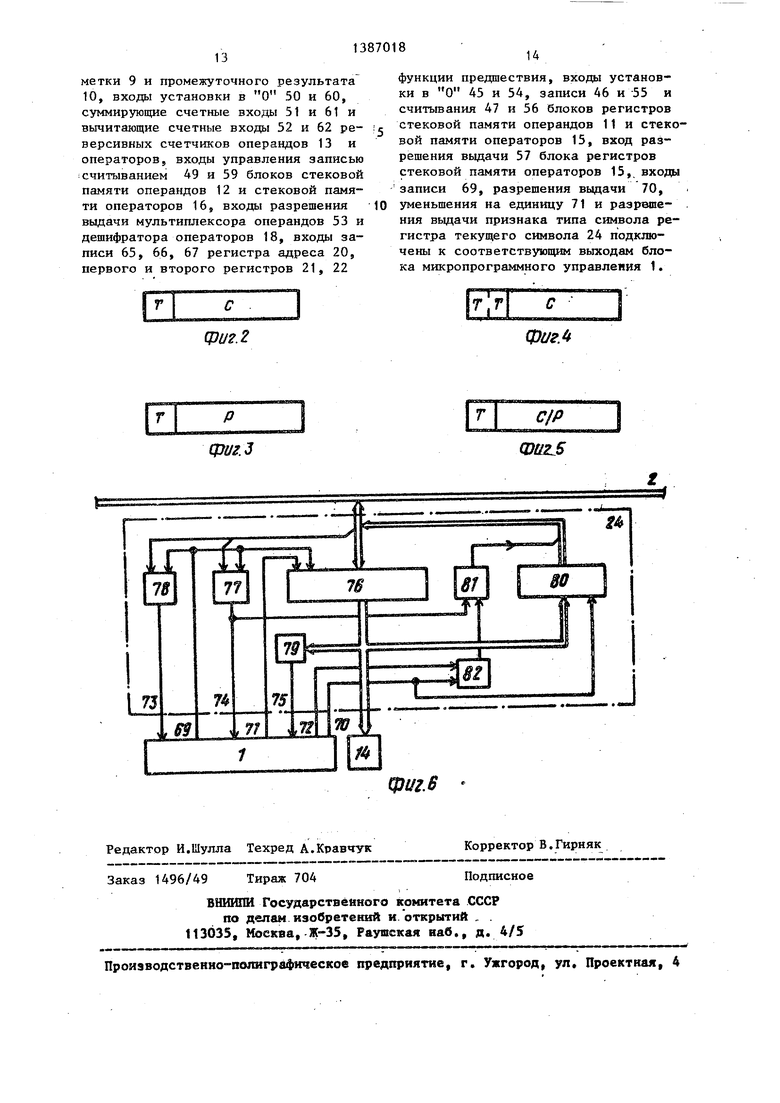

На фиг, 1 представлена функциональная схема транслятора на фиг.2- кодирование внутренних символов на входной ленте, где обозначает оператор, С - его код, а - one- ранд, причем С является указателем в таблице имен или постоянных} на фиг. 3 - кодирование символов в сте0

5

Q

5

0

5 0

5

Q

с

ковой памяти операндов, причем Р указатель, - терминал, а - нетерминал; на фиг. 4 - кодирование символов в памяти правил трансляции причем С - код или указатель, а биты ТТ кодируют тип следующим образом: - терминал, - нетерминал, - внутренняя метка, а - - промежуточный результат; на фиг.5 - кодирование символов на выходной ленте, которое является аналогичньм указанному на фиг 2 и 3; на фиг. 6 - функциональная схема регистр - текущего символа.

Транслятор (фиг. 1) содержит блок 1 микропрограммного управления, шину 2 данных, входной 3 и выходной 4. счетчики, счетчик 5 адреса текущего символа, блок 6 оперативной памяти те- кущего символа-, блок 7 постоянной памяти правил трансляции, счетчик 8 адреса 1 правила трансляции, счетчик 9 внутренней метки, счетчик 10 промежуточного результата, стек операндов, составленный из блока 11 регистров стековой памяти операндов и блока 12 памяти; операндов, реверсивного счетчика 13 операндов, мультиплексора 14 операндов, стек оператора, составленный из блока 15 регистров стековой памяти операторов и блока 16 стековой памяти операторов, реверсивного счетчика- 17 операторов,дешифратора 18 операторов, блока 19 постоянной памяти функции предшествия, регистра 20 адреса, первого 21 и второго 22 регистров функции предшествия, схемы 23 сравнения, регистра 24 текущего символа, причем вьгходы реверсивных счетчиков операндов 13 и операторов 17 подключены к адресным входам блоков стековой памяти операндов 12-и операторов 16 соответственно, информационные входы-выходы которых подключены к первым информационным входам-выходам блоков регистров стековой памяти операндов 11 и операторов 15 соответственно, информационные выходы которых подключены к информационным входам мультиплексора 14 операндов и дешифратора 18 операторов соответственно, выход счетчика 8 адреса правила трансляции подключен к адресному входу блока 7 постоянной памяти правил трансляции, выход которого подключен через шину 2 данных к информационному входу регистра 24 текущего символа,, первый выход которого подключей к адресному входу мультиплексора 14.операндов, выход которого подключен через шину 2 данных к информационному входу блока 6 оперативной памяти текущего символа, информационный выход которого подключен через шину 2 данных к информационным входам входного счетчика 3, выходного счетчика 4, к информаци- онному входу регистра 24 текущего символа, второй информационный выход которого соединен через шину 2 данных с информационным входом блока 6 оперативной памяти текущего симво- ла 6, с вторыми информационными входами-выходами блоков регистров стековой памяти операндов 11 и стековой памяти операторов 15 и с информационным входом регистра 20 адреса, выход которого подключен к адресному входу блока 19 постоянной памяти функции предшествия, выход которого подключен к информационным входам первого 21 и второго 22 регистров функции

: предшествия, выходы которых подключены к первому и второму информаци- онньш входам схемы 23 сравнения, выход 68 которой, выходы признаков заполнения блоков регистров стековой памяти операндов 48 и стековой памяти операторов 58, выходы разрядов призг каков типа символа 73 и 74 и нулево:го состояния регистра текущего символа подключены к соответствующим вхо- дам логических условий блока 1 микро- программного управления, выход дешифратора 18 операторов подключен через шину 2 данных к информационному входу счетчика 8 адреса правила трансляции, выходы счетчиков внутренней метки 9

и промежуточного результата 10 подключены через шину 2 данных к информационному входу регистра 24 текуща го символа, выхода входного 3 и вьг-.

входного 4 счетчиков подключены через шину 2 данных к информационному входу счетчика 5 адреса текущего символа, выход-выходного счетчика ключен через шину 2 данных к второму информационному входу-выходу блока 11 регистров стековой памяти операндов, второй информационный вход-выход блока 15 регистров стековой памяти операторов подключен через шину 2 данных к информационному входу регистра, 20 адреса, входы записи 25 и 28, выдачи 26 и 29 и счетные входы 27 и 30 входного счетчика 3 и выходного счет

Q 5 0 5

Q

, -

0

5

чика 4 соответственно, вход 31 начальной установки, вход 32 записи и счетный вход 33 счетчика 5 адреса текущего символа, вход 34 управления записью считыванием и вход 35 блока 6 оперативной памяти текущего символа, входы считывания 36 и 64 блоков постоянной памяти правил трансляции 7 и функции предшествия 19, вход записи 37 и счетный вход 38 счетчика 8 адреса правила трансляции, входы начальной установки 39 и 42, входы 40 и 43 разрешения вьщачи и счетные входы 41 и 44 счетчиков внутренней метки 9 и промежуточного результата 10 соответственно, входы установки в О 50 и 60, счетные суммирующие 51 и 61 и вычитающие 52 и 62 входы реверсивных счетчиков операндов 13 и операторов 17 соответственно, входы управления записью считыванием 49 и 59 блоков памяти операндов 12 и операторов 16, входы разрешения выдачи мультиплек- , сора 53 операндов и дешифратора 18 . операторов, входы 65, 66 и 67 записи регистра 20 адреса, первого 21 и второго 22 регистров функции предшествия, входы установки в О 45 и 54, записи 46 и 55, считывания 47 и 56 блоков регистров стековой памяти операндов 11 и операторов 15 соответственно, вход разрешения выдачи 57 блока регистров стековой памяти операторов 15, входы записи 69, разрешения выда- чи 71 и вьщачи признаков типа символа 72 регистра 24 текущего символа подключены к соответствующим управляющим выходам блока 1 микропрограммного управления. Таким образом, структура транслятора открыта (разомкнута) и каждаш блок можно подключить к остальным через шину 2 данных.

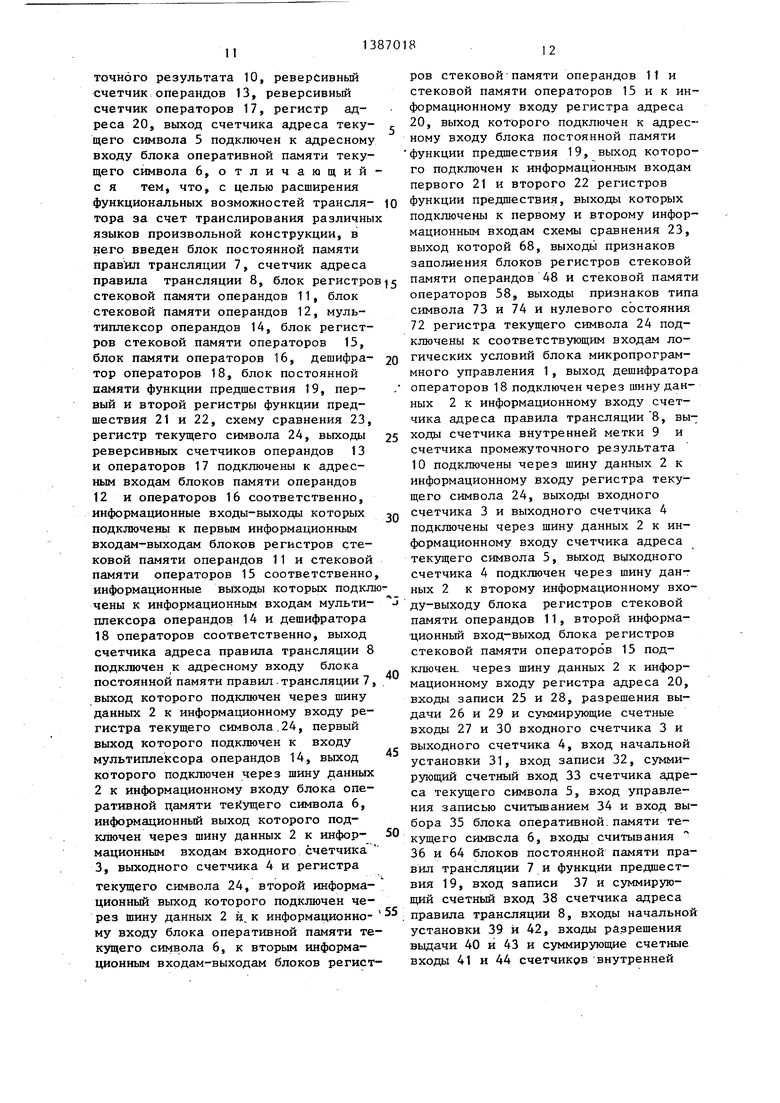

Регистр 24 текущего символа содержит счетчик 76, в котором помещается поле С, триггеры 77 и 78, в которых записываются признаки типа символа ТТ, дешифратор 79 нулевого состояния счетчика, буферы 80 и 81 .с тремя состояниями, элемент ИЛИ 82, причем информационный вход регистра 24 текущего символа составлен из информационных входов счетчика 76 и триггеров 77 и 78, выходом счетчика 76 является первый информационный выход регистра 24 и он подключен к входу дешифратора 79 нулевого состояния, к информационным входам буфера 80 и мультиплексора 14 oneрандов, выход триггера 77 подключен к информационному входу буфера 81, выходы буферов ВО и 81 составляют второй информационный выход регистра 24 текущего символа, вход 69 записи подключен к соответствующим входам счетчика 76 и триггеров 77 и 78,вход 71 уменьщения на единицу подключен к вычитающему счетному входу счетчика 76, вход 70 разрешения выдачи подключен к соответствующим входам буфера 80 и через элемент ИЛИ 82 буфера 81, вход 72 разрешения вьщачи признака типа символа подключен через элемент ШШ 82 к соответствующему входу буфера 81.

Транслятор работает следующим образом.

При запуске транслятора сначала осуществляется инициализация, при которой проводится начальная установка счетчиков 5, 9, 10, 13 и 17 и блоков 11 и 15 регистров, причем из блока 1 микропрограммного управления подаются соответствуннцие управляющие сигналы на входы 31, 39, 42, 45, 50, 54 и 60. После этого в входной счетчик 3 записывается адрес исходной программы, представляющей собой входную ленту транслятора, а в выходной счетчик 4 - начальный адрес, откуда должна передвигаться генерированная транслятором объектная программа, т.е. выходная лента транслятора. Это осуществляется путем подач на входы 34 и 35 блока 6 оперативной памяти текущего символа сигналов считывания 34 и выбора 35, считанна информация по адресу, содержащемуся в счетчике 5 адреса текущего символа, записывается через шину 2 данных в входной счетчик 3 путем подачи сигнала на его вход 25. Содержание счетчика 5 увеличивается на единицу (из блока 1 поступает сигнал на вход 33) а с блока 6 оперативной памяти ука-- занным образом считьюается информация и записывается в выходной счетчик 4 путем подачи сигнала на его вход 28.

Начинаются считъшание, анализ и трансляция исходной программы. Содержание входного счетчика 3 переда- ется через шину 2 данных в счетчик 5 адреса текущего символа, причем подаются управляющие сигналы на входы 26- и 32, считывается по соответствующему адресу блока 6 оперативной

0

5

0

5

0

5

0

5

памяти текущий символ с входной ленты (подаются управляющие сигналы на входы 34 и 35 блока 6), который посылается через шину 2 данных в регистр 24 текущего, символа путем подачи сигнала на вход 69.

Блок 1 микропрограммного управления анализирует текущий символ - его . поле Т, представляющее собой логическое условие 74, и в зависимости от его типа осуществляет некоторое из следующих дeйctвий,

Если символ типа операнд.(), то он записывается в стековую память операндов следующим образом. Блок 1 микропрограммного управления анализирует состояние признака 48 - Полный регистр. Если логический О, то блок 1 посылает управляющие сигналы 46 и 70, причем содержание ре- гистров 24 тек ущего символа записывается в самый верхний регистр блока 11 регистров, а поле Р устанавливаетт ся в 1. Если логическая 1, т.е. блок 11 регистров заполнен, то выхо-.. дящее содержание из самого нижнего регистра блока 11 регистров записывается в продолжение стековой памяти - блок 12 памяти путем подачи из блока 1 микропрограммного управления сигнала на вход 49, после чего содержание счетчика 13 увеличивается на единицу (подается сигнал на его вход 51). Теперь подается управляющий сигнал из блока 1 на вход 27 счетчика 3, в результате чего его содержание увеличивается на единицу и повторяются указанные действия по считыванию .и анализированию текущего символа.

Если символ типа оператор () то адрес, определенный кодом в регистре 24 текущего символа (после С), записывается в регистр 20 адреса (из блока 1 поступают управляющие сигналы на входы 65 и 70), после чего посылается сигнал считывания на вход 64 блока 19 постоянной памяти функции предшествия. Считанная информация представляет собой функцию предшествия - сравнительный приоритет текущего символа И записывается в первый регистр 21 функции предшествия путем подачи управляющего сигнала на его вход 65. После этого с самого верхнего регистра блока 15 считывается верхний символ стековой памяти и посылается в регистр 20 адреса (для этой цели блок 1 посылает управл5пощие

сигналы на входы 57 и 65). По соответствующему адресу с блока 19 постоянной памяти считывается функция предшествия - сравнительный приоритет верхнего символа в стековой памяти (приходит управляющий сигнал на вход 64 считывания) и записывается во второй регистр 22 функции предшествия 22 (блок 1 подает управляющий сигнал на вход 67). Содержание регистров 21 и 22 сравнивается комбинационным путем посредством схемы 23 и в зависимости от результата - признака 68, осуществляется одно из следующих действий.

а)Если содержание первого регистра 21 функции предшествия больше содержания второго регистра 22, т.е. величина признака 68 логическая 1, то текущий символ регистра 24 записывается в стековой памяти операторов следующим образом, Блок .1 микропрограммного управления анализирует состояние признака 58 полного блока регистров. Если оно логический О, то блок 1 посылает управляющие сигналы на входы 55 и 70 и содержание регистра 24 текущего символа за писывается в самый верхний регистр блока 15, причем одновременно информация передается между следующими регистрами. Если признак имеет значение логической 1, т.е. блок 15 заполнен, то выходящее из самого нижнего регистра блока 15 содержание записывается в продолжение стека -- блок 16 посредством подачи из блока 1 управляющего сигнала на вход 59 управления записью считыванием, после чего содержание счетчика 17 увеличивается на единицу (блок 1 посылает сигнал на вход 61). Далее следует увеличение содержания входного счетчика 3 на единицу (блок 1 подает сигнал на вход 27) и переход, к указанным действиям по считыванию и анализированию следующего символа : с входной ленты.

б)Если содержание первого 21 и второго 22 регистров функции предшествия равны между собой (величина на выходе 68 - логическая 1), то поступают по пункту а.

в)Если содержание первого регистра 21 функции предшествия меньше содержания второго регистра 22 - состояние признака 68 логический О,

то осуществляется трансляция-редук0

5

0

5

0

5

0

5

0

5

ция, которая заключается в следую.- щем: исходный код, генерируемый дешифратором 18 операторов, посылается через шину 2 данных в счетчик 8 адреса правила трансляции (из блока 1 микропрограммного управления прибывают управляющие сигналы на входы 37 и 63). Этот код определяет начальный адрес трансляционного правила. Начиная с адреса, заданного счетчиком 8, символы трансляционного правила счи- тываются по одному с блока 7 (до встрени символа Конец правила), причем для считывания каждого следующего символа содержание счетчика 8 адреса правила трансляции предварительно увеличивается на единицу. Считанный символ посылается в регистр 24 текущего символа. Для осуществления этих действий блок 1 микропрограммного управления посылает управляющие сигналы на входы 36 и 69, после чего подает сигнал на вход 38. Тип символа в регистре 24 анализируется блоком 1 микропрограммного управления - проверяются значения признаков 73 и 74 (поле ТТ) и в зависимости от его типа осуществляется одно из следующих действий.

.Если этот тип терминал, то он отправляется регистром 24 текущего символа в блок 6 по адресу, определенному выходным счетчиком 4 следующим образом. Содержание выходного счетчика 4 переводится в счетчик 5, причем из блока 1 микропрограммного управления высылаются управляющие сигналы на входы 29 и 32. После этого посылаются управляющие сигналы на входы 70, 34 и 35, в результате чего содержание регистра 24 текущего символа записывается в блок 6. Наконец увеличивается содержание выходного счетчика 4, причем подается управляющий сигнал на его вход 30. Таким образом, символ записывается на выходной ленте. Переходят к считыванию и анализу следующего символа трансляционного правила.

Если этот тип нетерминал, то тогда указанным способом адрес из выходного счетчика 4 записывается в счетчик 5, а в блок 6 - содержание k-ro регистра блока 11 регистров стековой памяти операндов, где k - указатель, находящийся в поле С регистра 24 текущего символа. Выбор регистра управляется мультиплексором 14 операндов.

Подача управляющих сигналов на входы 53, 34 и 35 приводит к записи содержания выбранного регистра в блок 6. Возвращаемся к считыванию и анализу следующего символа трансляционного правила.

Если это тип внутренняя метка

или промежуточный результат,

то

10

15

20

25

30

сначала формируется внутренний символ следующим образом. Содержание соответственно счетчика 9 метки или счетчика 10 промежуточного результата записывается в регистр 24 текущего символа (поле С), для этой цели подаются управляющие сигналы на входы 40 или 43 и 69. После этого внутренний символ записывается на выходной ленте содержание регистра 24 текущего символа записывается в блок 6 по адресу, определенному выходным счетчиком 4 указанным способом. Наконец увеличиваются на единицу содержания выходного счетчика 4, счетчика 9 внутренней метки (или счетчика 10 промежуточного результата) путем подачи управляющих сигналов на входы 30, 41 или 44 соответственно.

Далее приступают снова к считыванию и анализу следующего символа с трансляционного правила.

Если это символ Конец правила, то из стековой памяти операторов выталкиваются М-символы, где М определяется следующим по порядку символом трансляционного правила. Из стековой, памяти операндов выталкиваются К-символы, где К определяется следующим за М-символом, считанным из блока 7 постоянной памяти правила трансляции. Это осуществляется сле дующим образом. Указанным способом с блока 7 постоянной памяти правил трансляции считывается и записьшает- ся в регистр 24 текущего символа сим- ., вол. После этого содержание счетчика 8 адреса правила трансляции нарастает на единицу. Выталкивание символов из стековой памяти операторов осуществляется следующим образом.Со держание реверсивного счетчика 17 уменьшается на единицу (подается управляющий сигнал на вход 62), вынимается элемент, записанный на вершине стековой памяти -- самом верхнем регистре блока 15 регистров стековой 55 памяти аператоров путем подачи управляющих сигналов на входы 56 и 59, причем информация продвигается вверх

50

35

40

0

5

0

5

0

, 5

между регистрами, а элемент блока 16 стековой памяти операторов, указываемый реверсивным счетчиком 17, записывается в самый нижний регистр блока 15. Уменьшается содержание поля С регистра 24 текущего символа путем . подачи управляющего сигнала на,вход 71, после чего проверяется является ли его содержание нулем (признак 75). Если это не нуль, то повторяются указанные действия по выталкиванию элементов из стековой памяти операторов. В противоположном случае считывается с блока 6 и записывается в регистр 24 текущего символа следующий символ К. Начинается выталкивание символов из стековой памяти операндов. Содержание реверсивного счетчика 13 уменьшается . на единицу (блок 1 микропрограммного управления посьшаёт управляющий сигнал на вход 52), после чего поступают управляющие сигналы на входы 47 и 49, чем выталкивается символ с вершины стековой памяти (самого верхнего регистра блока 11 регистров стековой памяти операндов), а элемент блока 12 памяти операндов, Указываемый реверсивным счетчиком 13, записывается в самом нижнем регистре блока 11.Уменьшается содержание поля С регистра 24 текущего символа и проверяется явля- ется ли его содержание нулем. Если оно не нуль, то повторяются указанные действия по выталкиванию символа из стековой памяти операндов 11, за- письшается символ типа операнд и указатель, равный текущему содержанию выходного счетчика 4. Для этой цели из блока 1 микропрограммного управления подаются управляющие сигналы на входы 29 (разрешена выдача на счетчик 4), 72 (разрешена вьщача на регистр 24 - поле Т) и 46 (запись в 11). Приступают к считыванию следующего символа с входной ленты и анализу его типа. Этим цикл транслятора закрывается.

5

0

., 55

50 Формула изобретения

Транслятор языков программирования, содержащий блок микропрограммного управления 1, входной счетчик 3, выходной счетчик 4, счетчик адреса текущего символа 5, блок оперативной памяти текущего символа 6, счетчик внутренней метки 9, счетчик промежуточного результата 10, реверсивный счетчик операндов 13, реверсивный счетчик операторов 17, регистр адреса 20, выход счетчика адреса теку- щего символа 5 подключен к адресному входу блока оперативной памяти текущего символа 6, отличающий с я тем, что, с целью расширения функциональных возможностей трансля- тора за счет транслирования различны языков произвольной конструкции, в него введен блок постоянной памяти правил трансляции 7, счетчик адреса правила трансляции 8, блок регистро стековой памяти операндов 11, блок стековой памяти операндов 12, мультиплексор операндов 14, блок регистров стековой памяти операторов 15, блок памяти операторов 16, дешифра- тор операторов 18, блок постоянной памяти функции предшествия 19, первый и второй регистры функции предшествия 21 и 22, схему сравнения 23, регистр текущего символа 24, выходы реверсивных счетчиков операндов 13 и операторов 17 подключены к адресным входам блоков памяти операндов 12 и операторов 16 соответственно, информационные входы-выходы которых подключены к первым информационным входам-выходам блоков регистров стековой памяти операндов 11 и стековой памяти операторов 15 соответственно информационные выходы которых подклчены к информационным входам мульти- плексора операндов 14 и дешифратора 18 операторов соответственно, выход счетчика адреса правила трансляции 8 подключен к адресному входу блока постоянной памяти правил . трансляции 7, выход которого подключен через шину данных 2 к информационному входу регистра текущего символа.24, первый выход которого подключен к входу мультиплексора операндов 14, выход которого подключен через шину данных 2 к информационному входу блока оперативной дамяти текущего символа 6, информационный выход которого подключен через шину данных 2 к инфор- мационным входам входного счетчика 3, выходного счетчика 4 и регистра

текущего символа 24, второй информационный выход которого подключен через шину данных 2 й к информационному входу блока оперативной памяти текущего символа 6, к вторым информационным входам-выходам блоков регист

г 5 0 5 л j0

.

0

ров стековой памяти операндов 11 и стековой памяти операторов 15 и к информационному входу регистра адреса 20, выход которого подключен к адресному входу блока постоянной памяти функции предшествия 19, выход которого подключен к информационным входам первого 21 и второго 22 регистров функции предшествия, выходы которых подключены к первому и второму информационным входам схемы сравнения 23, выход которой 68, выходь признаков заполнения блоков регистров стековой памяти операндов 48 и стековой памяти операторов 58, выходы признаков типа символа 73 и 74 и нулевого состояния 72 регистра текущего символа 24 подключены к соответствующим входам логических условий блока микропрограммного управления 1, выход дешифратора операторов 18 подключен через шину данных 2 к информационному входу счетчика адреса правила трансляции 8, выходы счетчика внутренней метки 9 и счетчика промежуточного результата 10 подключены через шину данных 2 к информационному входу регистра текущего символа 24, выходы входного счетчика 3 и выходного счетчика 4 подключены через шину данных 2 к информационному входу счетчика адреса текущего символа 5, выход выходного счетчика 4 подключен через шину данных 2 к второму информационному входу-выходу блока регистров стековой памяти, операндов 11, второй информационный вход-выход блока регистров стековой памяти операторов 15 подключен, через шину данных 2 к информационному входу регистра адреса 20, входы записи 25 и 28, разрешения выдачи 26 и 29 и суммирующие счетные входы 27 и 30 входного счетчика 3 и выходного счетчика 4, вход начальной установки 31, вход записи 32, сумми- рзтощий счетный вход 33 счетчика адреса текущего символа 5, вход управления записью считыванием 34 и вход выбора 35 блока оперативной.памяти текущего симвсла 6, входы считывания 36 и 64 блоков постоянной памяти правил трансляции 7 и функции предшествия 19, вход записи 37 и суммирующий счетный вход 38 счетчика адреса правила трансляции 8, входы начальной установки 39 и 42, входы ра.зрешения выдачи 40 и 43 и суммируюпще счетные входы 41 и 44 счетчиков внутренней

метки 9 и промежуточного результата 10, входы установки в О 50 и 60, суммирующие счетные входы 51 и 61 и вычитающие счетные входы 52 и 62 реверсивных счетчиков операндов 13 и операторов, входы управления записью :считыванием 49 и 59 блоков стековой памяти операндов 12 и стековой памяти операторов 16, входы разрешения выдачи мультиплексора операндов 53 и дешифратора операторов 18, входы записи 65, 66, 67 регистра адреса 20, первого и второго регистров 21, 22

(PU2.2

cpuz.3

функции предшествия, входы установки в О 45 и 54, записи 46 и 55 и считьгоания 47 и 56 блоков регистров стековой памяти операндов 11 и стековой памяти операторов 15, вход разрешения выдачи 57 блока регистров стековой памяти операторов 15,, входы записи 69, разрешения выдачи 70, уменьшения на единицу 71 и разрешения выдачи признака типа символа регистра текущего символа 24 подключены к соответствующим выходам блока микропрограммного управления 1.

I у I с/Р

(DUZJS

Авторы

Даты

1988-04-07—Публикация

1981-11-12—Подача