- - . : .: - -1; . .

Изобрегёние огносигся к вычиспигельнбй техйике.

Известна система, в состав которой вход иг стековая память с двумя верхними йчёйками, выполненными на регистрах, блок управления, арифметический блок, триггеры эанягости, Мегчик операндов, блок чтения программ .1J ,.

Использование в этой системе стековой памяти уменьшает быстродействие выполняемых программ в 1,5-2 раза, так как запись и чгение информации в ячейки сгека осуществляется последовательно, а не прямым (координатным) способом.

Наиболее близкой по технической сущности к данному изобретению является система, содержащая вычислительное устройство, соединенное двухсторонними связами с оперативным эапоминавдщим усгройсгвом и устройством управления, которое через устройство управления каналами соединено двухсторонними связами.с внешним эапо- инающим устройством, управляющий вход перативйого запоминающего устройсгва

соединен с выходом устройства управления 2.

Однако такая система имеет низкую скорость трансляции программ, написанных на проблемно-ориентированных языках, так как основные элементы ее и связи между ними выпо лнены программно в виде инструкции. Но применение программ для транс- лядии, как известно ухудшает один из ооновных показателей ЭФМ - скорость трансляций.

Таким образом, в архитектуре и конструкции современных ЭВМ имеются элементы, разрешающие противоречие - либо повышенная скорость трансляции, либо по. вышенная скорость счета - в сторону улучшения Только одной характеристики. , . Поэтому задача состоит в том, чтобы ввести в архитектуру ЭВМ такие элементы, которые ПОЗВОЛИЛИ бы устранить или двусторонне уменьшить указанное противоречие.

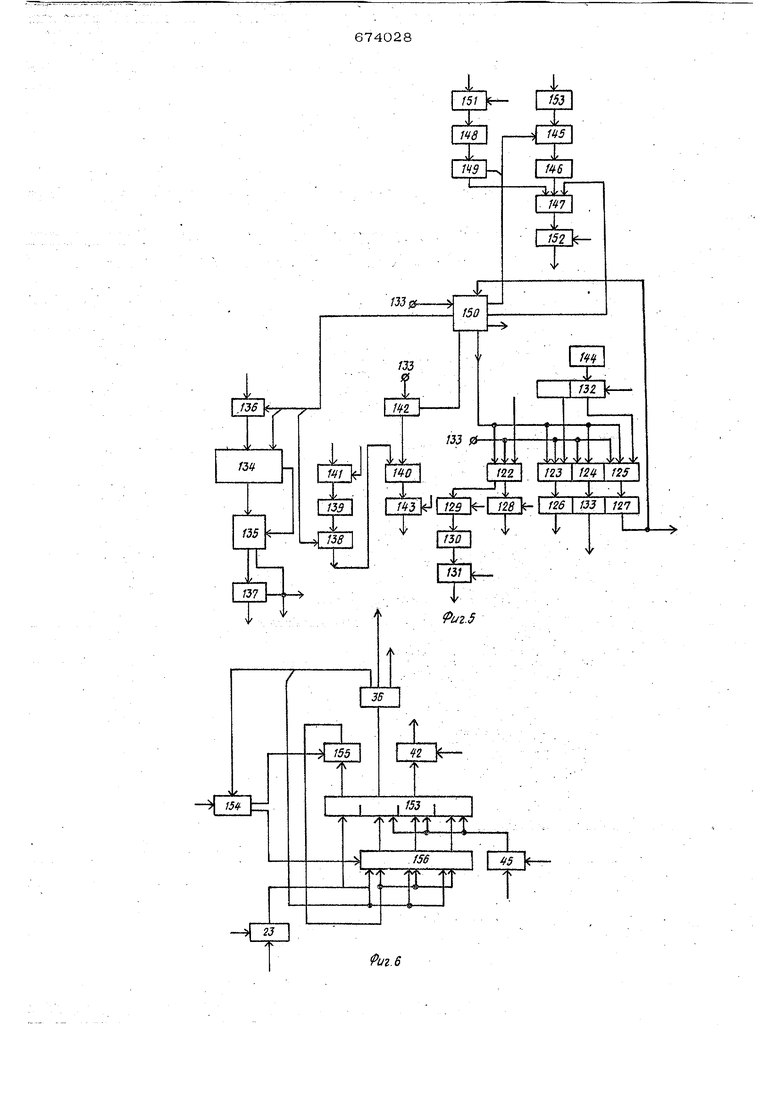

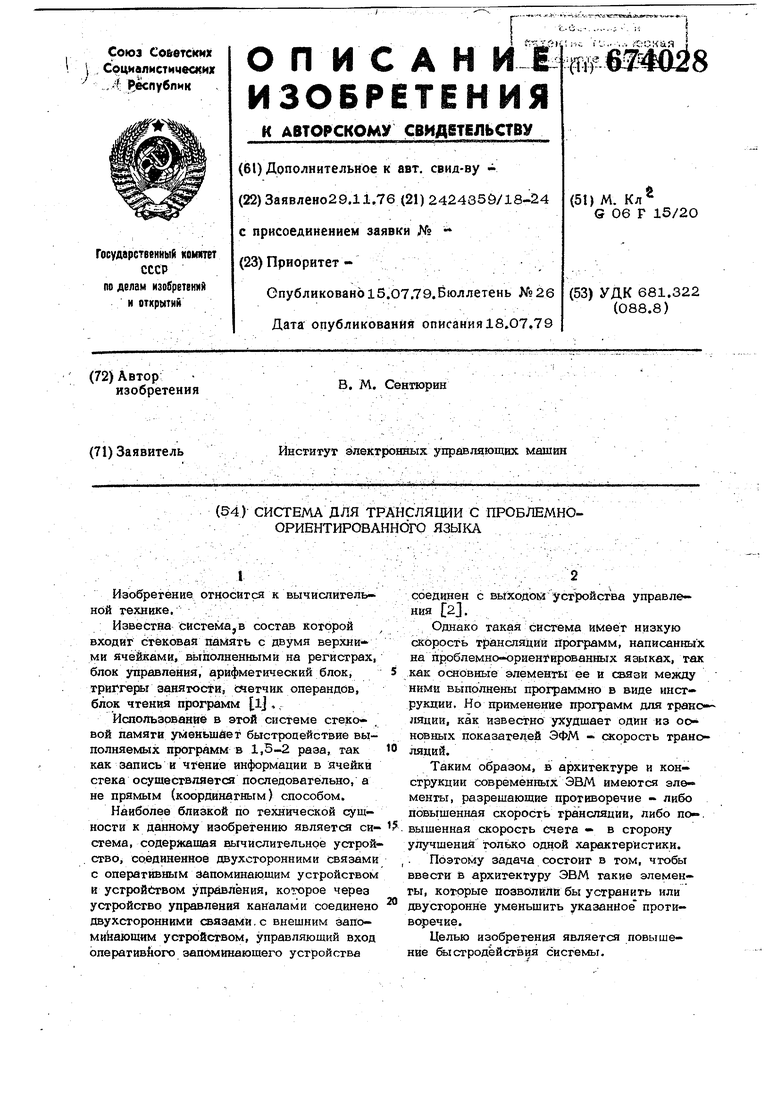

Целью изобретения является повышение & 1стродёйствия системы. Поставленная цель достигается тем, что в предлагаемую систему введе ты мо- дификатбры адреса символов исходного текста, адреса макрокоманд, адреса полуобъектных команд, адреса объектных команд, адреса меток, символьный анализатор, операторный анализатор, блоки перекодировки чисел и обработки ошибок, уп рШйЯйЩйё входы которых подключены к вьгходуустройства управления; выход вы. числительного устройства соединён с первыми. входами символьного и операторного анализаторов и блока перекодировки чисел первый выход и второй, вход символьного анализатора соединены соответственно со 1ЩЙ-}ГбШ1б1« ГШ|ШмШ тйвного анализатора, второй рого подключен к первому входу модификатора адреса макрокоманд, третий выход соединён с первыми входами модифйкато ров адреса попуобъектньк команд и адреса объектных команд, четвертый вьь.ход подключен к первому входу модифиКа: тора адреба меток, первые выходы блока перекодировки чисел, модификаторов адреса: меток, адреса объектных команд, адреса прлуобъектных комайД, Символов исходного текста, второй выход сим вольного анализатора и пятый ВЫХОДбпера Торного анализатора соединены с первым входом блока обработки ошибок, второй вы ход блока йерекодировки чисел, первые выходы бйока обработки ошибок и Модификатори адреса макрбкбманд, шест вйход операторного «.нализатора и третий ёыход . -, 1 СИМВОЛЬНОГО анализатора соединены со вхо дом устройства управления, седьмой выход операторного анйлйзагора подключен ко входу модификатора символов исходного текста, вторые входы модификатора адреса макрокоманд. Модификатора адреса меток и блока обработки ошибок соединены с выходом оперативного запоминающегчэ устройства, вХОдн 1 которого соединены с соответствующими выходами введенных модификаторов, анализаторов, блока перекодировки чисел и блока обработки ошибок; кроме того, символьный анализатор в сиётёМё содеркит Два счетчика, выход первого из которых, соединен со входом блока И, первый управляющий вход которого подключен к управляющему входу символьного анализатора, выход вто рого счетчика соединен со входом дешифратора, вь1ходы которого подключены соот вётственно к первому, второму и третьем .выходам симв ольного анализатора, первый вход которого соединен со входами счет674028чиков, второй вход - со управляющим входом блока И, выход которого соединен с выходом символьного анализатора; операторный анализатор в системе содержит переключатель, стековый регистр, первый выход которого подключень ко входу дешифратора, первый и второй выходы которого соединены соответственно с первым входом переключателя и первым входом стекового регистра, агорой вход переключателя соединен с управляющим входом операторного анализатора, третий вход переключателя и второй вход стекового регистра соединены с первым входом операторного анализатора, второй вход которого Соединен с четвертым входом переключателя, выходы которого с первого по четвертый подключены соответственна к выходам с первого по четвертый операторного анализатора, пятый, шестой и седьмой выходы которого соединены соответственно с третьим выходом дешифратора, вторым выходом стекового регистра и пятым выходом переключателя, четвертый выход дешифратора подключён ко второму выходу операторного анализатора, третий вход и третий выход стекового регистра соединены соответственно со входом и выходом операторного анализатора. На фиг. 1 показана блок-схема предлагаемой системы; на фиг, 2 - логическая схема системы; на фиг. 3 - логическая схема модификатора адреса; на фиг. 4 логическая схема блока перекодировки . Н-. , логическая схема блока обработки ошйёок на фиг. 6 - логическая iSfu-, . 9т tirff f ir TT rt Л TT T ITTJQ fflf Ct схема стекового регистра; на фиг. 7 логическая схема стека; на фиг, 8, 9 схемы реализации символьного анализатора на фиг, 10 - операторного анализатора. . Система включает в себя оперативное за1;оминающее устройство 1, вычислительНое устройство 2, устройство управления 3, устройство управления каналами 4,внешг нее запоминающее устройство 5, модификатор адреса символов исходного текста 6, символьный анализатор 7, операторньгй анализатор 8, модификатор адреса макрокоманд 9, модификатор адреса полуобъектных команд 10, модификатор адреса объектных команд 11, модификатор адреса меток 12, блок перекодировки .чисел 13, блок обработки ошибок 14. Более детально система представлена на фиг. 2, где дешифратор 15, блок чтения 16, блрк записи 17 являются элементами оперативного запоминающего устройсгва (ОЗУ) Ij регистры операндов 18, 19 схэединены с вычислигельным устройсгвом 2 блоками 20, 22 И, блоком 21 И - с ОЗУ 1, блоком 23 И - с операторным анализатором 8; модификатор символов исходного текста 6 состоит из трех параллельно включенных счетчиков 24, 25,26, причем выход счетчика 24 через блок 27 И соединен с дешифратором ОЗУ 15, выход счетчика 25 соединен с дешиф рагором 28, нулевой №.1ход которого соединен с третьим разрядом счетчиков 24, 26,а выход счётчика 26 через дешифратор 29 соединен с блоком, обработки ошибок 14. Символьный анйлиэагор 7 выполнен (см. фиг. 2 и фиг. 3) из двух счетчиков 30, 31, причем выход счетчика 30 соеди нен через блок 32 И с дешифратором ОЗУ 15, выходы счетчика 31 соединены через дешифратор 33 с переключателем 34 анализатора 8. и с. блоком обработки ошибок 14. I -. ,.-/....:.: . . -vОператорный анализатор 8 выполнен с использованием переключателя 34, вого регистра 35, дешифратора 36, сте« ка 37, счетчика 38, дешифратора сяетчнка 39, причем вь1ходь стековогч) регисг ра 35 соединены с дешифратором 36, вь1ходы дешифратора 36 соединены с переключателем 34, со стековым регистром 35, счетчиком 38, через блок 40 И, регистр 35 - со стеком 37; стек 37 соединен через блоки И 41, 42 с регистрами 18, 19, вЫходь стека 37 соединены через блоки И 43, 44 с регистрами18, 16 а через блок И со стековым регистром 35, выход дешифратора 39 соединен с блоком .обработки ошибки 14, Позицией 45 обозначен стековый регистр. Дешифратор 36 соединен через блок 46 И с модификатором адреса макрокоманд 9, стековый регистр 35 соединен через блок 47 И с ОЗУ 1. Второй вариант стека операторного ана лизатора 8 (см.. фиг. 2) может быть выполнен с использованием двух реверсивных параллельно включенных счетчиков 48, 49, причем выходы первогхэ счетчика 48 соединены через блок 50 И с дешифратором 15, выходы дешифратора 36 соединень с переключателем реверса счетчиkoB 48, 49, выходы стекового регистра 35 соединены через блок 47 И с ОЗУ 1, выходы ОЗУ 1 соединены со стековым регистром 35. Выход дешифратора 51 соеди нен с блоком 14. Модификатор адреса макрокоманд 9 выполнен в виде двух параллельно включен ных счетчиков 52, 53, причем входы счетчшса 52 соединены с регистром 54 через блок 55 и, входы младших разрядов счетчика 52 соединены через блок линий задержки 56 с блоком 46 И, выходы счетчика 52 соединещ. через блок 57 И с дешифратором ОЗУ 15, входы счетчика 53 соединены чегрез блок 58 И с выходами ОЗУ 1, ы 1ходы счетчика-53 соединены через дешифратор 59 с устройством управления 3, клеммы 60, 61 являются входами блока 58 И и дешифратора 59 соот ветствённо. Модификатор адреса полуобьектных команд 10 выполнен из четырех параллельно включенных счетчиков 62, 63, 64,65, причем ш.1хода 1 счетчика 62 соединены с дешифратором ОЗУ 15 через блок 66 И по первой ветви и через блок 67 И, регистр 68, блок 69 И - по второй ветви, счетчики бЗ,в4 через дешифраторы 70, 71 соединены с блоком обработки ошибок 14, выход счетчика 65 соединен через блок 72 И с ОЗУ 1, выходы регистра 7 3 подсьединё1а11 параллельно выходам счетчика 63 ко входам дешифратора 70. Модификатор адреса объектных команд . . 11 выполнен из двух параллельно включенных счетчиков 74, 75, причем выходы перв.ого счетчика 74 соединены через блок И 76, с дешифратором ОЗУ 15, выход счетчика 75 соединен через дешифратор 77с блоком обработки ошибок 14, входы счетчиков 74, 75 соединены через блок 78И параллельно входам счетчиков 62, 63, 64, 65. Модификатор адреса меток 12 выполнен из трех параллельно включенных счетчиков 79, 80, 81, причем выходы счетчика 79 ., соединень с дешифратором ОЗУ 15 через блок 82 И по первой ветви, а через блок 83 И, регистр 84, блок 85 И - по второй ветви, выходы счетчиков 80, 81 соединены через дешифраторы 86, 87 с. блоком обработки ошибок 14. Позицией 88 обозначен блок И. Входы счетчика 81 соединены через блок 89 И с выходами ОЗУ 1, регистр 84 через блок 88 И соединен со счетчиком 79. Второй вариант символьного анализатора (см. фиг. 2 и фиг. 9) выполнен из ре- . гистра 18, блоков 9О, 91 И и дешифратора 92, и отличиеего от первого варианта состоит в том, что выходы дешифратора объединены в алфавитные группы букв.

цифр, операторов, разделителей по кодам символов, а не по номеру в алфавите, как в первой варианте.

Более детально схема модификатора адреса 10 представлена на фиг. 3. Он выполней из триггера 93, регистров 94, 95, 96, соединенных через блоки 97, 98, 99 И со счетчиком 64, выхоДьгТрйпгера 93 соединены с шинами блоков И 1ОО и 101, блок И 102 включен на входе счетчиков 62, 63; выход триггера 103 соединен с шиной блока И 102, 104 включен на входе регистра 73 выТоЗь1 , которого соединены параллельно выводам счетчика 63 на входах дешифратора 70, Триггер 93 и блоки И 100, 101 представляют собой переключательсчёгнь1х ЙМ1Ч ЛЬСОВ.. .Применение модификаторов shpecaj со стоящих .из нескольких параллельно включенных счётчиков, позволяет осуществлять несжолько процессобойноврёмённЬ, что приводит к увеличению; сжороСтитрансЛй цйй..; , -:: Схема блока перекодировки чисел 13 представлена на фиг. 4. Этот блок ;выпол нен из упаковывающего регистра 105; узла перекодировки упакованнь х дёЬятичНБ1Х чисёл/й двойчнь Х.чйсйл§1|(ЙдНйь1е 106, узла перекодировки двоичшзс ;чисел в двЬйчньтё числа с плавающей запятой , 107, п ерекл1рчателя режимов 108, счет-.: чика 109 и дешифратора 110 упаковыва-, юшего регистра 105, счетчика ill и де- шифратора 112, причём ёлок 105, 106, 1О7 соединены последовательна через блоки И ИЗ, 114, 115, на Ъхбдах счётчиков 109 и 111 включены блока И 116, 117, выходы 105, 106, 107 соединены через блоки И 118, 119, и блок ИЛИ 120 с выходнь1м блоком 121. Детальная схема .блока ббраббтКй ошибок представлена на фиг. 5. Этот блок вы полнен в виде устройства, содержащего четадре параллельно включенных счетчика 122, 123, 124, 125, при этом на выходе счетчиков 123, 125 включень дешифратор 126, 127. На выходе счетчика 122 включены блоки И128,129, регистр: 130 адреса ключа защиты и блок И 131; блок И 132 включен на входе Счетчика 125; позицией 133 обозначен )щий вход блока 14. Устройство перекодирования двоичных чисел в десятичные 134 соединено со входом регистра распаковки 135, Влокй .И 136, 137 включены на входе блока 134 и выходе блока 137, блок И 138 включен между регистром

139 и счетчиком 140, блоки И, 141, 142, 143 включены на входе регистра 139, навходе и выходе счетчика 140 регистр 144 размера строки исходного текста включен ко входам блока Mi 32, блок И145, блок задержки 146 включены последовательно на входе счетчика 147 адреса области названий ошибок, регистр 148 адреса начала области названий ошибок включен че- рез блокИ 149 ко входам счетчика 147; позицией 150 обозначен переключатель. Блоки И 151, 152 включены на входе регистра 148 и счетчика 147, дешифратор 153 включен ко входам блока И 145. Стековый регистр {см. фиг. 6) выполнен из многобайтного основного регистра 153, блока управления импульсами сдвига 154, дешифратора 36, однобайтного блока И 155, многобайтного блока И 156, причем выходьг старшего байга регистра 153 соединены через однобайтный блок И 155 и многобайтный блок И 156 с младшими байтами регистра 153, выходы регистра. 153 соединены с дешифратором 36, выходы дешифратора 36. соединены с первыми входами схем И, включенных на входе байтных шин блока 156, а выходы блока управления импульсами сдвига 15 4соединены со вторыми входами ; схем И, включенныхна входе байтных шин блока 156.. .Схемы И, включённые н.а входе байт- ных ШИН блока И 156, на чертеже не по- казань считается, что он и Являются ко структиБной частью блока И 156. Стек (см.. фиг. 7) выполнен из генератора импульсов 157, переключателя 158, счетчика 159, дешифратора 160, регистра 161, блока И 162, Н-1 блоков И 163, 164, причем выход генератора 159 соединен через переключатель 158 СХ5 входом счетчика 159, один выход де-- шифратора соединен с переключателем 158, а остальные Н-1 выходов дешифратора 160 соединены с шинами блоков И 162, 164 в порядке возрастания их номеров, выхода блоков И 163, 164 соединены со входами элементов памяти, а выходы Н-1 элементов памяти, начиная с первого, соединены со входами Н-1 блоков И 163, 164, позицией 165 обозначен блок И, выходы счетчика 159 через блоки И 166, 167 и регистр 161 включены к вхрдам счетчика 159. Для простоты изображения стек на фиг. 7; выполнен из четырех элементов памяти, но он может бьгть увеличен до заданного объема, при этом принципиальНЫХ изменений конструкция стека не пре гёрпевает. Нумерация элементе на фиг. 8, 9,10 соответствует нумерации на фиг. 2, Описываемый транслятор предназначен для трансляции программ:. с проблемно- ориентирсжанного языка АМАС-1 и с несушественйыми дополнениями ой мЬжёг быть использован для трансляции аЛгеб- раических выражений на фортран-ХУ и Алгол-60. Усовершенствсшание языка АМАС-1 состоит в том, что признак типа операции, записанный в первом действии алгеб раического выражения, автот гатичесйя рао пространяется на все Последующие действия этого выражения. Указанное правило практически не усложняет трансляции, но упрощает програм мирование.; Например, алгебраическое выражение А С+К-М для вещественных чисел точно .так же изобразится на Фортран- -1У, АМАС и АМАС-1. Для целых чисел это выражение на Фортран-1У останется без изменения, на АМАС и АМАС-1 оно примет соответствующий ввд: А В-С 4- - вЪн + К - М. ... V Суть способа трансляции алгебраических выражений, реализуемого описьшашо системой, состоит в следующем: onepaTojbi программы на исходном тек сте заменяются на макрорасширения макрокоманд в объектных кодах; формула делится на уровни; трансляция алгебраических формул осуществляетм поэтапно - от уровня к уровн количество этапов равно количеству уровней; каждый уровень делится на два подуров ня: первый подуровень состоит из операций сложить, вычесть; второй подуровень состоит из операций умножить, поделить; трансляция осушбствляётся с помощью двух стеков; стека уро&нз и стека невы- полненнь1х операций; максимальное количество уровней, допускаемы:х в формуле, определяется объемом стека невьшолнеш1ых операций и может, например, равняться 32; в стек урсеня, ш шолненвый в виде сте кового регистра загружается не более че тырех операций: первая, последняя операция первого подуровня, последняя операция второхчэ подур ня и очередная, в стек уровня загружает также признак типа первой операции; В результаттрансляции заносятся объектные команды, реализующие загрузку и i выгрузку результатов вычислений в память ОЗУ По стековому способу. Предлагаемый способ является усовер- щенствованием известного способа трансляции Мильнеса и ПОЛИЗа, основанного на прямом просмотре формулы исходного текста программы, вычислений промежуточных результатов, загрузки формулы в стек в инверсном представлении ее с последующей выгрузкой формулы из стекла и вычислением результата. По этому методу в текст загружается вся формула вместе с операциями. Последнее обстоятельство не позволяет осуществлять анализ одновременно всех ячеек стека или отдельных еГо частей, так как стек в этом случае может иметь бесконечное количество состояний. В описанном выще методе для анализа формул используются два стека. Причем, стек уровня в виду конечного количества состояний (не больще четырех операций) может анализироваться с помощью аппаратного устройства - дешифратора одновременно по всем ячейкам, что увеличивает скорость трансляции. Кроме того, загрузка в стеки только операции увеличивает скорость загрузки и выгрузки в стек и увеличивает в целом скорость трансляции, а загрузка в стек в процессе вычислений только промежуточiabix результате не уменьщает скорость вычислений. При этом, под уровнем формулы принимается часть алгебраического выражения, заключенная между бткрьхвающей и закрывающей скобками одной степени вложенности. Под степенью вложенности понимается число, указывающее номер открывающей скобки и последовательности открывающих скобок в алгебраическом выражении, при условии равенства открывающих и закрывающих скобок. При нулевой степени вложенности скобки отсутствуют. Трансляция очередного уровня может прерываться появлением старщего по степени вложенности уровня. При этом результаты трансляции очередного, то есть прерванного и незакрытого уровня запоминат я в стеке. По заверщении трансляции высшего уровня осуществляется переход а трансляцию прерванного низшего уровя и т.д., пока не закончится трансляция сего выражения. Макрорасширения в объектных кодах елятся на два типа. Микрорасшйрения первого типа mvieror все даншедая их выполнения и сосгояг из обьекгнь1х команд. Макрорасширения второго типа представляют собой полуобьектные команды без адресной части. Трансляций осуществляется в две фазы. На первой фазе исходный текст заменяе7 ся макрорасширениями, при этом непосред ственно после записи микрорасширений второго типа заносите вторая адресная часть этих команд из программы на проблемнб-Ьрвентированном языке в виде сим вольного адреса или литера. Результатом первой фазы является полуобъектная программа. На второй фазе символьные адреса и литералы заменянэтся их относительными адресами в объектных кодах и на этом трансляций кончается. Результ атом транс ляции является перемешаемый программны модуль в объектных кодах. Система работает следующим образом выполняя соответствующие режимы. Режим (ЗТ) загрузки данных. В этом режиме массив микрокоманд заносится с внешнё;го запоминающего устройства 5 в ОЗУ 1 и адрес начала этого массиьа заносится в модификатор адреса макроко манд9. , Режим (ЗП) загрузки исходного текота йрограммь и параметров транслятора. В этбм режиме исходный текст программы на проблемно-ориентированном язьгке заносится в. ОЗУ 1 и адрес н;ачала и pia3мер этого текста, а также размер строк этогб текста заносится в модификатор ад реса символов исходного текста 6, Кроме того, в модификаторы адреса 10, li, 12, заносятся соответственно адреса и размеры областей пЬлуобъектной и объект ной йрограммь, номер регистра и адрес иразмер области таблиць меток. В блок обработки ошибок 14 также заносят ся адрес и размер области таёлицы назва ний ошибок н таблицы ошибок. Режим ЗП MojKei выполнятьсй многократно после од нократного выполнения режима ЗТ. . Режимы ЗТ и ЗП выполняются пЪд управлением операционной системы ЭВМ. Размеры записей объектных, полуобъект- ных макрорасширений, а также меток, лит ералов и ШШс сяГТГ ключ, рас положенный в нулевом байте указа1шых записей. Старший восьмой разряд Кйкэчй,равный , йвЛЯётШ прИзнаком макрорасши рения первого типа, а равный О - являтся признаком макрорасширения второго ипа. Седьмой разряд ключа, равный 1, явяется признаком литерала, а равный О является признаком символьного адреса в макрорасширении второго типа. Из этог;5 стедует, что максимальная : длина макрорасширений первого типа может достигать 127 байт, а литералов до 63 байт. Ключи макрорасширений составляются и записыва отсй в их записи перед загрузкой таблицы макрорасширений в ОЗУ 1, Остальные ключя формируются транолятором. .. Режим работы фазы 1 состоит в выполнений следующих операций. Первая операция. Анализ символов. Эта операция выполняется символьным анализатором. :Блоки 6 и 7 устанавливаются в исходное сюстояние. Это в счетчике 24 находится адрес очередного симвбла исходного текста, в счетчике 25 - номер этого символа в строке Tekci-a, в счетчик.е 26 - размер неоттранслированной часгй гекста. В счетчик 30 заносится адрес алфавита исходного текста, записанный из регистра 94 через блок И 97, в счетчик 31 - размер алфавита в символах, в регистр 139 - содержимое счетчика 24.. : Очередаой символ считывается по адресу в счетчике 24 и заносится в регистр 18 и в стековый регися-р 35 через блок И 91. Далее, первый (или очередной) символ алфавита считывается по адресу в счетчике 30 в регистр 19. Далее, содержимое регистров 18 и 19 через блоки И 20, 22 ;занс сигся в вычислительное устройство и, где осуществляется их сравнение. Если при этом символ оказался оператором (или частью оператора), то управлёййе передается на выполнение второй Ьперации; если сим&ол оказался признаком снмвольнЬгЬ адреса, то управление передается на выполнение третьей операции; если символ оказался литералом, то управление передается на выполнение четвертой операции; если символ оказался признаком метки, то управление передается на ш шолнеиие пятой операции. После каждой операции сравнения к счётчику 30 прибавляется + 1, а из содержимого счетчика 31 вь11читается + 1. При появлении нуля в счетчике 31 дешифрагор 33 подаёт сигнал об ошибке (появления неалфавитного сикшола в тексте) в блок 14. По окончании обработки ошибки к содержимому счетчикоБ 24, 25 прибавляет ся + 1. а из соаеожимогр счетчика 26 вычитается +1. Если в счетчике 25 по- явилось число 72 (сигнал окончания текстовой части строки), то с выхода дешиф ратора 28 поступает сигнал на четверты входы счетчиков 24, 26, что эквивалентно прибавлению числа 8 к счетчикам 24, 26, Это необходимо для того, чтобы номер перфокарты, записанный в колонку перфокарты, не анализировался как текст программы. Далее счетчик 25 устанавливается в .нуль и осуществляется переход в начало первой операции на уотановление в исходное состояние счетчйков 30, 31 и регистра адреса начала стр ки 139 блока 14. Появление нуля в счетчике 26 оанаЕчает конец исходного текста, и соответству юший сигналс дешифратора 29 подаете в устройство упразвленйя 3. При втором sapHaiHTe анализа символов код сиМвойа из регистра 18 через блок И 9О пбступает в дешифратор 92, где осуществляется йнализ символов за один такт. Второй вариант йревосходит первый по быстродействию, но уступает первому по пррс;тоте изготовления. Вторая операция. Анализ ойераторов, Анадиз состояния стекового регистра 35 осуществляется дешифратором 36, кото {ый подает на схемы И, включенные на входе байтных шин блока И 156, разрешающие ситаалы. .. По окончании первой операции на блок управления импульсами сдвига 154 подается сигнал, последний подает в блок И 155 и на вторые входы схем И, включенных на входе байтш 1Х шин блока И 156, разрешающие сигналы и в регистре 35 осуществляется перемещение информации, как описано в таблице. Кроме того, дешифратор 36, в соответствии с состоянием регистра 35, выдает на вторые выхоhbF относительнь1й адрес соответс№ук)ще- го макрорасширения в таблице макрорасширений. Разрешающий, импульс, пОдаваемь1й на шину блока И 46 от блока 154, позволяет считать относительнь и адрес с выхода дешифратора 36 н прибавить его к адресу начала таблицы макрорасширений в счетчике 55. Для этого постоянные вре мени линий задержки в блоке 56 выбраны так, чтойл постоянная времени в старшем разряде &)1ла больше времени переходного процесса в младших предшествующих разрядах. Далее, ключ макрорасширения считывается из ОЗУ 1 в стетчик 53 через блок И 58. Далее осуществляется побайтное считывание макрорасширения под счетчиком 52 и запись макрорасширения под счетчиком 62, При этом к счетчикам 52, 62, 65 прибавляется + 1, а из счетчиков 53, 63 вычитается + 1. При появлении в младших семи разрядах счетчика 53 нуля, дешифратор 59 выдает сигнал об окончании записи макрораоширения, при этом содержимое счетчика 65 заносится в ОЗУ 1 по адресу в регистре 68, то есть, записывается ключ с. . нулем в восьмом разряде, что является признаком того, что эта запись будет переноситься в поле объектной программы без изменения. , После этогх содержимое счетчика 62 блок И 67 заносится в регистр 68, к счетчику 62 прибавляется + 1, а из счетчика 63 вычитается + 1. . ; Параллельно побайтному считыванию макрорасширения к содержимому счетчика 74 размера объектной программы в модификаторе 11 прибавляется число, равное раз меру макрорасширения. Сложение этого числабсузцествляется путем прибавления +1 через схему И 78 к счетчику 74 при чтеНИИ или записьтвании каждого байта макрорасширения, В случае, если макрорасширение представляет собой часть объектной команды, то есть в восьмом разряде находится О, .то к счетчику 74 прибавляется + 2, а из счетчика 75 вычитается + 2, или, что то же самое, прибавляется и вычитается +1 из второго по старшинству разряда соответствуюших счетчиков 74 и 75. Это обуслйвлено тем, что размер относительного адреса вместе с номером регистра базы равен двум байтам. При этом, в соответствии с состоянием стекового регист)ра 35, анализируемого дешифратором 36, содержимое последнего либо не изменяется, либо заносится в стек 37, через блок И 4О, а затем обнуляется, либо в обнуленнъхй регистр 35 через ёлок И 45 заносится информация о невыполненных операциях очередного уровня выражения (см. таблицу ). В случаях, если размер объектной программы превышает установленное число, то в счетчике 75 появляется нуль, а дешифратор 77 выдает сигнал об ошибке в блок 14. Сдвиги информации в стеке 37 осуществляются следующим образом: в счетчике l59 ведется счет сдвигаемой информации элёиен ов памяти влево или вправо при каждом обращении к регистру 37, а в счетчике 35 ведется счет открытъ1х уровней в формуле. Счет этот ведется следую шим образом: при появлении открывающей скобки формулы к содержимому счетчика . 35 прибавляется +1, при появлении закрьтЁающей скобки из содержимого счегчи ка 3 вычитается + 1. В случае, если содержимое счетчика 35 превысило дйпустиMde чийЛо или оказалось меньще йуля, дешифратор 39 подает сигнал оё ошибке в блок 14. Сигнал об ошибке подается и в том случае, если пойвился символ окончакия формулы i, а содержимое счетчики 35 не равно нулю или индексный уровень оказался открытым, При организации стека на ОЗУ 1 соот- BeTCTsyrouiHe занесения информации из регистра 35 осуществляются через блок И 47 по адресу в счетчике 48. При этом, в параллельно включенном сяетчике 49 ведется счет свободной части стека, а дешифратор 51 выдает сигнал об ошибке в случае переполнения стека. Е ели очередным символом оказалсй оператор конца программы или в счетчике 2 8 уо тановипся нуль, то осуществляется первход шестой операции, в противном случае осу- шествляется переход к первой операции 1. Третья операция. Запись символьного адреса. Эта операция сводится к описанию работы модификатора адреса, изображенного на фиг, 2 и на фиг. 3. К исходному моменту в счетчике 62 находится адрес свободной части ОЗУ 1, увеличенный на + 1, в данном йлучаё - адрес полуобъектной программы. В счет-t чиках 63, 64, б5 находится О, в регистре 68 находится адрес полуобъектной программы, в регистре 88 находится размер полуобъектной программь. Счетчики 62, 63, 65 установлены на сложение + 1, счетчик 64 установлен на Бьгчйтание + 1. Триггер 93 включен и при этом на шину блока И 100 подаётсй разрешающий сигнал, а на блока И 1О1 подается запрещающий ситоал. На шину блока И 102 подается разрешающий сигнал с выхода триггера ЮЗ. Триггеры 93, 103 включаются устройством 3. На:первом такте .считывается содержимое регистра 94 число 8 в счетчик 64 через блок И 97, а восьмой разряд счетчика 65 устанавливается в 1. Затем символьный адрес побайтно счишвается по адресу в счетчике 24 модификатора 6 и записывается по адресу в счетчике 62 модификатора 10 с помощью устройства 3 и блоков чтения 16 и запи-. си 17 в ОЗУ 1. При этом входной сигнал подается на входы трех счетчиков 24, 25, 26 или четырех счет-чиков 62, 63, 64,65 одновременно. . При Зёписи символов адреса к содержимому счетчиков 24, 25, 62, 63, 65 прибавляется + 1, а из содержимого счет чиков 26, 64 вычитается + 1. При появлении в счетчике 64 нуля дешифратор 71 йодает закрывающий сигнал на вход триггера 93. Последний закрывает блок И 100 и открывает блок И 101. Если размер символьного адреса оказался равным 8, то ключ его, сформированный к этому моменту в счетчике 65, заносится в ОЗУ 1 по адресу в регистре 68. Затем содержимое счетчика 62 через блок И 67 заносится в регистр 68, после этого к счетчикам 62, 63 прибавляется + 1 и модификатор заканчивает работу./ Если размер символьного адреса оказался меньше 8, то переключатель 34 закрывает триггер 93, к осуществляется переход на запись ключа символьного адреса.-, .-л-, -.. . - ( . Если размер символьного адреда ока- Эй лея больше 8, то очередной импульс записи через блок И 101 йоступает в блок обработки ошибок, а йе на входы счетчиков 62-б5, так как блок И .100 закрыт. После обработки ошибки в 14 очередной импул:ьс запйри может вновь пройти через блок И 101. Этот гфюцесс повторяется до тех пор, пока не появится операторный символ, после чего осуществляется переход на запись клнэча символьного адреса размером в 8 байт При работе модификатора 10 в счетчике 63 ведется счет объема памяти, заня: ой полуобъектной программой. При совпадении еодержимого .сяетчика 63с содерЖамьш регистра 73 Дешифратор 70 выдает с о№ётс твующий сигнал о заполйении или переполнении области полуобъектной программы. По окончании третьей операции осуществляется переход к первой операции. , , -. . Для использования только счетчиков 64, 65 подается сигнал, закрывающий триггер 103, который закрывает блок И 102. Четвертая операция. Запись литерала. В восьмой и седьмой разряды счетчика 65 заносится , в остальные шесть ра рядов заносится О, Проверяется признак типа литерала и соответственно типу литерала в счетчик 64 из какого-либо регистра 94, 95, 96 заносится соответствующее число 63,16 8, указывающее максимальшэгй размер дл данного типа литерала. Если литерал буквенно-цифровой (ма1Ксимальный размер его 63), то он записы вается в полуобьектную программу под счетчиком 63 аналогично символьному ад ресу до признака конца литерала. Если литерал цифровой, то управление передается в блок перекодировки чксеп 13, где литерал перекодировьгеается соответственно типу операции, хранящемуся в стековом регистре 35. По окончании перекодировки литерал заносится в ОЗУ 1 под счетчиком 62 аналогично символьному адрасу, но исходная информация берется из блока 13. В случае появления ошибки в записи литерала дешифратор 71 и блок 13 выдают сигнал ошибки в блок 14, По окончании четвертой операции осуществляется переход к первой операции. Пятая операция. Запись метки. При по явлении признака (оператора) метки в ио ходном тексте осуществляется чтение сле дующих за признаком символов по адресу в счефчике 24 модификатора 6 и запись его в восьмибайтный регистр 18. При этом размер метки подсчитывается счет- чиками 64, 65, а входы счетчиков 62, 63 блокирук)тся. Затем по адресу в счетчике 79 считывается очередная метка из таблицы меток в регистр 19, Это считывание о суще ст ляется следующим образом. Адрес таблицы меток из регистра 84 заносится в счет чик 79, а содержимое счетчиков 80 и 81 заносится в регистры 95, 96. Счетный вход счетчика 80 устанавлива ется в положение вычитания .+ 1, в счет чик 81 считывается ключ метки по адресу в счетчике 79. Затем осуществляется чтение гЛетки в регистр 19 до появления в счетчике 81 О. При появлении в счег чике 81 О осуществляется сравнение содержимого регистров 18, 19 с помощью устройства 2. В случае несовпадения на вход счетчиков 79, 8О, 81 подаются два импульса (то-есть пропускается от- носительный адрес в два байта) и считывается очередная метка из таблицы меток в регистр 19. Появление в счетчике 80 О и соответствующего сигнала на выходе дешифратора 86 означает, что просмотр таблиц меток закончен. Если к этому моменту совпадения регистров 18, 19 не было, то содержимое регистра 18 заносится в таблицу меток. Oq гщвcтвляeтcя это следующим образом. По адресу в регистре 84 заносится ключ метки из счегчижа 65 р ОЗУ 1. Затем содержимое регистра 84 заносится в счетчик 79, к счетчику 79 прибавляется. + 1, восстанавливается содержимое счетчиков 80, 81 из регистров 95, 96, счет- . ный вход счетчика 8О устанавливается на сложение + 1 и осуществляется побаЙтное « чтение - запись символов метки по адресу в счетчике 79. При этом счетчики 79, 80 работают на сложение, счетчик81 на вычитание + 1; в счетчике 79 указывается адрес очередного свободного байта, в счетчике 8О - размер таблицы меток, в счетчике 81 - размер свободной части ОЗУ 1 области таблицы меток. По окончании записи меток содержимое стетчика 74, то есть относительный адрес метки, заносится в ОЗУ 1 по .адресу в счетчике 79, после этого содержимое счетчика 79 заносится в регист 84. На этом формирование записи в таблице меток заранчивается. Совпадение содержимого регистров 18, 19 означает наличие ошибки - двух одинаковых меток Поэтому при совпадении подается сигнал в блок 14, ошибочная метка не записывается, содержимое счетчиков восстанавливается прежним. По окончании пятрй рперации происходит переход к первой операции. Шестая операция. Загрузка фазы 2, В счетчики 52, 53 заносятся адрес и раз мер области объектной программы, в счетчики 24, 25 модификатора 6 заносятся адрес и размер области полуобъектной программы. Занесение данных в счетчики модификатора 6 и 9 может осуществляться либо из ячеек ОЗУ 1, либо из регистров сверх-, оперативной памяти устройства 2 и потому в описании шестой операции строго не оговаривается. Размер области таблицы меток заносится из счетчика 79 в регистр 95. Размер области полуобъектной программы заносится из счетчика 63 в счетчик 25. Указание, через какой именно блок И проходит это занесение, не дается, так как считается, что необходимый для это го занесения блок И является составной частью одного из указанных счетчиков. Это относится и к другим подобным случаям, так как указание всех блоков И ейль)яо загромождает .схемы и описание их Затем выполняется вторая фаза, состоящая в реализации следующих операций. Седьмая операция. Чтение ключа. Ключ очередной записи полуобьекгной программы считываются по адресу в счетчике 24 модификатора 6 в счетчик 26 модификатора 6, затем к счетчику 24 прибавляется +1 и анализируются два старших разряда ключа. Если восьмой разряд ключа равен О, то осуществляется переход к восьмо операции, если седьмой разряд равен О, то осуществляется переход к девятой операции, если седьмой ключа равен 1, Гб ос гществляется переход к десятой операции. Восьмая операция. Запись Мйкрбрасширений. Очерёдное макрорасширение считывается по iaдp&cy в счетчике 24 и заноси ся в область объектной программы по адрёсу в счетчике 52 модификатора Э, В м дификаторе 6 ведется счет байтов макрорасширения путем вычитания + 1 из счет чика 26; появление О в счетчике 2б оз начает- конец макрорасширения и соответствующий сигнал С аешифратора 29 ос-г Тйнавливает запись, сигнализируя окончание восьмой операции. Затем управление передается седьмой операции. Девятая операция. Запись о;гноситель ного адреса операнда (то есть символьного адреса). Регистры 18, 19 обнуляются в счетчики 79, 80 из регистров 94, 95 заносятся адрес области таблицы меток и размер этой области. Счетчик 79 вклю- .чен на сложение + 1, счетчики 80, 81 включены на вычитание +1. 5:1 V Операнд считывается по адресу в счетчике 24 модификатора 6 в регистр 18 до тех пор, пока в счетчике 53 не появит ся О. При этом дешифратор 29 подает сигнал об окончании з агрузки регистра 18. Далее, ключ первой или очередной Метки считывается в счетчик 81, а на вхйды счетчиков 79, 80 подается импуль (+1). Затем первая или очередная метка считывается в регистр 19 до адресу в счетчике 79, До появления в счетчике 81 нуля. Пбяв1Ление нуля означает окончание загруэки метки в регистр 19, что сигнализируется сигналом с дешифратора 87. После этого осуществляется сравнение регистров 18,19с помощью устройства2.В случае совпадения содержимого регистров 18, 19 осуществляется чтение относительного адреса метки, расположенного вслед за еткой, по адресу в счетчике 79 и запись го в область объектной программы по адесу в счетчике 52 модификатора 9. При несовпадении содержимого регистов 18, 19 осуществляется аналогичное тение и сравнение следующей метки. Этот роцесс повторяется до тех пор, пока не будет найдена нужная метка или счетчик 80 не установится в нуль. Последний слу- ай означает, что просмотр таблицы меток окончен, а метка не найдена. Для об- работки этой ошибка с выхода дешифратора 87 поступает сигнал в блок 14. По окончании девятой операции управление, передается седьмой операции. Десятая операция. Запись относительного адреса литерала. Содержимое двух байт счетчика 74 модификатора 11, представляющее собой конкатенацию номера базового регистра в Старшей тетраде и относительный адрес конца объектной программы в младших тетрадазГ (по этому адресу будет записан ниже очередной литерал) заносится в поле обьектной программы по адресу в счетчике 52 модификатора 9. Затем литерал считывается из полуобъектной программы по адресу в счетчике 24 модификатора 6. и записывается в. поле полуобъектной программы по адресу в счетчике 62 модификатора 10. При этом содержимое счетчиков 24; 25, 52, 62, 63, 74 модификаторов 6, 9, 11 изменяетсяна вёййчину записываемого литерала. По окончании десятой операции осуществляется переход к.седьмой операций. Выполнение второй заканчивает- , ся с просмотром полуобъектной программы, т.е. при установлении содержимого счетчика 25 в ноль, о чем дешифратор 28 выдает соответствующий сигнал. Реализация описанных операций выполняется под управлением устройства управления 3, в когорс)М выполнены прошивки, соответствующие этим операциям. При обнаружении синтаксических ошибок в исходной программе на первой и второй фазах трансляции в блок обработки ошибок 14 подается Сигнал на передачу управления. По этому сигналу блок 14 записывает в область ошибок текст перфокарты, в которой обнаружена ошибка, если идет первая фаза трансляции. Известно, Что в заданных позициях перфокарть записан ее номер, который-слуЖИГ первой частью адреса ошибок. Второ частью адреса ошибки является номер ош бочного символа в перфокарте, когорЕзТй записывается после текста перфокарты блоком 14. После этого блок 14 записы вает название ошибки. На этом составление записи об ошибке на первой фазе заканчивается. На второй фазе может быть только од на ошибка - отсутствие метки. Поэтому запись об ошибке состоит из имени оши- бочной метки и названия ошибки. Работа блока ошибок 14 и всей систе мы при обнаружении ошибок осушествляет ся по принципу локализации и игнорировани ошибки. Реализация этих принципов позволяет после занесения адреса ошибки в та лицу ошибок запускать систему в работу дальше до тех пор, пока не встретится не ошибочная ситуация. Это позволяет выявить при одной трансляции максимальное количество ошибок. Стековый регистр 35 выполняет операции, составляющие суть поэтапной трансляции алгебраических выражений. Для определенности положим, что для /арифметики с плаваюшеи точкой для первого подуровня берется второй регистр, для второго подуровня берется четвертый регистр. В исходном состоянии во всех байтах регистра 35 - нули. Заполнен;и.е регистра 35 сведено в таблицу. Информация в первый байт региста 35 заносится для распознавания ошибки отсутствие операнда между двумя операциями, а так же для распознавания индеко ной круглой скобки (в Фортране 1У) от иерархической круглой скобки. Заполнение стекового регистра 35 осуществляется в следующем порядке: первый символ заносится в первый байт регистра 35, затем дешифратор 36, в соответствии с состоянием регистра 35, подает сигнал на перемещение (сдвиг вправо) данного символа вопределенный байт регистра 35Jпри этом символ С во втором байте стирается. Если код первой операции начинался знаком кавычки (), го этот знак заносится в восьмой байт, знак операций равенство ) или сравнение ( : ) заносится в пятый байт,, символ типа арифметики - в седьмой байт регистра 35. Ес ли код первой операции состоит из одного знака, в байтах 7 и 8 остаются пули. Закрывающие кавычки кода первой операции в регистр 35 не заносятся. Знак кавычки в восьмом байте позволяет записать в пятый байт символ типа арифметики. Символ типа арифметики служит переключателем при выборке констант соответствующей арифметики из таблицы макрорасширений. Знаки второй и третьей очередной операции заносятся соответственно в четвертый и третий байт регистра 35. Выборка знаков стекового регистра 35 для трансляции осуществляется в порядке, определяемом соответствуюш, состоянием стекового регистра 35. Состояния регистра 35 сведены в таблицу. При этом введены следующие обозначения; операция трансляция (+) означает трансляцию сложения, выполняемую арифметико-логическим устройством; операция сдвиг означает перемещение символов в регистре 35. В первой строчке указано исходное состояние регистра 35, в последующих-промежуточные состояния, в последней - конечное состояние регистра 35. В таблицег используются все четыре алгебраических знака +, -, х, /, хотя знаки одного подуровня взаимозаменяемы и могут ставиться в соответствующих позициях произвольно. Символ уозначает наличие произвольного символа, символ С означает наличие V символьного адреса, точнее, его последнего символа, так как предыдущие символы зати-; раются последним. Знак-индексная открывающая скобка С является операцией перехода на третий индексный подуровень, он заносится в третий байт регистра 35. Цри его появлении дешифратор 36 настраивается на выборку таких команд из таблицы макрорасширений, которые будут модифицировать адреса операндов с помощью индексов. С появлением в первом байге регистра) 33 знака заттятая , заканчивается модификация адреса операнда с помощью индекса.-: С появлением.в первом байте регистра 33 знака закрывающая индексная скобка 3 заканчивается модификация адреса с помошью очередного индекса, осуществляется выход с индексного подуровня, а значение операнда, выбранное по модифицированному адресу, заносится в соответствующий регистр. После этого содержимое первого, второго, третьего байтов регистра 33 устанавливается в нуль.. Знак открывающая скоба ( является операцией перехода на очередной верхний уровень алгебраического выражения (см.

таблицу). Его появление в первом байге регистра 33 настраивает дешифратор 34 на выборку таких команд из таблицй макрорасширений, которые осуществляют Зйпаеь промежуточных результатов из регистров 2 и 4 в оперативную память (в стек промежу.точных результатов, адрес которого указан программистом в общем регистре 12).; Затем дещифратор 36 подает сигнал на запись пятого и четвертого байта из регистра 35 в оперативную память (в стек операций) под счетчиками 48, 49 через блок схем И 47. После этого содержимое с первого по пятый байт регистра 35 устанавливается в нуль, и регистр 35 подготовлен для приема знаков очередного уровня алгебраического выражения. Знак закрывающая скобка ) являетён операцией пе рехода на очередной нижний уровень алгебраического выражения. Bix) появление в первом байте регистра 35 настраивает 36 на выборку команд из таблицы макрорасширений и запись их в полуобъектную программу. Эти команды осуществляют запись результата текущего уров11Я в своШднъгй регистр 6, восстановление результатов предыдущего уровня с помощью стека про межуточных результатов в регистр 2, 4, слияние результатов текущего уровня, т.е. содержимого регистра Ь, с результ атом Состояния стекового регистра 35 (с 1 по 6

восстановленного уровня с помощью соответствующего знака операции восстановленного уровня.

Запись в стек операций и в стек результатов осуществляется и при нулевом значении четвертого и пятого байта регистра 35 и регистров 2, 4. В случае нулевого значения байтов 5 и 4 регистра 35, запись результатов в стек резуль татов не нужна,С появлением знака точка С запятой ; заверщается трансляция выражения. При этом осуществляется слияние результатов второго подуровня (если они были) с результатами первого подуровня, и генерируется команда занесения результата по адресу первого операнда или сравнение результата с числом, адрес которого указан nepBbnvi операндом. Затем стековый регистр 35 устанавливается в нуль и он готов для трансляции следующего выражения., Для использования круглых скобок ( ) в качестве индексных необходимо увели ить стековый регистр 35 до девяти байт, отвести под индексные скобки специально третий байт, соответственно сдвинуть расположение других знаков и внести соответствующие изменения в дешифратор 36.. &ВИДУ тривиальности действий с индекснымЙ скобками соответствующие состояййя регистра 35 в таблице не показаны. байт)- лица

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синтаксического анализа программ | 1980 |

|

SU918950A1 |

| Устройство для синтаксически-управляемого перевода | 1982 |

|

SU1062721A1 |

| Устройство для обработки выражений языков программирования | 1974 |

|

SU519715A1 |

| ФОРМУЛЬНЫЙ ПРОЦЕССОР С КОМАНДОПОДОБНЫМИ ЛОГИЧЕСКИМИ УПРАВЛЯЮЩИМИ ЭЛЕМЕНТАМИ | 1997 |

|

RU2143726C1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1115063A1 |

| Устройство для отладки программ | 1985 |

|

SU1297064A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для отладки программ | 1979 |

|

SU849218A1 |

| УСТРОЙСТВО СОРТИРОВКИ ИНФОРМАЦИИ | 2004 |

|

RU2274893C2 |

| Транслятор языков программирования | 1981 |

|

SU1387018A1 |

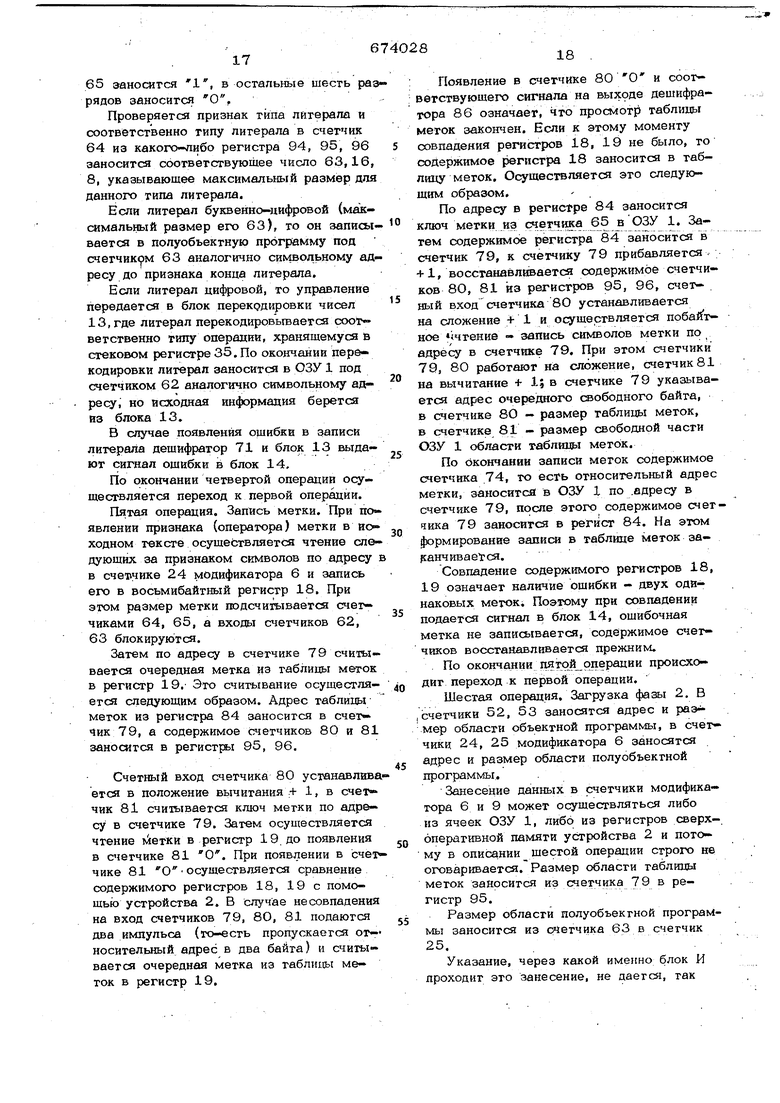

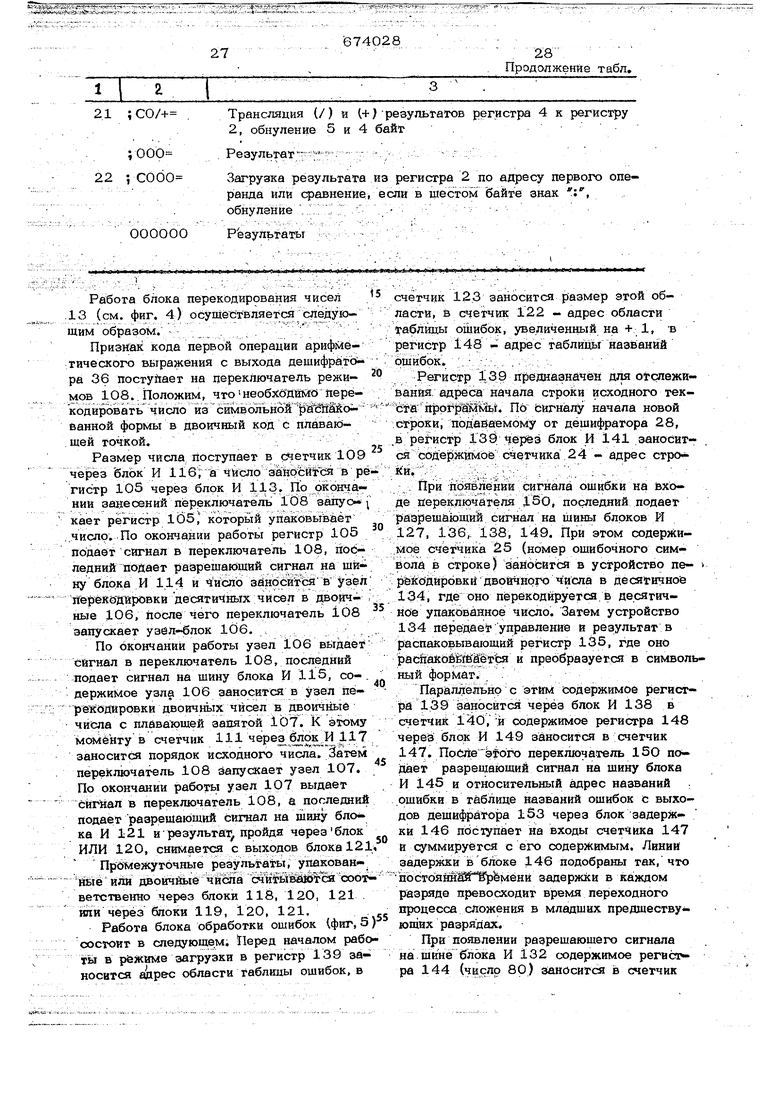

1 СООООО Трансляция () загрузки перв соооо регистр, сдвиг {). Результат 00000 2 +СбОС) Трансляция загрузки второго 0000+ Результат 3/СОО+ Трансляция загрузки третьего Результат оооз+ Трансляция (/), сдвиг ( ) ООЬн+ Результат Трансляция () ), (+) со слия 5-СО + сдвиг (-) 0000- Результат Трансляция (-), сдвиг (+) 6+СОО- 0000+ РёШрпВгаТ го операнда в общий . перанда, сдвиг (+) операнда, сдвиг (/) ием результатов (+),

25 7.-СООО ОООО 8/СОШ 0000/ 9+СОО/ oodo+ 10(0000 00000 11(0004- - 00000 12(00/+ 00000 13.)СООО ооопп 14)СООО+ 0)ОПП 15)СО/+ о)опп 160)ОЛ+ . 0000+ .17 0|00+ П)ОШ- 18-)00+ 000019/)00+ 000/+ 20; СОО+ ;0000

674028

26 Продолжение таблицы Трансляция загрузки первого операнда, сдвиг () Резульгаг Трансляция (-), сдвиг (/) Результат . Трансляция (/), сдвиг (+) Результат . Загрузка пятого и чсегвертого: байтов регистра 35 в стек невыполненных операций, обнуление Результат .-.. -: , .-, ...: Трансляция загрузки стека невьшо)шекнь1х операций и стека результатов взрегйстр & 2 и 4, обнуление .Результат .- ,..-/:;/: V . Трансляция загру1зкй Стека нёвыпойнейшхойераций и стека результатов.из регистров 2 в 4, обнуление Результат; /;;.,.;.-:.:./.; :V/.;.;- ;.//-/:::.. .;,- , . , Выгрузка двух байт из стека невыпопценных операций . и занесение их в пятый и четвертый байт регистра 15 Результат (см. пц. 2-9 таблицы) Трансляция (+), выгрузка двух байт из стека невыполненцых операций, трансляция зшебениярезультатоЕ (+) в регистр 6, из стека рё зудьТат6в и загруэки их в |регис1ри 2 а 4, сдвиг ) Результат (см. ш, 2-) Трансляция (/), (+) со слиянием результатов (/), занесение результатов (+) в регистр 6, выгрузки нз стека.результатов, сяваг ) Результаты (см. ш, 2-9), . Транслящия (j) результатов регистров 2 а 6, обнуление третьего байта Результат, тение очередногх) знака в регистр 35 езультат рансляция (+) к регистру 2 регистра 6,-сдвиг (-) езультат , рансляция загрузки регистра 6 в регистр 4, сдвиг (/) езультат ранслящш (+}, обнуление 5 и 4 байт езультат

674028

27 21;СО/+ ;000 22; СОбО ОООООО Работа блока перекодирова)ния чисел .13 (см. фиг. 4) осущёствшется;(:Ледув щим образом. . Признак кода первой операции арифметического выражения с выхода дешифрагора 36 постуйает на переключатель режимов 108.. Положим, что 1 необхбдййо перекодировать число из сймвольн6й р1ШШббанной формы в двоичный код с плавающей точкой. Размер числа поступает в счетчик 109 через блок И 116; И Число заносится в ре гистр 105 через блок И 113. По окончании занесений переключатель 108 запускает регистр 105, который упаковывает ..число. По окончании работы регистр 105 подает сигнал в переключатель 108, iioc;леднкй подает раарешанзщий сигнал )яа шину блока и 114 и зйнос№ЬяВ узел лерекщйровки десятичных Чисел в двоичвые 106, после чего переключатель 108 запускает узел-блок 1О6. . По окончаний работы узел 106 выдает сигнал в переключатель 108, последний подает сигнал на шину блока И 115, содержимое узла 1О6 заносится в узел пе р еткодировки двоичньтх чисел в двоичные числа с плйвающей завзятой 107. К этому моменту ia счетчик 111 через бпо И 117 заносится порядок исходного числа. переключатель 1О8 запускает узел 107. По окончании работь узел 107 выдает сигнал в переключатель 108, а последний подает разрешающий сигнал на шину блока И 121 и результат, пройдя черезблок ИЛИ 120, снимается с выходов блока 121 Промежуточные результаты, упакованйыё° илм двойчйлечйШа счйШШЙгсй соот ветственно через блоки 118, 120, 121 ши через блоки 119, 120, 121. Работа блока обработки ошибок Чфиг, S состоит в следующем. Г1еред началом рабо ты в рёжтаме загрузки в регистр 139 заносится aijpec области таблицы ошибок, в

Продолжение табл. Трансляция (/) и +}резупьтагов регистра 4 к регистру 2, обнуление 5 и 4 байт Резульгатр ; :;:;.- -/:/, . Загрузка результата из регистра 2 по адресу первого операнда или сравнение, если в шестом байте знак :, обнуление Результаты счетчик 12.3 заносится размер этой области, в счетчик 122 - адрес области таблицы ошибок, увеличенный на +1, в регистр 148 - адрес таблицы названий ошибок.. ;. . -..-., . :,.: -..; ; Регистр 139 п{)еднааначе11 для отслеживания, адреса начала строки исходного текстйпрЬ1 рщШг. По Ьигн;ал начала новой строки, подаваемому от дешифратора 28, в регистр 139 через блок И 141 заносится содержимое счетчика 24 - адрес строки. При появлении сигнала ошибки на входе нереключателя 15О, последний подает разрешающий сигнал на шины блоков И 127, 136,: 138, 149. При этом содержи.мое счетчика 25 (номер ошибочного символа в строке) заносится в устройство пе- рёкбДйрбвкй ДВОИЧНОГО числа в десягичное 134, где оно перекодируется, в десятичное упакованное число. Затем устройство 134 передает управление и результат в распаковывающий регистр 135, где оно расйакоёШЙётЬя и преобразуется в символьный формат. . Параллельнр с этим содержимое регистipa 139 заносится через блок И 138 в счетчик 140, И содержимое регистра 148 через блок И 149 заносится в счетчик 147. noCjie eforo переключатель 150 подает разрешающий сигнал на шину блока И 145 и относительный адрес названий : ошибки в таблице названий ошибок с выходов дешифратора 153 через блок задержки 146 пбсэупает на входы счетчика 147 и суммируется с его содержимым. Линии задержки в блоке 146 подобраны так, что постояннШ ёмёнй задержки в разряде превосходит время переходного процесса сложения в младших предшествующих разрядах. При появлении разрешающего сигнала на ш(ше блока И 132 содержимое регисч ра 144 (число 80) заносится в счетчик 29. 125. После эгого переключатель 130 дает в устройство управления 3 сигнал на чтение перфокарты с ошибкой по адресу в счетчике 140 и запись ее в область таблицы ошибок по адресу в счетчике 122. s При этом счетчики 140, 122, 124 работают на сложение +1, а счетчйжи 123, 125 - на вычитание +1. Перезапись чивается, когда в счетчике 125 появится О и дешифратор 127 подает при этом Ю сигнал в переключатель 150, останавливающий перезапись.,. Затем на входь счетчиков 122, 123, 124 подается импульс для записи однобайтного разделителя. 5 После этого содержимое регистра 135 . через блок И 137 считывается в ОЗУ 1 по адресу в счетчике 122, для чего размер записи регистра 135 заносится в счетчик 125. 20 При появлении в счетчике 12:5 н нулевого .сигнала на выходе дешифратора 127 запись содержимого регистра 135 в ОЗУ 1 прекращается переключателем 150. После этого переключ атель 15О подает сигнал на чтение ключа названия ошибки по су в счетчике 147 и запись его в счетчик 125. После чтения ключа к содержимому счетчика 147 прибавляется +1 и переключатель 150 подает сигнал в устройство ° управления 3 на чтение названия ошибки по адресу в счетчике 147 и запись его в строку таблицы ошибок по адресу в счетчике 122, . При появлении в счетчике 125 нуля дешифратор 127 выдает сигнал в переключатель ISO, и последний подает сигнал. в устройство 3 об окончании перезаписи. После этого содержимое счетчика 124, т.е. ключ записи, блок И 133 зано- сится в ОЗУ 1 по адресу в регистре 130, а затем содержимое счетчика 122 через . блок И 129 заносится в регистр 130. На этом формирование записи в табли це ошибок заканчивается и управление передается на продолжение трансляции в блок, откуда пришла ошибка, с помощью устройства 3. В случае появления нуля в счетчике 123 дешифратор 126 выдает сигнал о полнении области таблицы ошибок в устройство 3.. Работа блока ошибок 14 на второй фазе имеет следующие отличия. Ключ метки заносится в счетчик 125 и в регистр 135, адрес метки заносится в регистр 139, Таким образом, вместо номера ошибочного байта в записи будет стоять раз67402830мер мегкив байтах, а вмесго- записи 80 байт перфокарты будет записана метка, последовательность микроопераций работы блока 14 при этом не изменятся, Работа стека, изображенного на фиг. 7, состоит в выполнении следующих операций: загрузки и выгрузки В исходном состоянии стека счетчик 159 и регистр 161 установлены в нуле. В режиме загрузки переключатель 158 подает на шину блока И 166 разрешающий сигнал, и .содержимое регистра 161 заносится в счетчик 159, к которому затем прибавляется +1. После этого переключатель 158 включает выход генерато- ра 157 на отрицательный {т.е. на вычитанне +1) счетный вход счетчика 159. Выходы счетчика 159-анализируются дешифратором 16О, с выходов которого разрешающие сигналы поступают на байтные шины блока И 163, в соответствии с чаетотой генератора 157. При этом содержи.мое элеменгш памяти блока 162 перезаписывается со сдвигом вправо на один элемент памяти. Период генератора 157 выбирается большим .переходного процес. са при перезаписи элементов в блоке 162. При появлении в счетчике 159 числа О , дешифратор 16О подает сигнал fe переключатель 158, последний отключает вход счетчика 159 от генератора 157 и перезапись прекращается, После этого в .освободившийся старший элемент памяти блока 162 (. во входные байты) заносится информация через блок И 168, переключатель 158 подает разрешающий сигна.л на шину блока И 167 и содержимое счетчика 159 заноснтся в регистр 161 через блок И 167, На этом загрузка стека кончается, . При выгрузке стека 162 на шину блока И 169 подается разрешающий сигнал и содержимое старшего элемента памяти . блока 162 выгружается из стека. Далее, переключатель 158 подает сигнал в счетчик .159, устанавливая его в нуль, и включает на положительный вход (т.е. на сложение +1) счетчика 159 выход генератора 157, при. этом дешифратор 16О, анализирующий состояние счетчика 159, пода ет разрешающие сигналы на байтные шины блока И 163, осущес1вляя перезапись элементов памяти со сдвигом влево на один элемент. При совпадении содержимого счетчика 159 и регистра 161 блок И165 вырабатывает сигнал окончания перезаписи, подавая его в переключатель 158. После.цний переключает отрицательный вход счетчика 159 на выход генератора 157 на один такт, т.е. для уменьшения содержимого счетчика 159 на +1. После этого, переключатель 158 отключает вход счетчика 159 от выхода ге нератора 157 и подает на шину блока И 167 разрешающий сигнал,, при этом содер жимое счетчика 159 заносится в регистр 161 и выгрузка из стека заканчивается. Описанный стек может применяться не только при трансляции, но и при вычислении алгебраических выражений, для чего должны быть введены в ассемблер ЭВМ Ком/анды загрузки и выгрузки стека. Результатом работы системы являет- ся перемещаемый программный модуль, сх ставленный в кодах машин. В гекёте модуля находится программно органйзоранный стек, использующий часть регйст ров и часть памяти оперативного аапоминающего устройства, для хранения резуль fiafoB промежуточных вычислений алгебра ИчесжИх вьгражений.v / Для трансляции алгебраических выражений с фортран-1У и Алгол-60 необходимо в строках таблицы меток, таблицы литералов ввести байт гтризнака чисел. Этот признак следует испрльаовать пр коррекции кода операции. Если число имеет признак вещественного, то в код операции вводится коррекция, преобразующая данный кой в код операции над числаШ с плавающей запятой, если число имеет признак целого, то данный код преобразуется в кс(д операции шд целыми числа- ми.. V - -:-, . , - : ,... .. / : / Для выполнения этой коррекции необхо димо в устройство управления 3 ввести дополнительные элементы, позволяющие организовать цикл коррекции кода операци повторяющийся столько раз, сколько операций имеется в алгебраической выражении. Из этого следует, что время траиоляции алгебраических выражений на языке ЛМАС1 меньше времени ,трансляции на языках Фортран-1У или Алгол-60 на интервал времени, затрачиваемый на выполнение цикла коррекции кода операции. Формула изобретения - . . 1. Система для трансляции с проблем но-ориентированного языка, содержащая вычислительное устройство, соединенное двухсторонними, связями с операгйвньш запоминающим устройством и устройс№ом управления, которое через устройство управления каналами соединено двухсторонними связями с внешним запоминающим устройством, управляющий вход оперативного запоминающего устройства соединен с выходом устройства управления, отличающаяся тем, что, с целью повышения быстродействия, в нее введены модификаторы адреса символов исходного текста, адреса макрокоманд, адреса полу- объектных команд, адреса обьектнЬ1х команд, адреса меток, символьный анализатор, операторный анализатор, блоки перекодировки чисел и обработки ошибок, управляющие входы которых подключены к вызсоду устройства управления, выход вычислительного устройства соединен с первыми входами символьного и операторного анализаторов и блока перекодировки чисел, первый вь1ход и второй вход символьного анализатора соединены соответственно ср вторым входом и первым выходом операторного анализатора, бторой выход которого подалючен к первому входу модификатора адреса макрокоманд, третий выход соединен с первыми входами модифиКатбров адреса полуобьектных команд и адреса объектных команд, четвертый выход подключен к первому входу модификатора адреса метЬк, первые выходы блока перекодировки чисел, модификаторов адреса меток, адреса объектных команд, адреса полуобъбктных команд, адреса символов исходного текста, второй выход символьного айализагбра и цятый вьгход операторного анализатора соединены с первым входом блока обработки ошибок, второй выход блока перекодировки чисел, первые выходы блока обработки ошибок и модификатора адреса макрокоманд, шестой выход операторного анализатора и третий выход символьного анализатора соединены со входом у стройства управления, седьмой выхбд операторного анализатора .подключен ко входу модификатора адреса символов исходного текста, вторые входы модификатора адреса макрокоманд, модификатора адреса меток , и блока обработки ошибки соединены с выходом оперативного запоминающего устройства, входы которого соединены с соответствующими выходами введенных модификаторов, анализаторов, блока перекодировки чисел и блока обработки ошибок. 2. Система по п. 1, о т л и ч а ю щ а Я с я тем, что символьный а1шлизатОр содержит два счетчика, выход первого из которых соединен со входом блоКа И, первый управляющий вход которого подключей к управляющему входу символьного анализагора, выход второго счегчлкй соединен схэ входом дешифратора, выходы которого подключены соответственно к первому, второму и третьему выходам с5им вольного анализатора, первый вход которого соединен со входами счетчиков, второй вход - со вторым управляющим входом блока И, быход которого соединен с выходом СИМВОЛЬНОГО анализатора.

Источники информации, -принятые во вниманке при экспертизе

iV Патент США № 3593312. кл. 340-.17Й.5, 1971.

.2. Опубликованная заявка Великобритании № 14О7761, кл. СгОб F 15/20, .1975, :

//2./

I S ff5 6 I

f . Ф . Д

П

1/фJ y

Пи

Риг.6

Авторы

Даты

1979-07-15—Публикация

1976-11-29—Подача