ОО 00

VI

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2002 |

|

RU2204884C1 |

| Устройство для измерения амплитуды одиночных импульсных сигналов | 1982 |

|

SU1112301A1 |

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ ЧИСЛОВЫХ ВЕЛИЧИН | 1965 |

|

SU167366A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

| Аналого-цифровой преобразователь | 2017 |

|

RU2656989C1 |

| Способ преобразования аналогового сигнала в цифровой сигнал и устройство для его осуществления | 1977 |

|

SU892704A1 |

| Устройство для определения максимальных значений импульсов при ультразвуковой дефектоскопии | 1985 |

|

SU1288591A1 |

| Преобразователь напряжения в код | 1974 |

|

SU507930A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU809556A1 |

| Устройство для измерения амплитуды одиночных импульсных сигналов | 1980 |

|

SU960644A1 |

Изобретение относится к электроизмерительной и вычислительной технике и предназначено для преобразования амплитуды импульсов в код. Способ основан на выполнении первой операции считывания амплитуды импульса, а во время убывания его амплитуды производится вычитание из максимального значения амплитуды импульса его убывающего значения, нижний предел которого зафиксирован первым считыванием и второй операцией считывания (методом одного отсчета) разностного напряжения. Суммирование результатов первого и второго считываний в момент времени максимума разностного н; 1 ряжения позволяет определить максимум амплитуд -, электрического импульса в цифрово;- фспше. Устройство, реализующее предлагаемый спосоГ). состоит из двух параллельно подключенных каналов: в первом фиксируется в ПЗУ результат первого считывания известным ., а на втором выходе формируется логическая единица в момент времени максимума разностного напряжения, во втором, состоящем из последовательно соедниенных пикового детектора, вычитающего устрсч ктв.ч п точного АЦП, осуществляется формнпон,. ние разностного напряжения и считывание его (методом одного отсчета) точным АЦП. 2 с.п.ф-лы, 2 ил. O (/ с

со

4:

Изобретение относится к цифровой измерительной и вычислительной технике.

Цель изобретения - повышение точности.

Способ преобразования максимума амплитуды электрического импульса в цифровую форму заключается в сравнении преобразуемого сигнала с набором опорных уровней, соответствующих старшим разрядам формируемого кода, формировании и запоминании кода, соответствующего количеству опорных уровней напряжений, превышенных преобразуемым сигналом, в момент равенства уменьшаюшегося после достижения максимума преобразуемого сигнала ближайшему опорному уровню, причем одновременно со сравнением преобразуемого сигнала с набором опорных уровней запоминают максимум амплитуды преобразуемого сигнала и вычитают из последнего преобразуемый сигнал, а в момент равенства уменьшающегося преобразуемого сигнала ближайшему опорному уровню сравнивают разностный сигнал с набором опорных уровней, соответствующих младшим разрядам формируемого кода, формируют код младщих разрядов и суммируют его с кодом старших разрядов.

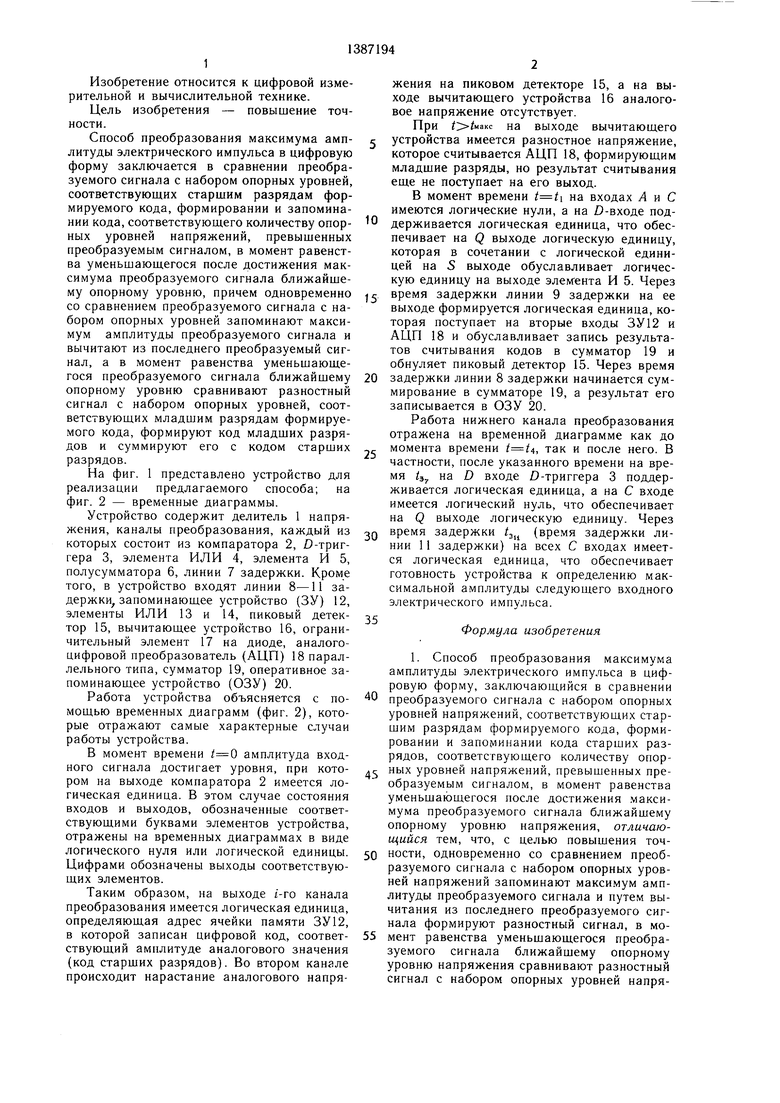

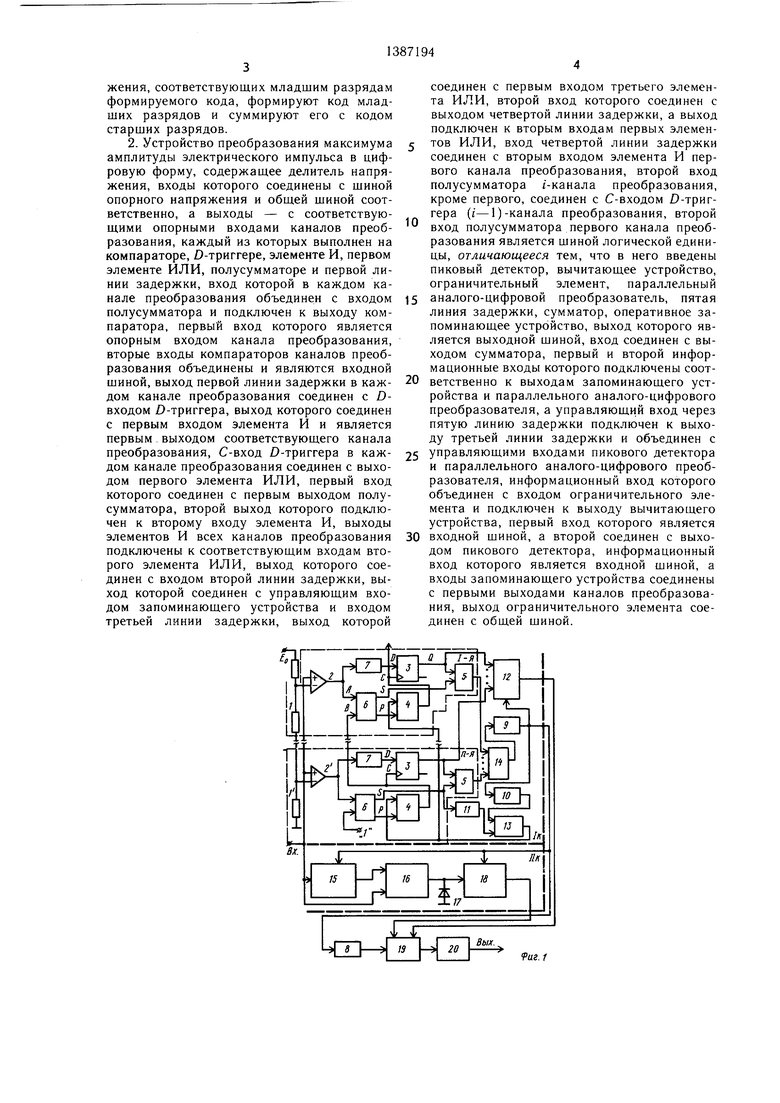

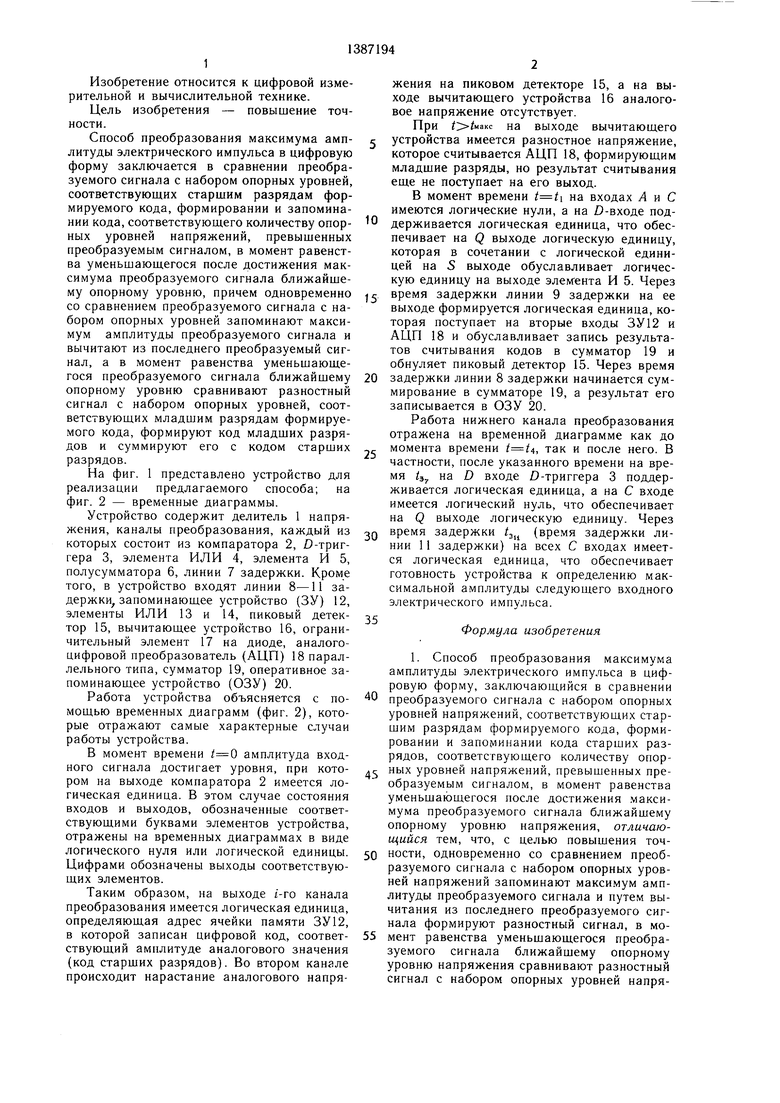

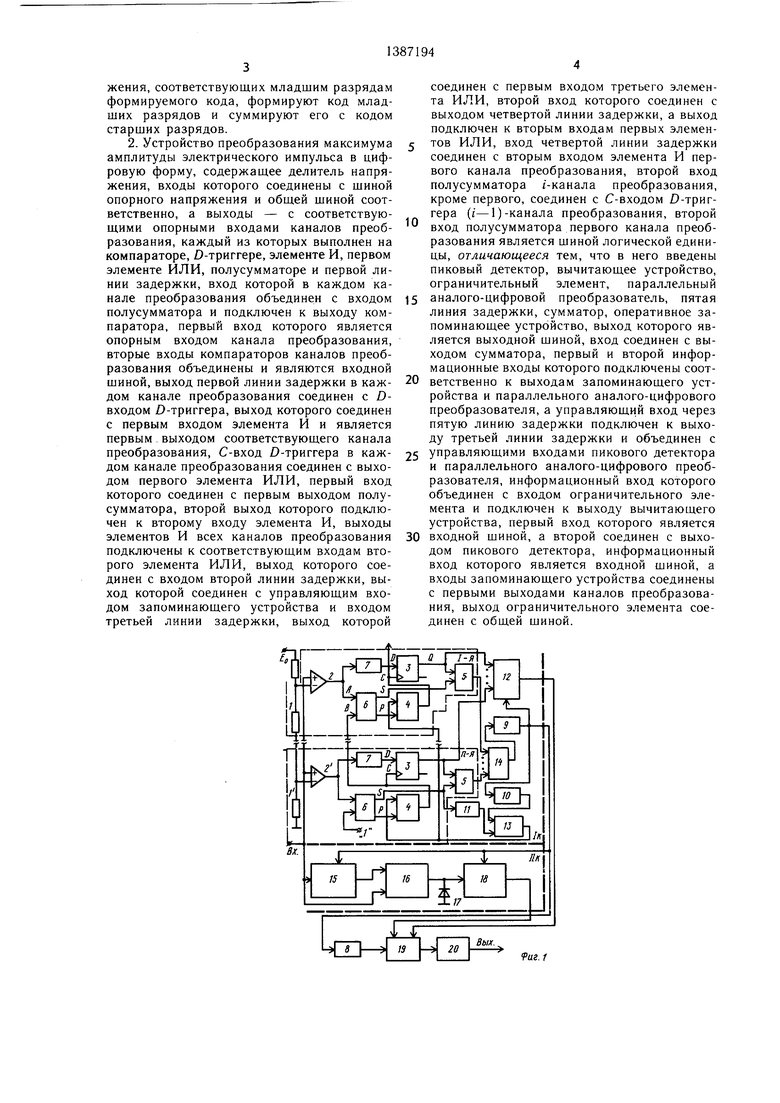

На фиг. 1 представлено устройство для реализации предлагаемого способа; на фиг. 2 - временные диаграммы.

Устройство содержит делитель 1 напряжения, каналы преобразования, каждый из которых состоит из компаратора 2, D-триг- гера 3, элемента ИЛИ 4, элемента И 5, полусумматора 6, линии 7 задержки. Кроме того, в устройство входят линии 8-11 задержки запоминающее устройство (ЗУ) 12, элементы ИЛИ 13 и 14, пиковый детектор 15, вычитающее устройство 16, ограничительный элемент 17 на диоде, аналого- цифровой преобразователь (АЦП) 18 параллельного типа, сумматор 19, оперативное запоминающее устройство (ОЗУ) 20.

Работа устройства объясняется с помощью временных диаграмм (фиг. 2), которые отражают самые характерные случаи работы устройства.

В момент времени амплитуда входного сигнала достигает уровня, при котором на выходе компаратора 2 имеется логическая единица. В этом случае состояния входов и выходов, обозначенные соответствующими буквами элементов устройства, отражены на временных диаграммах в виде логического нуля или логической единицы. Цифрами обозначены выходы соответствующих элементов.

Таким образом, на выходе /-го канала преобразования имеется логическая единица, определяющая адрес ячейки памяти ЗУ12, в которой записан цифровой код, соответствующий амплитуде аналогового значения (код старших разрядов). Во втором канале происходит нарастание аналогового напряжения на пиковом детекторе 15, а на выходе вычитающего устройства 16 аналоговое напряжение отсутствует.

При на выходе вычитающего

устройства имеется разностное напряжение, которое считывается АЦП 18, формирующим младшие разряды, но результат считывания еще не поступает на его выход.

В момент времени на входах Л и С имеются логические нули, а на D-входе поддерживается логическая единица, что обеспечивает на Q выходе логическую единицу, которая в сочетании с логической единицей на 5 выходе обуславливает логическую единицу на выходе элемента И 5. Через

время задержки линии 9 задержки на ее выходе формируется логическая единица, которая поступает на вторые входы ЗУ 12 и АЦП 18 и обуславливает запись результатов считывания кодов в сумматор 19 и обнуляет пиковый детектор 15. Через время

0 задержки линии 8 задержки начинается суммирование в сумматоре 19, а результат его записывается в ОЗУ 20.

Работа нижнего канала преобразования отражена на временной диаграмме как до

- момента времени , так и после него. В частности, после указанного времени на время /ЗУ на D входе )-триггера 3 поддерживается логическая единица, а на С входе имеется логический нуль, что обеспечивает на Q выходе логическую единицу. Через

Q время задержки /э, (время задержки линии 11 задержки) на всех С входах имеется логическая единица, что обеспечивает готовность устройства к определению максимальной амплитуды следующего входного электрического импульса.

Формула изобретения

0 преобразуемого сигнала с набором опорных уровней напряжений, соответствующих старшим разрядам формируемого кода, формировании и запоминании кода старших разрядов, соответствующего количеству опор5 ных уровней напряжений, превышенных преобразуемым сигналом, в момент равенства уменьшак)щегося после достижения максимума преобразуемого сигнала ближайшему опорному уровню напряжения, отличающийся тем, что, с целью повышения точ0 ности, одновременно со сравнением преобразуемого сигнала с набором опорных уровней напряжений запоминают максимум амплитуды преобразуемого сигнала и путем вычитания из последнего преобразуемого сигнала формируют разностный сигнал, в мо5 мент равенства уменьшающегося преобразуемого сигнала ближайщему опорному уровню напряжения сравнивают разностный сигнал с набором опорных уровней напряжения, соответствующих младшим разрядам формируемого кода, формируют код младших разрядов и суммируют его с кодом старших разрядов.

соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом четвертой линии задержки, а выход подключен к вторым входам первых элементов ИЛИ, вход четвертой линии задержки соединен с вторым входом элемента И первого канала преобразования, второй вход полусумматора /-канала преобразования, кроме первого, соединен с С-входом D-триг- гера (г-1)-канала преобразования, второй

вход полусумматора первого канала преобразования является шиной логической единицы, отличающееся тем, что в него введены пиковый детектор, вычитающее устройство, ограничительный элемент, параллельный

аналого-цифровой преобразователь, пятая линия задержки, сумматор, оперативное запоминающее устройство, выход которого является выходной шиной, вход соединен с выходом сумматора, первый и второй информационные входы которого подключены соответственно к выходам запоминающего устройства и параллельного аналого-цифрового преобразователя, а управляющий вход через пятую линию задержки подключен к выходу третьей линии задержки и объединен с

управляющими входами пикового детектора и параллельного аналого-цифрового преобразователя, информационный вход которого объединен с входом ограничительного элемента и подключен к выходу вычитающего устройства, первый вход которого является

входной щиной, а второй соединен с выходом пикового детектора, информационный вход которого является входной щиной, а входы запоминающего устройства соединены с первыми выходами каналов преобразования, выход ограничительного элемента соединен с общей шиной.

fag. 1

| Бахтиаров Г | |||

| Д | |||

| и др | |||

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Пылеочистительное устройство к трепальным машинам | 1923 |

|

SU196A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Авторское свидетельство СССР по заявке № 3915743/28, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-04-07—Публикация

1986-09-15—Подача