1

Изобретение относится к связи, может быть использовано в приемных устройствах или в устройствах обработки данных для обнаружения комбинации двоичных сигналов известного типа при неизвестном моменте прихода.

Целью изобретения является обеспечение возможности обнаружения комбинаций произвольной длины и обнаружения одновременно двух комбинаций, а также упрощение устройства при больших длинах обнаруживаемых комбинаций.

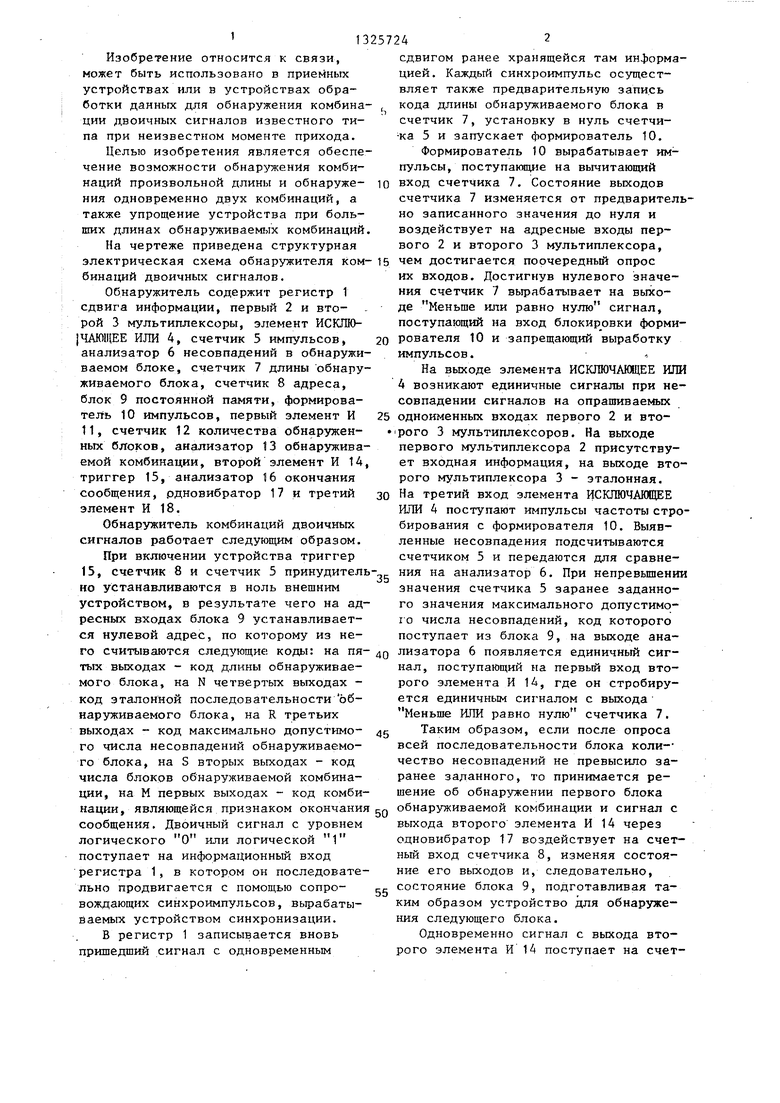

На чертеже приведена структурная

13

электрическая схема обнаружителя ком- 15 чем достигается поочередный опрос

бинаций двоичных сигналов.

Обнаружитель содержит регистр 1 сдвига информации, первый 2 и второй 3 мультиплексоры, элемент ИСКЛНЬ |ЧАЮЩЕЕ ИЛИ 4, счетчик 5 импульсов, анализатор 6 несовпадений в обнаруживаемом блоке, счетчик 7 длины обнаруживаемого блока, счетчик 8 адреса, блок 9 постоянной памяти, формирователь 10 импульсов, первый элемент И 11, счетчик 12 количества обнаруженных блоков, анализатор 13 обнаруживаемой комбинации, второй элемент И 14, триггер 15, анализатор 16 окончания сообщения, рдновибратор 17 и третий элемент И 18.

Обнаружитель комбинаций двоичных сигналов работает следующим образом.

При включении устройства триггер

15, счетчик 8 и счетчик 5 принудитель- ния на анализатор 6. При непревьппении

но устанавливаются в ноль внешним устройством, в результате чего на адресных входах блока 9 устанавливается нулевой адрес, по которому из него считываются следующие; коды: на пятых выходах - код длины обнаруживаемого блока, на N четвертых выходах - код эталонной последовательности обнаруживаемого блока, на R третьих выходах - код максимально допустимого числа несовпадений обнаруживаемого блока, на S вторых выходах - код числа блоков обнаруживаемой комбинации, на М первых выходах - код комби40

45

значения счетчика 5 заранее заданного значения максимального допустимого числа несовпадений, код которого поступает из блока 9, на выходе анализатора 6 появляется единичный сигнал, поступающий на первый вход второго элемента И 14, где он стробиру- ется единичным сигналом с выхода Меньше ИЛИ равно нулю счетчика 7. Таким образом, если после опроса всей последовательности блока коли- чество несовпадений не превысило заранее заданного, то принимается решение об обнаружении первого блока

нации, являющейся признаком окончания Q обнаруживаемой комбинации и сигнал с

сообщения. Двоичный сигнал с уровнем логического О или логической 1 поступает на информационный вход регистра 1, в котором он последовательно продвигается с помощью сопровождающих синхроимпульсов, вьфабаты- ваемьгх устройством синхронизации. В регистр 1 записывается вновь пришедший сигнал с одновременным

55

выхода второго элемента И 14 через одновибратор 17 воздействует на счетный вход счетчика 8, изменяя состояние его выходов и, следовательно, состояние блока 9, подготавливая таким образом устройство для обнаружения следующего блока.

Одновременно сигнал с выхода второго элемента И 14 поступает на счет

57242

сдвигом ранее хранящейся там информацией. Каждый синхроимпульс осуществляет также предварительную запись

, кода длины обнаруживаемого блока в ь

счетчик 7, установку в нуль счетчика 5 и запускает формирователь 10.

Формирователь 10 вырабатывает импульсы, поступакмц е на вычитающий 10 вход счетчика 7. Состояние выходов счетчика 7 изменяется от предварительно записанного значения до нуля и воздействует на адресные входы первого 2 и второго 3 мультиплексора.

их входов. Достигнув нулевого значения счетчик 7 вырабатывает на выходе Меньше или равно нулю сигнал, поступающий на вход блокировки формирователя 10 и запрещающий выработку импульсов.

На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 возникают единичные сигналы при несовпадении сигналов на опрашиваемых

одноименных входах первого 2 и вто- ого 3 мультиплексоров. На выходе первого мультиплексора 2 присутствует входная информация, на выходе второго мультиплексора 3 - эталонная.

На третий вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 поступают импульсы частоты стро- бирования с формирователя 10. Выявленные несовпадения подсчитываются счетчиком 5 и передаются для сравне0

5

значения счетчика 5 заранее заданного значения максимального допустимого числа несовпадений, код которого поступает из блока 9, на выходе анализатора 6 появляется единичный сигнал, поступающий на первый вход второго элемента И 14, где он стробиру- ется единичным сигналом с выхода Меньше ИЛИ равно нулю счетчика 7. Таким образом, если после опроса всей последовательности блока коли- чество несовпадений не превысило заранее заданного, то принимается решение об обнаружении первого блока

обнаруживаемой комбинации и сигнал с

выхода второго элемента И 14 через одновибратор 17 воздействует на счетный вход счетчика 8, изменяя состояние его выходов и, следовательно, состояние блока 9, подготавливая таким образом устройство для обнаружения следующего блока.

Одновременно сигнал с выхода второго элемента И 14 поступает на счетный вход счетчика 12. Если же первый блок не был обнаружен, то вновь пришедший синхроимпульс перезаписьгеает информацию в регистре 1 и обнулит счетчик 5. Далее будут снова проходить поразрядные сравнения входной и эталонной последовательности и так до тех пор, пока не будет обнаружен искомый блок или признак конца сообщения анализатором 16. Счетчик 12 при обнаружении каждого блока увеличивает свое состояние на единицу.

Анализатор 13 сравнивает содержимое счетчика 12 с числом блоков обнаруживаемой комбинации, поступающей из блока 9, и при равенстве этих чисел вьщает единичный сигнал обнаружения двоичной комбинации на первый элемент И 11, где он стробируется выходным сигналом одновибратора 17.

С вькода первого элемента И 11 сигнал поступает на второй установочный вход триггера 15, на установочный вход счетчика 8 и на установочный вход счетчика 12. Установка триггера 15 в единичное состояние говорит о начале сообщения, уровень логической 1 с выхода триггера 15 передается на второй вход третьего элемента И 18, разрешает передачу на выход сигналов, поступающих на {Первый вход третьего элемента И 18 с

первого выхода регистра 1. Анализатор 16 при совпадении входной информации с кодом комбинации, признаком конца сообщения, вьщает сигнал, который поступает на первый установочный вход триггера 15 и на первый установочный вход счетчика 8. Уровень логического О с выхода триггера 15, воздействуя на третий элемент И 18, блокирует вькод устройства. Если же при регистрации будет обнаружен первый блок комбинации, говорящий о начале нового сообщения, -то установка триггера 15 в ноль, блокировка регистрации, произойдет под воздействием сигнала, поступающего с выхода второго элемента И 14 на вход триггера 15.

Формула изобретения

Обнаружитель комбинаций двоичных сигналов, содержащий регистр сдвига информации, синхронизирующий вход которого объединен с установочным вхо- дом счетчика импульсов, а также первый, второй и третий элементы И, о тличаютдий ся тем, что, с целью обнаружения комбинаций произвольной длины U обнаружения одновременно двух комбинаций, а также упрощения устройства при больших длинах обнаруживаемых комбинаций, введены первый и второй мультиплексоры, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, анализатор несовпадений в обнаруживаемом блоке, формирователь импульсов, счетчик дли- МЫ обнаруживаемого блока, счетчик адреса, триггер, блок постоянной памяти, счетчик количества обнаруженных блоков, анализатор обнаруживаемой комбинации, одновибратор и анализатор окончания сообщения, выход которого подключен к объединенным входу установки нуля, счетчика адреса и первому входу установки нуля триггера, вход установки единицы которого объединен со вторым входом установки нуля счетчика адреса и с устайовочным входом счетчика количества обнаруженных блоков, и подключен к выходу первого элемента И, первый вход, которого объединен со счетным входом счетчика адреса и подключен к выходу одновибратора, вход которого объединен со вто рым входом установки нуля триггера и счетным входом счетчика количества обнаруженньпс блоков и подключен к выходу второго элемента И, первый вход которого соединен с выходом анализатора несовпадения в обнаруживаемом блоке, R первых входов которого соединены с R выходами счетчика импульсов, вход которого соединен с выходом элемента ИС- КЛЮЧАЩЕЕ ИЛИ первый и второй входы

которого -соединены с выходами соот-- ветственно первого и второго мультиплексоров, третий вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к первому выходу формирователя импульсов, второй выход которого подключен к вычитающему входу счетчика длины обнаруживаемого блока, синхронизирующий вход : которого объединен с синхронизирующими входами формирователями импульсов и регистра сдвига информации, N выходов которого подключены к соответствующим N входам первого мультиплексора, а первый разряд - к первому входу третьего элемента И, второй вход которого соединен с выходом триггера, причем первые М из N выходов регистра .сдвига информации подключены к соответствующим М первым

чвходам анализатора окончания сообщения, вторые М входов которого подключены к соответствующим М первым выходам блока постоянной памяти S вторых выходов которого подключены к соот- ветствуюпщм S первым входам анализатора обнаруживаемой комбинации, S вторых входов которого подключены к соответствующим S выходам счетчика количества обнаруженных блоков, выход анализатора обнаруживаемой комбинации подключен к второму входу первого элемента И, R третьих выходов блока постоянной памяти подключены к соответствующим R вторым входам анализатора несовпадений в обнаруживаемом блоке, N четвертых выходов блока

Составитель В. Шевцов Редактор А. Шулла Техред Л. Сердюкова

Заказ 3127/57 Тираж 638Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

постоянной памяти подключены к N первым входам второго мультиплексора, L вторых входов попарно объединены с соответствующими L вторыми входами первого мультиплексора и подключены к соответствующим L выходам счетчика длины обнаруживаемого блока, выход Меньше - или - равно нулю которого подключен к объединенным второму входу второго элемента И и входу блокировки формирователя импульсов, К информационных входов счетчика длины обнаруживаемого блока подключены к соответствующим К пятым выходам блока постоянной памяти адресные входы которого подключены к выходам счётчика адреса.

Корректор А.Тяско

| название | год | авторы | номер документа |

|---|---|---|---|

| Обнаружитель комбинаций двоичных сигналов | 1988 |

|

SU1596492A1 |

| Анализатор состояния сети обмена дискретными сообщениями | 1979 |

|

SU886261A2 |

| Устройство для приема цифровых сигналов | 1990 |

|

SU1734240A1 |

| Обнаружитель комбинаций двоичных сигналов | 1986 |

|

SU1356266A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Устройство для телеконтроля | 1990 |

|

SU1732366A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

| Устройство приема двоичных сигналов | 1984 |

|

SU1197116A1 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

| Устройство для приема информации | 1983 |

|

SU1088051A1 |

Изобретение относится к технике связи. Цель изобретения - обеспечение возможности обнаружения комбинаций произвольной длины и обнаружения одновременно двух комбинаций, а также упрощение устр-ва при больших длинах обнаруживаемых комбинаций. Обнаружитель содержит регистр 1 сдвига информации, мультиплексоры 2 и 3, эл-т ИСКПЮЧАЩЕЕ ИДИ 4, счетчик 5 импульсов, анализатор 6 несовпадений в обнаруживаемом блоке, счетчик 7 длины обнаруживаемого блока, счетчик 8 адреса, блок постоянной памяти (БПП) 9, формирователь 10 импульсов, , эл-ты И 11, 14 и 18, счетчик 12 количества обнаруженных блоков, анализатор 13 обнарз живаемой комбинации, триггер 15, анализатор 16 окончания сообщения и одновибратор 17. На выходах мультиплексоров 2 и 3 присутствуют соответственно входная и эталонная информации. В обнаружителе происходят поразрядные сравнения входной и зталонной последовательности до до тех пор, пока не обнаружен искомый блок или признак конца сообщения . анализатором 16. Цель достигается введением мультиплексоров 2 и 3, з-та ИСКЛЮЧАЮЩЕЕ ИЛИ 4, анализаторов 6, 13 и 16, счетчиков 7, 8 и 12, БПП 9, формирователя 10, триггера 15 и одновибратора 17. 1 ил. (Л с

| Обнаружитель комбинаций двоичных сигналов | 1979 |

|

SU987859A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-07-23—Публикация

1986-01-03—Подача