щим входам регистра адреса и блока ввода начального адреса, информационные входы которого и информационные входы второго, третьего и четвертого накопителей являются вторьм информационным входом устройства, а адресный вход подключен к выходу второго элемента НЕ, первый вход мультиплексора является адресным входом устройства, второй вхсд подключен к выходу сумматора, а выход к входам установки адреса второго, третьего и четвертого накопителей, управляюаще входы которых, управляющий вход мультиплексора и вход второго элемента НЕ являются управляющим входом устройства, выходы нако40172

пителей подключены к входам соответствующих мажоритарнБк элементов, выходы первого и второго мажоритарных элементов соединены соответственно с первым и вторым входами блока сравнения, выход третьего мажоритарного элемента подключен к второму входу первого элемента И, третий вход которого соединен с вторым выходом распределителя сигналов и с первым входом третьего элемента И, второй вход которого подключен к вы- f ходу четвертого мажоритарного элемента, а выход - к входу счетчика порогового числа совпадений, выходы которого соединены с другим входом порогового элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1981 |

|

SU1014036A1 |

| Логическое запоминающее устройтво | 1979 |

|

SU858104A1 |

| Устройство для приема информации | 1983 |

|

SU1088051A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1429148A2 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1984 |

|

SU1156110A1 |

| Обнаружитель комбинаций двоичных сигналов | 1986 |

|

SU1356266A1 |

| Устройство для приема трехкратно повторяемых команд управления | 1986 |

|

SU1385309A1 |

| Обнаружитель комбинации двоичных сигналов | 1983 |

|

SU1270898A1 |

| Устройство классификации N-разрядных двоичных комбинаций | 1982 |

|

SU1089576A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

ЛОГИЧЕСКОЕ ЗАПОМИНАЩЕЕ УСТРОЙСТВО, содержащее генератор импульсов, элемент ИЛИ, триггер, регистр адреса, счетчик адреса, первый, второй и третий накопители, блок сравнения, первый элемент И, счетчик числа совпадений и пороговый элемент, причем первый вход триггера соединен с первым входом элемента ИЛИ, выходкоторого подключен к входу счетчика адреса, выходы которого соединены с входами установки адреса первого накопителя, информационный вход которого является первым информационным входом устройства, входы установки адреса второго накопителя соединены с входами установки третьего накопителя, выход блока сравнения подключен к первому входу первого элемента И, выход которого соединен с входом счетчика числа совпадений, выходы которого подключены к одному иэ входов порогового элемента, выход которого является выходом устройства, отличающееся тем, что, с целью пов1двения надежности устройства, в него введены распределитель сигналов, формирователи сигналов, формирователь пачки импульсов, второй и третий элемент И, элементы НЕ, блок ввода начального адреса, сумматор, мультиплексор, четвертый накопитель, мажоритарные элементы, счетчик порогового числа совпадений, причем выход генератора импульсов подключен к первому входу первого формирователя сигналов и к входу распределителя сигналов, первый выход которого сокдинен с первыми входами второго и третьего формирователей сигналов и формирователя пачки импульсов и входом первого элемента НЕ, второй вход второго формирователя сигналов является синхронизирующим входом устройства, первыйвыход подключен (Л к первому входу триггера, а второй выход - к второму входу третьего формирователя сигналов, выход которого подключен к вторым входам первого триггера и формирователя пачки импульсов, первьй выход которого соединен с третьими входами второго и третьего формирователей сигналов, а второй выход - с вторым входом элемента ИЛИ, выход триггера подключен к первому входу второго элемента И, второй вход которого подключен к выходу первого элемента НЕ, а выход к управляющему входу первого накопителя, третий в.ыход формирователя пачки импульсов соединен с первым- входом сумматора, второй вход которого подключен к выходу регистра адреса, информационный вход которого подключен к информационному выходу блока ввода начального адреса, управляющий выход которого соединен с вторым входом первого формирователя сигналов, выход которо го подключен к управляю

1

Изобретение относится к вычислительной технике, в частности, к запоминающим устройствам, и может, быть использовано для анализа комбинаций двоичного кода.

Известно логическое запомингиощее устройство, содержащее регистр сдвига входного сигнала, прямой выход каждого разряда которого соединен с первым входом одного из элементов И, выходы которых соединены с соответствующими шинами считывания запоминающего устройства на магнитных сердечниках, в которое постоянно зашиты эталоны, а вторые входы объединены между собой, на них поданы импульсы считывания, причем выходы запоминающего устройства подключены к пороговьм устройствам tl.

Недостатком этого устройства является то, что в нем не предусмотрена возможность смены эталонов в процессе работы, что ограничивает его функциональные возможности.

Наиболее близким к предлагаемому является логическое запоминающее устройство, -состоящее: из генератора импульсов, триггера, элемента ШШ регистра адреса, счетчика адреса, трех накопителей, схемы сравнения, элемента И, счетчика совпадений и порогового элемента, причем первые входы триггера и элемента ИЛИ соединены между собой выход элемента ИЛИ

подключен к входу счетчика адреса, выходы которого соединены с входами установки адреса первого накопителя, информационный вход которого является входом устройства, входы установк адреса второго и третьего накопителе соединены между собой, выход схемы сравнения подключен к первому входу элемента И, выходы счетчика совпадений подключены к первым входам порогового элемента, выход которого является выходом устройства. Принцип действия этого логического запоминающего устройства заключается в том, что информация в последовательном коде заносится в него, затем его содержимое сравнивается с содержимым запомина{рщего устройства, в котором хранится эталонная последовательность, на результат сравнения накл адывается маска, определяющая совокупность признаков, по которым входящая последовательность импульсов сравнивается с эталонной, число совпадений импульсов входящей последовательности и эталонной подсчитывается счетчиком и поступает на вход порогового элемента, где сравнивается с порогоBbw числом совпадений, результат сравнения поступает на выход устройства 2.

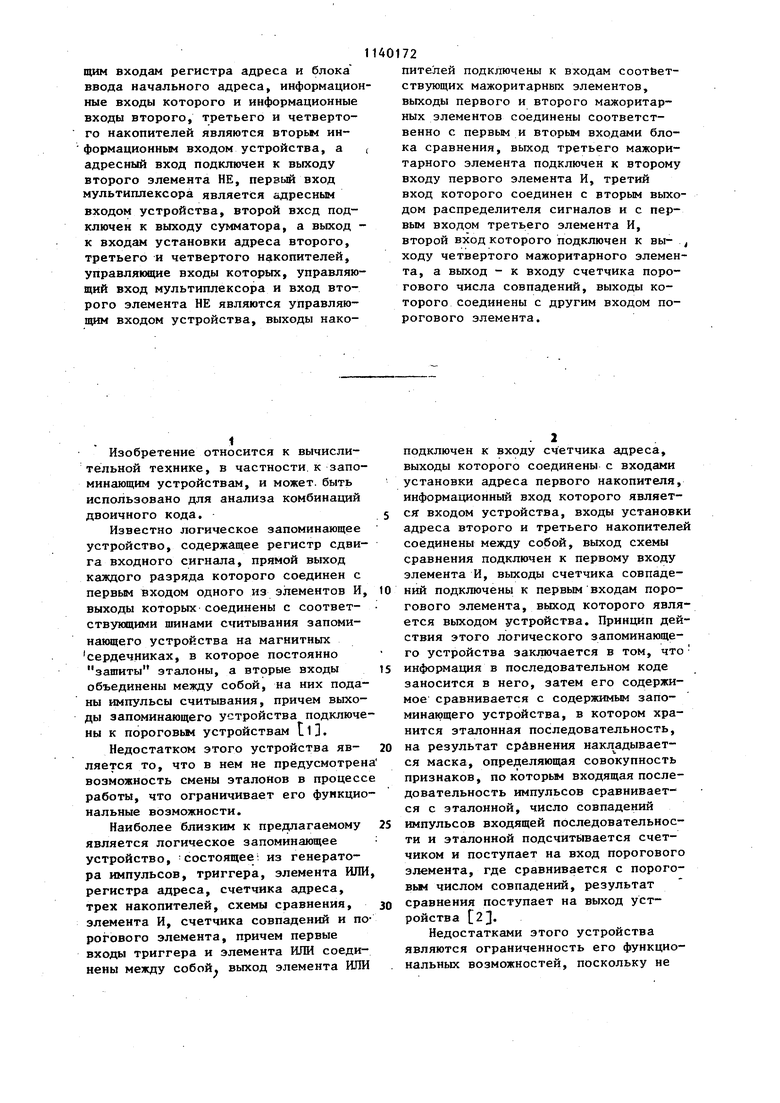

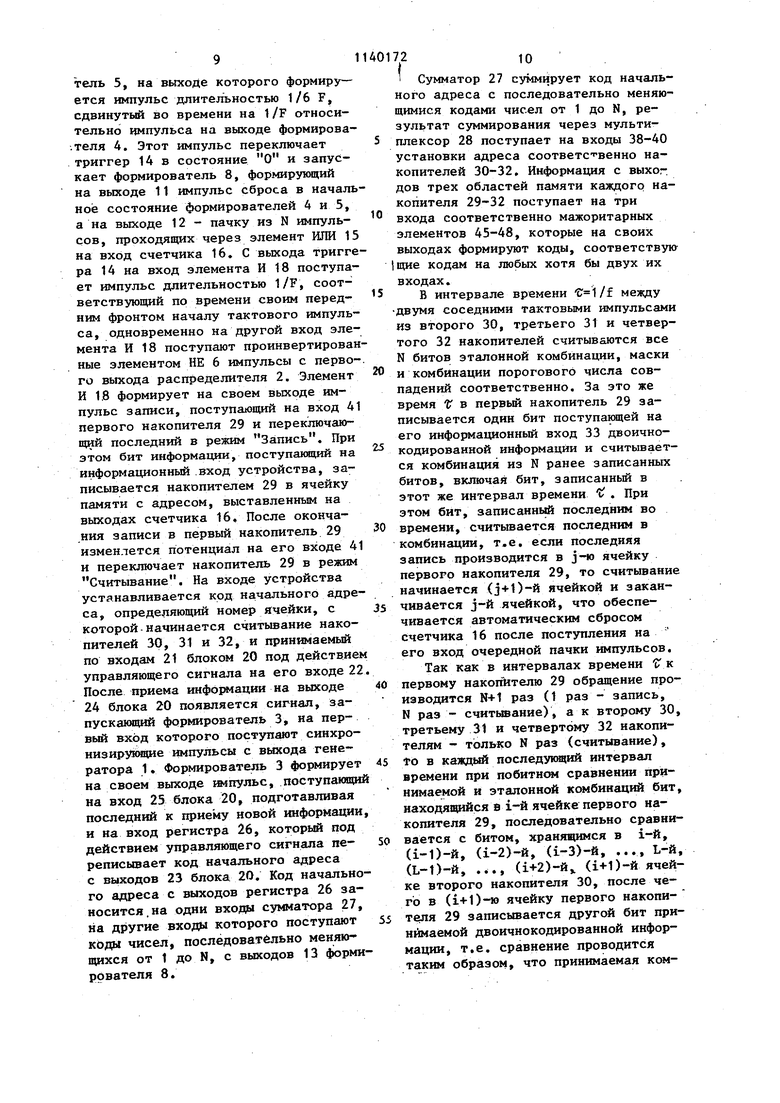

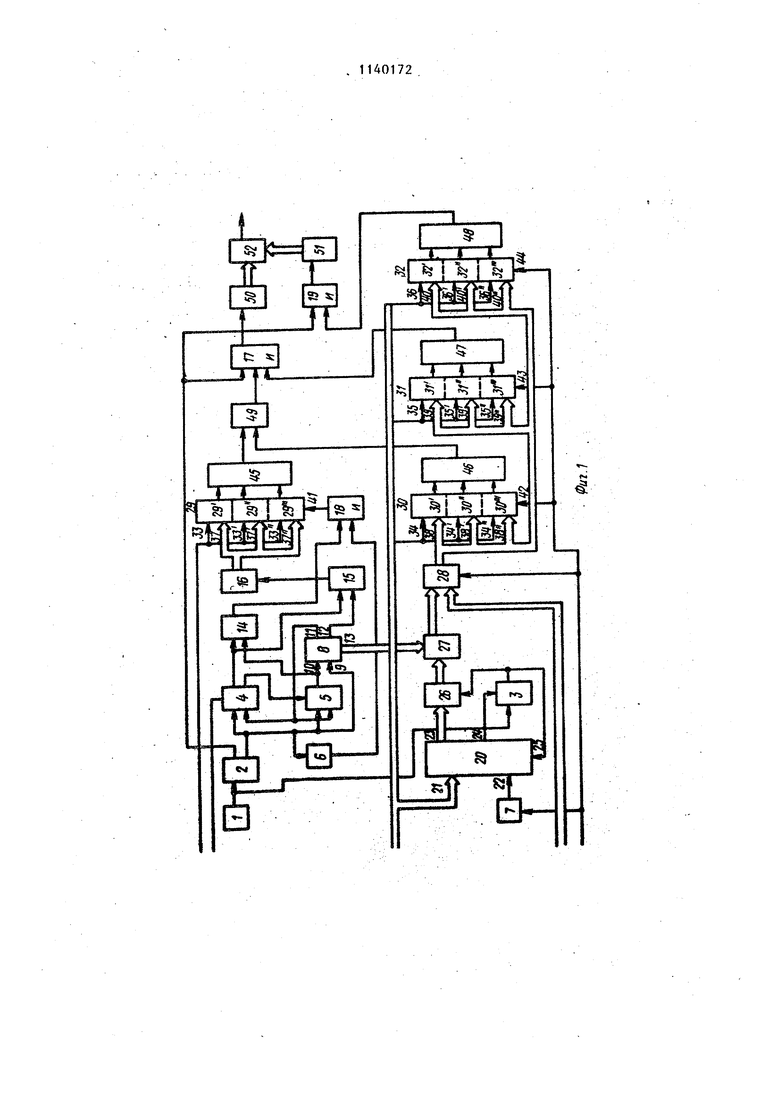

Недостатками этого устройства являются ограниченность его функциональных возможностей, поскольку не предусмотрены стыковка устройства с микро-ЭВМ для более оперативной смены эталонной комбинации в процессе работы, а также возможность оперативного изменения порогового числа совпадений, и низкая надежность устройства вследствие отсутствия дублирования входящей двоичной комбинации, эталонной комбинации и маски, Цель изобретения - повьпиение надежности устройства. Поставленная цель достигается (тем, что в логическое запоминающее устройство, содержащее генератор импульсов, элемент ИЛИ, триггер, регистр адреса, счетчик адреса, первый, второй и третий накопители, блок сравнения, первый элемент И, счетчик числа совпадений и пороговый элемент, причем первый вход триг гера соединен с первым входом элемента ИЛИ, выход которого подключен к входу счетчика адреса, выходы которого соединены с входами установки адреса первого накопителя, информационный вход которого является пер вым информационным входом устройства, входы установки адреса второго накопителя соединены с входами установки третьего накопителя, выход бло ка сравнения подключен к первому вхо ду первого элемента И, выход которого соединен с входом счетчика числа совпадений, выходы которого подключе ны к одному из, входов порогового эл мента, выход которого является выходом устройства, введены распределитель сигналов, -формирователи сигналов, формирователь пачки импульсов, второй и третий элемент И, элементы НЕ, блок ввода начального адр са, сумматор, мультиплексор, четвертый накопите ль, мажоритарные элемен ты, счетчик порогового числа совпадений, причем выход генератора импульсов подключен к первому входу первого формирователя сигналов и к входу распределителя сигналов, первый выход которого соединен с, перв ми входами второго и третьего форми рователей сигналов и формирователя пачки импульсов и входом первого эл мента НЕ, второй вход второго форми рователя сигналов является синхрони зирующим входом устройства, первый выход подключен к первому входу три гера, а второй выход - к второму вх 724 ду третьего формирователя сигналов, выход которого подключен к вторым входам первого триггера и формирователя пачки импульсов, первый выход которого соединен с третьими входами второго и третьего формирователей сигналов, а второй вькод - с вторым входом элемента ИЖ, выход триггера подключен к -первому входу второго элемента И, второй вход которого подключен к выходу первого элемента НЕ, а выход - к управляющему входу первого накопителя, третий выход формирователя пачки импульсов соединен с первым входом сумматора, второй вход которого подключен к выходу регистра адреса, информацион ный вход которого подключен к информационному выходу блока ввода начального адреса, управляющий выход которого соединен с вторым входом первот го формирователя сигналов, выход которого подключен к управляющим входам регистра адреса и блока ввода начального адреса, информационные входы которого и информационные входы второго, третьего и четвертого накопителей являются вторым информационным входом устройства, а адресный вход подключен к выходу второго элемента НЕ, первый вход мультиплексора является адресным входом устройства, второй вход подключен к выходу сумматора, а выход - к входам установки адреса второго, третьего и четвертого накопителей, управляющие входы которых, управляющий вход мультиплексора и вход второго элемента НЕ являются управляющим входом устройства, выходы накопителей подключенык входам соответствуюш сх мажоритарных элементов, выходы первого и второго мажоритарных элементов соединены соответственно с первым и вторым входами -блока сравнения, выход третьего мажоритарного элемента подключен к второму входу первого элемента И, третий вход которого соединен с вторым выходом распределителя сигналов и с первым входом третьего элемента И, второй вход которого подключен к выходу четвертого мажоритарного элемента, а выход - к входу счетчика порогового числа совпадений, выходы которого соединены с другим входом порогового элемента. На фиг. 1 представлена структурная схема предлагаемого устройства;

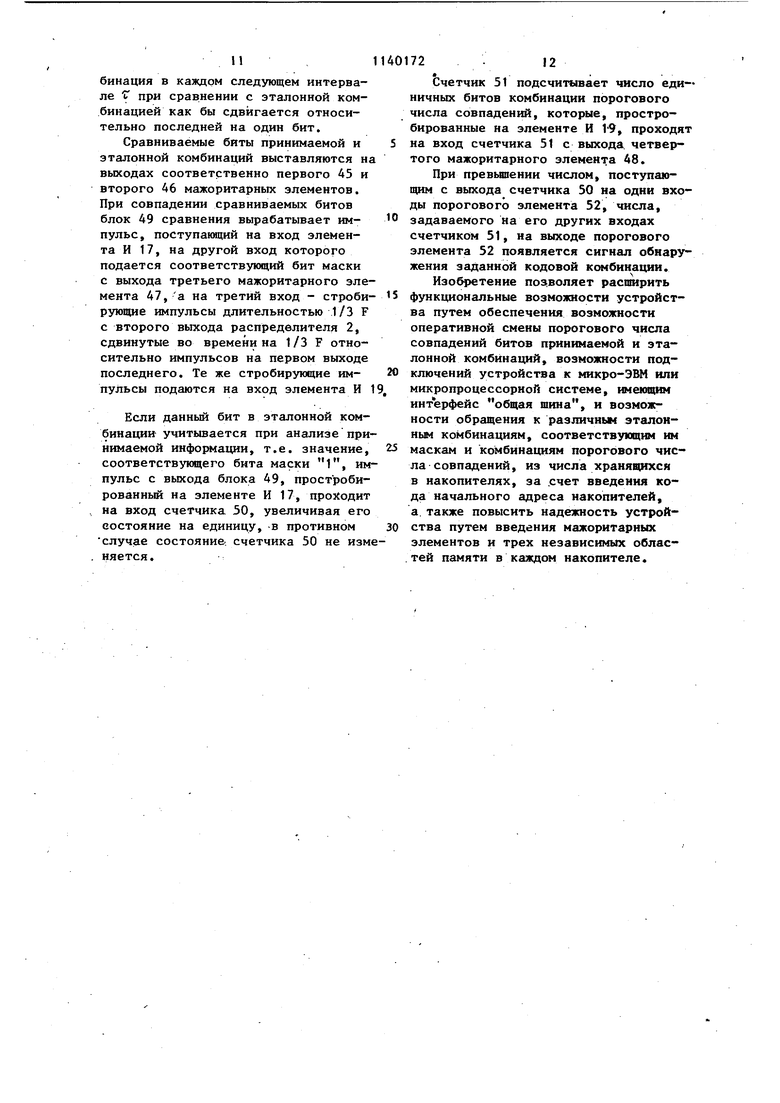

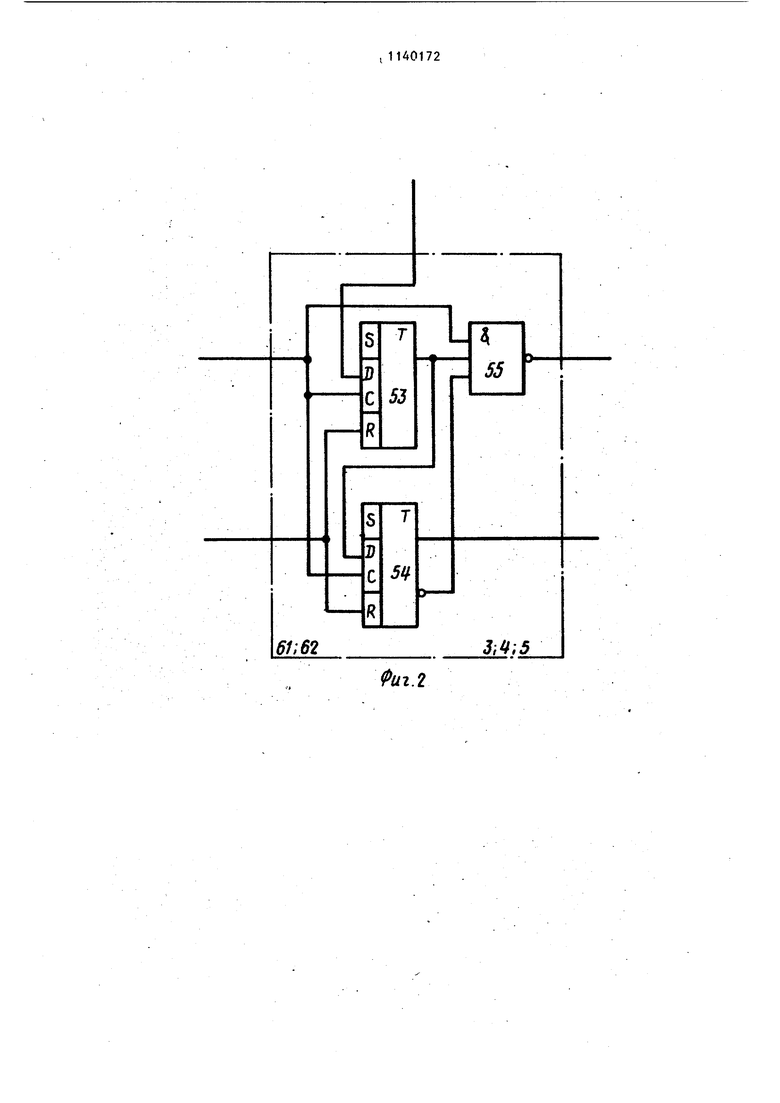

на фиг. 2 - функциональная схема формирователя сигналов; на фиг. 3 структурная схема формирователя пачки импульсов.

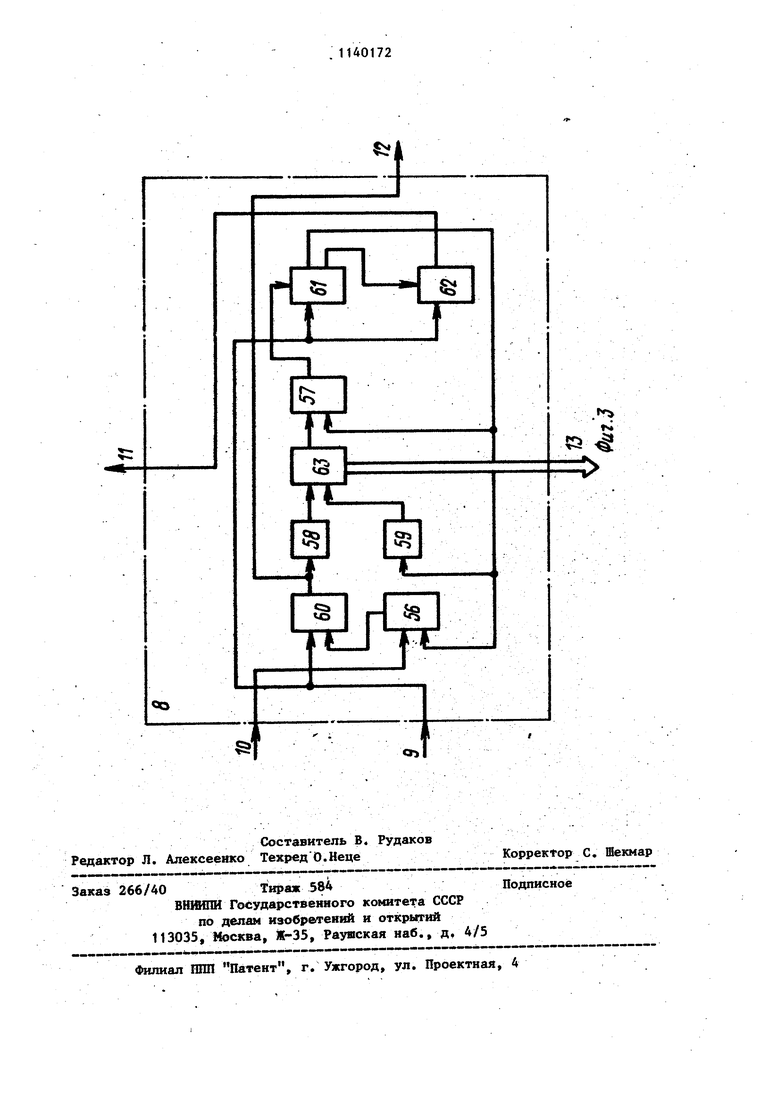

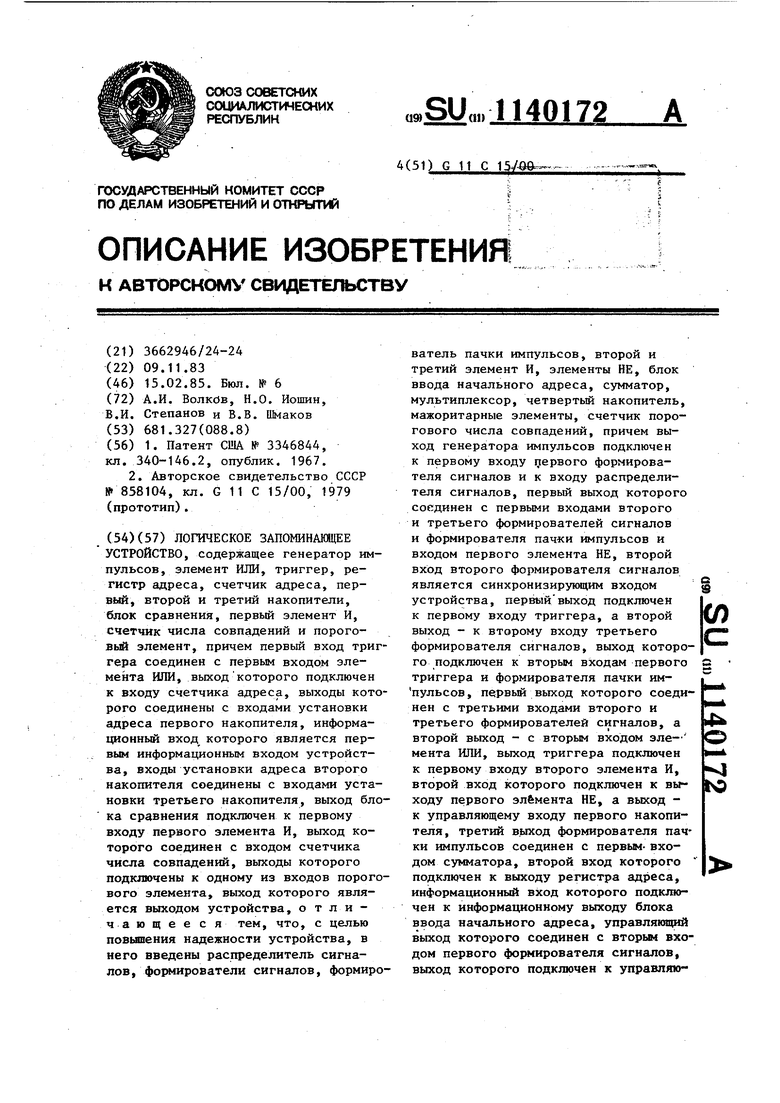

Логическое запоминающее устройство содержит (фиг. 1) генератор 1 импульсов, распределитель 2 сигналов, первый 3, второй 4 и третий 5 формирователи сигналов, первый 6 и второй 7 элементы НЕ, формирователь 8 пачки импульсов, имеющий входы 9 и 10 и выходы 11-13, первьй триггер 14, элемент ИЛИ 15, счетчик 16 адреса, первый 17, второй 18 и третий 19 элементы И, блок 20 ввода начального адреса, имеющий входы 21 и 22 и выходы 23 и 24, вход 25 регистра 26 адреса, сумматор 27, мультиплексор 28, первый 29, второй 30, третий 31 и четвертый 32 накопители, имеющие соответственно информационные входы 33-36, входы 37-40 установки адреса и управляющие входы 41-44, первьй 45 второй 46, третий 47 и четвертьй 48 мажоритарные элементы, блок 49 сравнения, счетчик 50 числа совпадений, счетчик 51 порогового числа совпадет НИИ и пороговый элемент 52.

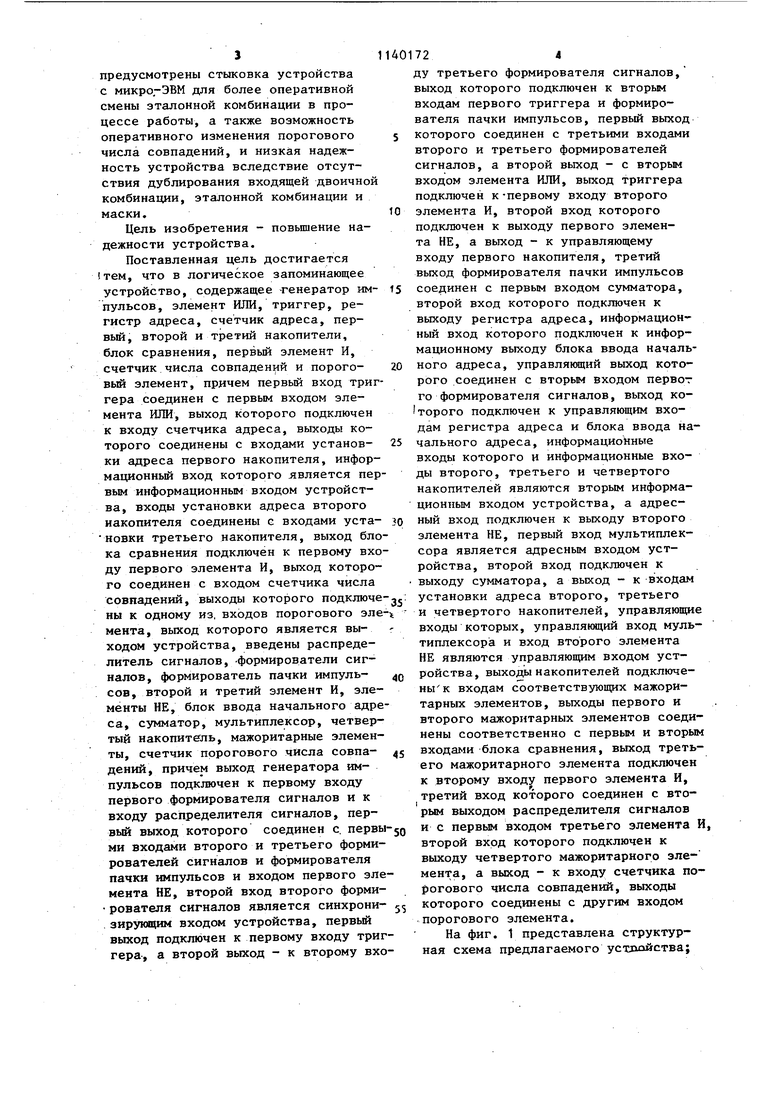

Формирователь 4 сигналов (фиг.2) содержит второй 53 и третий 54 триггеры и элемент И-НЕ 55 и работает следующим образом.

На первьй вход элемента И-НЕ 55, соединенный с синхронизирующими входами триггеров 53 и 54 и являющийся первым входом формирователя, подаются синхронизирующие импульсы. На вход данных триггера 53, являющийся входом формирователя, поступает запускающий импульс длительностью t при этом 1:1, ) fj, где IX; длительность синхроимпульсов. При этом на выходе триггера 53, соединенном с вторьм входом элемента И-НЕ 55 и с входом данных триггера 54, в момент прихода первого синхроимпульса в период времени 1,, появляется единичньй потенциал. На инверсном выходе триггера 54, подключенном к третьему входу элемента И-НЕ 55 появляется нулевой потенциал в момент прихода второго в период времени f. синхроимпульса. Таким образом, .на выходе элемента И-НЕ 55, являющемся первьм выходом формирователя, формируется нулевой импульс дпите;льностью tj , соответствующий по времени первому в период времени t синхроимпульсу.

На прямом выходе триггера 54, являющемся вторым выходом формирователя, устанавливается единичньй потенциал в момент прихода второго в период времени .Т синхроимпульса. Сброс триггеров 53 и 54 в состояние О осуществляется с приходом на третий . вход формирователя, соединенньй с входами установки в О триггеров 53 и 54, импульса сброса.

Состав и работа формирователей 3 и 5 сигналов аналогичны составу и работе формирователя 4.

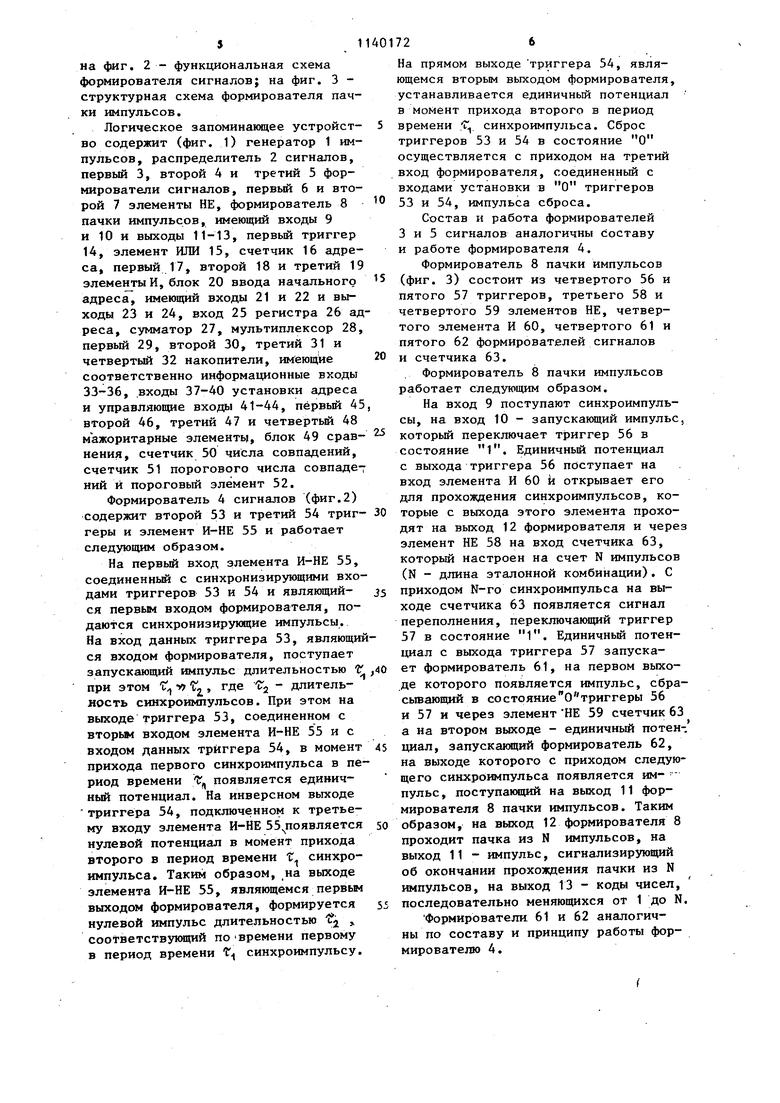

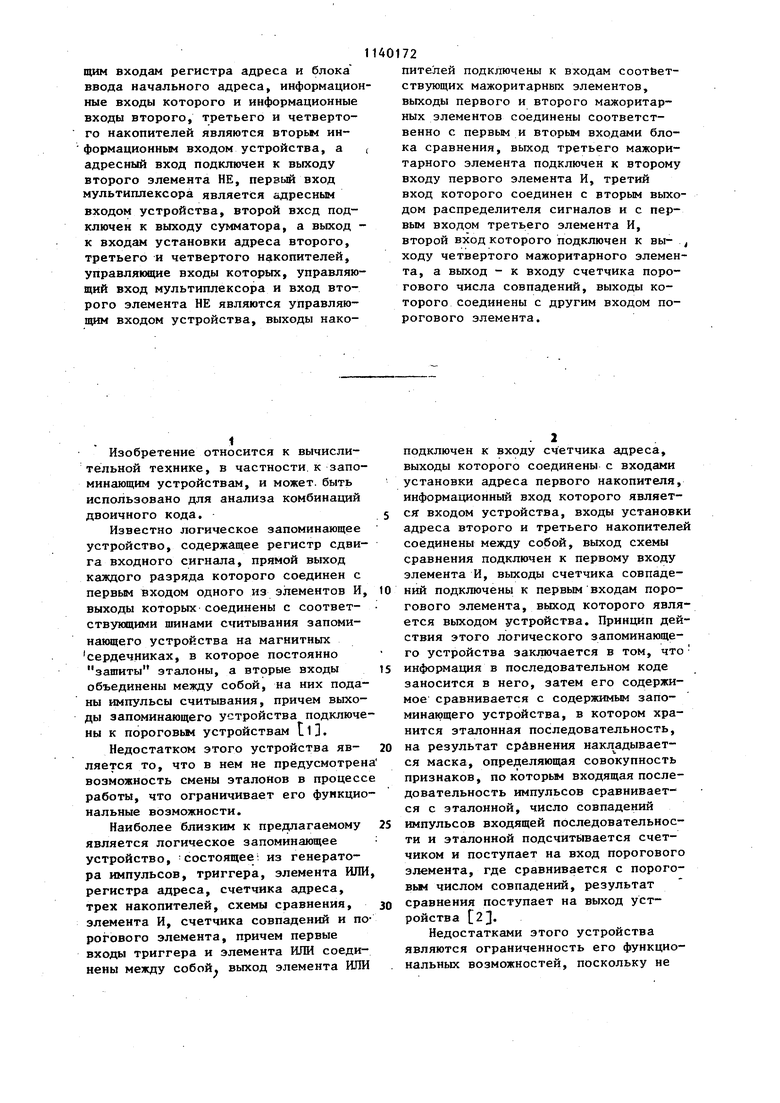

Формирователь 8 пачки импульсов (фиг. 3) состоит из четвертого 56 и пятого 57 триггеров, третьего 58 и четвертого 59 элементов НЕ, четвертого элемента И 60, четвертого 61 и пятого 62 формирователей сигналов и счетчика 63.

. Формирователь 8 пачки импульсов работает следующим образом.

На вход 9 поступают синхроимпульсы, на вход 10 - запускающий импульс которьй переключает триггер 56 в состояние 1. Единичньй потенциал с выхода триггера 56 поступает на вход элемента И 60 и открывает его для прохождения синхроимпульсов, которые с выхода этого элемента проходят на выход 12 формирователя и чере элемент НЕ 58 на вход счетчика 63, который настроен на счет N импульсов (N - длина эталонной комбинации). С приходом N-ro синхроимпульса на выходе счетчика 63 появляется сигнал переполнения, переключающий триггер 57 в состояние 1. Единичньй потенциал с выхода триггера 57 запускает формирователь 61, на первом выходе которого появляется импульс, сбрасьгоающий в состояние0 триггеры 56 и 57 и через элементНЕ 59 счетчик 63 а на втором выходе - единичный потенциал, запускакяций формирователь 62, на выходе которого с приходом следующего синхроимпульса появляется им- пульс, поступающий на выход 11 формирователя 8 пачки импульсов. Таким образом, на выход 12 формирователя 8 проходит пачка из N импульсов, на выход 11 - импульс, сигнализирующий об окончании прохождения пачки из N импульсов, на выход 13 - коды чисел, последовательно меняющихся от 1 до N

Формирователи 61 и 62 аналогичны по составу и принципу работы формирователю 4.

71

Блок 20 ввода начального адреса может быть реализован на БИС К580ИК55 Его вход 22 предназначен для выбора кристалла БИС, выход 24 и вход 25 для обмена сигналами с формирователем 3.

Накопители 29, 30, 31 и 32 выполнены на полупроводниковых запоминающих схемах, причем каждый накопитель имеет три независимые области памяти (например, 29, 29 и 29 для накопителя 29), соответствующие входы которых соединены между собой. Управляющие входы 41-44 соответственно накопителей 29-32 предназначены для управления режимами записи-считывания.

Работа устройства заключается в следующем.

Устройство позволяет анализировать комбинации двоичного кода произвольной длины, не превьшакмцей объема первого накопителя 29, и работает в режимах Запись эталона и Анализ.

Режим Запись эталона.

На управляющем входе устройства устанавливается потенциал, переключающий накопители 30-32 в режим Запись и открывающий одни из входов мультиплексора 28. На адресных входах устройства устанавливается в двоичном коде число, не превышающее М, такое, что L-M N , где L - некоторое, например максимально возможное, .число, которое может находиться в счетчике 16 адреса. Во второй накопитель 30 заносится первый бит эталонной комбинации, S третий накопитель 31 - первый бит маски, которая представляет собой комбинацию двоичного, кода, содержащую, как и эталонная комбинация, N битов и характеризующуюся тем, что в ней определенный бит принимает значение 1, если соответствующий ему бит эталонной комбинации учитывается при анализе принимаемой комбинации, или О в противном случае, одновременно в четвертый накопитель 32 заносится ,первый бит такой двоичный комбина|ции, что сумма битов, принимакицих значение 1, соответствует пороговому числу совпадений битов принимаемой и эталонной комбинаций, учитывающемуся при анализе принимаемой комбинации. В каждом накопителе запись производится в три независимых

8

области памяти, соответственно обозначенных для второго накопителя ЗО, 30 и 30 , для третьего накопителя 31 , 31, и для четвертого накопителя 32, 32 и 32 . Затем число, установленное на адресных входах устройства, последовательно увеличивается на единицу синхронно с изменениек{ на информационных входах битов эталонной комбинации, маски и комбинации порогового числа совпадений до тех пор, пока во второй 30, третий 31 и четвертый 32 накопители не будет занесено по N битов соответствующих двоичных комбинаций, причем в каждом накопителе эти комбинации занимают последовательно N ячеек. Затем на управляющем входе устройства устанавливается потенциал, соответствующий режиму считывания. Этот потенциал переключает второй 30, третий 31 и четвертый 32 накопители в режим Считывание, открывает другие входы мультиплексора 28 и, проинвертированный элементом НЕ 7, поступает на вход 22 блока 20 ввода, подготавливая его к приему данных. После этого устройство может работать в режиме Анализ

Режим Анализ.

Тактовые импульсы, сопровождающие двоичнокодированную информацию и соответствукидие во времени началу каждого бита, поступают на синхронизирующий вход устройства. На вход распределителя 2 поступают импульсы с генератора 1, следующие с частотой F, значение которой удовлетворяет условию , где частота следования тактовых импульсов. Синхронизирующие импульсы длительностью 1/6 F с частотой F с первого выхода распределителя 2 поступают на входы формирователей 4 и 5 и формирователя 8 пачки импульсов. Тактовый импульс, поступающий на синхронизирующий вход устройства, запускает формирователь 4, который формирует на своем первом выходе. единичный импульс длительностью 1/6 соответствующий по времени началу тактового импульса длительностью 1/f. Импульс с первого выхода формирователя 4 переключает триггер 14 в состояние 1 и через элемент ИЛИ 1 проходит на вход счетчика 16 адреса. Потенциал с второго выхода формирователя 4 запускает формирова9

тель 5, на выходе которого формиру- ется импульс длительностью 1/6 F, сдвинутый во времени на 1/F относительно импульса на выходе формирова.теля 4. Этот импульс переключает триггер 14 в состояние О и запускает формирователь 8, формирующий на выходе 11 импульс сброса в начальное состояние формирователей 4 и 5, а на выходе 12 - пачку из N импульсов, проходящих через элемент ИЛИ 15 на вход счетчика 16. С выхода триггера 14 на вход элемента И 18 поступает импульс длительностью 1/F, соответствующий по времени своим передним фронтом началу тактового импульса, одновременно на другой вход элемента И 18 поступают проинвертированные элементом НЕ 6 импульсы с первого выхода распределителя 2. Элемент И 1.8 формирует на своем выходе импульс записи, поступающий на вход 41 первого накопителя 29 и переключающий последний в режим Запись, При этом бит информации, поступанщий на информационный вход устройства, записывается накопителем 29 в ячейку памяти с адресом, выставленным на выходах счетчика 16, После оконча.ния записи в первый накопитель 29 изменлется потенциал на его входе 41 и переключает накопитель 29 в режим Считывание. На входе устройства устанавливается код начального адреса, определяющий номер ячейки, с которой-начинается считывание накопителей 30, 31 и 32, и принимаемый по входам 21 блоком 20 под действием управляющего сигнала на его входе 22 После приема инфо1 1ации на выходе 24 блока 20 появляется сигнал, запускающий формирователь 3, на первый вход которого поступают синхронизирутоЕще импульсы с выхода генератора 1, Формирователь 3 формирует на своем выходе импульс, поступающий на вход 25 блока 20, подготавливая последний к приему новой информации, и на вход регистра 26, который под действием управляющего сигнала переписьшает код начального адреса с выходов 23 блока 20, Код начального адреса с выходов регистра 26 заносится, на одни входы сумматора 27, на другие входы которого поступают кЬды чисел, последовательно меняющихся от 1 до N, с выходов 13 формирователя 8.

140172

10

Сумматор 27 суммирует код начального адреса с последовательно меняющимися кодами чисел от 1 до N, результат суммирования через мультиплексор 28 поступает на входы 38-40 установки адреса соответс- венно накопителей 30-32. Информация с выхог дов трех областей памяти каждого накопителя 29-32 поступает на три входа соответственно мажоритарных элементов 45-48, которые на своих выходах формируют коды, соответствую Iщие кодам на любых хотя бы двух их входах.

5 в интервале времени между двумя соседними тактовыми импульсами из второго 30, третьего 31 и четвертого 32 накопителей считываются все N битов эталонной комбинации, маски

0 и комбинации порогового числа совпадений соответственно. За это же время f в первьй накопитель 29 записывается один бит поступакяцей на его информационный вход 33 двоичнокодированной информации и считывается комбинация из N ранее записанных битов, включая бит, записанный в этот же интервал времени t . При этом бит, записанный последним во

0 времени, считывается последним в комбинации, т.е. если последняя запись производится в ячейку первого накопителя 29, то считывание начинается (д+1)-й ячейкой и закан5 чивйется j-й ячейкой, что обеспечивается автоматическим сбросом счетчика 16 после поступления на его вход очередной пачки импульсов. Так как в интервалах времени

первому накопителю 29 обращение производится N+1 раз (1 раз - запись, N раз - считывание), а к второму 30, третьему 31 и четвертому 32 накопителям - только N раз (считывание),

5 to в каждый последукщий интервал

времени при побитном сравнении принимаемой и эталонной комбинаций бит, находящийся в i-й ячейке первого накопителя 29, последовательно сравнивается с битом, хранящимся в i-й, (1-1)-й, (1-2)-й, (1-3)-й, ,.., L-й, а-1)-й, ..., (1+2)-й„ (i+1)-и ячейке второго накопителя 30, после чего в (1+1)-ю ячейку первого накопителя 29 записывается другой бит принимаемой двоичнокодированной информации, т.е. сравнение проводится таким образом, что принимаемая комбинация в каждом следующем интервале Г при сравнении с эталонной комбинацией как бы сдвигается относительно последней на один бит.

Сравниваемые бяты принимаемой и эталонной комбинаций выставляются на выходах соответственно первого 45 и второго 46 мажоритарных элементов. При совпадении сравниваемых битов блок 49 сравнения вырабатывает импульс, поступающий на вход элемента И 17, на другой вход которого подается соответствующий бит маски с выхода третьего мажоритарного элемента 47, а на третий вход - стробирующие импульсы длительностью 1/3 F с второго выхода распределителя 2, сдвинутые во времени на 1 /3 F относительно импульсов на первом выходе последнего. Те же стробирующие импульсы подаются на вход элемента И

Если данный бит в эталонной комбинации учитывается при анализе принимаемой информации, т.е. значение, соответствующего бита маски 1, импульс с выхода блока 49, простробированный на элементе И 17, проходит на вход счетчика 50, увеличивая его состояние на единицу, в противном случае состояние-, счетчика 50 не измняется.

Счетчик 51 подсчитывает число единичных битов комбинации порогового числа совпадений, которые, простробированные на элементе И 19, проходят

на вход счетчика 51 с выхода, четвертого мажоритарного элемента 48.

При превьшении числом, поступаюищм с выхода счетчика 50 на одни входы порогового элемента 52, числа,

задаваемого на его других входах счетчико м 51, на выходе порогового элемента 52 появляется сигнал обнаружения заданной кодовой комбинации. Изобретение позволяет расширить

функциональные возможности устройства путем обеспечения возможности оперативной смены порогового числа совпадений битов принимаемой и эталонной комбинаций, возможности подключеиий устройства к микро-ЭВМ или микропроцессорной системе, имекнцим инт ерфейс общая шина, и возможности обращения к различным эталонным комбинациям, соответствующим им

маскам и комбинациям порогового числа совпадений, из числа хранящихся в накопителях, за .счет введения кода начального адреса накопителей, а. также повысить надежность устройства путем введения мажоритарных элементов и трех независимых облас.тей памяти в кфкдом накопителе.

6f:62

д

55

5

J;4f;5

иг.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3346844, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Запальная свеча для двигателей | 1924 |

|

SU1967A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Логическое запоминающее устройтво | 1979 |

|

SU858104A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-02-15—Публикация

1983-11-09—Подача