Изобретение относится к радиотехнике и может использоваться в контрольно-измерительной и диагностической аппаратуре для автоматизирован- ного расчета характеристик линии передачи информации с использованием метода глаз-диаграммы.

Цель изобретения - повышение достоверности контроля.

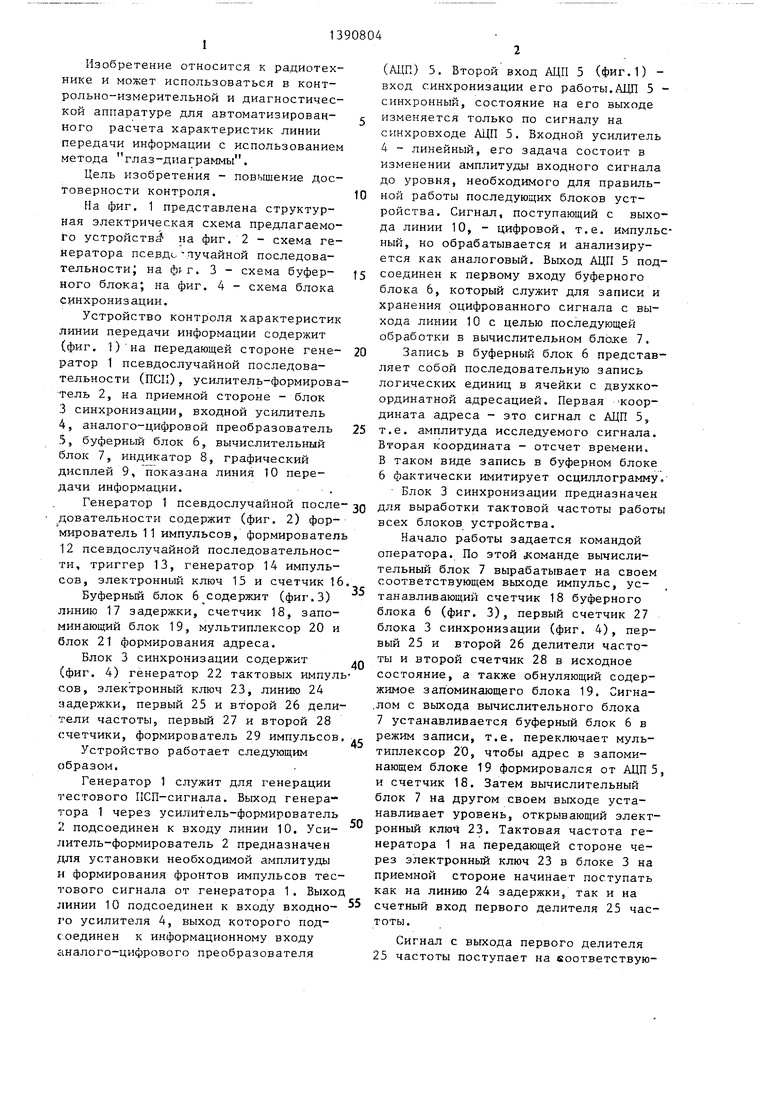

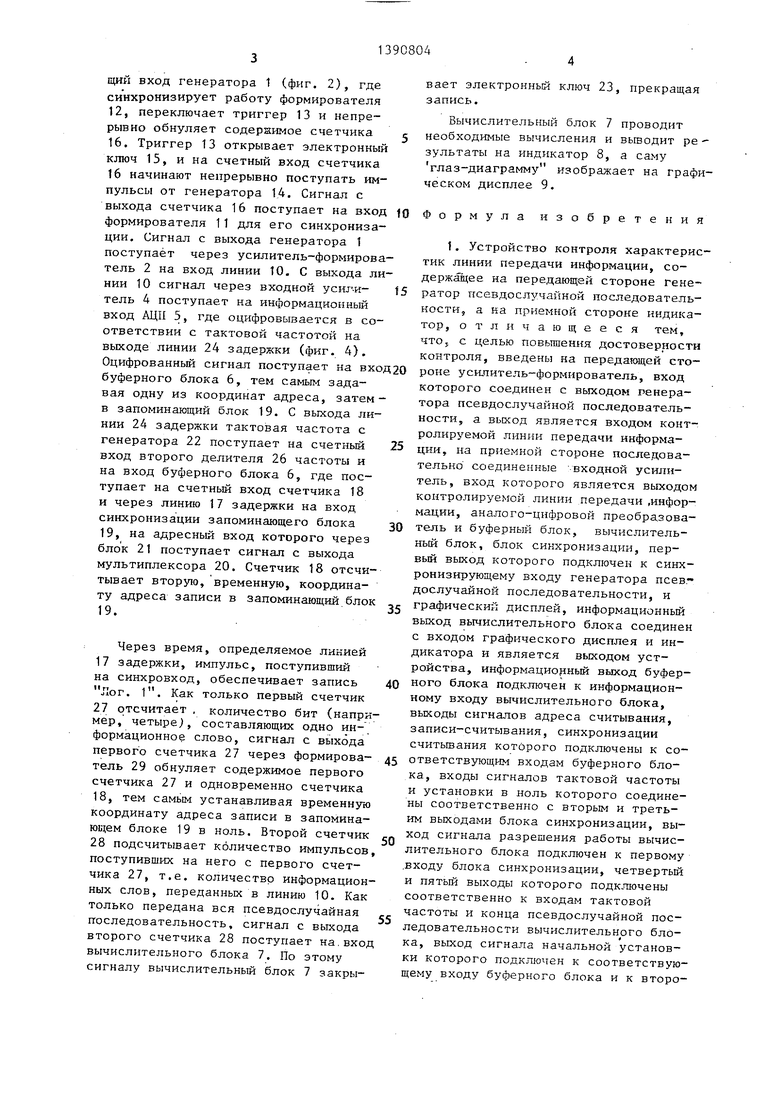

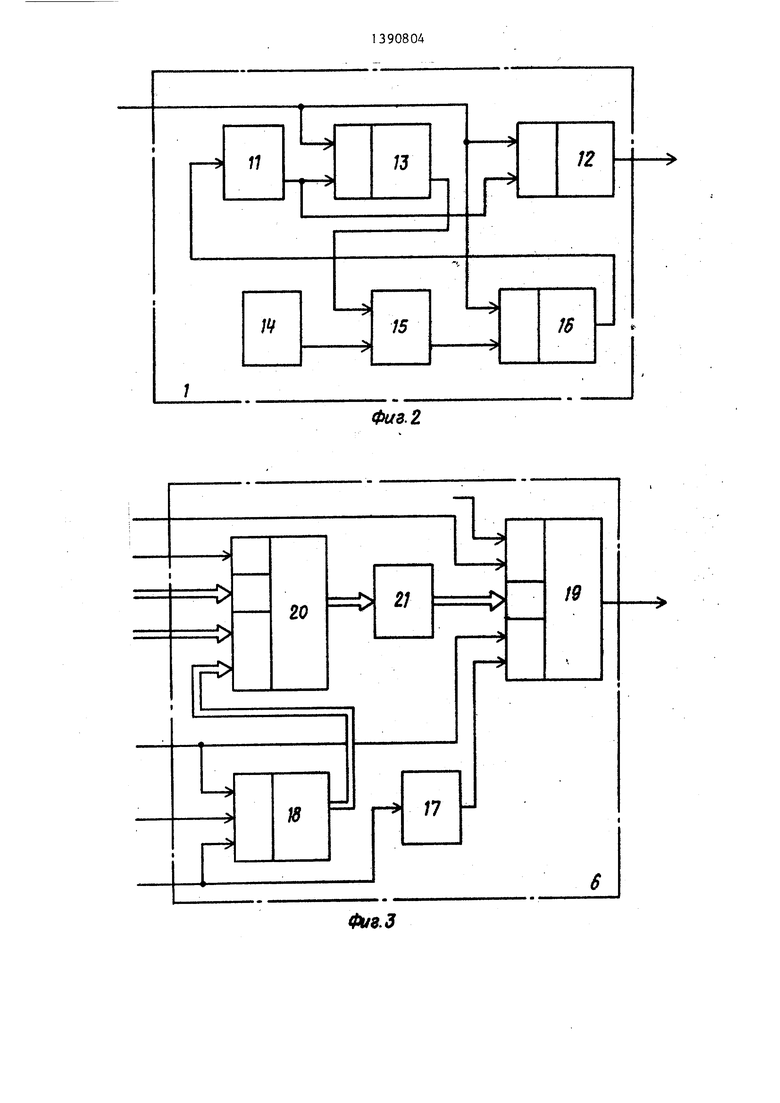

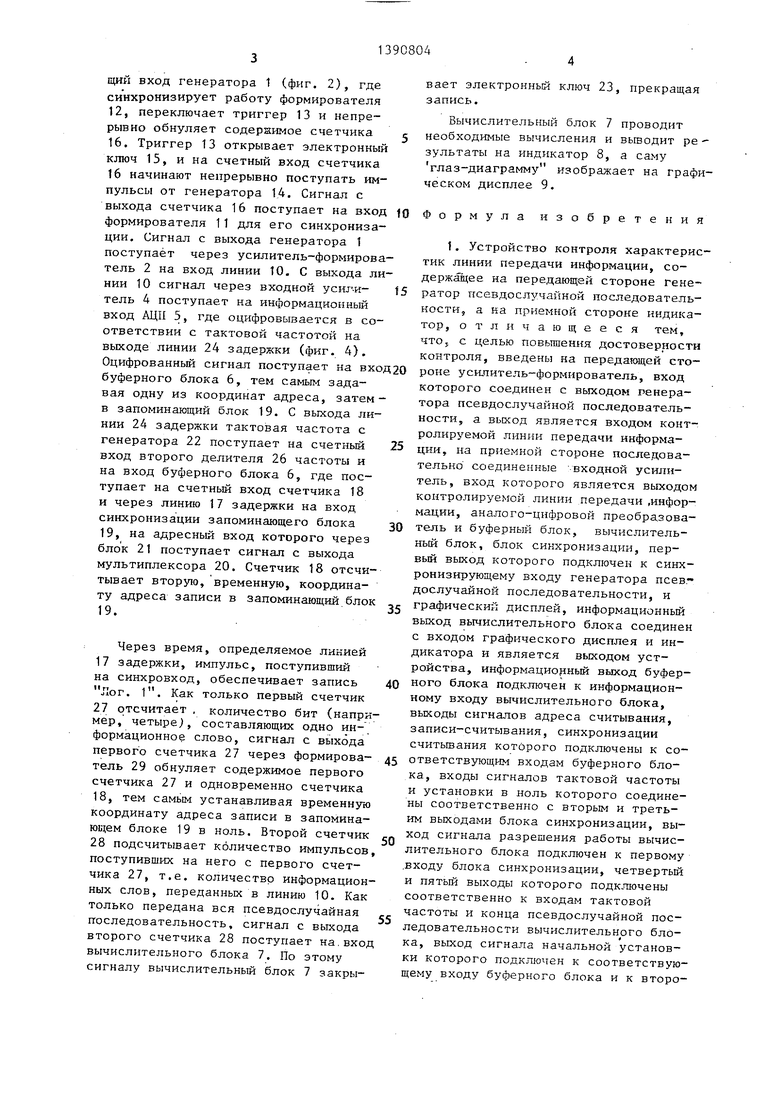

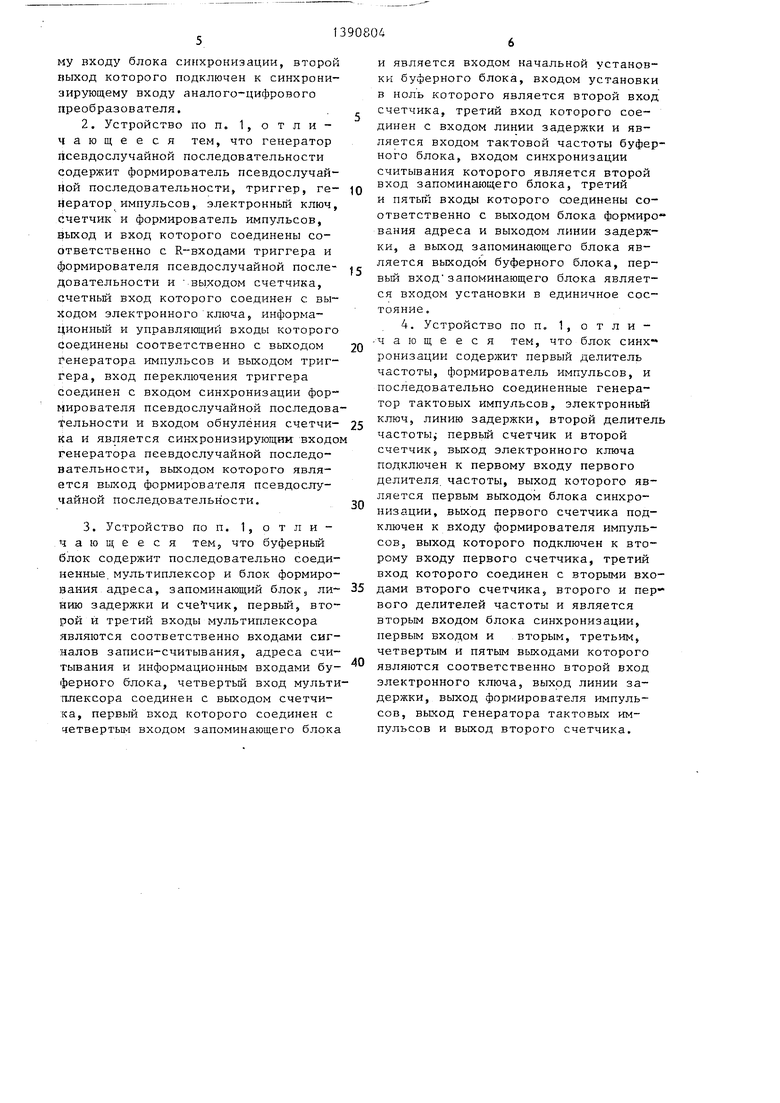

На фиг. 1 представлена структурная электрическая схема предлагаемого устройств на фиг. 2 - схема генератора псевдь Лучайной последовательности; на ф)-г. 3 - схема буфер- ного блока; на фиг. 4 - схема блока синхронизации.

Устройство контроля характеристик линии передачи информации содержит (фиг. 1) на передающей стороне гене- ратор 1 псевдослучайной последовательности (ПСИ), усилитель-формирователь 2, на приемной стороне - блок 3 синхронизации, входной усилитель

4,аналого-цифровой преобразователь

5,буферный блок 6, вычислительный блок 7, индикатор 8, графический дисплей 9, показана линия 10 передачи информации.

(АЦП) 5. Второй вход АЦП 5 (фиг.1) - вход синхронизации его работы.АДП 5 - синхронный, состояние на его выходе изменяется только по сигналу на синхровходе АЦП 5. Входной усилитель 4 - линейный, его задача состоит в изменении амплитуды входного сигнала до уровня, необходимого для правильной работы последующих блоков устройства. Сигнал, поступающий с выхо-- да линии 10, - цифровой, т.е. импульсный, но обрабатывается и анализируется как аналоговый. Выход АЦП 5 подсоединен к первому входу буферного блока 6, который служит для записи и хранения оцифрованного сигнала с выхода линии 10 с целью последующей обработки в вычислительном блоке 7.

Запись в буферный блок 6 представляет собой последовательную запись логических единиц в ячейки с двухко- ординатной адресацией. Первая -координата адреса - это сигнал с АЦП 5, т.е. амплитуда исследуемого сигнала. Вторая координата - отсчет времени. В таком виде запись в буферном блоке 6 фактически имитирует осциллограмму Блок 3 синхронизации предназначен

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения ядер нелинейных объектов | 1981 |

|

SU1008747A1 |

| Устройство поиска псевдослучайной последовательности | 1991 |

|

SU1788592A1 |

| СИСТЕМА РАДИОСВЯЗИ С ПОДВИЖНЫМИ ОБЪЕКТАМИ | 2003 |

|

RU2263401C2 |

| УПРАВЛЯЮЩИЙ АППАРАТНО-ПРОГРАММНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 2001 |

|

RU2222028C2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МЕСТА ПОВРЕЖДЕНИЯ ЛИНИЙ ЭЛЕКТРОПЕРЕДАЧИ И СВЯЗИ | 1996 |

|

RU2142142C1 |

| Программируемый генератор импульсов | 1985 |

|

SU1298869A2 |

| Система радиосвязи с подвижными объектами | 1986 |

|

SU1401626A1 |

| Радиоимпульсный фазометр | 1985 |

|

SU1257558A1 |

| Система управления многопозиционной индукционной нагревательной установкой | 1983 |

|

SU1121789A1 |

| МОДУЛЬ СИНХРОНИЗАЦИИ | 2006 |

|

RU2304788C1 |

Изобретение относится к радиотехнике и позволяет повысить достоверность контроля. Устр-во содержит на передающей стороне генератор 1 псевдослучайной последовательности (ПСГТ) , усилитель-формирователь 2, а на приемной стороне - блок 3 синхро низации, входной усилитель 4, АЦП 5, буферный блок 6. вычислительнЬШ блок 7, индикатор 8 и графический дисплей 9. Генератор 1 формирует тестовый сигнал ПСП. З силитель-формирователь 2 устанавливает необходимую амплитуду и формирует фронты ш-1пульсов тестового сигнала. Тестовый сигнал проходит через линию 10 передачи информации, усиливается, преобразуется в цифровой вид и записывается в буферный блок 6 в виде амплитуды исследуемого сигнала и соотв. отсчета времени. Обрабатываются значения принятого сигнала ПСП в вычислительном блоке 7. 3 з.п. ф-лы. 4 ил. с 9 (Л

Генератор 1 псевдослучайной после- Q для выработки тактовой частоты работы

35

40

довательности содержит (фиг. 2) формирователь 11 импульсов, формирователь 12 псевдослучайной последовательности, триггер 13, генератор 14 импульсов, электронный ключ 15 и счетчик 16.

Буферный блок 6 содержит (фиг.З) линию 17 задержки, счетчик 18, запоминающий блок 19, мультиплексор 20 и блок 21 формирования адреса.

Блок 3 синхронизации содержит (фиг. 4) генератор 22 тактовых импуль сов, электронный ключ 23, линию 24 яадержки, первый 25 и вт орой 26 делители частоты, первый 27 и второй 28 счетчики, формирователь 29 импульсов. .

Устройство работает следующим образом.

Генератор 1 служит для генерации тестового ПСЦ-сигнала. Вькод генератора 1 через усилитель-формирователь 2 подсоединен к входу линии 10. Усилитель-формирователь 2 предназначен для установки необходимой амплитуды и формирования фронтов импульсов тестового сигнала от генератора 1. Выход линии 10 подсоединен к входу входно- I o усилителя 4, выход которого под- с.оединен к информационному входу аналого-цифрового преобразователя

всех блоков устройства.

Начало работы задается командой оператора. По этой лсоманде вычислительный блок 7 вырабатывает на своем соответствующем выходе импульс, устанавливающий счетчик 18 буферного блока 6 (фиг. 3), первый счетчик 27 блока 3 синхронизации (фиг. 4), первый 25 и второй 26 делители частоты и второй счетчик 28 в исходное состояние, а также обнуляющий содержимое запоминающего блока 19. Сигна- .лом с выхода вычислительного блока 7 устанавливается буферный блок 6 в режим записи, т.е. переключает мультиплексор 20, чтобы адрес в запоминающем блоке 19 формировался от АЦП 5, и счетчик 18. Затем вычислительный блок 7 на другом своем выходе устанавливает уровень, открывающий электронный 23. Тактовая частота генератора 1 на передающей стороне через электронный ключ 23 в блоке 3 на приемной стороне начинает поступать как на линию 24 задержки/ так и на счетный вход первого делителя 25 частоты.

Сигнал с выхода первого делителя 25 частоты поступает на аоответствую5

0

всех блоков устройства.

Начало работы задается командой оператора. По этой лсоманде вычислительный блок 7 вырабатывает на своем соответствующем выходе импульс, устанавливающий счетчик 18 буферного блока 6 (фиг. 3), первый счетчик 27 блока 3 синхронизации (фиг. 4), первый 25 и второй 26 делители частоты и второй счетчик 28 в исходное состояние, а также обнуляющий содержимое запоминающего блока 19. Сигна- .лом с выхода вычислительного блока 7 устанавливается буферный блок 6 в режим записи, т.е. переключает мультиплексор 20, чтобы адрес в запоминающем блоке 19 формировался от АЦП 5, и счетчик 18. Затем вычислительный блок 7 на другом своем выходе устанавливает уровень, открывающий электронный 23. Тактовая частота генератора 1 на передающей стороне через электронный ключ 23 в блоке 3 на приемной стороне начинает поступать как на линию 24 задержки/ так и на счетный вход первого делителя 25 частоты.

Сигнал с выхода первого делителя 25 частоты поступает на аоответствующий вход генератора 1 (фиг, 2), где синхронизирует работу формирователя 12, переключает триггер 13 и непрерывно обнуляет содержимое счетчика 16, Триггер 13 открывает электронный ключ 15, и на счетный вход счетчика 16 начинают непрерывно поступать импульсы от генератора 14, Сигнал с выхода счетчика 16 поступает на вход формирователя 11 для его синхронизации. Сигнал с выхода генератора 1 поступает через усилитель-формирователь 2 на вход линии 10. С выхода линии 10 сигнал через входной усиг-и- тель 4 поступает на информационный вход АЦИ 5, где оцифровывается в соответствии с тактовой частотой на выходе линии 24 задержки (фиг, 4),

25

Оцифрованный сигнал поступает на вход20 роне усилитель-формирователь, вход буферного блока 6, тем самым задавая одну из координат адреса, затем - в запоминающий блок 19, С выхода линии 24 задержки тактовая частота с генератора 22 поступает на счетный вход второго делителя 26 частоты и на вход буферного блока 6, где поступает на счетный вход счетчика 18 и через линию 17 задержки на вход синхронизации запоминающего блока 19, на адресный вход которого через блок 21 поступает сигнал с выхода мультиплексора 20, Счетчик 18 отсчитывает вторую, временную, координату адреса записи в запоминающий блок 19,

30

35

которого соединен с выходом генератора псевдослучайной последовательности, а выход является входом конт ролируемой линии передачи информации, на приемной стороне последовательно соединенные входной усилитель, вход которого является выходо контролируедмой линии передачи (Инфор мации, аналого-цифровой преобразова тель и буферный блок, вычислитель- ньм блок, блок синхронизации, пер- вьй выход которого подключен к синх ронизирующему входу генератора псев дослучайной последовательности, и графический дисплей, информационньм выход вычислительного блока соедине с входом графического дисплея и индикатора и является выходом устройства, информационный выход буфер ного блока подключен к информационному входу вычислительного блока, выходы сигналов адреса считывания, записи-считывания, синхронизации считьшания которого подключены к со ответствующим входам буферного блока, входы сигналов тактовой частоты и установки в ноль которого соедине ны соответственно с вторым и третьим выходами блока синхронизации, выход сигнала разрешения работы вычислительного блока подключен к первому ,входу блока синхронизации, четвертый и пятый выходы которого подключены соответственно к входам тактовой частоты и конца псевдослучайной последовательности вычислительного блока, выход сигнала начальной установки которого подключен к соответствую щему входу буферного блока и к второ

Через время, определяемое линией 17 задержки, импульс, поступивший на синхровход, обеспечивает запись Лог, 1, Как только первый счетчик

27отсчитает , количество бит (например, четыреj, составляющих одно информационное слово, сигнал с выхода первого счетчика 27 через формирователь 29 обнуляет содержимое первого счетчика 27 и одновременно счетчика 18, тем самьм устанавливая временную координату адреса записи в запоминающем блоке 19 в ноль. Второй счетчик

28подсчитывает количество импульсов поступивших на него с первого счетчика 27, т,е, количество информационных слов, переданньк в линию 10, Как только передана вся псевдослучайная последовательность, сигнал с выхода второго счетчика 28 поступает на.вхо вычислительного блока 7, По этому сигналу вычислительньш блок 7 закры

вает электронный ключ 23, прекращая запись.

Вычислительный блок 7 проводит необходимые вычисления и вьшодит ре зультаты на индикатор 8, а саму глаз-диаграмму изображает на графическом дисплее 9,

Формула изобретения

1, Устройство контроля характеристик линии передачи информации, содержащее на передающей стороне генератор псевдослучайной последовательности, а на приемной стороне индикатор, отличающееся тем, 4TOj с целью повышения достоверности контроля, введены на передающей сто-

5

0 роне усилитель-формирователь, вход

0

5

0

5

0

5

которого соединен с выходом генератора псевдослучайной последовательности, а выход является входом контролируемой линии передачи информации, на приемной стороне последовательно соединенные входной усилитель, вход которого является выходом контролируедмой линии передачи (Информации, аналого-цифровой преобразователь и буферный блок, вычислитель- ньм блок, блок синхронизации, пер- вьй выход которого подключен к синхронизирующему входу генератора псевг дослучайной последовательности, и графический дисплей, информационньм выход вычислительного блока соединен с входом графического дисплея и индикатора и является выходом устройства, информационный выход буферного блока подключен к информационному входу вычислительного блока, выходы сигналов адреса считывания, записи-считывания, синхронизации считьшания которого подключены к соответствующим входам буферного блока, входы сигналов тактовой частоты и установки в ноль которого соединены соответственно с вторым и третьим выходами блока синхронизации, выход сигнала разрешения работы вычислительного блока подключен к первому ,входу блока синхронизации, четвертый и пятый выходы которого подключены соответственно к входам тактовой частоты и конца псевдослучайной последовательности вычислительного блока, выход сигнала начальной установки которого подключен к соответствующему входу буферного блока и к второму входу блока синхронизации, второй выход которого подключен к синхронизирующему входу аналого-цифрового преобразователя.

5

0

5

0

и является входом начальной установки буферного блока, входом установки в ноль которого является второй вход счетчика, третий вход которого соединен с входом линии задержки и является входом тактовой частоты буферного блока, входом синхронизации

считывания которого является второй вход запоминающего блока, третий

и пятый входы которого соединены соответственно с выходом блока формиро вания адреса и выходом линии задержки, а выход запоминающего блока является выходом буферного блока, пер- вьш вход запоминающего блока является входом установки в единичное состояние.

п

/V

20

16

;з

12

15

1В

Физ.2

21

19

17

ФЫ8. Ц

| Ohlhaber R.L | |||

| Eye pattern testing of fiber optic systems | |||

| - Proceedigs Fiber Optic and Communications, 1978, p | |||

| Регулятор давления для автоматических тормозов с сжатым воздухом | 1921 |

|

SU195A1 |

Авторы

Даты

1988-04-23—Публикация

1986-12-08—Подача