00

;о

ND

Од

to

Изобретение относится к автоматике и вычислительной технике и может найти применение в системах управления и контроля.

Целью изобретения является повышение помехозащищенности при одновременном упрощении.

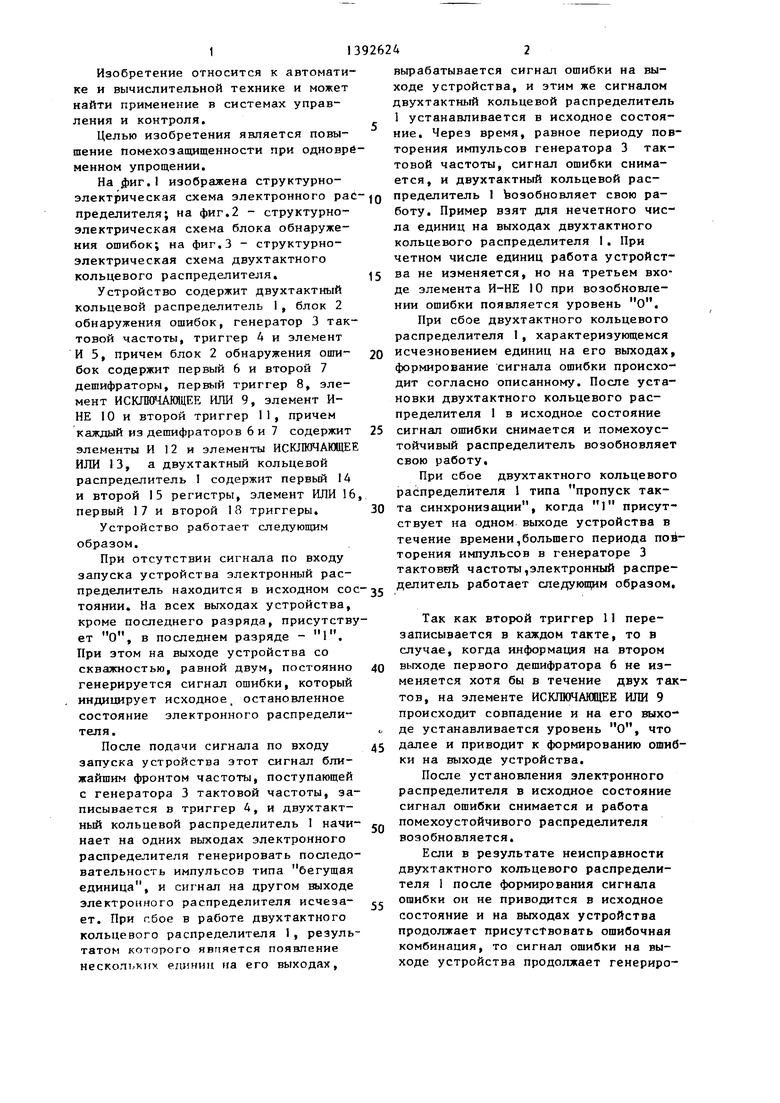

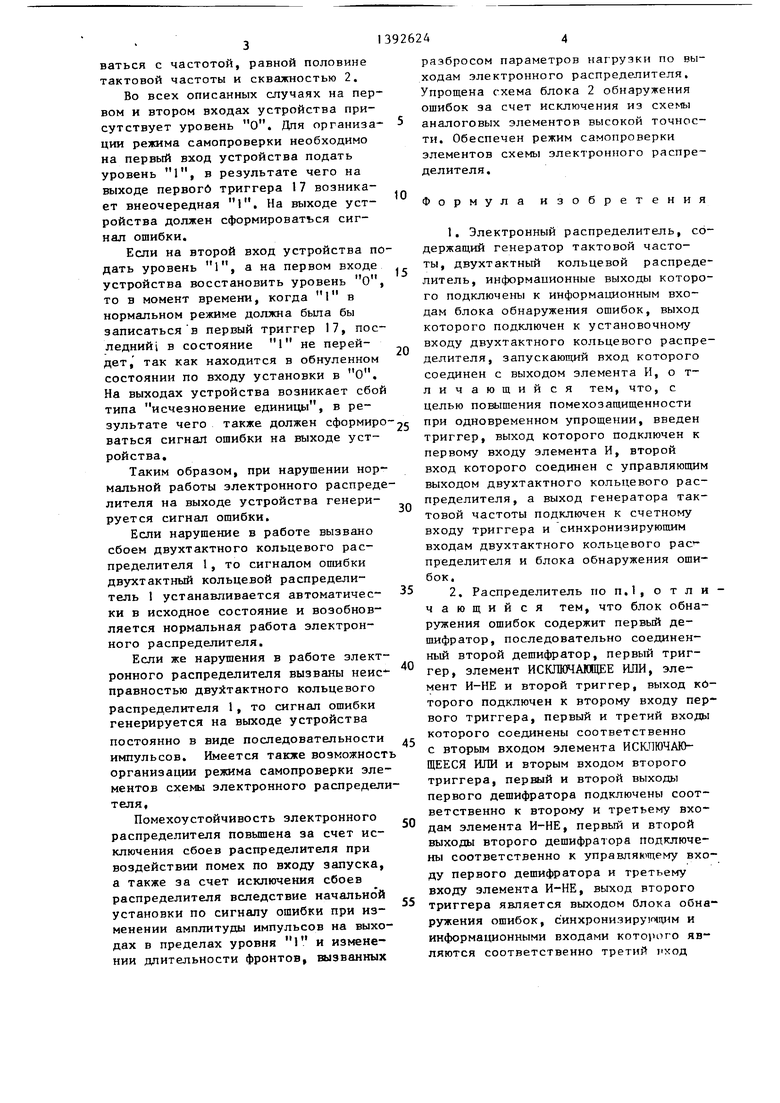

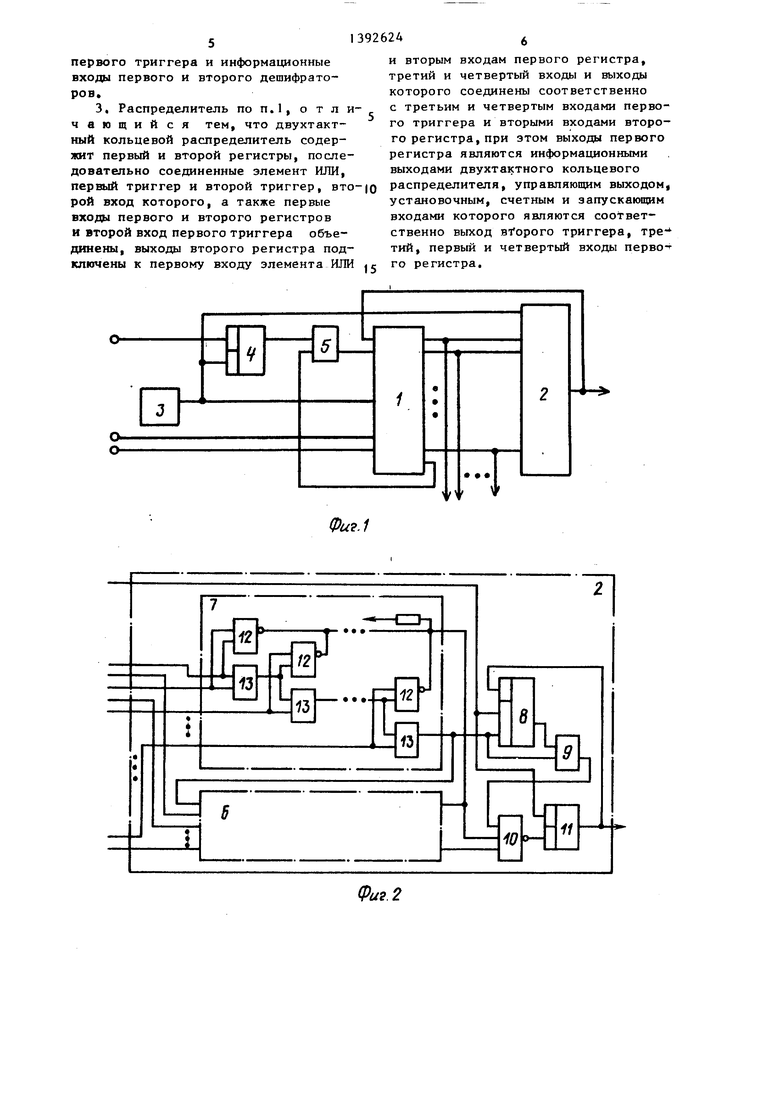

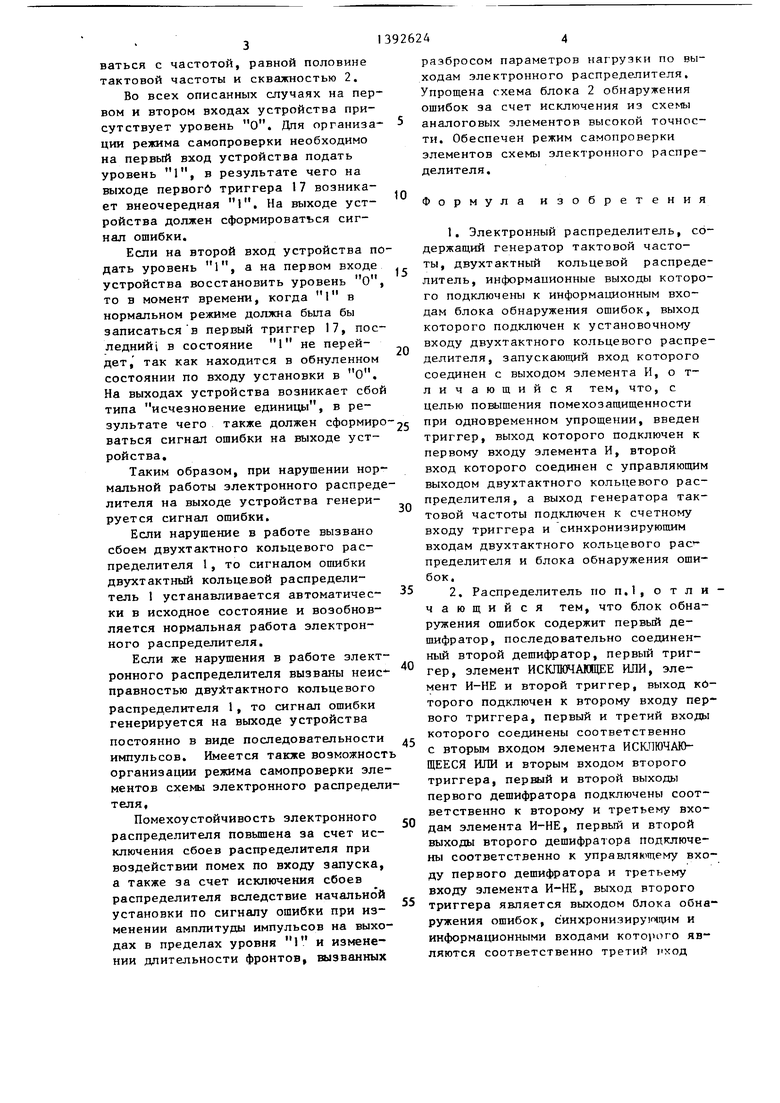

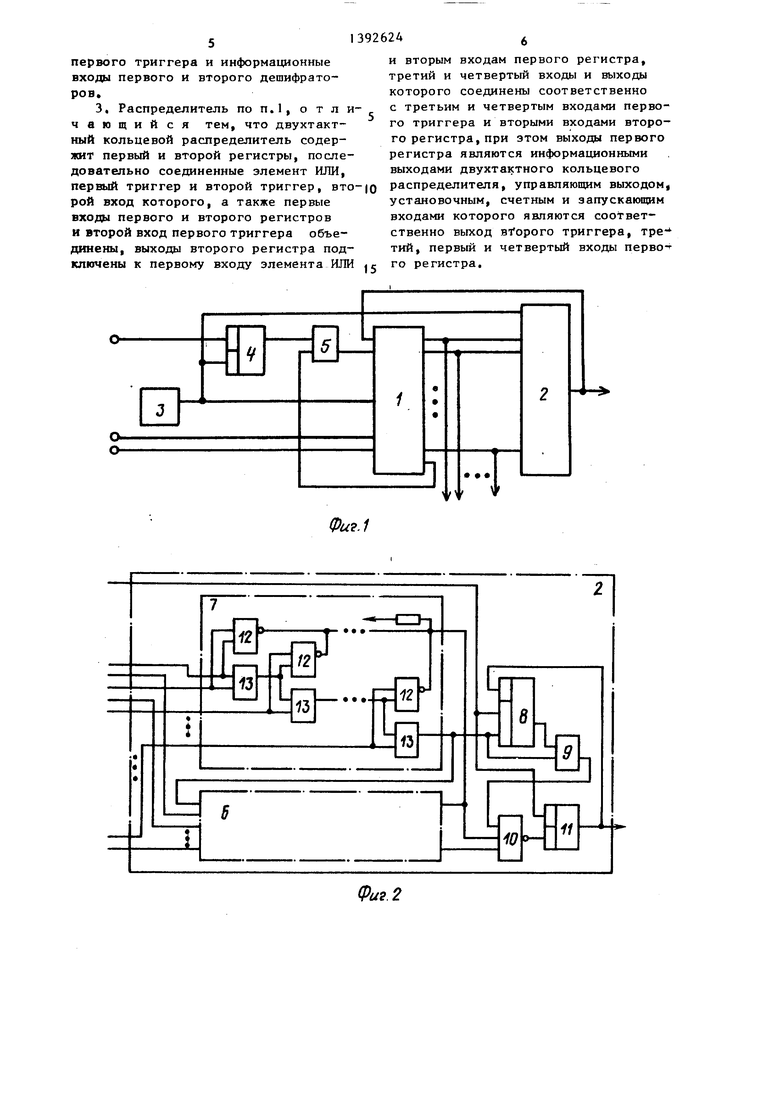

На .1 изображена структурно- электрическая схема электронного paC пределителя; на фиг.2 - структурно- электрическая схема блока обнаружения ошибок; на фиг.З - структурно- электрическая схема двухтактного кольцевого распределителя,

Устройство содержит двухтактный кольцевой распределитель I, блок 2 обнаружения ошибок, генератор 3 тактовой частоты, триггер А и элемент И 5, причем блок 2 обнаружения оши- бок содержит первый 6 и второй 7 дешифраторы, первый триггер 8, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 9, элемент И- НЕ 10 и второй триггер 11, причем каждый из дешифраторов 6и 7 содержит элементы И 12 и элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 13, а двухтактный кольцевой распределитель 1 содержит первый 14 и второй 15 регистры, элемент ИЛИ 16 первый 17 и второй 18 триггеры.

Устройство работает следующим образом.

При отсутствии сигнала по входу запуска устройства электронный распределитель находится в исходном сое тоянии. На всех выходах устройства, кроме последнего разряда, присутствует о, в последнем разряде - 1. При этом на выходе устройства со скважностью, равной двум, постоянно генерируется сигнал ошибки, который индицирует исходное, остановленное состояние электронного распределителя.

После подачи сигнала по входу запуска устройства этот сигнал ближайшим фронтом частоты, поступающей с генератора 3 тактовой частоты, записывается в триггер 4, и двухтактный кольцевой распределитель I начинает на одних выходах электронного распределителя генерировать последовательность импульсов типа бегущая единица, и сигнал на другом выходе электронного распределителя исчеза- ет. При сбое в работе двухтактного кольцевого распределителя 1, результатом которого явпяется появление несколтлхих ециниа fta его выходах.

Q 5

0 5 0

5 0

5

0

вьфабатывается сигнал ошибки на выходе устройства, и этим же сигналом двухтактный кольцевой распределитель 1 устанавливается в исходное состояние. Через время, равное периоду повторения импульсов генератора 3 тактовой частоты, сигнал ошибки снимается, и двухтактный кольцевой распределитель 1 возобновляет свою работу. Пример взят для нечетного числа единиц на выходах двухтактного кольцевого распределителя 1. При четном числе единиц работа устройства не изменяется, но на третьем входе элемента И-НЕ 10 при возобновлении ошибки появляется уровень О.

При сбое двухтактного кольцевого распределителя 1, характеризующемся исчезновением единиц на его выходах, формирование сигнала ошибки происходит согласно описанному. После установки двухтактного кольцевого распределителя 1 в исходно.е состояние сигнал ощибки снимается и помехоустойчивый распределитель возобновляет свою работу.

При сбое двухтактного кольцевого распределителя 1 типа пропуск такта синхронизации, когда 1 присутствует на одном выходе устройства в течение времени,большего периода повторения импульсов в генераторе 3 тактовнй частоты,электронный распределитель работает следующим образом.

Так как второй триггер 11 перезаписывается в каждом такте, то в случае, когда информация на втором выходе первого дешифратора 6 не изменяется хотя бы в течение двух тактов, на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 9 происходит совпадение и на его выходе устанавливается уровень О, что далее и приводит к формированию ошибки на выходе устройства.

После установления электронного распределителя в исходное состояние сигнал ошибки снимается и работа помехоустойчивого распределителя возобновляется.

Если в результате неисправности двухтактного кольцевого распределителя 1 после формирования сигнала ошибки он не приводится в исходное состояние и на выходах устройства продолжает присутствовать ошибочная комбинация, то сигнал ошибки на выходе устройства продолжает генерироваться с частотой, равной половине тактовой частоты и скважностью 2.

Во всех описанных случаях на первом и втором входах устройства присутствует уровень о. Для организации режима самопроверки необходимо на первый вход устройства подать уровень 1, в результате чего на выходе первогб триггера 17 возникает внеочередная 1. На выходе устройства должен сформироваться сигнал ошибки.

Если на второй вход устройства подать уровень 1, а на первом входе устройства восстановить уровень О, то в момент времени, когда I в нормальном режиме должна была бы записаться в первый триггер 17, пос- ледниЙ1 в состояние 1 не перейдет, так как находится в обнуленном состоянии по входу установки в О. На выходах устройства возникает сбой типа исчезновение единицы, в ре

разбросом параметров нагрузки по выходам электронного распределителя. Упрощена схема блока 2 обнаружения ошибок за счет исключения из схемы аналоговых элементов высокой точности. Обеспечен режим самопроверки элементов схемы электронного распределителя.

Формула изобретения

1. Электронный распределитель, содержащий генератор тактовой частоты, двухтактный кольцевой распределитель, информационные выходы которого подьслючены к информационным входам блока обнаружения ошибок, выход которого подключен к установочному входу двухтактного кольцевого распределителя, запускающий вход которого соединен с выходом элемента И, о тличающиицелью повышения

с я тем, что, с помехозащищенности

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1149318A1 |

| Устройство для контроля логических блоков | 1980 |

|

SU902018A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1152042A1 |

| Устройство для контроля мажоритарных схем | 1983 |

|

SU1117643A1 |

| Устройство для контроля ошибок аппаратуры многоканальной магнитной записи | 1988 |

|

SU1580438A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU964707A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для контроля синхронизма воспроизведенных сигналов | 1988 |

|

SU1585833A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК ДИСКРЕТНОГО КАНАЛА СВЯЗИ | 1995 |

|

RU2138910C1 |

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

Изобретение относится к автоматике и вычислительной Технике и может использоваться в системах управления и контроля. Цель изобретения- повышение помехозащищенности при одновременном упрощении устр-ва. Элект ронный распределитель (ЭР) содержит двухтактный кольцевой распределитель (ДКР) I, блок обнаружения ошибок 2, генератор 3 тактовой частоты, триггер 4 и элемент И 5. В исходном состоянии на всех выходах устр-ва, кроме последнего, присутствует логический о, а на последнем - 1. При поступлении сигнала запуска ДКР 1 начинает генерировать на выходах ЭР последовательность импульсов типа бегущая единица. При сбое в работе ДКР 1, в результате которого на его выходах исчезает 1 или появляются несколько 1, блок обнаружения сигнал ошиб- устанавлиошибок 2 вырабатывает ки, по которому ДКР 1 вается в исходное состояние. Через время, равное периоду импульсов генератора 3, ДКР 1 возобновляет работу. Поясняется работа блока обнаружения ошибки 2, ДКР 1 и всего устр- ва при сбое ДКР 1 типа пропуск такта синхронизации. 2 з.п. ф-лы, 3 ил. (Л

зультате чего также должен сформиро-25 при одновременном упрощении, введен

ваться сигнал ошибки на выходе устройства.

Таким образом, при нарушении нормальной работы электронного распределителя на выходе устройства генерируется сигнал ошибки.

Если нарушение в работе вызвано сбоем двухтактного кольцевого распределителя 1 , то сигналом ошибки двухтактный кольцевой распределитель 1 устанавливается автоматически в исходное состояние и возобновляется нормальная работа электронного распределителя.

Если же нарушения в работе электронного распределителя вызваны неис правностью двухтактного кольцевого

распределителя 1, то сигнал ошибки генерируется на выходе устройства

постоянно в виде последовательности импульсов. Имеется также возможность организации режима самопроверки элементов схемы электронного распределителя.

Помехоустойчивость электронного распределителя повышена за счет исключения сбоев распределителя при воздействии помех по входу запуска, а также за счет исключения сбоев распределителя вследствие начальной установки по сигналу ошибки при изменении амплитуды импульсов на выходах в пределах уровня 1 и изменении длительности фронтов, вызванных

30

35

40

45

50

55

триггер, выход которого подключен к первому входу элемента И, второй вход которого соединен с управляющим выходом двухтактного кольцевого распределителя, а выход генератора тактовой частоты подключен к счетному входу триггера и синхронизирующим входам двухтактного кольцевого рас г- пределителя и блока обнаружения ошибок.

30

35

40

45

50

55

триггер, выход которого подключен к первому входу элемента И, второй вход которого соединен с управляющим выходом двухтактного кольцевого распределителя, а выход генератора тактовой частоты подключен к счетному входу триггера и синхронизирующим входам двухтактного кольцевого рас г- пределителя и блока обнаружения ошибок.

первого триггера и информационные входы первого и второго дешифраторов,

3, Распределитель по п.1, о т л и чающийся тем, что двухтактный кольцевой распределитель содержит первый и второй регистры, последовательно соединенные элемент ИЛИ, первый триггер и второй триггер, вто рой вход которого, а также первые входы первого и второго регистров и второй вход первого триггера объединены, выходы второго регистра подключены к первому входу элемента ИЛИ

|0

15

и вторым входам первого регистра, третий и четвертый входы и выходы которого соединены соответственно с третьим и четвертым входами первого триггера и вторыми входами второго регистра, при этом выходы первого регистра являются информационными выходами двухтактного кольцевого распределителя, управляющим выходом, установочным, счетным и эапускаю1цим входами которого являются соответственно выход второго триггера, тре- тий, первый и четвертый входы перво-т го регистра.

Ч

м-

Фиг. 2

Фие.З

| Помехоустойчивый распределитель | 1980 |

|

SU930729A1 |

Авторы

Даты

1988-04-30—Публикация

1986-01-21—Подача