Изобретение относится к вычислительной технике и может быть использовано в качестве основного и вспомогательного ЗУ в вычислительных системах.

Известно запоминающее устройство с самоконтролем, содержащее накопитель, выход которого подключен к входам регистров прямого и обратного кодов, блок обнаружения отказавщих разрядов, входы которого соединены с; прямыми выходами регистров прямого и обратного кодов, корректирующее устройство, вход которого соединен с выходом регистра прямого кода, схему равенства кодов, к входам которой подключены выходы блока обнаружения отказавщих разрядов и корректирующего устройства, блок управления, входы которого связаны с выходами корректирующего устройства и схемы равенства кодов, а выходы - с входами регистров прямого и обратного кодов и блока элементов И, к вторым входам которого подключен выход корректирующего устройства. Выход регистра прямого кода соединен с входом накопителя 1.

Недостатками этого устройства являются ограниченные обнаруживающая и корректирующая способности при появлении ощибок, вызванных сбоями, а также, совместным действием отказов и сбоев.

Наиболее близким к изобретению является запоминающее устройство с самоконтролем, содержащее накопитель, регистры прямого и обратного кодов, коммутатор, блок декодирования, дешифратор, блок контроля, блок коррекции, элемент ИЛИ, блок элементов И-ИЛИ, регистр, блок управления, причем информационные входы накопителя подключены к инверсным выходам регистра прямого кода, а выходы накопителя соединены с информационными входами регистров прямого и обратного кодов, прямые выходы регистра прямого кода соединены с одними входами блока контроля и коммутатора, другие входы которых подключены, к выходам регистра обратного кода, выходы-коммутатора соединены с входами блока декодирования и одними входами блока коррекции, выходы которого соединены с инфо1рмационными входами регистра, выходы блока декодирования подключены к входам дещифратора и элемента ИЛИ, выходы дешифратора подключены к другим входам блока коррекции и одним входам блока элементов И-ИЛИ, другие входы которого соединены с выходами блока контроля, одни выходы блока управления подключены к управляющим входам накопителя, регистров прямого и обратного кодов , регистра, другие выходы являются контрольными выходами устройства, выходы элемента ИЛИ, блока элементов и-ИЛИ подключены к входам блока управления 2.

Недостатками известного устройства являются ограниченные обнаруживающая и корректирующая способности.

Целью изобретения является повышение надежности устройства.

Поставленная цель достигается тем, что

в запоминающее устройство с самоконтролем, содержащее накопитель, регистры прямого и обратного кодов, блок контроля, первые блок декодирования, дешифратор, блок коррекции, блок сравнения и блок управнения, причем информационные входы

5 накопителя подключены к инверсным выходам регистра прямого кода, а выходы накопителя соединены с информационными входами регистров прямого и обратного кодов, прямые выходы регистра прямого кода соединены с одними входами блока контроля, первого блока коррекции и входами первого блока декодирования, одни выходы которого подключены к входам первого дещифратора, выходы которого соединены с другими входами первого блока коррекции и одними входами первого блока сравнения, другие входы которого подключены к выходам блока контроля, выходы блока контроля, первого блока сравнения и другие выходы первого блока декодирования подключены соответственно к первому, второму, третьему, и четвертому входам блока управления, первый,второй и третий выходы которого соединены соответственно с управляющими входами накопителя и регистров прямого и обратного кодов, пятый и шестой входы и четвертый и пятый выходы блока управления являются соответственно управляющими входами и контрольными выходами устройства, введены вторые блок декодирования, дещифратор, блок коррекции, блок сравнения, а так° же блок элементов И-ИЛИ, причем выходы регистра обратного кода подключены к другим входам блока конт-роля, к входам второго блока декодирования и одним входам второго блока коррекции, одни выходы

5 второго блока декодирования соединены с входами второго дешифратора, выходы которого подключены к другим, входам второго блока коррекции и одним входам второго блока сравнения, другие входы которого соединены с выходами блока контроля,

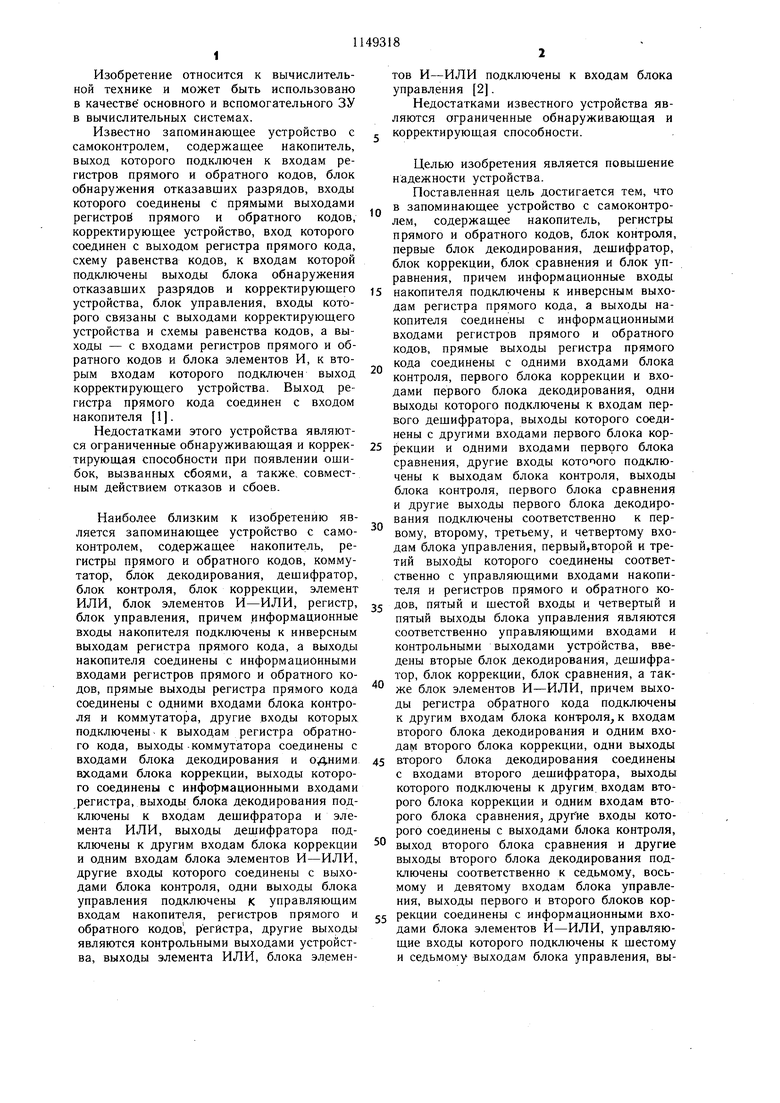

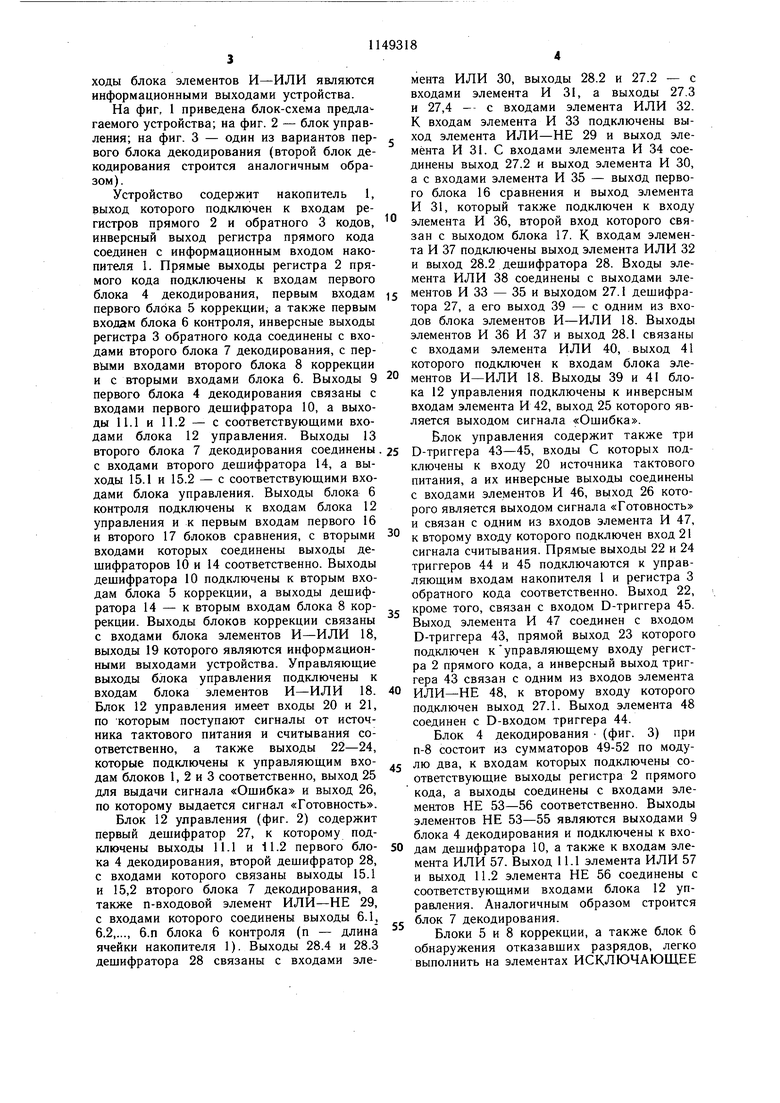

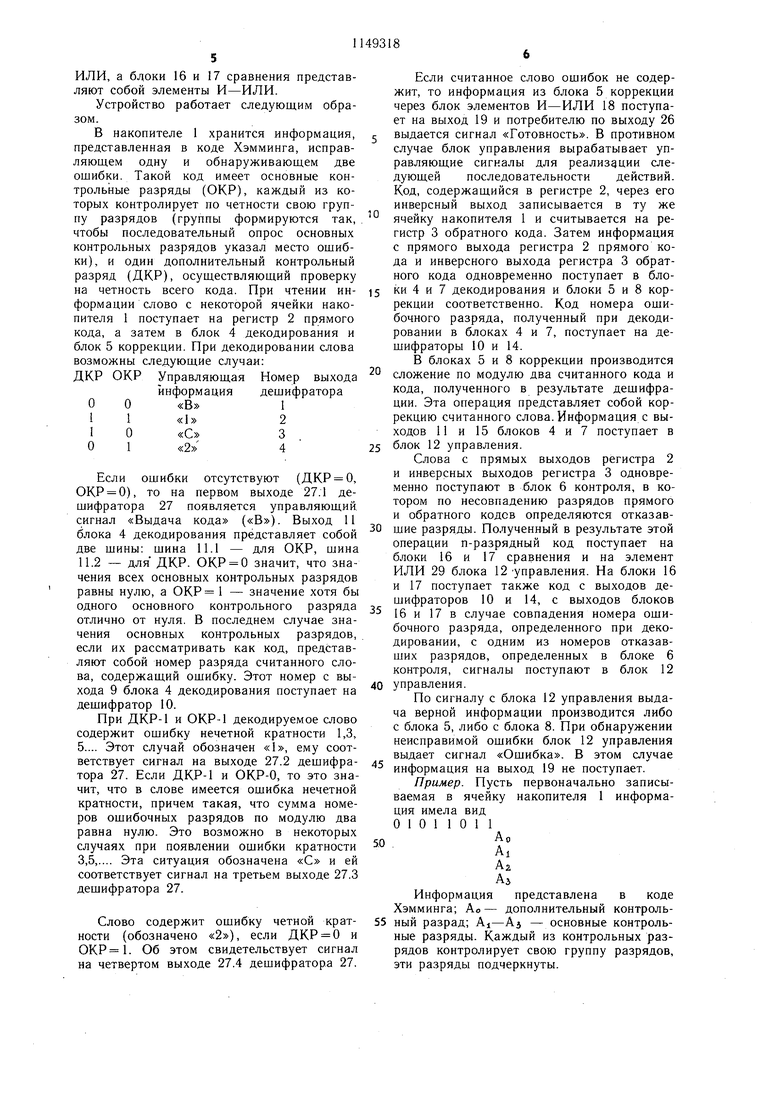

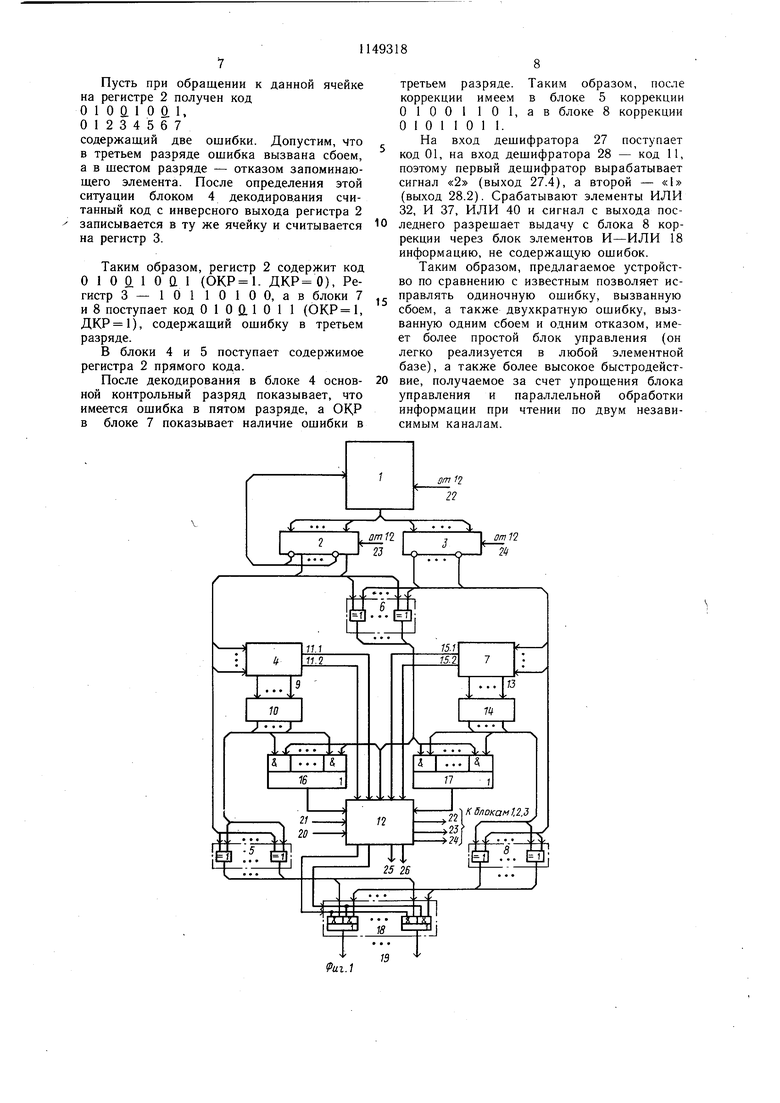

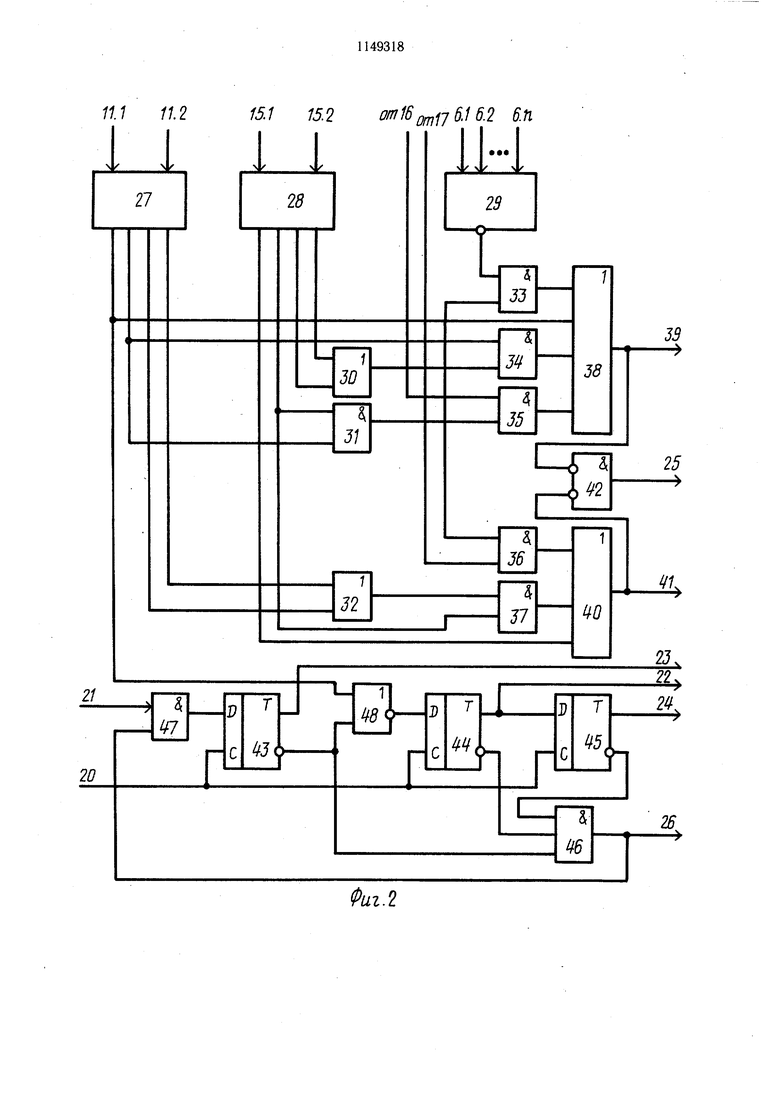

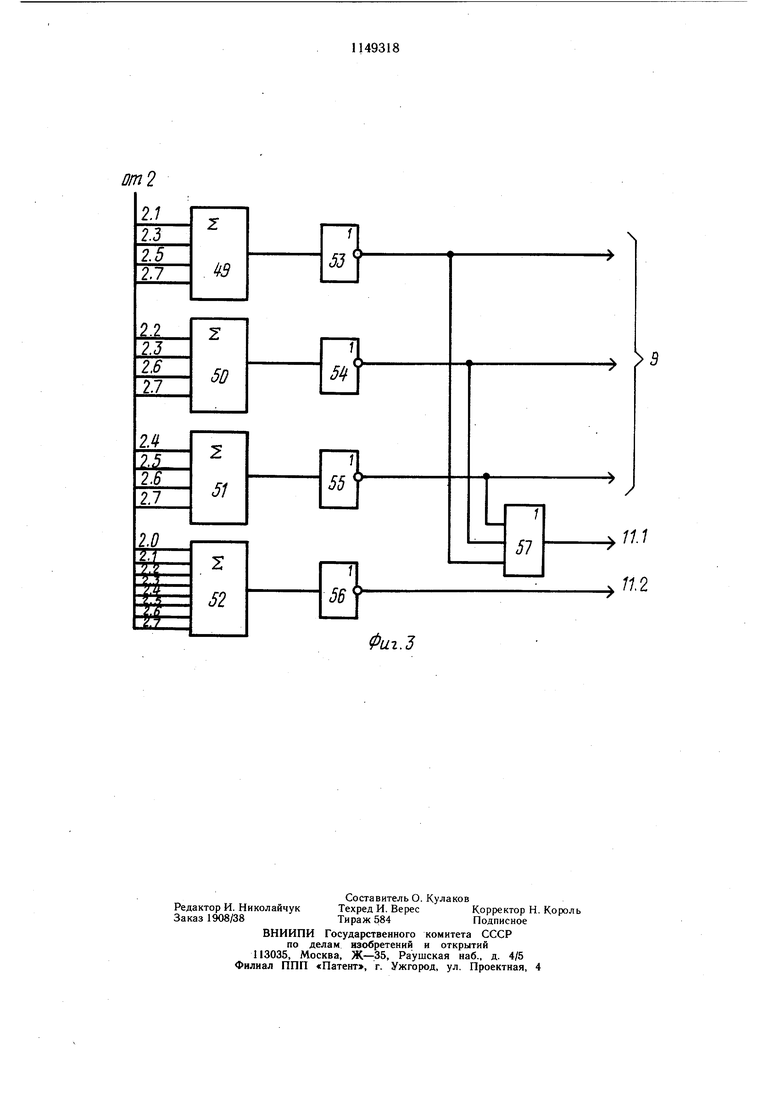

0 выход второго блока сравнения и другие выходы второго блока декодирования подключены соответственно к седьмому, восьмому и девятому входам блока управления, выходы первого и второго блоков коррекции соединены с информационными входами блока элементов И-ИЛИ, управляющие входы которого подключены к щестому и седьмому выходам блока управления, выходы блока элементов И-ИЛИ являются информационными выходами устройства. На фиг, 1 приведена блок-схема предла гаемого устройства; на фиг. 2 - блок управления; на фиг. 3 - один из вариантов первого блока декодирования (второй блок декодирования строится аналогичным образом). Устройство содержит накопитель 1, выход которого подключен к входам регистров прямого 2 и обратного 3 кодов, инверсный выход регистра прямого кода соединен с информационным входом накопителя 1. Прямые выходы регистра 2 прямого кода подключены к входам первого блока 4 декодирования, первым входам первого блока 5 коррекции, а также первым входам блока 6 контроля, инверсные выходы регистра 3 обратного кода соединены с входами второго блока 7 декодирования, с первыми входами второго блока 8 коррекции и с вторыми входами блока 6. Выходы 9 первого блока 4 декодирования связаны с входами первого дешифратора 10, а выходы 11.1 и 11.2 - с соответствующими входами блока 12 управления. Выходы 13 второго блока 7 декодирования соединены с входами второго дешифратора 14, а выходы 15.1 и 15.2 - с соответствующими входами блока управления. Выходы блока 6 контроля подключены к входам блока 12 управления и к первым входам первого 16 и второго 17 блоков сравнения, с вторыми входами которых соединены выходы дешифраторов 10 и 14 соответственно. Выходы дешифратора 10 подключены к вторым входам блока 5 коррекции, а выходы дешифратора 14 - к вторым входам блока 8 коррекции. Выходы блоков коррекции связаны с входами блока элементов И-ИЛИ 18, выходы 19 которого являются информационными выходами устройства. Управляющие выходы блока управления подключены к входам блока элементов И-ИЛИ 18. Блок 12 управления имеет входы 20 и 21, по которым поступают сигналы от источника тактового питания и считывания соответственно, а также выходы 22-24, которые подключены к управляющим входам блоков 1, 2 и 3 соответственно, выход 25 для выдачи сигнала «Ошибка и выход 26, по которому выдается сигнал «Готовность. Блок 12 управления (фиг. 2) содержит первый дешифратор 27, к которому подключены выходы 11.1 и 11.2 первого блока 4 декодирования, второй дешифратор 28, с входами которого связаны выходы 15.1 и 15,2 второго блока 7 декодирования, а также п-входовой элемент ИЛИ-НЕ 29, с входами которого соединены выходы 6.1, 6.2,..., 6.П блока 6 контроля (п - длина ячейки накопителя 1). Выходы 28.4 и 28.3 дешифратора 28 связаны с входами элемента ИЛИ 30, выходы 28.2 и 27.2 - с входами элемента И 31, а выходы 27.3 и 27,4 - с входами элемента ИЛИ 32. К входам элемента И 33 подключены выход элемента ИЛИ-НЕ 29 и выход элемента И 31. С входами элемента И 34 соединены выход 27.2 и выход элемента И 30, а с входами элемента И 35 - выход первого блока 16 сравнения и выход элемента И 31, который также подключен к входу элемента И 36, второй вход которого связан с выходом блока 17. К входам элемента И 37 подключены выход элемента ИЛИ 32 и выход 28.2 дешифратора 28. Входы элемента ИЛИ 38 соединены с выходами элементов И 33 - 35 и выходом 27.1 дешифратора 27, а его выход 39 - с одним из входов блока элементов И-ИЛИ 18. Выходы элементов И 36 И 37 и выход 28.1 связаны с входами элемента ИЛИ 40, выход 41 которого подключен к входам блока элементов И-ИЛИ 18. Выходы 39 и 41 блока 12 управления подключены к инверсным входам элемента И 42, выход 25 которого является выходом сигнала «Ошибка. Блок управления содержит также три D-триггера 43-45, входы С которых подключены к входу 20 источника тактового питания, а их инверсные выходы соединены с входами элементов И 46, выход 26 которого является выходом сигнала «Готовность и связан с одним из входов элемента И 47, к второму входу которого подключен вход 21 сигнала считывания. Прямые выходы 22 и 24 триггеров 44 и 45 подключаются к управляющим входам накопителя 1 и регистра 3 обратного кода соответственно. Выход 22, кроме того, связан с входом D-триггера 45. Выход элемента И 47 соединен с входом D-триггера 43, прямой выход 23 которого подключен куправляющему входу регистра 2 прямого кода, а инверсный выход триггера 43 связан с одним из входов элемента ИЛИ-НЕ 48, к второму входу которого подключен выход 27.1. Выход элемента 48 соединен с D-входом триггера 44. Блок 4 декодирования (фиг. 3) при п-8 состоит из сумматоров 49-52 по модулю два, к входам которых подключены соответствующие выходы регистра 2 прямого кода, а выходы соединены с входами элемеатов НЕ 53-56 соответственно. Выходы элементов НЕ 53-55 являются выходами 9 блока 4 декодирования и подключены к входам дешифратора 10, а также к входам элемента ИЛИ 57. Выход 11.1 элемента ИЛИ 57 и выход 11.2 элемента НЕ 56 соединены с соответствующими входами блока 12 управления. Аналогичным образом строится блок 7 декодирования. Блоки 5 и 8 коррекции, а также блок 6 обнаружения отказавших разрядов, легко выполнить на элементах ИСКЛЮЧАЮЩЕЕ

ИЛИ, а блоки 16 и 17 сравнения представляют собой элементы И-ИЛИ.

Устройство работает следующим образом.

В накопителе 1 хранится информация, представленная в коде Хэмминга, исправляющем одну и обнаруживающем две ошибки. Такой код имеет основные контрольные разряды (ОКР), каждый из которых контролирует по четности свою группу разрядов (группы формируются так, чтобы последовательный опрос основных контрольных разрядов указал место ошибки), и один дополнительный контрольный разряд (ДКР), осуществляющий проверку на четность всего кода. При чтении информации слово с некоторой ячейки накопителя 1 поступает на регистр 2 прямого кода, а затем в блок 4 декодирования и блок 5 коррекции. При декодировании слова возможны следующие случаи: ДКР ОКР Управляющая Номер выхода информация дешифратора

0О«В 1

11«1 2 I О «С 3 О 1 4

Если ошибки отсутствуют (ДКР 0, ОКР 0), то на первом выходе 27.1 дешифратора 27 появляется управляющий сигнал «Выдача кода («В). Выход 11 блока 4 декодирования представляет собой две шины: шина 11.1 - для ОКР, шина 11.2 - для ДКР. ОКР О значит, что значения всех основных контрольных разрядов равны нулю, а ОКР 1 - значение хотя бы одного основного контрольного разряда отлично от нуля, в последнем случае значения основных контрольных разрядов, если их рассматривать как код, представляют собой номер разряда считанного слова, содержащий ошибку. Этот номер с выхода 9 блока 4 декодирования поступает на дещифратор 10.

При ДКР-1 и ОКР-1 декодируемое слово содержит ошибку нечетной кратности 1,3, 5.... Этот случай обозначен «1, ему соответствует сигнал на выходе 27.2 дешифратора 27. Если ДКР-1 и ОКР-0, то это значит, что в слове имеется ошибка нечетной кратности, причем такая, что сумма номеров ошибочных разрядов по модулю два равна нулю. Это возможно в некоторых случаях при появлении ошибки кратности 3,5,.... Эта ситуация обозначена «С и ей соответствует сигнал на третьем выходе 27.3 дешифратора 27.

Слово содержит ошибку четной кратности (обозначено «2), если ДКР 0 и . Об этом свидетельствует сигнал на четвертом выходе 27.4 дешифратора 27.

Если считанное слово ошибок не содержит, то информация из блока 5 коррекции через блок элементов И-ИЛИ 18 поступает на выход 19 и потребителю по выходу 26

выдается сигнал «Готовность. В противном случае блок управления вырабатывает управляющие сигналы для реализации следующей последовательности действий. Код, содержащийся в регистре 2, через его инверсный выход записывается в ту же ячейку накопителя 1 и считывается на регистр 3 обратного кода. Затем информация с прямого выхода регистра 2 прямого кода и инверсного выхода регистра 3 обратного кода одновременно поступает в блоки 4 и 7 декодирования и блоки 5 и 8 коррекции соответственно. Код номера ошибочного разряда, полученный при декодировании в блоках 4 и 7, поступает на дешифраторы 10 и 14.

В блоках 5 и 8 коррекции производится

0 сложение по модулю два считанного кода и кода, полученного в результате дешифрации. Эта операция представляет собой коррекцию считанного слова. Информация с выходов 11 и 15 блоков 4 и 7 поступает в

5 блок 12 управления.

Слова с прямых выходов регистра 2 и инверсных выходов регистра 3 одновременно поступают в блок 6 контроля, в котором по несовпадению разрядов прямого и обратного кодов определяются отказавшие разряды. Полученный в результате этой операции п-разрядный код поступает на блоки 16 и 17 сравнения и на элемент ИЛИ 29 блока 12 управления. На блоки 16 и 17 поступает также код с выходов дешифраторов 10 и 14, с выходов блоков

16 и 17 в случае совпадения номера ошибочного разряда, определенного при декодировании, с одним из номеров отказавших разрядов, определенных в блоке 6 контроля, сигналы поступают в блок 12

0 управления.

По сигналу с блока 12 управления выдача верной информации производится либо с блока 5, либо с блока 8. При обнаружении неисправимой ошибки блок 12 управления выдает сигнал «Ошибка. В этом случае

информация на выход 19 не поступает.

Пример. Пусть первоначально записываемая в ячейку накопителя 1 информация имела вид 01011011

,

AI

А2

АЗ

Информация представлена в коде Хэмминга; АО- дополнительный контрольный разрад; AI-АЗ - основные контрольные разряды. Каждый из контрольных разрядов контролирует свою группу разрядов, эти разряды подчеркнуты.

Пусть при обращении к данной ячейке на регистре 2 получен код 01001001, 01234567

содержащий две ощибки. Допустим, что в третьем разряде ошибка вызвана сбоем, а в щестом разряде - отказом запоминающего элемента. После определения этой ситуации блоком 4 декодирования считанный код с инверсного выхода регистра 2 записывается в ту же ячейку и считывается на регистр 3.

Таким образом, регистр 2 содержит код О 1 О О 1 О U 1 (. ), Регистр 3-101 10100, ав блоки 7 и 8 поступает код О 1 О Q. 1 О 1 1 (ОКР 1, ДКР 1), содержащий ощибку в третьем разряде.

В блоки 4 и 5 поступает содержимое регистра 2 прямого кода.

После декодирования в блоке 4 основной контрольный разряд показывает, что имеется ощибка в пятом разряде, а ОК,Р в блоке 7 показывает наличие ощибки в

третьем разряде. Таким образом, после коррекции имеем в блоке 5 коррекции 01001 1 О 1, а в блоке 8 коррекции 01011011.

На вход дешифратора 27 поступает код 01, на вход дешифратора 28 - код 11, поэтому первый дешифратор вырабатывает сигнал «2 (выход 27.4), а второй - «1 (выход 28.2). Срабатывают элементы ИЛИ 32, И 37, ИЛИ 40 и сигнал с выхода последнего разрешает выдачу с блока 8 коррекции через блок элементов И-ИЛИ 18 информацию, не содержащую ошибок.

Таким образом, предлагаемое устройство по сравнению с известным позволяет исд правлять одиночную ошибку, вызванную сбоем, а также двухкратную ошибку, вызванную одним сбоем и о.аним отказом, имеет более простой блок управления (он легко реализуется в любой элементной базе), а также более высокое быстродействие, получаемое за счет упрощения блока управления и параллельной обработки информации при чтении по двум независимым каналам.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1152042A1 |

| Запоминающее устройство с обнаружением и коррекцией ошибок | 1983 |

|

SU1138836A1 |

| Запоминающее устройство с исправлением ошибок | 1983 |

|

SU1133624A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1381605A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU898509A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU875470A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1374286A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU855730A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ, содержащее накопитель, регистры прямого и обратного кодов, блок контроля, первые блок декодирования. Дешифратор, блок коррекции, блок сравнения и блок управления, причем информационные входы накопителя подключены к инверсным выходам регистра прямого кода, а Выходы накопителя соединены с информационными входами регистров прямого и обратного кодов, прямые выходы регистра прямого кода соединены с одними входами блока контроля, первого блока коррекции и входами первого блока декодирования, одни выходы которого подключены к входам первого дешифратора, выходы которого соединены с другими входами первого блока коррекции и одними входами первого блока сравнения, другие входы которого подключены к выходам блока контроля, выходы блока контроля, первого блока сравнения и другие выходы первого блока декодирования подключены соответственно к первому, второму, третьему и четвертому входам блока управления, первый, второй и третий выходы которого соединены соответственно с управляющими входами накопителя и регистров прямого и обратного кодов, пятый и шестой входы и четвертый и пятый выходы блока управления являются соответственно управляющими входами и контрольными выходами устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены вторые блок декодирования, дешифратор, блок коррекции, блок сравнения, а также блок элементов И-ИЛИ, причем выходы регистра обратного кода подключены к другим входам блока контроля, к входам S второго блока декодирования и одним входам второго блока коррекции, одни выходы второго блока декодирования соединены с входами второго дешифратора, выходы которого подключены к другим входам второго блока коррекции и одним входам второго блока сравнения, другие входы которого соединены с выходами блока контроля, выход второго блока сравнения и другие выходы второго блока декодирования подклю чены соответственно к седьмому, восьмому и девятому входам блока управления, ходы первого и второго блоков коррекции СдЭ 00 соединены с информационными входами блока элементов И-ИЛИ, управляющие входы которого подключены к шестому и седьмому выходам блока управления, выходы блока элементов И-ИЛИ являются информационными выходами устройства.

-«W

.1

иг.2

9

-

/

ni

-

Фиг.5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU855730A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке №,3662564/24, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-04-07—Публикация

1983-12-30—Подача