Изобретение относится к радиотехнике и предназначено для использования в антенных решетках с электрическим сканированием.,

Цель изобретения - повышение точности фазирования.

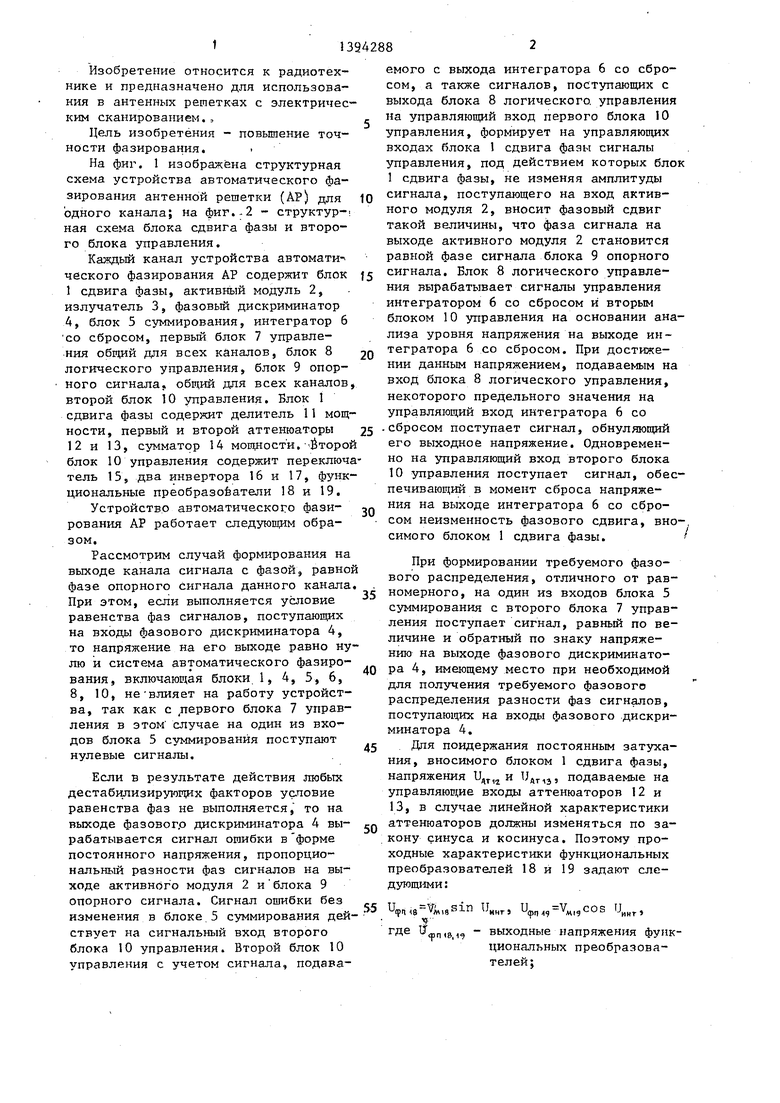

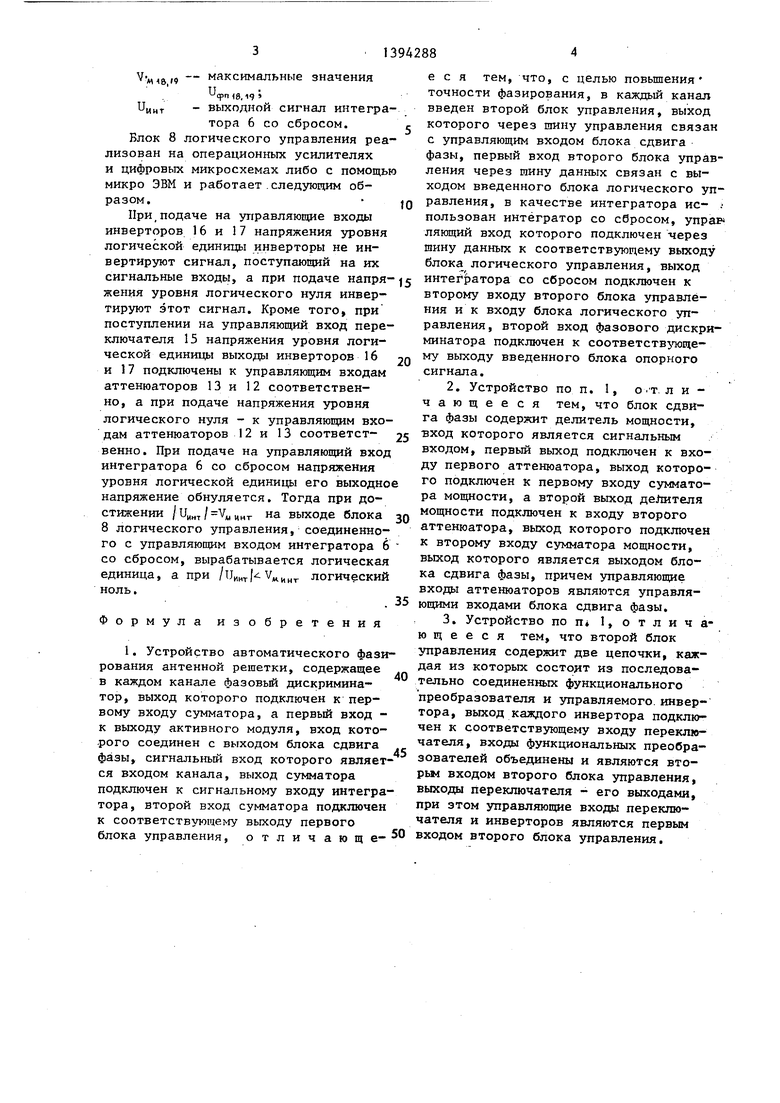

На фиг. 1 изображена структурная схема устройства автоматического фазирования антенной решетки (АР) для одного канала; на фиг.-2 - структур- ная схема блока сдвига фазы и второго блока управления.

Каждый канал устройства автомати- ческого фазирования АР содержит блок 1 сдвига фазы, активга)1й модуль 2, излучатель 3, фазовый дискриминатор 4, блок 5 суммирования, интегратор 6 СО сбросом, первый блок 7 управления обрщй для всех каналов, блок 8 логического управления, блок 9 опорного сигнала, общий для всех каналов второй блок 10 управления. Блок 1 сдвига фазы содержит делитель 11 мощности, первый и второй аттенюаторы 12 и 13, сумматор 14 могцност и. второй блок 10 управления содержит переключатель 15, два инвертора 16 и 17, функциональные преобразователи 18 и 19.

Устройство автоматического фази- рования АР работает следующим образом.

Рассмотрим случай формирования на выходе канала сигнала с фазой, равно фазе опорного сигнала данного канала При этом, если выполняется условие равенства фаз сигналов, поступающих на входы фазового дискриминатора 4, то напряжение на его выходе равно нулю и система автоматического фазирования, включающая блоки 1, 4, 5, 6, 8, 10, не влияет на работу устройства, так как с первого блока 7 управления в этом случае на один из входов блока 5 суммирования поступают нулевые сигналы.

Если в результате действия любых дестабилизирующих факторов ус-повие равенства фаз не выполняется, то на выходе фазовогр дискриминатора 4 вырабатывается сигнал ошибки в форме постоянного напряжения, пропорциональный разности фаз сигналов на выходе активног о модуля 2 и блока 9 опорного сигнала. Сигнал ошибки без изменения в блоке 5 суммирования дей ствует на сигнальный вход второго блока 10 управления. Второй блок 10 управления с учетом сигнала, подава

Q

5

0

5

0

емого с выхода интегратора 6 со сбросом, а также сигналов, поступающих с выхода блока 8 логического, управления на управляющий вход первого блока 10 управления, формирует на управляющих входах блока 1 сдвига фазы сигналы управления, под действием которых блок 1 сдвига фазы, не изменяя амплитуды сигнала, поступающего на вход активного модуля 2, вносит фазовый сдвиг такой величины, что фаза сигнала на выходе активного модуля 2 становится равной фазе сигнала блока 9 опорного сигнала. Блок 8 логического управления вырабатывает сигналы управления интегратором 6 со сбросом и вторым блоком 10 управления на основании анализа уровня напряжения на выходе интегратора 6 со сбросом. При достижении данным напряжением, подаваемым на вход блока 8 логического управления, некоторого предельного значения на управляющий вход интегратора 6 со .сбросом поступает сигнал, обнуляющий его выходное напряжение. Одновременно на управляющий вход второго блока 10 управления поступает сигнал, обеспечивающий в момент сброса напряжения на выходе интегратора 6 со сбросом неизменность фазового сдвига, вно-, симого блоком 1 сдвига фазы.

При формировании требуемого фазового распределения, отличного от равномерного, на один из входов блока 5 суммирования с второго блока 7 управления поступает сигнал, равный по величине и обратный по знаку напряжению на выходе фазового дискриминатора 4, имеющему место при необходимой для получения требуемого фазового распределения разности фаз сигналов, поступающих на входы фазового .дискриминатора 4.

Дпя поидержания постоянным затухания, вносимого блоком 1 сдвига фазы, напряжения и д, подаваемые на управляющие входы аттенюаторов 12 и 13, в случае линейной характеристики аттенюаторов должны изменяться по закону синуса и косинуса. Поэтому проходные характеристики функциональных преобразователей 18 и 19 задают сле- дздащими:

.вй1П и

..

Uq,n.,V,9COS

и,

ИНТ

где 11,, - выходные напряжения функциональных преобразователей;

Vv . ,« - максимальные значения

М В, т

и

ИНТ

ифп18,19

- ВЫХОДНОЙ сигнал интегратора 6 со сбросом.

Блок 8 логического управления реализован на операционных усилителях и цифровых микросхемах либо с помощью микро ЭВМ и работает .следующим образом.

При подаче на управляющие входы инверторов 16 и 17 напряжения уровня логической единицы инверторы не инвертируют сигнал, поступающий на их сигнальные входы, а при подаче напря жения уровня логического нуля инвертируют этот сигнал. Кроме того при поступлении на управляющий вход переключателя 15 напряжения уровня логической единицы выходы инверторов 16 и 17 подключены к управляющим входам аттенюаторов 13 и 12 соответственно, а при подаче напряжения уровня логического нуля - к управляющим входам аттенюаторов 12 и 13 соответст- венно. При подаче на управляющий вход интегратора 6 со сбросом напряжения уровня логической единицы его выходно напряжение обнуляется. Тогда при достижении /и„„т/ минт на выходе блока 8 логического управления, соединенного с управляющим входом интегратора 6 со сбросом, вырабатывается логическая единица, а при /Пцнт инг логический ноль.

Формула изобретения

1. Устройство автоматического фазирования антенной решетки, содержащее

40

в каждом канале фазовьй дискриминатор, выход которого подключен к первому входу сумматора, а первый вход - к выходу активного модуля, вход которого соединен с выходом блока сдвига . фазы, сигнальный вход которого является входом канала, выход сумматора подключен к сигнальному входу интегратора, второй вход сумматора подключен к соответствующему выходу первого блока управления, отличающе-

o

5 0 5 о

5

0

е с я тем, что, с целью повьшения точности фазирования, в каждый канал введен второй блок управления, выход которого через шину управления связан с управляющим входом блока сдвига фазы, первый вход второго блока управления через шину данных связан с выходом введенного блока логического управления, в качестве интегратора ис- . пользован интегратор со сбросом, управ ляющий вход которого подключен через щину данных к соответствующему выходу блока логического управления, выход интегратора со сбросом подключен к второму входу второго блока управления и к входу блока логического управления , второй вход фазового дискриминатора подключен к соответствзтоще- му выходу введенного блока опорного сигнала.

2.Устройство по п. 1, оVT. л и - чающееся тем, что блок сдвига фазы содержит делитель мощности, вход которого является сигнальньм входом, первый выход подключен к входу первого аттенюатора, выход которого подключен к первому входу сумматора мощности, а второй выход делителя мощности подключен к входу второго аттенюатора, выход которого подключен к второму входу сумматора мощности, выход которого является выходом блока сдвига фазы, причем зшравляющие входы аттенюаторов являются управляющими входами блока сдвига фазы,

3.Устройство по п« 1, отличающееся тем, что второй блок управления содержит два цепочки, каждая из которых состоит из последовательно соединенных функционального преобразователя и управляемого, инвертора, выход каждого инвертора подключен к соответствующему входу переключателя, входы функциональных преобразователей объединены и являются вто- рьм входом второго блока управления, выходы переключателя - его выходами, при этом управляющие входы переключателя и инверторов являются первым входом второго блока управления.

//

/

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1982 |

|

SU1840565A1 |

| Устройство распределенного автофазирования антенной решетки | 1990 |

|

SU1800526A1 |

| Устройство распределенного автофазирования антенной решетки | 1987 |

|

SU1506497A1 |

| Устройство фазирования бинарного сигнала | 1981 |

|

SU1075431A1 |

| Устройство фазирования регенераторов цифрового сигнала | 1978 |

|

SU786036A1 |

| Устройство контроля комбинационных составляющих сигнала нелинейного четырехполюсника | 1985 |

|

SU1264111A1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

| УСТРОЙСТВО УСКОРЕННОЙ СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2011 |

|

RU2446560C1 |

| Цифровой синтезатор частот с частотной модуляцией | 1985 |

|

SU1293840A1 |

Изобретение относится к радиотехнике и повьшает точность фазирования. Каждый канал устр-ва содержит блок 1 сдвига фазы, активный модуль 2, излучатель 3, фазовый дискриминатор (ФД) 4, блок 5 суммирования, интегратор (и) 6, блок управления (БУ) 7,общий для всех канёлов. Введены блок 8 логич. управления, БУ 10 и блок 9 опорного сигнала, общий для всех каналов. В качестве И 6 исполь- -зован И со сбросом. По п. 2 ф-лы блок 1 содержит делитель мощности. два аттенюатора, сумматор мо1г;ности. По п. 3 БУ 10 содержит переключатель, два инвертора, два функциональных преобразователя. При равенстве фаз сигналов, поступающих на ФД 4, напряжение на его выходе равно нулю и система автоматич. фазирования, включающая блоки 1, 4, 5, 6, 8, 10, не влияет на работу устр-ва, т.к. с БУ 7 на один из входов блока 5 поступают нулевые сигналы. Если равенство фаз не выполняется, то на выходе ФД 4 вырабатывается сигнал ошибки в форме постоянного напряжения, пропорциональный разности фаз сигналов на выходе модуля 2 и блока 9. Сигнал. ошибки в блоке 5 дейс 1;вует на сигнальный вход БУ 10, к-рый формирует на управляюш х входах блока 1 сигналы управления. Под их действием блок 1, не изменяя амплитуды сигнала, поступающего на модуль 2, вносит фа- зовьй сдвиг, и фаза сигнала на выходе модуля 2 становится равной фазе сигнала блока 9. Блок 8 вырабатывает сигналы управления И 6 и БУ 10 на основании анализа уровня напряжения на выходе И 6. 2 з,.п. ф-лы, 2 ил. (Л со 4 Ю 00 00

n

15

16

18

17

13

..J

.2

| Самойленко В.И., Ю.А | |||

| Управление фазированными антенньп и решетками - М.: Радио и связь, 1983, с | |||

| Капельная масленка с постоянным уровнем масла | 0 |

|

SU80A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-05-07—Публикация

1986-03-18—Подача