ответственно с йторыми входами второго и третьего ключей, выходы которых соединены соответственно через первы и второй сумматоры с первым и вторым входами вычитателя, выход вычитателя соединен с вторыми входами триггера, генератора и вторым выходом блока управления о

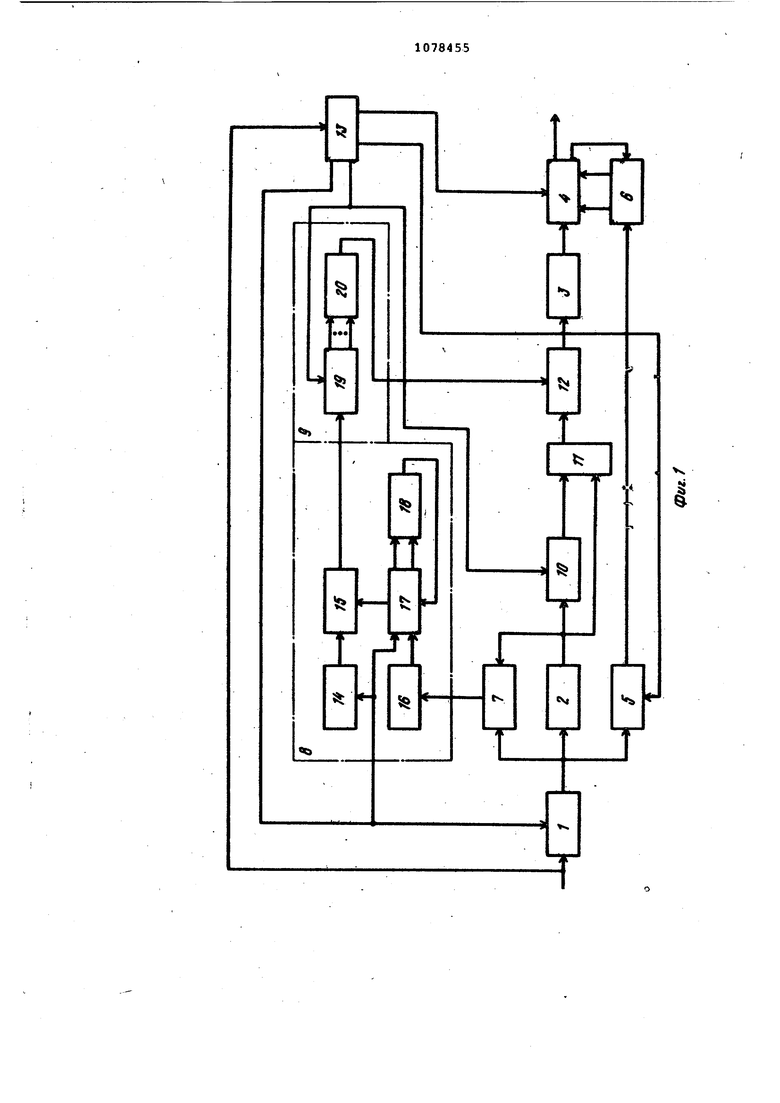

3.Устройство по п Л г о т л и чающееся тем, что первый бло памяти содержит элемент памяти и элемент задержки, первый вход и выход элемента памяти соединены соответственно с входом и выходом блока памяти, выход и второй вход элемента памяти соединены соответственно с вхог дом и выходом элемента задержки,

4.Уст Х йство по п.1, отличающееся тем, что логический блок содержит ключи, триггеры, элемент ИЛИ, элемент задержки, первые входы первого ключа и элемента ИЛИ соединены соответственно с первым и вторым входами логического блока, выход первого ключа соединен с первым входом второго ключа и с выходом логического блока,выход и второй вход второго ключа соединены соответствейно с первыми входами первого, второго триггеров, входом элемента .задержки и выходом первого триггера, выход элемента задержки соединен с вторыми входами первого и второго триггеров, выход второго триггера соединен с вторым входом элемента ИЛИ, выход которого соединен с вторым входом первого ключа,

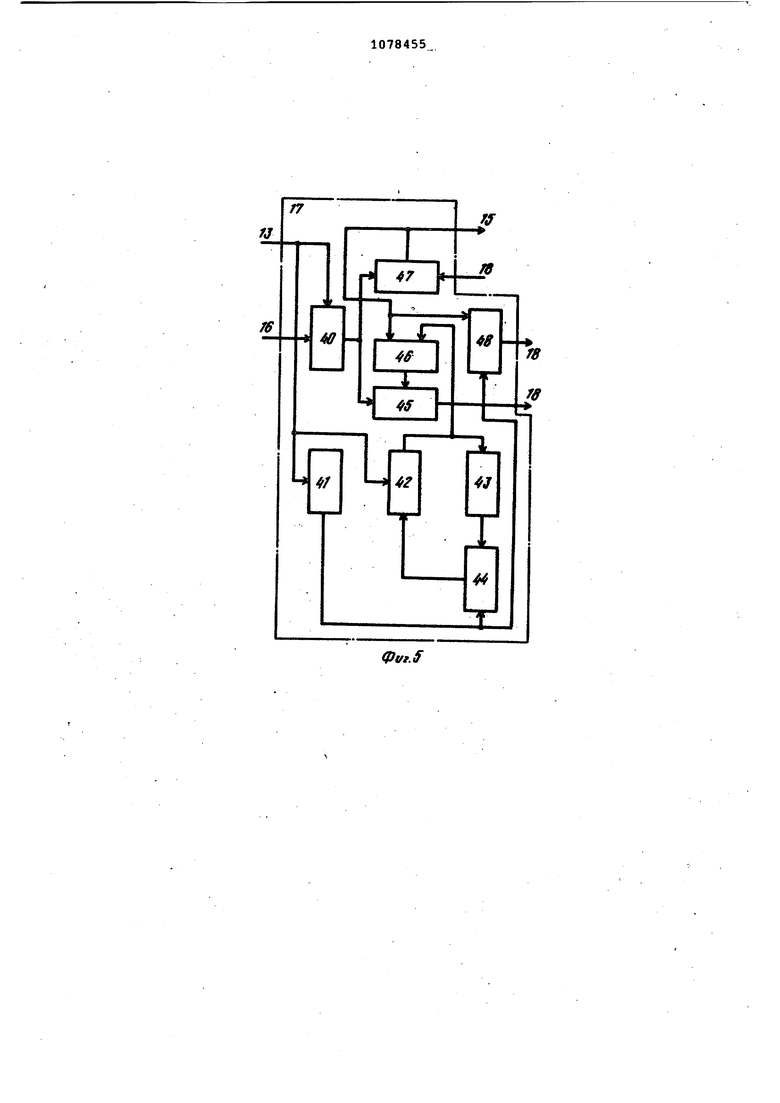

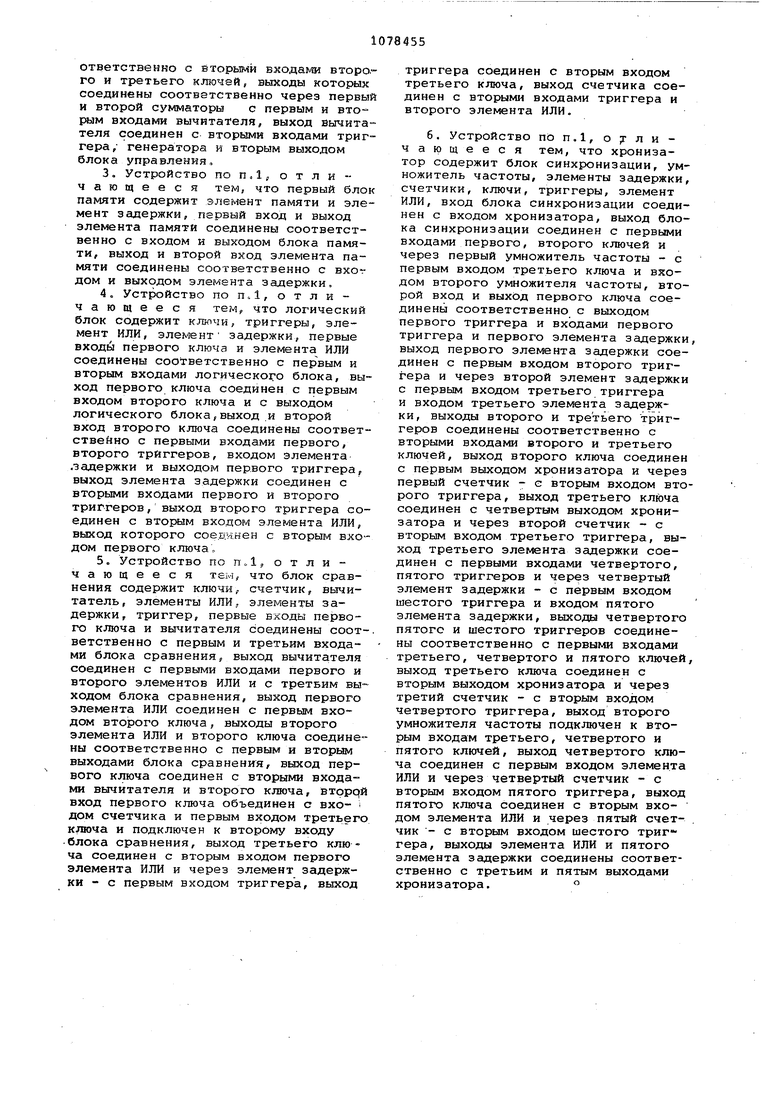

5.Устройство ПОП.1, отличающееся тем, что блок сравнения содержит ключи, счетчик, вычитатель, элементы ИЛИ., элементы задержки, триггер, первые входы первого ключа и вычитателя соединены соответственно с первым и третьим входами блока сравнения, выход вычитателя соединен с первыми входами первого и второго элементов ИЛИ и с третьим выходом блока сравнения, выход первого элемента ИЛИ соединен с первым входом второго ключа, выходы второго элемента ИЛИ и второго ключа соединены соответственно с первым и вторым выходами блока сравнения, выход первого ключа соединен с вторыми входами вычитателя и второго ключа, втрррй вход первого ключа объединен с вхо- дом счетчика и первым входом третьего ключа и подключен к второму входу

блока сравнения, выход третьего ключа соединен с вторым входом первого элемента ИЛИ и через задержки - с первым входом триггера, выход

триггера соединен с вторым входом третьего ключа, выход счетчика соединен с вторыми входами триггера и второго элемента ИЛИ.

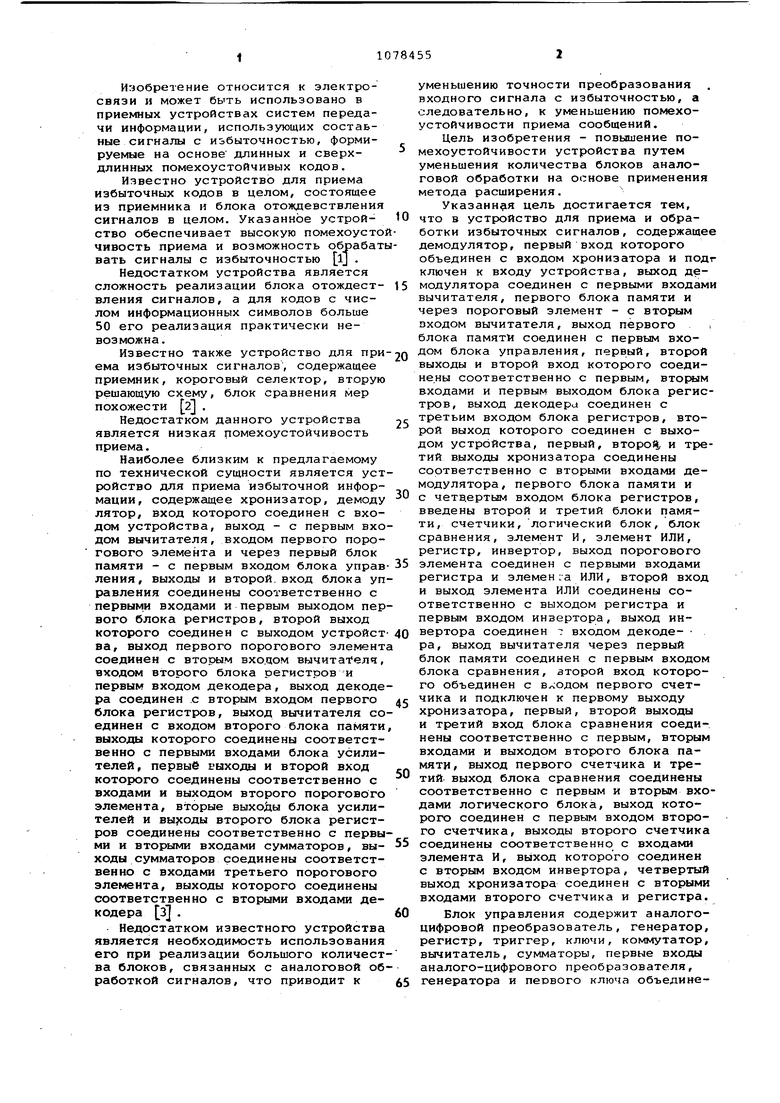

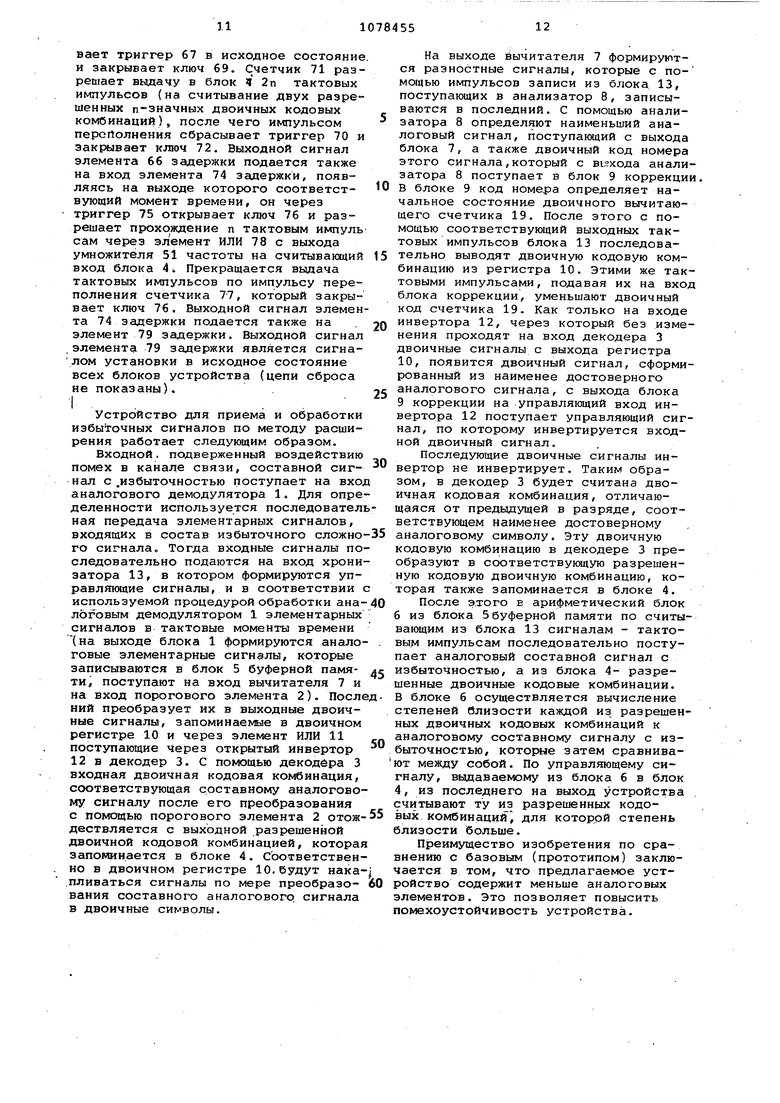

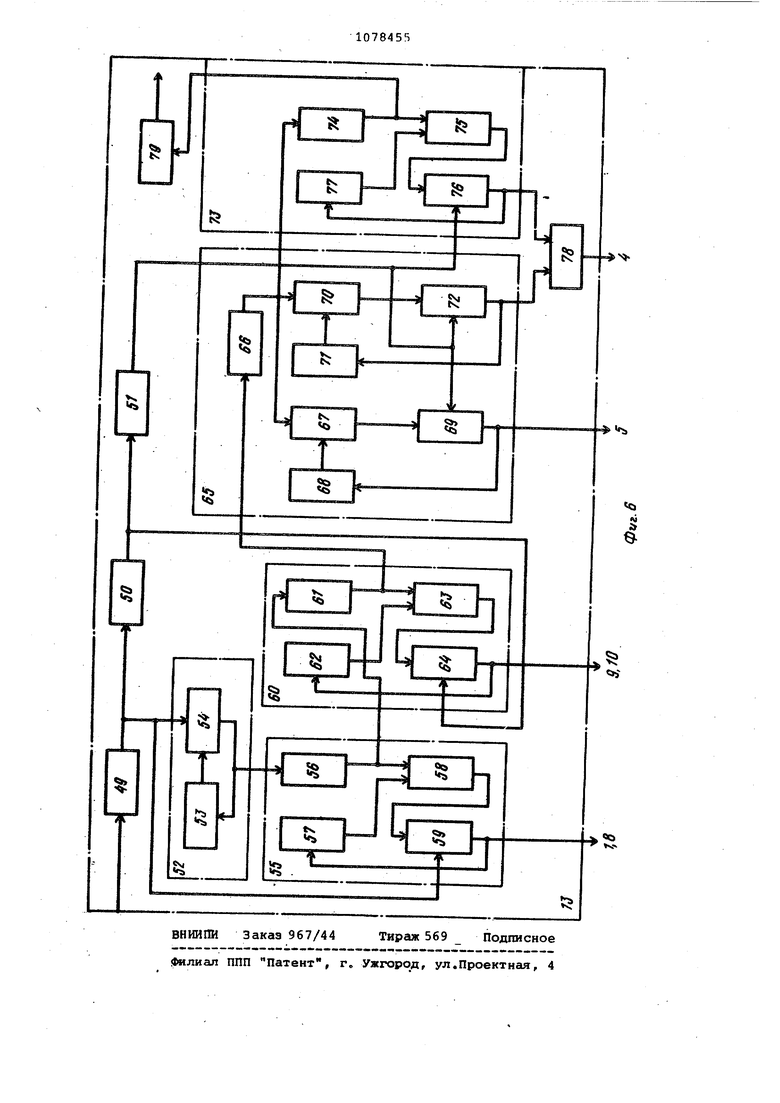

6. Устройство пОп,1, о -личающееся тем, что хронизатор содержит блок синхронизации, умножитель частоты, элементы задержки, счетчики, ключи, триггеры, элемент ИЛИ, вход блока синхронизации соединен с входом хронизатора, выход блока синхронизации соединен с первыми входами первого, второго ключей и через первый умножитель частоты - с первым входом третьего ключа и входом второго умножителя частоты, второй вход и выхОд первого ключа соединены соответственно с выходом первого триггера и входами первого триггера и первого элемента задержки выход первого элемента задержки соединен с первым входом второго триггера и через второй элемент задержки с первым входом третьего триггера и входом третьего элемента задержки, выходы второго и третьего триггеров соединены соответственно с вторыми входами второго и третьего ключей, выход второго ключа соединен с первым выходом хронизатора и через первый счетчик - с вторым входом второго триггера, выход третьего ключа соединен с четвертым выходом хронизатора и через второй счетчик - с вторым входом третьего триггера, выход третьего элемента задержки соединен с первыми входами четвертого, пятого триггеров и через четвертый элемент задержки - с первым входом шестого триггера и входом пятого элемента задержки, выходы четвертого пятого и шестого триггеров соединены соответственно с первыми входами третьего, четвертого и пятого ключей выход третьего ключа соединен с вторым выходом хронизатора и через третий счетчик - с вторым входом четвертого триггера, выход второго умножителя частоты подключен к вторым входам третьего, четвертого и пятого ключей, выход четвертого ключа соединен с первым входом элемента ИЛИ и через четвертый счетчик - с вторым входом пятого триггера, выход пятого ключа соединен с вторым входом элемента ИЛИ и через пятый счетчик - с вторым входом шестого триггера, выходы элемента ИЛИ и пятого элемента задержки соединены соответственно с третьим и пятым выходами хронизатора. Изобретение относится к электросвязи и может быть использовано в приемных устройствах систем передачи информации, использующих составные сигналы с избыточностью, формируемые на основе длинных и сверхдлинных помехоустойчивых кодов. Известно устройство для приема избыточных кодов в целом, состоящее из приемника и блока отождевствления сигналов в целом. Указанное устройство обеспечивает высокую помехоусто чивость приема и возможность обрабат вать сигналы с избыточностью ij . Недостатком устройства является сложность реализации блока отождествления сигналов, а для кодов с числом информационных символов больше 50 его реализация практически невозможна. Известно также устройство для при ема избыточных сигналов, содержащее приемник, короговый селектор, вторую решающую схему, блок сравнения мер похожести 2 . Недостатком данного устройства является низкая помехоустойчивость приема. Наиболее близким к предлагаемому по технической сущности является уст ройство для приема избыточной информации, содержащее хронизатор, демоду лятор, вход которого соединен с входом устройства, выход - с первым вхо дом вычитателя, входом первого порогового элемента и через первый блок памяти - с первым входом блока управ ления, выходы и второй, вход блока уп равления соединены соответственно с первыми входами и первым выходом пер вого блока регистров, второй выход которого соединен с выходом устройст на, выход первого порогового элемент соединен с вторым входом вычитателя, входом второго блока регистров и первым входом декодера, выход декоде ра соединен .с вторым входом первого блока регистров, выход вычитателя со единен с входом второго блока памяти выходы которого соединены соответственно с первыми входами блока усилителей , первые выходы и второй вход которого соединены соответственно с входами и выходом второго порогового элемента, вторые выходы блока усилителей и выходы второго блока регистров соединены соответственно с первы ми и вторыми входами сумматоров, выходы сумматоров соединены соответственно с входами третьего порогового элемента, выходы которого соединены соответственно с вторыми входами декодера з . Недостатком известного устройства является необходимость использования его при реализации большого количест ва блоков, связанных с аналоговой об работкой сигналов, что приводит к уменьшению точности преобразования входного сигнала с избыточностью, а следовательно, к уменьшению помехоустойчивости приема сообщений. Цель изобретения - повышение помехоустойчивости устройства путем уменьшения количества блоков аналоговой обработки на основе применения метода расширения. Указанная цель достигается тем, что в устрюйство для приема и обработки избыточных сигналов, содержащее демодулятор, первый вход которого объединен с входом хронизатора и подг ключен к входу устройства, выход д модулятора соединен с первыми входами вычитателя, первого блока памяти и через пороговый элемент - с вторым входом вычитателя, выход первого i блока памяти соединен с первым входом блока управления, первый, второй выходы и второй вход которого соединены соответственно с первым, вторым входами и первым выходом блока регистров, выход декодера соединен с третьим входом блока регистров, второй выход которого соединен с выходом устройства, первый, второй и третий выходы хронизатора соединены соответственно с вторыми входами демодулятора, первого блока памяти и с четвертым входом блока регистров, введены второй и третий блоки памяти, счетчики, логический блок, блок сравнения, элемент И, элемент ИЛИ, регистр, инвертор, выход порогового элемента соединен с первыми входами регистра и элемента ИЛИ, второй вход и выход элемента ИЛИ соединены соответственно с выходом регистра и первым входом инвертора, выход инвертора соединен 7 входом декоде- ра, выход вычитателя через первый блок памяти соединен с первым входом блока сравнения, аторой вход которого объединен с входом первого счетчика и подключен к первому выходу хронизатора, первый, второй выходы и третий вход блока сравнения соединены соответственно с первым, вторым входами и выходом второго блока памяти / выход первого счетчика и третий выход блока сравнения соединены соответственно с первым и вторым входами логического блока, выход которого соединен с первым входом второго счетчика, выходы второго счетчика соединены соответственно с входами элемента И, выход которого соединен с вторым входом инвертора, четвертый выход хронизатора соединен с вторыми входами второго счетчика и регистра. Блок управления содержит аналогоцифровой преобразователь, генератор, регистр, триггер, ключи, коммутатор, вычитатель, сумматоры, первые входы аналого-цифрового преобразователя, генератора и первого ключа объединены и подключены к первом/ входу блок управления, выход аналого-цифрового преобразователя соединен с первыми входами регистра и второго ключа, вы ход генератора соединен с вторыми входами аналого-цифрового преобразователя и регистра, выход регистра соединен с первым входом третьего ключа, выход первого ключа соединен с первым входом триггера и первым выходом блока управления, выход-триг гера соединен с вторым входом первого ключа, вход коммута.тора соединен с вторым входом блока управления, первый и второй выходы коммутатора соединены соответственно с вторыми входами второго и третьего ключей, выходы которых соединены соответственно через первый и второй сумматоры с первым и вторым входами вычитателя, выход вычитателя соединен с вторыми входами триггера, генератора и вторым выходом блока управления. Первый блок памяти, содержит элемент памяти и элемент задержки, первый вход и выход элемента памяти соединены соответственно с входом и вы ходом блока памяти, выход и второй вход элемента памяти соединены соответственно с входом и выходом элемен та задержки. Логический блок содержит ключи, триггер, элемент-ИЛИ, элемент задерж ки, первые-входы первого ключа и эле мента ИЛИ соединены соответственно с первьви и вторым входами логического блока, выход первого ключа соединен первым входом второго ключа и с выходом логического блока,выход и второй вход второго ключа соединены соо ветственно с первыми входами первого второго триггеров, входом элемента з держки и выходом первого триггера, вы ход элемента задержки соединен с вто рыми входами первого и второго тригг ров, выход второго триггера соединен с вторым входом элемента ИЛИ, выход которого соединен с вторым входом пе вого ключа. Блок сравнения содержит ключи, сче чик, вычитатель, элементы ИЛИ, элемен задержки, триггер, первые входы пер вого ключа и вычитателя соединены соответственно с первым и третьим -входа ми блока сравнения, выход вычитателя соединен с первыми входами первого и второго элементов ИЛИ и с третьим вы ходом блока сравнения, выход первого элемента.ИЛИ соединен с первым входом второго ключа, выходы второго элемента ИЛИ и второго ключа соединены соот ветственно с первым и вторым выходами блока сравнения,выход первого ключа соединен с вторыми входами вычитателя и второго ключа, второй вход первого ключа объединен с входом счетчика и первым входом третьего ключа и подключен к второму входу блока сравнения, выход третьего ключа соединен с вторым входом первого элемента ИЛИ и через элемент задержки - с первым входом триггера, выход триггера соединен с вторым входом третьего ключа, выход счетчика соединен с вторыми входами триггера и второго элемента ИЛИ. Хронизатор содержит блок синхронизации, умножители частоты, элементы задержки, счетчики, ключи, триггеЕял, элемент ИЛИ, вход блока синхронизации соединен с первыми входами первого, второго ключей и через первый умножитель частоты - -с первым входом ..третьего ключа и входом второго умножителя частрты, второй вход и выход первого ключа соединены соответственно с выходом первого триггера и входами первого триггера и первого элемента задержки, выход первого элемента задержки соединен с первым входом второго триггера и через второй элемент задержки - с первым входом третьего триггера и входом третьего элемента задержки, выходы второго и третьего триггеров соединены соответственно с вторыми входами второго и третьего ключей, выход вторюго ключа соединен с первым выходом хронизатора и через счетчик - с вторым входом второго триггера, выход третьего ключа соединен с. четвертым выходом хронизатора и через второй счетчик - с вторым входом третьего триггера, выход третьего элемента задержки соединен с первыми входами четвертого, пятого триггеров и через четвертый элемент задержки - с первым входом шестого триггера и входом пятого элемента задержки, выходы четвертого, пятого и шестоготриггеров соединены соответственно с первыми входами третьего, четвертого и пятого ключей, выход третьего ключа соединенн с вторым выходом хронизатора и через третий счетчик - с вторым входом четвертого триггера, выход второго умножителя частоты подключен к вторым входам третьего, четвертого и пятого ключей, выход четвертого ключа соединен с первым входом элемента ИЛИ и через четвертый счетчик - с вторым входом пятого триггера, выход пятого ключа соединен с вторым входом элемента ИЛИ и через пятый счетчик - с вторым входом шестого триггера, выходы элемента ИЛИ и пятого элемента задержки соединены соответственно с третьим и пятым выходами хронизатйра. На фиг.1 приведена структурная схема устройства; на фиг. 2 - функциональная схема блока управления выдачей информации; на фиг.З - функциональная схема блока памяти; на фиг.4 функциональная схема логического блока; на фиг.5 - функциональная схема блока сравнения;на фиг.б - функциональная схема хронизатора. Устройство содержит демодулятор 1 пороговый элемент 2, декодер 3, блок 4 регистров, аналоговый блок 5 буфер ной памяти, блок 6 управления выдачей информации, .вычитатель 7, анализатор 8, блок 9 коррекции, регистр 10 сдвига, элемент ИЛИ 11, управляемый инвертор 12, хронизатор 13, двоичный суммирующий счетчик 14, логический блок 15, блок 16 памяти,блок 17 сравнения, блок 6 управления выдачей сопеожит (Фигг2) элемент 18 памяти, двоичный вычитающий счетчик 19, элемент И 20, аналого-цифровой преобразователь 21, коммутатор 22, ключ 23, сумматор 24, регистр 25 сдвига, ключ 26, сумматор 27, вычитатель 28, генератор ,29 тактовых импульсов, ключ 30 и триггер 31, блок 16 памяти содержит (фиг.З) элемент 32 памяти, элемент 33 задержки, логический блок 15 содержит (фиг.4) ключи 34 и 35, элемент 36 задержки, триггер 37, триггер 38 и элемент ИЛИ 39, блок 17 сравнения содержит (фиг.5) ключ 40, счетчик 4 ключ 42, элемент 43 задержки, триггер 44, ключ 45, элемент ИЛИ 46, вычитатель 47 и элемент ИЛИ 48, хро низатор 13 содержит блок 49 синхронизации, умножитель 50 и 51 частоты блок 52 вьщеления первого тактового импульса, содержащий триггер 53 и ключ 54, логический блок 55, содержа щий элемент 56 задержки, счетчиА 57 триггер 58, и ключ 59, логический блок 60, содержащий элемент 61 задержки, счетчик 62, триггер 63 и ключ 64, логический блок 65, содержа щий элемент 66 задержки, триггер 67 счетчик 68, ключ 69, триггер 70, счетчик 71 и ключ 72, логический блок 73, содержащий элемент 74 задержки, триггер 75, ключ 76 и счетчик 77, элемент ИЛИ 78 и элемент 79 задержки. Пороговый элемент 2 преобразует входной аналоговый сигнал в выходной двоичный сигнал, например, по следую щему правилу. Если входной аналоговы сигнал больше некоторого порогового значения, то на выходе порогового элемента появляется единичный сигнал заданной величины. В противном случа на его выходе - нулевой сигнал. Декодер 3 входную двоичную кодову комбинацию отождествляет с выходной разрешенной двоичной кодовой комбинацией, в нем реализуется соответствующая процедура исправления ошибок (например, мажоритарное декодирование, пороговое и т.п.). В блоке 4 регистров памяти записываются и хранятся двоичные разреше ные кодовые комбинации. По управляющему сигналу из блока 6 управления вьадачей информации разрешенные комбинации считываются (с регенерацией) в блок 6, по другой команде одна из разрешенных комбинаций считывается на выход устройства. Объем памяти данного блока - два двоичных регистра. В блок 6 управления выдачей информации подается аналоговый составной сигнал с избыточностью (последовательно) разрешенные двоичные кодовые комбинации. С выхода блока 5 аналоговый сигнал проходит через открытый ключ 30 на вход блока 4, разрешая в нем считывание разрешенных двоичных кодовых комбинаций в блок 6. При этом меняется состояние триггера 31 и ключ 30 закрывается. Во время действия первого входного аналогового сигнала с небольшой задержкой на вход коммутатора 22 из блока 4 поступает первый двоичный символ (сигнал) первой разрешенной кодовой комбинации. Первый аналоговый сигнал запускает генератор 29 iактовых импульсов. Его тактовая частота вт раз (где m разрядность выходного сигнала кодовой комбинации аналого-цифровс го преобразователя 21 превышает тактовую частоту поступления входных аналоговых сигналов). Первый аналоговый сигнал подается в аналого-цифровой преобразователь 21, .в котором преобразуется в т-значную двоичную кодовую комбинацию. Эта комбинация с помощью выходных так говых кмпулъсов генератора 29 записывается в тп-разрядный двоичный регистр 25 сдвига и . подается через ключ 23 на вход cyivwaтора 24 двоичных т-разрядных чисел. Коммутатор 22 двоичные символы первой разрешенной кодовой комбинации . направляет на управляющий вход ключа 23. Выходы коммутатора - потенциальные. Это означает, что состояние ключа 23 во вреь;л присутствия его на входе символов значной двоичной комбинации определяется первым символом первой разрешекной кодовой ком-, бинации. Если первый символ первой разраиенной кодовой комбинации является нулевым, то на выход ключа шзначная комбинация не проходит. В противном случае, когда первый символ первой разрешенной комбинации является единичным, ключ 23 открыт и ш-значная двоичная комбинация подается в сумматор 24. Далее на вход блока 6 поступает второй символ аналоговой комбинации Гвторой аналоговый сигнал J, При этом с выхода блока 4 через коммутатор 22 на управляющий вход ключа 23 подается второй двоичный символ первой резрешенной комбинации. Второй аналоговый сигнал с помощью аналого-цифрового преобразователя 21 преобразуется в т-значную двоичную кодовую комбинацию;

Она так же, как и первая, записывается в регистр 25 и подается на вход ключа 23, Если второй символ первой разрешенной кодовой комбинации явля ется единичным, то ключ 23 открыт и вторая т-значная двоичная комбинация поступает на вкод сумматора 24. Если второй символ является кулевым, то ключ 23 закрыт и т эначная двоичная комбинация на сумматор 24 не подается. Аналогичным образом обрабатывают Ю ся все входные аналоговые сигналы,По окончании обработки последнего, п-го аналогового сигнала в регистре 25 будет записана двоичная копия составного сигнала с избыточностью. Далее 15 на вход коммутатора 22 из блока 4 поступает (также последовательно) вторая разрешенная двоичная кодовая комбинация. С помощью коммутатора 22 ее символы подаются на управляющий вход 20 ключа 26. Прюцесс управления ключом 26 аналогичен процессу управления ключом 23. Во время присутствия на управляющем входе ключа 26 первого двоичного символа второй разрешенной 25 кодовой комбинации из регистра 25 считывается т-значная двоичная кодовая комбинация, соответствующая первому аналоговому сигналу. Во время

присутствия на управляющем входе ключа 26 второго двоичного символа второй разрешенной комбинации из регистра 25 считывается т-значная двоичная комбинацияf соответствующая второму аналоговому элементарному сигналу, и т.д. После считывания из 35 блока 4 в блок б всех символов второй разрешенной комбинации ключи 23 и 26 закрыты, в сумГЛаторах 24 и 27 в двоичном коде будут вычислены значения степеней близости между аналого- 40 вым избыточным сигналом и соответственно первой и второй разрешенными кодовыми комбинациями. Двоичные коды степеней близости в вычитателе 28 вычитаются. Если в результате вычи- 45 тания окажется, что двоичный код сумматора 24 превышает двоичный код сумматора 27, то на выходе вычитателя 28 формируется положительный сигнал. В противном случае - отрицатель-.,, ный. Выходной сигнал вычитателя 28 подается в блок 4, в котором в зависимости от полярности выходного сигнала вычитателя на выходе устройства

считывается или первая или вторая разрешенная кодовая комбинация (для 55 этого считывания из хронизатора .13 в соответствующий момент времени

подаются тактовые импульсы). Выходной сигнал вычитателя 28 также возвращает -в исходное состояние триггер 60 31, открывает ключ 30 и прекращает функционирование генератора 29 Блок 6 управления выдачей информации готов к обработке следующего составнот избыточного сигнала,

в анализаторе 8 с выхода блока 7 на вход элемента 32 памяти подается аналоговый сигнал, а на вход счетчика 14 и блока 17 сравнения синхронного поступают тактовые импульсы с выхода блока 13. Первый тактовый им пульс устанавливает счетчик 14 в единичное состояние, двоичный код которого через открытый в исходном состоянии ключ 34 подается на выход анализатора 8. Выходной сигнал ключа 34 через открытый в исходном состоянии ключ 35 переводит триггеры 38 и 37 из исходных единичных состояний в нулевые, закрывая тем самым соответственно ключи 34 и 35. Сигнал с выхода ключа 35 подается также на злемент 36 задержки и устанавливает триггеры и ключи блока 15 в исходное состояние После того, как триггер 38 переведен в нулевое состояние, ключ 34 управляется выходным сигналом вычитателя 47 блока 17. Тактовый импульс открывает ключ 40, изменяя состояние счетчика 41 на единичное и через открытый в исходном состоянии ключ 42, элемент ИЛИ 46 открывает ключ 45. Этот же тактовый импульс через элемент 43 задержки соответствующий момент времени переводит триггер 44 из исходного единичного состояния в нулевое, закрывая ключ 42. Первый аналоговый сигнал, записавшись в элемент 32 памяти, с его потенциального выхода через открытый ключ 40 подается на первый вход вычитателя 47 и через открытый ключ 45 записывается во второй элемент 8 памяти. С потенциально го выхода элемента 18 памяти аналоговый сигнал подается на второй вход вычитателя 47. Так как входные сигналы вычитателя 47 равны между собой, на его выходе не формируется управляющий сигнал. Далее сбрасывается информация в блоке 32 выходным сигналом элемента 33 задержки и в анализатор 8 поступают второй аналоговый сигнал с выхода блока 7 и второй тактовый импульс с выхода блока 13, который за записывается в счетчики 14 и 41, изменяя их двоичный код (емкость счетчика 14 равна емкости счетчика 41, т.е. равна п двоичным символам).Второй тактов1ай импульс открывает ключ 40, через который второй аналоговый сигнал, записанный в элемент 32 памяти с потенциального выхода элемента 32 памяти,подается на первый вход вычитателя 47, на его второй вход с потенциального выхода элемента 18 памяти подается первый аналоговый сигнал. Рассмотрим случаи различного соотношения между величинами амплитуд первого и второго аналоговых сигналов. Случай первый. Второй аналоговый сигнал не больше (меньше или равен) первого. При этом уп-, равляющий сигнал на выходе вычитателя 47 не формируется. Чеь-еэ определенное время элемент 32 обнуляется выходным сигналом, элемент 33 задержки и анализатор 8 готов к обработке следующего, третьего аналогового сигнала так же, как и второго. Случай второй. ВТорой аналоговый сигнал больше первого. В этом случае на выходе вычитателя 47 формируется управляющий сигнал, по которому выполняют ся следующие операции: в блоке 15 от крывается ключ 34, выдавая на выход анализатора двоичный код состояния счетчика 14, в блоке 17 через элемен ИЛИ 48 обнуляется элемент 18 памяти и открывается ключ 45, через который второй аналоговый сигнал с потенциального выхода элемента 32 через открытые ключи 40 и 45 записывается в элемент 18 памяти. После этого вхо дные сигналы вычитателя 47 .вычитаются один из другого и с его выхода снимается управляющий сигнал (соответствующей полярности). В соответствующий момент времени обнуляется элемент 32 памяти и анализатор 8 готов к обработке следующего аналогового сигнала. Подобным образом обрабатываются все выходные аналоговые сигнсшы блока 7. После обработки последнего п-го аналогового сигнала на выходе блока 36 появляется сигнал. по которому триггеры 37 и 38 устанавливаются в исходное состояние (единичное) , открывав; ключи 34 и 35. В это же время появляется сигнал переполнения на выходе счетчика 41, по которому тригпр 44 устанавливается в исходное единичное состояние, открывая ключ 42, и элемент 18 памяти обнуляется. Анализатор 8 готов к обработке следующего составного сигнала с избыточностью. Блок 9 коррекции формирует управля1т ий сигнал, запускающий инвертор 12. На вход данного блока поступает двоичньтй код номера аналогового сигнала, записанного в блоке 18 памяти после обработки всех входных элементарных сигналов. В счетчике 19 записывается код наименьиюго достоверного аналогового сигнала. На другой вход блока 9 коррекции подаются импульсы считывания двоичных сигналов. Количество двоичных ячеек в счетчике 19 превышает количество ячеек счетчика 14 на одну. При считывании из регистра 10 двоичной кодовой комбинации импульсы считывания из блока 13 поступают и-на вход счетчика 19, уменьшая его двоичный код. В тот момент времени,когда на входе инвертора 12 появится двоичный символ, соответствующий наименее достоверному аналоговому сигналу, состояние счетчика 19 станет нулевым. Этот факт будет зафиксирован с помощью элемента И 20, на выходе которого будет , лсформирован управляющий сигнал, по которому блок 12 осуществит инверсию двоичного сигнала, соответствующего наименее достоверному аналоговому сигналу. При отсутствии управляющего сигнала на входе управляемого инвертора 12 входные двоичные сигналы проходят на его выход беэ изменения. При поступлении на управляющий вход сигнала входной двоичный сигнал этого блока инвертируется. Хронизатор 13 обеспечивает вьоделение тактовой частоты и фиксирует момент прихода первого элементарного сигнала, входящего в состав избыточного сигнала, на его выходе формируются тактовые импульсы. На вход хронизатора подаются входные элементарные сигналы. .На его выходе формируются тактовые импульсы, следующие с тактовой частотой, определяемой скоростью манипуляции (модуляции). С помощью умножителей 50 и 51 формируют тактовые импульсы вспомогательных частот. Блок 52 выделяет первый тактовый импульс. Элемент 56 задержки задерживает первый тактовый импульс на определенное время, после чего он поступает на вход элемента 61 задержки, а также на вход триггера 58, изменяя состояние последнего. Ключ 59 открывается и через него на управляющий вход аналогового демодулятора 1 и на вход анализатора 8 пропускают п тактовых импульсов, синфазных с выходными сигналами блока 7, который практически является безынерционным. Одновременно число выходных импульсов ключа 59 подсчитывается с помощью счетчика 57. Как только оно станет равным п, на выходе счетчика формируется управляющий сигнал, возвращающий триггер 58 в исходное нулевое состояние, закрывая ключ 59. Выходной сигнал элемента 56 задержки проходит через элемент 61 задержки и через триггер 63, открывая . ключ 64, через который на блоки 9 и 10 проходит п выходных импульсов ум- ножителя 50. Последний импульс вызывает переполнение счетчика 62, в результате чего его выходной сигнал через триггер 63 закрывает ключ 64,прекращая подачу тактовых импульсов. Выходной сигнал элемента 61 задержки через элемент 66 задержки подается на триггердл 67 и 70, изменение состояния которых приводит к открыванию соответственно ключей 69 и 72. Выходные тактовые импульсы умножителя частоты 51 через ключ 69 подаются на считывающий вход блока 5, а через ключ 72 и элемент ИЛИ 78 - на считывающий вход блока 4. Счетчик 68 разрешает выдачу в блок 5 только п тактовых импульсов/ после чего сбрасывает триггер 67 в исходное состояние и закрывает ключ 69. Счетчик 71 разрешает вьадачу в блок Ч 2п тактовых импульсов {на считывание двух разрешенных п-значных двоичных кодовых комбинаций), после чего импульсом пероЛолнения сбрасывает триггер 70 и закрывает ключ 72, Выходной сигнал элемента 66 задержки подается также на вход элемента 74 задержки, появляясь на выходе которого соответствугощий момент времени, он через триггер 75 открывает ключ 76 и разрешает прохождение п тактовым импуль сам через элемент ИЛИ 78 с выхода умножителя 51 частоты на считываквдий вход блока 4i Прекращается выдача тактовых импульсов по импульсу переполнения счетчика 77, который закрывает ключ 76. Выходной сигнал элемента 74 задержки подается также на . элемент 79 задержки. Выходной сигнал элемента 79 задержки является сигналом установки в исходное состояние всех блоков устройства (цепи сброса не показаны). Устройство для приема и обработки избыточных сигналов по методу расширения работает следующим образом. Входной. подверженный воздействию помех в канале связи, составной сигнал с .избыточностью поступает на вход аналогового демодулятора 1. Для определенности используется последователь ная передача элементарных сигналов, входящих в состав избыточного сложного сигнала. Тогда входные сигналы последовательно подаются на вход хронизатора 13, в котором формируются управляющие сигналы, и в соответствии с используемой процедурой обработки аналоговым демодулятором 1 элементарных сигналов в тактовые моменты времени (на выходе блока 1 формируются аналоговые элементарные сигналы, которые записываются в блок 5 буферной памяти, поступают на вход вычитателя 7 и на вход порогового элемента 2). После ний преобразует их в выходные двоичные сигналы, запоминаемые в двоичном регистре 10 и через элемент ИЛИ 11 поступающие через открытый инвертор 12 в декодер 3. С помощью декодера 3 входная двоичная кодовая комбинация, соответствующая составному аналоговому сигналу после его преобразования с помощью порогового элемента 2 отождествляется с выходной разрешенной двоичной кодовой комбинацией, которая Запоминается в блоке 4. Соответственно в двоичном регистре 10,будут нака.пливаться сигналы по мере преобразования составного аналогового, сигнала в двоичные символы. На выходе вычитателя 7 формируются разностные сигналы, которые с помощью импульсов записи из блока 13, поступающих в анализатор 8, записываются в последний. С помощью анализатора 8 определяют наименьший аналоговый сигнал, поступающий с выхода блока 7, а также двоичный код номера этого сигнала, который с вьл-хода анализатора 8 поступает в блок 9 коррекции, 8блоке 9 код номера определяет начальное состояние двоичного вычитающего счетчика 19. После этого с помощью соответствующий выходных тактовых импульсов блока 13 последовательно выводят двоичную кодовую комбинацию из регистра 10. Этими же тактовыми импульсами, подавая их на вход блока коррекции, уменьшают двоичный код счетчика 19. Как только на входе инвертора 12, через который без изменения проходят на вход декодера 3 двоичные сигналы с выхода регистра 10, появится двоичный сигнал, сформированный из наименее достоверного аналогового сигнала, с выхода блока 9коррекции на управляющий вход инвертора 12 поступает управляющий сигнал, по которому инвертируется входной двоичный сигнал. Последующие двоичные сигналы инвертор не инвертирует. Таким образом, в декодер 3 будет считана двоичная кодовая комбинация, отличающаяся от предыдущей в разряде, соответствующем наименее достоверному аналоговому символу. Эту двоичную кодовую комбинацию в декодере 3 преобразуют в соответствующую разрешенную кодовую двоичную комбинацию, которая также запоминается в блоке 4. После Э.ТОГО в арифметический блок 6 из блока 5 буферной памяти по считывающим из блока 13 сигналам - тактовы.м импульсам последовательно поступает аналоговый составной сигнал с избыточностью, а из блока 4- разрешенные двоичные кодовые комбинации. В блоке 6 осуществляется вычисление степеней близости каждой из разрешенных двоичных кодовых комбинаций к аналоговому составному сигналу с избыточностью, которые затем сравнивают между собой. По управляющему сигналу, выдаваемому из блока 6 в блок 4, из последнего на выход устройства считывают ту разрешенных кодовых комбинаций, для которой степень близости больше. Преимущество изобретения по сравнению с базовым (прототипом) заключается в том, что предлагаемое устройство содержит меньше аналоговых элементов. Это позволяет повысить помехоустойчивость устройства.

1г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и обработки избыточных сигналов | 1983 |

|

SU1152017A2 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1983 |

|

SU1152016A1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

| Устройство для приема избыточных сигналов | 1989 |

|

SU1695353A1 |

| Устройство для приема избыточной информации | 1984 |

|

SU1167638A1 |

| Устройство для мажоритарного декодирования в целом | 1984 |

|

SU1243101A1 |

| Устройство для приема сигналов с избыточностью | 1983 |

|

SU1128281A1 |

| Адаптивное устройство для обработки избыточной информации | 1982 |

|

SU1062752A1 |

| Телеметрическая система со сжатием информации | 1991 |

|

SU1837349A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1193713A1 |

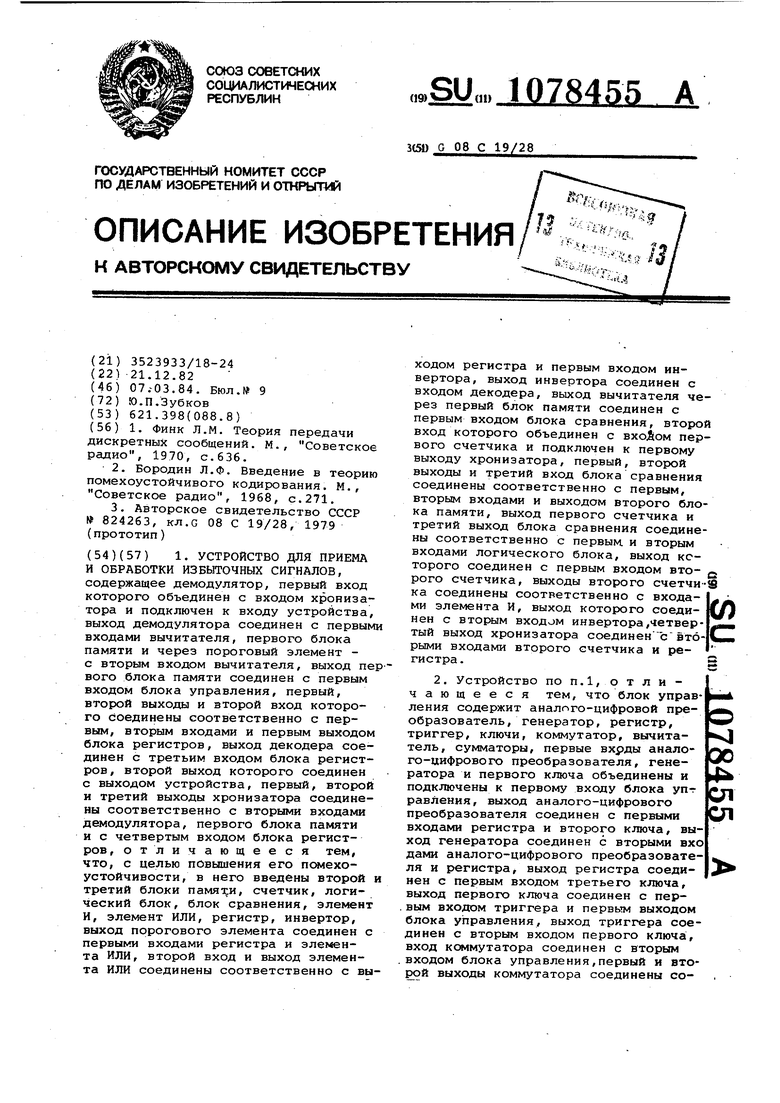

1, УСТРОЙСТВО ДЛЯ ПРИЕМА И ОБРАБОТКИ ИЗБЫТОЧНЫХ СИГНАЛОВ, содержащее демодулятор, первый вход которого объединен с входом хронизатора и подключен к входу устройства, выход демодулятора соединен с первыми входами вычитателя, первого блока памяти и через пороговый элемент с вторым входом вычитателя, выход первого блока памяти соединен с первым входом блока управления, первый, второй выходы и второй вход которого соединены соответственно с первым, вторым входами и первым выходом блока регистров, выход декодера соединен с третьим входом блока регистров, второй выход которого соединен с выходом устройства, первый, второй и третий выходы хронизатора соединены соответственно с вторыми входами демодулятора, первого блока памяти и с четвертым входом блока регистров , отличающееся тем, что, с целью повышения его nca iexoустойчивости, в него введены второй и третий блоки памяти, счетчик, логический блок, блок сравнения, элемент И, элемент ИЛИ, регистр, инвертор, выход порогового элемента соединен с первыми входами регистра и элемента ИЛИ, второй вход и выход элемента ИЛИ соединены соответственно с выходом регистра и первым входом инвертора, выход инвертора соединен с входом декодера, выход вычитателя через первый блок памяти соединен с первым входом блока сравнения, второй вход которого объединен с входом первого счетчика и подключен к первому выходу хронизатора, первый, второй выходы и третий вход блока сравнения соединены соответственно с первым, вторым входами и выходом второго блока памяти, выход первого счетчика и третий выход блока сравнения соединены соответственно с первык и вторым входами логического блока, выход которого соединен с первым входом вто- Q рого счетчика, выходы второго счетчи-8 ка соединены соответственно с входа(Л ми элемента И, выход которого соединен с вторым входом инвертора,четвертый выход хронизатора соединен с вторыми входами второго счетчика и регистра. 2. Устройство по п.1,о т л и чающееся тем, что блок управления содержит аналого-цифровой преобразователь, генератор, регистр, vl триггер, ключи, коммутатор, вьлчитатель, сумматоры, первые вхрды анало00 го-цифрового преобразователя, гене4;: ратора и первого ключа объединены и подключены к первому входу блока упт ел ел равления, выход аналого-цифрового преобразователя соединен с первыми входами регистра и второго ключа, выход генератора соединен с вторыми вхо дами аналого-цифрового преобразователя и регистраj выход регистра соединен с первым входом третьего ключа, выход первого ключа соединен с пер. вым входом триггера и первьтм выходом блока управления, выход триггера соединен с вторым входом первого ключа, вход коммутатора соединен с вторым входом блока управления,первый и второй выходы коммутатора соединены со

S5

5

Лг

«x

0ut.2

W

32

/7

I

JJ

0ut3

/7

f6

4ff

J

ЛГ

18

Г 7

Г8

4ff

re

S

b

3

2

Фог.5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Теория передачи дискретных сообщений | |||

| М., Советское радио, 1970, с.636, 2, Бородин Л.Ф | |||

| Введение в теорию помехоустойчивого кодирования | |||

| М., Советское радио, 1968, с.271, 3 | |||

| Устройство для приема избыточнойиНфОРМАции | 1979 |

|

SU824263A1 |

Авторы

Даты

1984-03-07—Публикация

1982-12-21—Подача