СО

со сп

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1986 |

|

SU1370654A1 |

| Цифровой преобразователь координат | 1979 |

|

SU842801A1 |

| Устройство для умножения | 1979 |

|

SU773622A1 |

| Умножитель частоты | 1984 |

|

SU1179334A1 |

| Многоканальное устройство контроля температурных режимов инкубаторов | 1983 |

|

SU1157528A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСОВ | 1979 |

|

SU826343A1 |

| Умножитель частоты периодических импульсов | 1980 |

|

SU935956A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1001098A1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ УРОВНЯ СЫПУЧИХ МАТЕРИАЛОВ | 1998 |

|

RU2138027C1 |

| КОРРЕЛЯЦИОННАЯ ИЗМЕРИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2007753C1 |

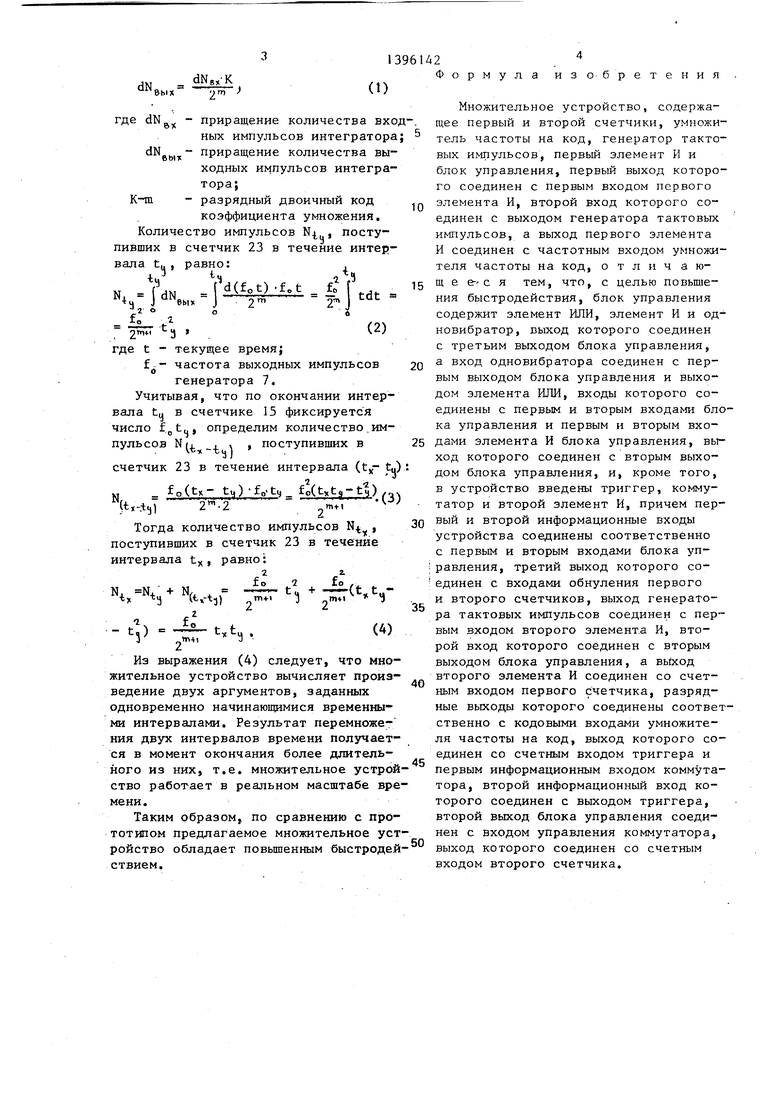

Изобретение относится к вычислительной технике и может быть использовано для построения специализирован ных умножителей;временных интервалов. Цель изобретения - повышение быстродействия. Множительное устройство включает в себя блок 1 управления, входы которого соединены с информационными входами 2,3, генератор 7 тактовых импульсов, первый элемент И 8, второй элемент И 11, умножитель 14частоты на код, первый счетчик 15с входом 16 обнуления и счетным входом 17, триггер 18, коммутатор 19 с информационными входами 20, 21 и управляющим входом 22 и второй счетчик 23 с входом 24 обнуления и счетным входом 25 с соответствующими связями. Блок 1 управления содержит элемент ШШ, элемент И и одновибра- тор. Устройство вычисляет произведение двух аргументов, заданных одно- в ременно начинанщимися временными интервалами. Результат умножения формируется в момент окончания более длительного интервала времени. 2 ил. С S (Л

30

4: Ю

. 1

Изобретение относится к вычислительной технике и может быть использовано для построения специализированных умножителей временных интерва лов.

Цель изобретения - повышение быстродействия.

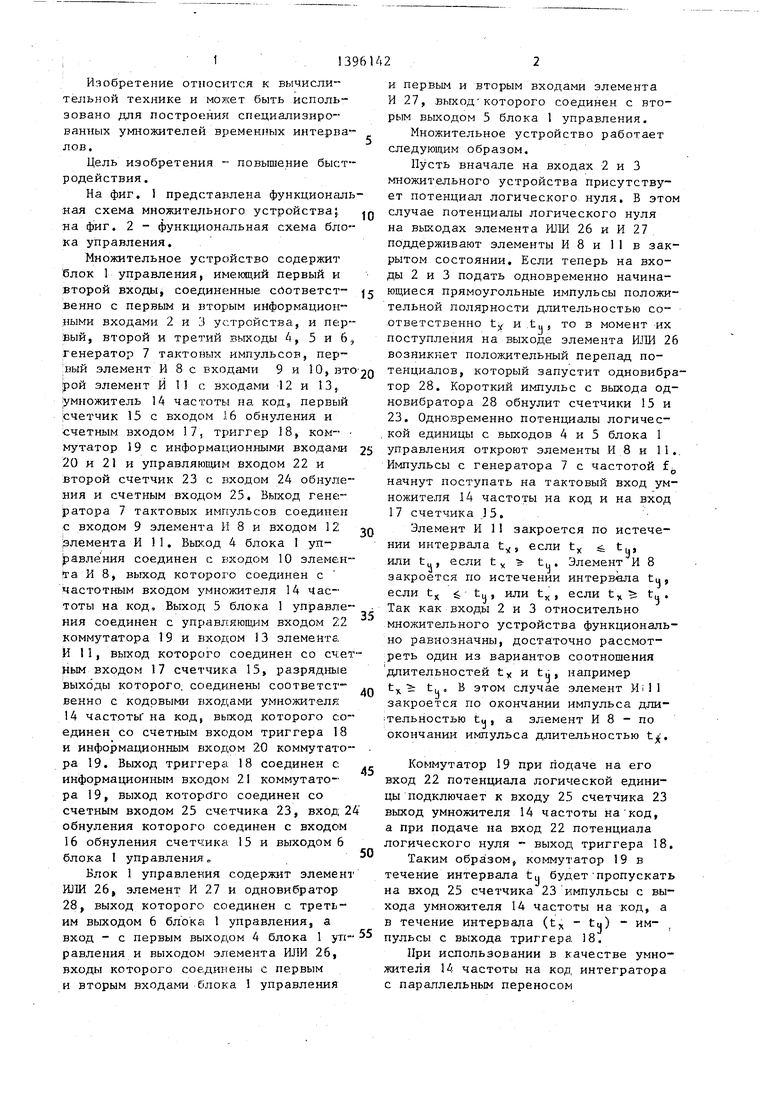

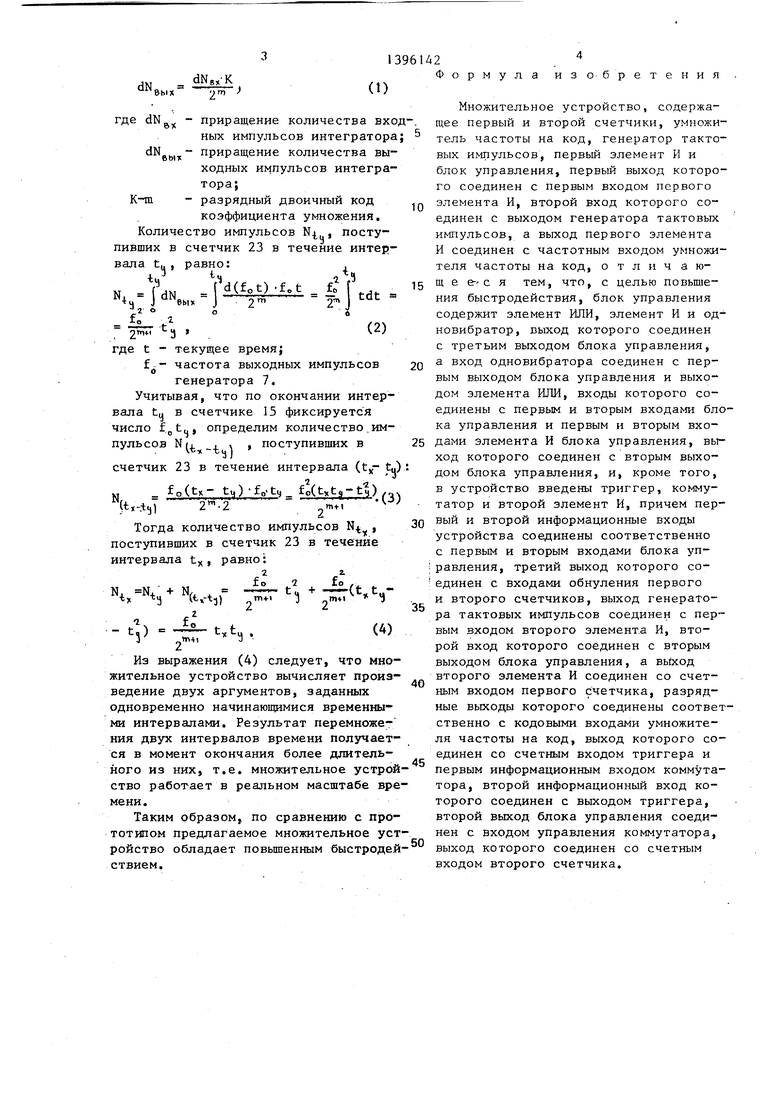

На фиг. 1 представлена функционгшь ная схема множительного устройства} на фиг. 2 - функцион шьная схема блока управления.

Множительное устройство содержит блок 1 управления, имеющий первый и второй входы, соединенные сОответст- венно с первым и вторым информационными входами 2 и 3 устройства, и первый, второй и третий выходы 4, 5 и 6,, генератор 7 тактовых импульсов, пер)

:вый элемент И 8 с входами 9 и 10,)зто-20 тенциалов, который запустит одновибратор 28. Короткий импульс с выхода од- новибратора 28 обнулит счетчики 15 и 23. Одновременно потенциалы логической единицы с выходов 4 и 5 блока 1 управления откроют элементы И 8 и 11.. Импульсы с генератора 7 с частотой f, начнут поступать на тактовый вход умножителя 14 частоты на код и на вход 1 7 счетчика J 5,

Элемент И 11 закроется по истече25

30

35

;рой элемент И 11 с входами 12 и 13,, умножитель 14 частоты на код, первый счетчик 15 с входом 16 обнуления и счетным входом 17, триггер 18, ком- мутатор 19 с информационными входами 20 и 21 и управляющим входом 22 и второй счетчик 23 с входом 24 обнуления и счетным входом 23, Выход генератора 7 тактовых импульсов соединен с входом 9 элемента И 8 и входом 12 Элемента И 11. Выход 4 блока 1 уп- нии Давления соединен с входом 10 элемен- или Та И В, вьгход которого соединен с частотным входом умножителя 14 частоты на код. Выход 5 блока 1 управления соединен с управляющим входом 22 коммутатора 19 и входом 3 элемента ИМ, выход которого соединен со счет ным входом 17 счетчика 15, разрядные выходы которого, соединены соответственно с кодовыми входами умножителя 14 частоты на код, выход которого соединен со счетным входом триггера 18 и информационным входом 20 коммутатора 19. Выход триггера 18 соединен с информационным входом 21 коммутатора 19, выход которого соединен со счетным входом 25 счетчика 23, вход 24 обнуления которого соединен с входом 16 обнуления счетчика. 15 и выходом 6 блока 1 управления

Блок 1 управления содержит элемент ИЛИ 26, элемент И 27 и одновибратор 28, выход которого соединен с третьим выходом 6 блока 1 управления, а вход - с первым выходом 4 блока 1 55 равления и выходом элемента ШШ 26, входы которого соединены с первым и вторым входами блока 1 управления:

интервала если

-т( S

если t

X -y Элемент И 8

tu, если t у t. закроется по истечении интервела t

если t 6 ty

-X

если tx 5 t

Г

Г

40

45

50

-X t: -U ) ИЛИ

Так как входы 2 и 3 относительно множительного устройства функционально равнозначны, достаточно рассмотреть один из вариантов соотношения длительностей ty и t, например t Ъ ti, В этом случае элемент И111 закроется по окончании импульса дли- тельностью tu, а элемент И 8 - по окончании и шyльca длительностью .

Коммутатор 19 при подаче на его вход 22 потенциала логической единицы подключает к входу 25 счетчика 23 выход умножителя 14 частоты на код, а при подаче на вход 22 потенциала логического нуля выход триггера 18.

Таким образом, коммутатор 19 в течение интервала tu будет пропускать на вход 25 счетчика 23 импульсы с выхода умножителя 14 частоты на код, а в течение интервала (t - tu) - импульсы с выхода триггера 18.

При использовании в качестве умножителя 14 частоты на код интегратора с параллельным переносом

и первьм и вторым входами элемента И 27, вькод-которого соединен с вторым выходом 5 блока 1 управления.

Множительное устройство работает следующим образом.

Пусть вначале на входах 2 и 3 множительного устройства присутствует потенциал логического нуля, В этом случае потенциалы логического нуля на выходах элемента ИЛИ 26 и И 27, поддерживают элементы И 8 и 11 в закрытом состоянии. Если теперь на входы 2 и 3 подать одновременно начинающиеся прямоугольные импульсы положительной полярности длительностью соответственно ty и.Ьц, то в момент их поступления на выходе элемента ШШ 26 возникнет положительный перепад по5

нии или

5

интервала если

-т( S

если t

X -y Элемент И 8

tu, если t у t. закроется по истечении интервела t

если t 6 ty

-X

если tx 5 t

Г

Г

0

5

0

-X t: -U ) ИЛИ

Так как входы 2 и 3 относительно множительного устройства функционально равнозначны, достаточно рассмотреть один из вариантов соотношения длительностей ty и t, например t Ъ ti, В этом случае элемент И111 закроется по окончании импульса дли- тельностью tu, а элемент И 8 - по окончании и шyльca длительностью .

Коммутатор 19 при подаче на его вход 22 потенциала логической единицы подключает к входу 25 счетчика 23 выход умножителя 14 частоты на код, а при подаче на вход 22 потенциала логического нуля выход триггера 18.

Таким образом, коммутатор 19 в течение интервала tu будет пропускать на вход 25 счетчика 23 импульсы с выхода умножителя 14 частоты на код, а в течение интервала (t - tu) - импульсы с выхода триггера 18.

При использовании в качестве умножителя 14 частоты на код интегратора с параллельным переносом

dN

вых

dNg. K 2m .

dN

выи

где dN - приращение количества вхо ных импульсов интегратора приращение количества выходных импульсов интегратора;

разрядный двоичный код коэффициента умножения. Количество импульсов N , поступивших в счетчик 23 в течение интервала tц, равно:

К-т

Ч

NI

:г о о

d(fot) -fot

Ijtdt

(2)

f: .

, 2

где t - текущее время;

частота выходных импульсов

генератора 7.

Учитывая, что по окончании интервалачисло

U -J -

в

ty в счетчике 15 фиксируется

fpty, определим количество импульсов N , , , поступивших

счетчик 23 в течение интервала ( tu

3

N

fo(tx- tij)-fp-ty f;(txts-t4)

,m-n

(tj-.-tij)

Тогда количество импульсов , поступивших в счетчик 23 в течение

интервала t, равно:

2

N, N.: + N,,

a.

Ц)

-3

fo

,№1+1

Из выражения (4) следует, что множительное устройство вычисляет произведение двух аргументов, заданных одновременно начинающимися временными интервалами. Результат перемноже- НИН двух интервалов времени получается в момент окончания более длительного из них, т.е. множительное устройство работает в реальном масштабе времени.

Таким образом, по сравнению с про30 вый и второй информационные входы устройства соединены соответственн с первым и вторым входами блока уп :равления, третий выход которого со единен с входами обнуления первого и второго счетчиков, выход генерат ра тактовых импульсов соединен с п вым входом второго элемента И, вто рой вход которого соединен с вторым выходом блока управления, а вькод второго элемента И соединен со сче ным входом первого счетчика, разря ные выходы которого соединены соот ственно с кодовыми входами умножит ля частоты на код, выход которого единен со счетным входом триггера первым информационным входом комму тора, второй информационный вход к торого соединен с выходом триггера второй выход блока управления соеди нен с входом управления коммутатор

тотипом предлагаемое множительное устройство обладает повьшенным быстродей- выход которого соединен со счетным ствием.входом второго счетчика.

(1)

1396U2

Фор

мула изобретения

ва вход-, ратора; ва вытегракодния. остуинтер4 Ijtdt

(2)

ьсов

интерв

тся

( tu)

3)

t4)

; , ние

(t,t w

10

15

20

о мнопроизыхенныноже- учаеттельустройбе врес проМножительное устройство, содержащее первый и второй счетчики, умножитель частоты на код, генератор тактовых И1у1пульсов, первый элемент И и блок управления, первый выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом генератора тактовых иьтульсов, а вьосод первого элемента И соединен с частотным входом умножителя частоты на код, отличаю- щ е е с я тем, что, с целью повышения быстродействия, блок управления содержит элемент ИЛИ, элемент И и од- новибратор, выход которого соединен с третьим выходом блока управления, а вход одновибратора соединен с первым выходом блока управления и выходом элемента ИЛИ, входы которого соединены с первым и вторым входами блока управления и первым и вторым вхо25 дами элемента И блока управления, выход которого соединен с вторым выходом блока управления, и, кроме того, в устройство введены триггер, коммутатор и второй элемент И, причем пер30 вый и второй информационные входы устройства соединены соответственно с первым и вторым входами блока уп- :равления, третий выход которого со- единен с входами обнуления первого и второго счетчиков, выход генератора тактовых импульсов соединен с первым входом второго элемента И, второй вход которого соединен с вторым выходом блока управления, а вькод второго элемента И соединен со счетным входом первого счетчика, разрядные выходы которого соединены соответственно с кодовыми входами умножителя частоты на код, выход которого соединен со счетным входом триггера и первым информационным входом коммутатора, второй информационный вход которого соединен с выходом триггера, второй выход блока управления соединен с входом управления коммутатора.

35

40

45

ое усттродей- выход которого соединен со счетным входом второго счетчика.

tft9.2

чшяитя1лЛ

| Данчеев В.П | |||

| Цифро-частотные вычислительные устройства | |||

| М.: Энергия, 1976, с | |||

| Устройство для выпрямления многофазного тока | 1923 |

|

SU50A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Оранский A.M | |||

| Аппаратные методы в цифровой в lчиcлитeльнoй технике | |||

| Минск: БГУ,1977, с.64, рис.3.5. | |||

Авторы

Даты

1988-05-15—Публикация

1986-11-25—Подача