ФизЛ

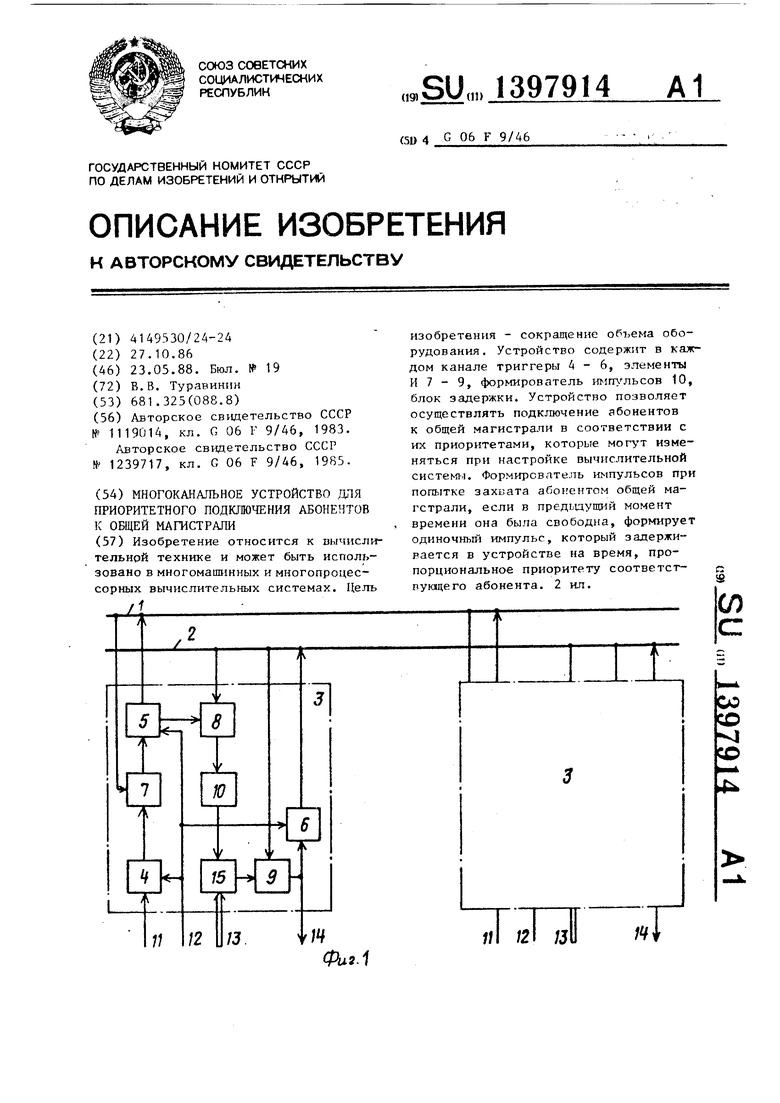

Изобретенне относится к вычисли- тельной технике, в частности к устройствам приоритетного обслуживания.

Целью изобретения является сокра- щение объема оборудования устройства

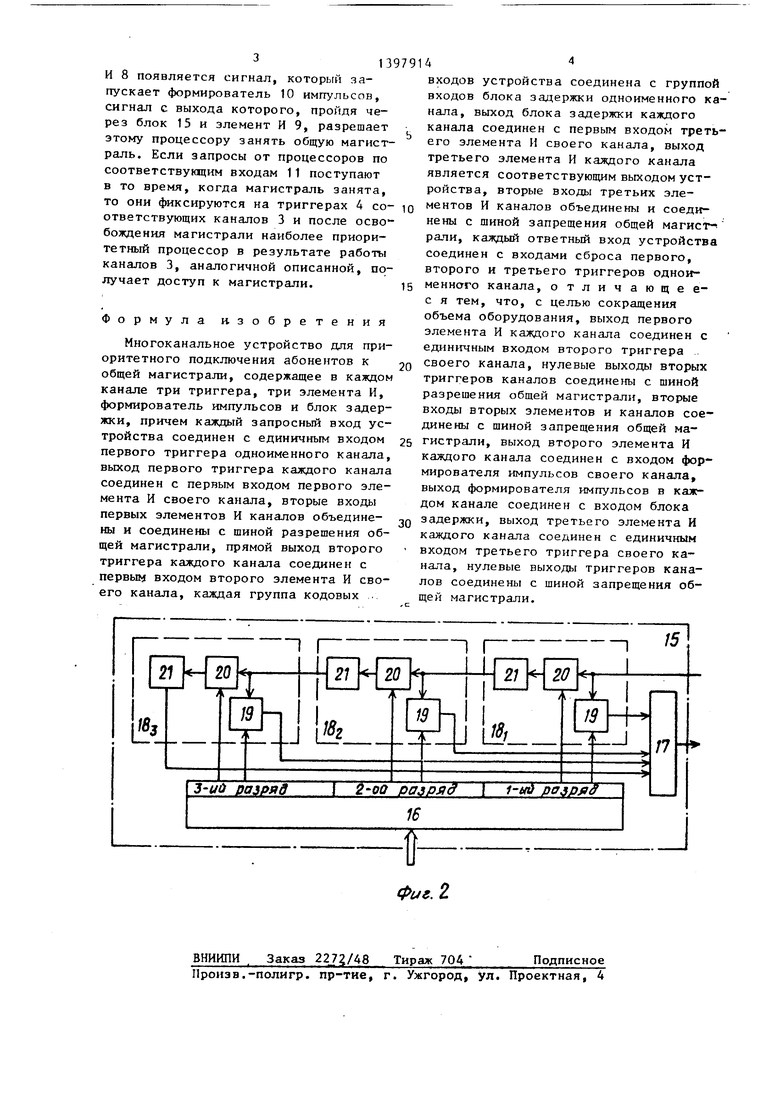

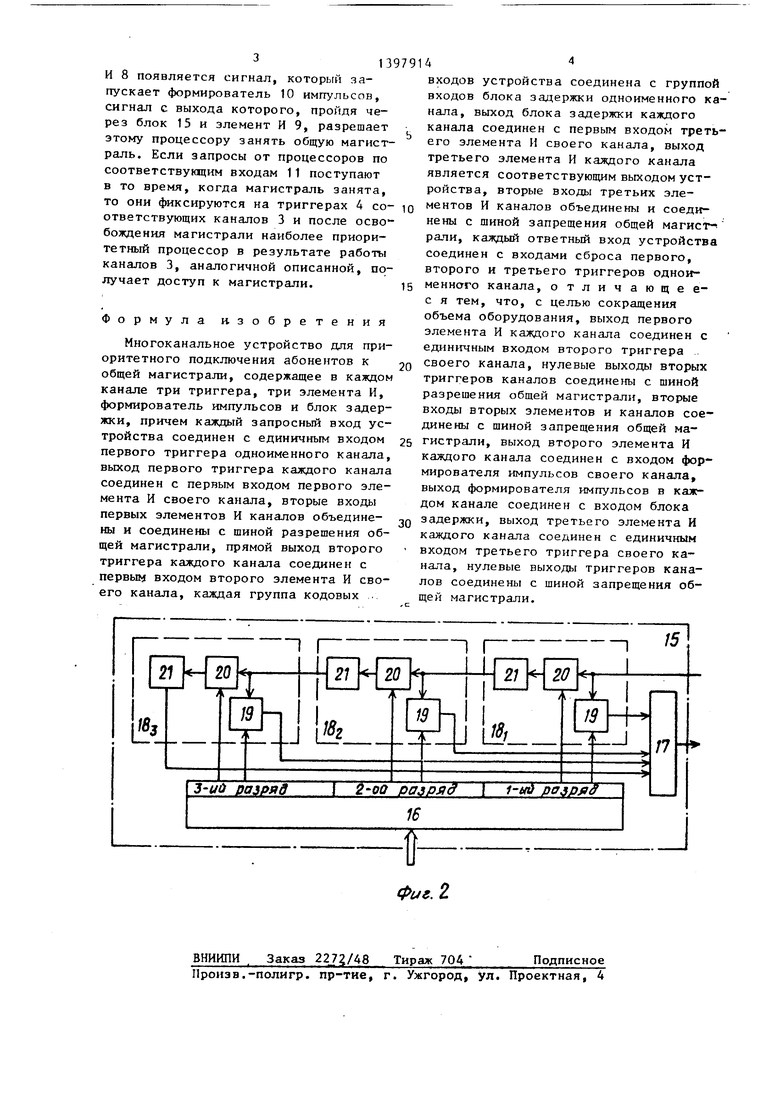

На фиг.1 изображена структурная схема устройства; на фиг.2 - структурная схема блока задержки (пример для трехразрядного кода).

Устройство содержит шину 1 разрешения общей магистрали, шину 2 запрещения общей магистрали, каналы 3, каждый из которых содержит триггеры 4-6, элементы И 7 - 9,.формироател

10импульсов, запросный вход 11 устройства, ответные входы 12 устройств ва, группы кодовых входов 13 устройства, выходы 14 устройства, блок 15 задержки, который содержит (фиг,2) регистр 16, элемент ИЛИ 17, узлы 18 задержки (по количеству разрядов регистра) , каждый из которых содержит элементы И 19,и 20 и элемент 21 задержки.

Устройство работает следукщим образом.

В исходном состояниии на регистры

16 от соответствующих источников информации через соответствующие груп- пы входов 13 заносятся коды приори- теттз процессоров, которые не могь Т быть одинаковыми, но при настройке вычислительной системы могут опера- Т1ГВНО изменяться, триггеры 4-6 на- ходятся в нулевом состоянии, на шинах 2 и 1 установлен сигнал кой единицы. В случайные моменты времени процессоры по мере необходимости передачи сообщений другим процес- сорам выдают на соответствующие вход

11сигналы, устанавливающие триггеры

4соответствующих каналов 3 в единичное состояние.

Рассмотрим работу одного из кана- лов 3, так как в остальных ка1галах работа осуществляется аналогичным образом. Сигнал с единичного выхода триггера 4 через открытый элемент И устанавл свает триггер 5 в единичное состояние, закрывая при этом через шину 1 элементы И 7 всех каналов 3. Сигнап с единичного выхода триггера

5через открытый элемент -И 8 запускает формирователь 10 импульсов, кото- рый выдает одиночньй импульс, поступающий на вход блока 15. Поскольку

на регистрах 16 блоков 15 различных каналов 3 установлены различные коды

то сигналы на выходах блоков 15 различных каналов 3 появляются в различное время (тем раньше, чем вьш1е приоритет процессора, подключенного к данному каналу). Так, например, для четырехпроцессорной вычислительной системы коды приоритетов процессоров должны иметь следующий вид: 111, 011, 001, 000 (коды записаны в порядке возрастания приоритета). Если, например, в данное время на общую магистраль претендуют два процессора, имеющие первый и второй приоритеты, т.е. их коды приоритетов соответственно равны 000 и 001, то после поступления сигнала на вход блока 15, на регистре 16 которого установлен код 000, на выходе блока 15 появляется единичный сигнал через время задержки, которое обусловлено задержкой поступившего сигнала на элементе И 19 и элементе ИЛИ 17 этого блока 15. На выходе блока i5, на регистре 16 которого установлен код 001, появляется сигнал через время, обусловленное прохождением сигнала, поступающего на вход этого блока 15 через элемент И 20, элемент 21 задержки узла 18,элемент И 19 узла IBj и элемент ИЛИ 17 данного блока 15.

После появления сигнала на выходе блока 15, имеющего максимальный приоритет, срабатывает элемент И 9 канала 3, и через выход 14 выдается сиг- нал, уведомляющий о том, что общая магистраль захвачена, можно передавать по ней информацию. Этот же сиг- нал переводит триггер 6 в единичное состояние, устанавливая тем самым нулевой сигнал на шине 2 и закрывая таким образом элементы И 8 и 9 всех каналов 3. Для надежной работы устройства время задержки элементов 21 должно быть не меньше трех логических элементов. В этом случае к моменту вьщачи сигнала с выхода блока 15, на регистре 16 которого установлен.код 001, элемент И 9 закрыт. Доступ к общей магистрали он может получить после того, как процессор с первым приоритетом закончит передачу информации и вьщаст на вход 12 своего канала 3 сигнал, устанавливающий триггеры 4-6 этого канала в нулевое состояние. Так как на шине 2 появляется единичный сигнал, то в канале 3, к которому подключен процессор с первым приоритетом, на выходе элемента

313

И 8 появляется сигнал, который запускает формирователь 10 импульсов, сигнал с выхода которого, пройдя через блок 15 и элемент И 9, разрешает этому процессору занять общую магистраль. Если запросы от процессоров по соответствующим входам 11 поступают в то время, когда магистраль занята, то они фиксируются на триггерах 4 со- ответствующих каналов 3 и после освобождения магистрали наиболее приоритетный процессор в результате работы каналов 3, аналогичной описанной, получает доступ к магистрали.

Формула изобретения

Многоканальное устройство для приоритетного подключения абонентов к общей магистрали, содержащее в каждом канале три триггера, три элемента И, формирователь импульсов и блок задержки, причем каждый запросный вход устройства соединен с единичным входом первого триггера одноименного канала, выход первого триггера каждого канала соединен с первым входом первого элемента И своего канала, вторые входы первых элементов И каналов объединены и соединены с шиной разрешения общей магистрали, прямой выход второго триггера каждого канала соединен с первьп входом второго элемента И своего канала, каждая группа кодовых

входов устройства соединена с группой входов блока задержки одноименного канала, выход блока задержки каждого канала соединен с первым входом третьего элемента И своего канала, выход третьего элемента И каждого канала является соответствующим выходом устройств а, вторые входы третьих элементов И каналов объединены и соеди нены с шиной запрещения общей магист- рали, каждый ответный вход устройства соединен с входами сброса первого, второго и третьего триггеров однои

меннаго канала, отличающее- с я тем, что, с целью сокращения объема оборудования, выход первого элемента И каждого канала соединен с един}гчным входом второго триггера . своего канала, нулевые выходы вторых триггеров каналов соединены с шиной разрешения общей магистрали, вторые входы вторых элементов и каналов соединены с шиной запрещения общей магистрали, выход второго элемента И каждого канала соединен с входом формирователя импульсов своего канала, выход формирователя импульсов в каждом канале соединен с входом блока задержки, выход третьего элемента И каждого канала соединен с единичным входом третьего триггера своего канала, нулевые выходы триггеров каналов соединены с шиной запрещения общей магистрали.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1989 |

|

SU1709312A1 |

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1984 |

|

SU1239717A1 |

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1989 |

|

SU1589277A2 |

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1987 |

|

SU1458873A2 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1987 |

|

SU1462311A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1988 |

|

SU1524059A1 |

| Многоканальное устройство для сопряжения абонентов с общей магистралью | 1984 |

|

SU1223237A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Многоканальное устройство для распределения заданий процессорам | 1988 |

|

SU1619287A1 |

| Многоканальное устройство для подключения абонентов к общему ресурсу | 1990 |

|

SU1837307A1 |

Изобретение относится к вычисли- тельнрй технике и может быть использовано в многомашинных и многопроцессорных вычислительных системах. Цель / г| / изобретения - сокращение объема оборудования. Устройство содержит в каждом канале триггеры 4-6, элементы И 7 - 9, формирователь импл льсов 10, блок задержки. Устройство позволяет осуществлять подключение абонентов к общей магистрали в соответствии с их приоритетами, которые могут изменяться при настройке вычислительной систем.. Формирователь импульсов при попытке захвата абонентом общей ма- гстрали, если в предьузущий момент времени она была свободна, формирует одиночный импульс, который задерживается в устройстве на время, пропорциональное приоритету соответствующего абонента. 2 ил. п сл 00 со vj (Г ;|| /21 /J П «Г

| Многоканальное устройство приоритета | 1983 |

|

SU1119014A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1984 |

|

SU1239717A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-05-23—Публикация

1986-10-27—Подача