СП

00 00

оо

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1986 |

|

SU1397914A1 |

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1989 |

|

SU1589277A2 |

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1989 |

|

SU1709312A1 |

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1984 |

|

SU1239717A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1987 |

|

SU1462311A1 |

| Устройство для распределения приоритетных заявок по процессорам | 1987 |

|

SU1495795A1 |

| Отказоустойчивая вычислительная система | 1990 |

|

SU1798800A1 |

| Многоканальное устройство для сопряжения абонентов с общей магистралью | 1984 |

|

SU1223237A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1988 |

|

SU1524059A1 |

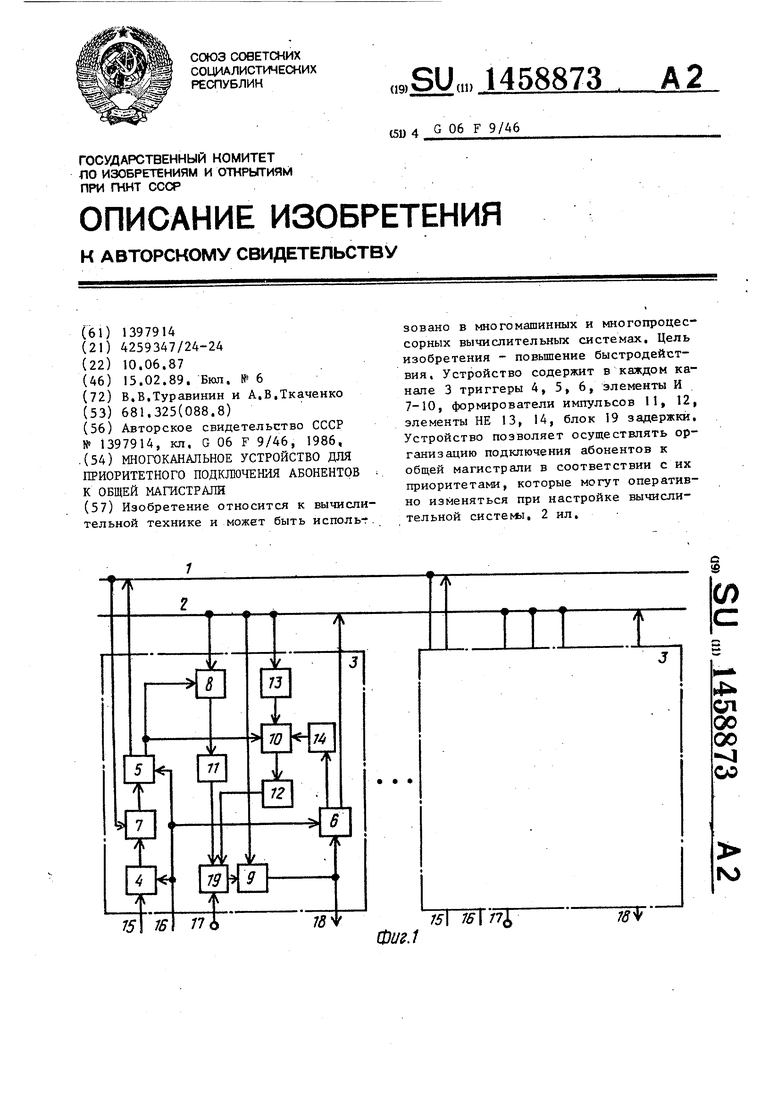

Изобретение относится к вычислительной технике и может быть исполь-. зовано в многомашинных и многопроцессорных вычислительных системах. Цель изобретения - повьшение быстродействия. Устройство содержит в каждом канапе 3 триггеры 4, 5, 6, элементы И 7-10, формирователи импульсов 11, 12, элементы НЕ 13, 14, блок 19 задержки. Устройство позволяет осуществлять организацию подключения абонентов к общей магистрали в соответствии с их приоритетами, которые могут оперативно изменяться при настройке вычислительной систеи. 2 ил.

N

Изобретение относится к области вычислительной техники и может быть применено в многомашинных и многопроцессорных вычислительных системах, ис- одиночный импульс, поступающий на первый вход блока 19, Поскольку на реничного выхода триггера 5 через открытый элемент И 8 запускает формиро- .ватель 11 импульсов, который выдает

пользукяцих для обмена данными общую магистраль (ОМ),

Цель изобретения - повьшение быстродействия.

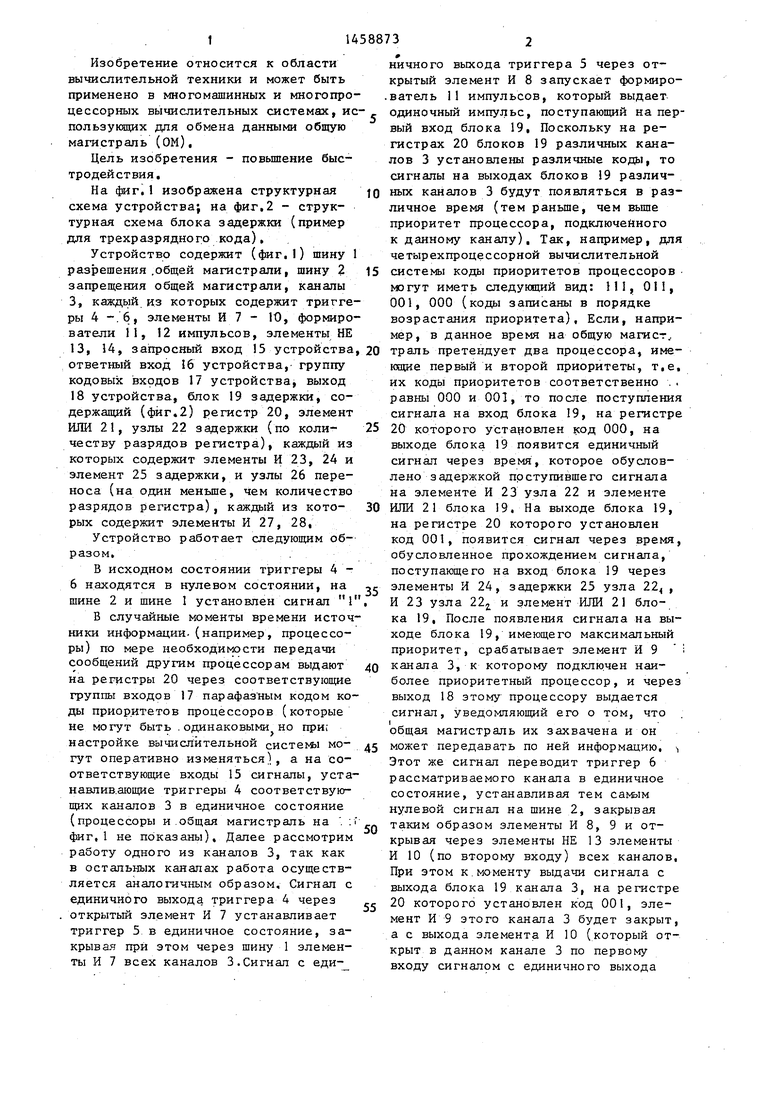

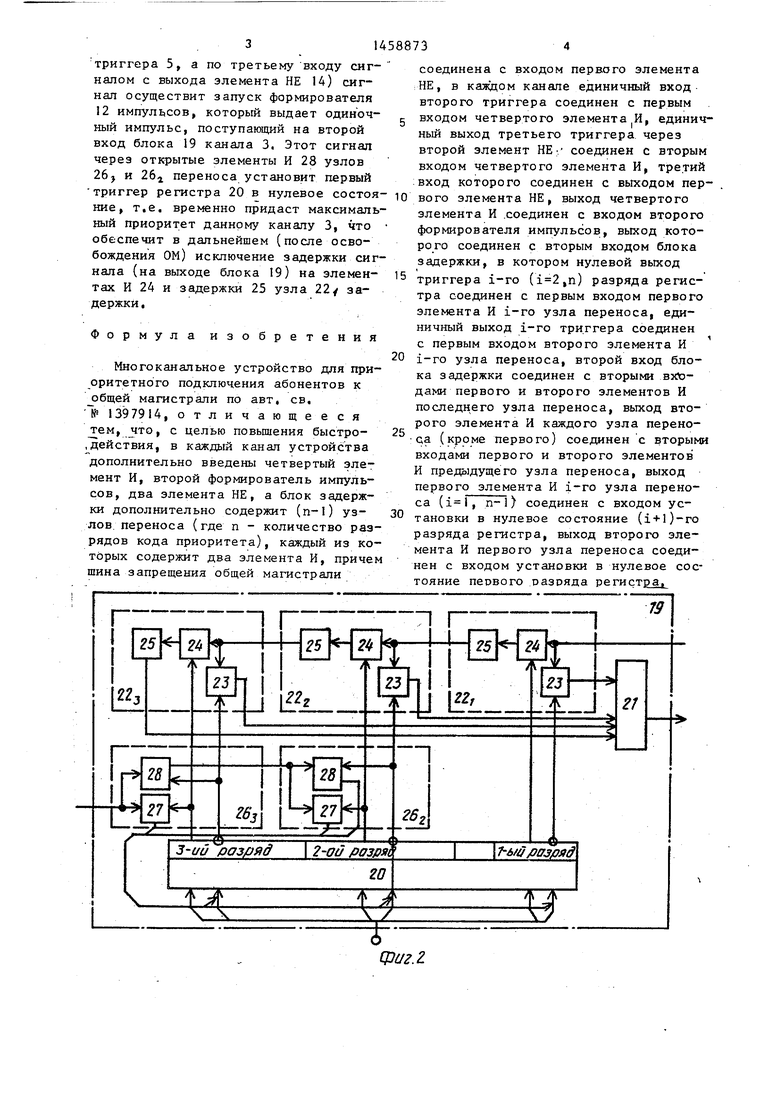

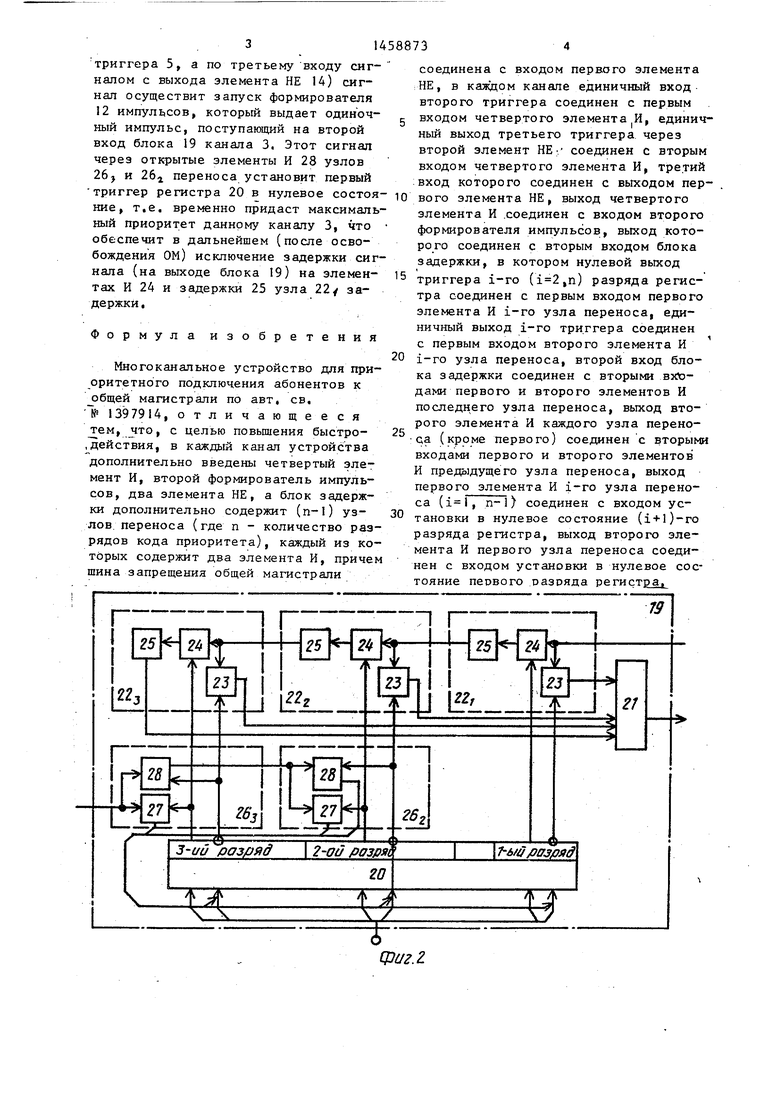

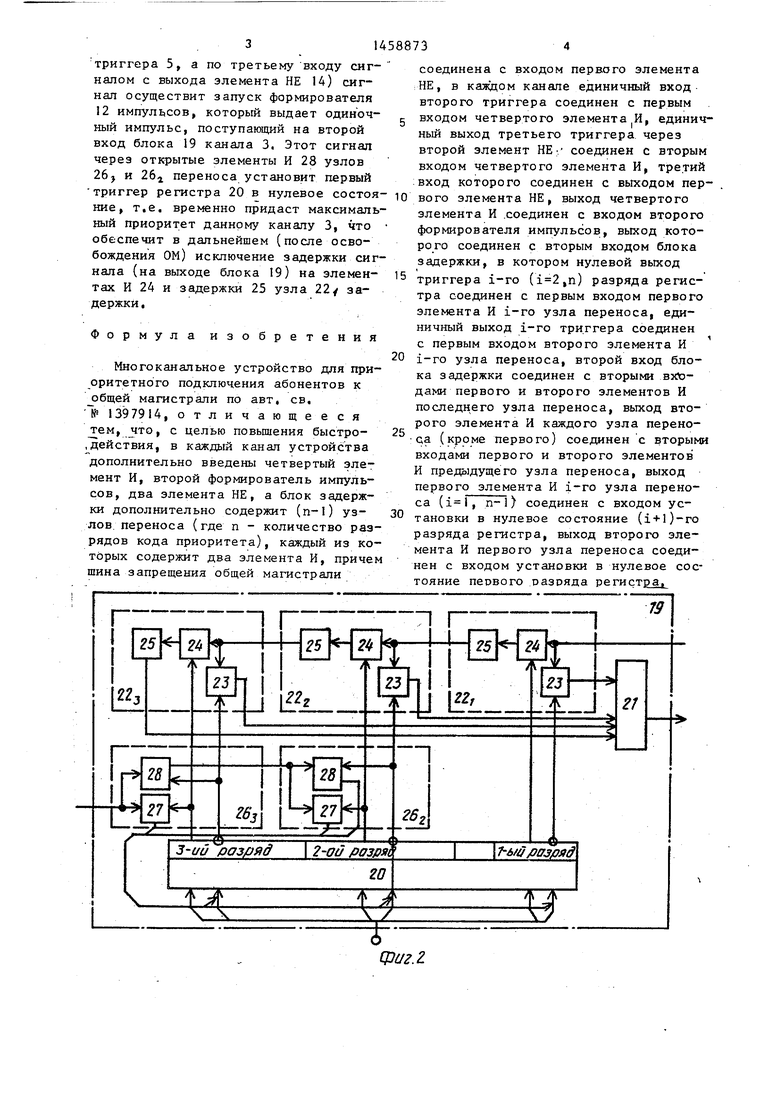

На фиг,1 изображена структурная схема устройства; на фиг,2 - структурная схема блока задержки (пример для трехразрядного кода).

Устройство содержит (фиг,1) шину 1 разрешения .общей магистрали, шину 2 запрещения общей магистрали, каналы 3, каждый из которых содержит триггеры 4 -.6, элементы И 7 - Ю, формирователи 11, 12 импульсов, элементы НЕ

гистрах 20 блоков 19 различных каналов 3 установлены различные коды, то сигналы на выходах блоков 19 различ10 ных каналов 3 будут появляться в различное время (тем раньше, чем вьщ1е приоритет процессора, подключенного к данному каналу). Так, например, для четырехпроцессорной вычислительной

15 системы коды приоритетов процессоров могут иметь следукщий вид: П1, 011, 001, 000 (коды записаны в порядке возрастания приоритета). Если, например, в данное время на общую магист..

30

13, 14, запросный вход 15 устройства, 20 траль претендует два процессора, име- ответный вход 16 устройства, группу кодовых входов 17 устройства, выход 18 устройства, блок 19 задержки, содержащий (фиг.2) регистр 20, элемент ИЛИ 21, узлы 22 задержки (по коли- 25 честву разрядов регистра), каждый из которых содержит элементы И 23, 24 и элемент 25 задержки, и узлы 26 переноса (на один меньше, чем количество разрядов регистра), каждый из которых содержит элементы И 27, 28,

Устройство работает следующим образом,.

В исходном состоянии триггеры 4 - 6 находятся в нулевом состоянии, на шине 2 и шине I установлен сигнал 1,

В случайные моменты времени источники информации, (например, процессоры) по мере необходимости передачи сообщений другим процессорам выдают 40 на регистры 20 через соответствующие группы входов 17 парафаз ным кодом коды приоритетов процессоров (которые

35

ющие первый и второй приоритеты, т,е, их коды приоритетов соответственно .. равны 000 и 001, то после поступления сигнала на вход блока 19, на регистре 20 которого установлен код 000, на выходе блока 19 появится единичный сигнал через время, которое обусловлено задержкой поступившего сигнала на элементе И 23 узла 22 и элементе ИЛИ 21 блока 19, На выходе блока 19, на регистре 20 которого установлен код 001, появится сигнал через время, обусловленное прохождением сигнала, поступающего на вход блока 19 через элементы И 24, задержки 25 узла 22 , И 23 узла 22 и элемент ИЛИ 21 блока 19, После появления сигнала на выходе блока 19, имеющего максимальный приоритет, срабатывает элемент И 9 ; канала 3, к которому подклю.чен наиболее приоритетный процессор, и через выход 18 этому процессору выдается сигнал, уведомляюш;ий его о том, что общая магистраль их захвачена и он может передавать по ней информацию, , Этот же сигнал переводит триггер 6 рассматриваемого канала в единичное состояние, устанавливая тем самым нулевой сигнал на шине 2, закрывая таким образом элементы И 8, 9 и открывая через элементы НЕ 13 элементы И 10 (по второму входу) всех каналов. При этом к. моменту выдачи сигнала с выхода блока 19 канала 3, на регистре 20 которого установлен код 001, элемент И 9 этого канала 3 будет закрыт, .а с выхода элемента И 10 (который открыт в данном канале 3 по первому входу сигналом с единичного выхода

не могут быть .одинаковыми но при; настройке вычислительной системы могут оперативно изменяться), а на соответствующие входы 15 сигналы, уста- навлив.ающие триггеры 4 соответствующих каналов 3 в единичное состояние (процессоры и .общая магистраль на . : фиг,1 не показаны). Далее рассмотрим работу одного из каналов 3, так как в осталы-гых каналах работа осуществляется аналогичным образом. Сигнал с единичного выхода триггера 4 через открытый элемент И 7 устанавливает триггер 5 в единичное состояние, закрывая при этом через шину 1 элементы И 7 всех каналов 3.Сигнал с еди одиночный импульс, поступающий на первый вход блока 19, Поскольку на реничного выхода триггера 5 через открытый элемент И 8 запускает формиро- .ватель 11 импульсов, который выдает

гистрах 20 блоков 19 различных канаов 3 установлены различные коды, то сигналы на выходах блоков 19 различных каналов 3 будут появляться в различное время (тем раньше, чем вьщ1е приоритет процессора, подключенного к данному каналу). Так, например, для четырехпроцессорной вычислительной

системы коды приоритетов процессоров могут иметь следукщий вид: П1, 011, 001, 000 (коды записаны в порядке возрастания приоритета). Если, например, в данное время на общую магист..

траль претендует два процессора, име-

траль претендует два процессора, име-

ющие первый и второй приоритеты, т,е, их коды приоритетов соответственно .. равны 000 и 001, то после поступления сигнала на вход блока 19, на регистре 20 которого установлен код 000, на выходе блока 19 появится единичный сигнал через время, которое обусловлено задержкой поступившего сигнала на элементе И 23 узла 22 и элементе ИЛИ 21 блока 19, На выходе блока 19, на регистре 20 которого установлен код 001, появится сигнал через время, обусловленное прохождением сигнала, поступающего на вход блока 19 через элементы И 24, задержки 25 узла 22 , И 23 узла 22 и элемент ИЛИ 21 блока 19, После появления сигнала на выходе блока 19, имеющего максимальный приоритет, срабатывает элемент И 9 ; канала 3, к которому подклю.чен наиболее приоритетный процессор, и через выход 18 этому процессору выдается сигнал, уведомляюш;ий его о том, что общая магистраль их захвачена и он может передавать по ней информацию, , Этот же сигнал переводит триггер 6 рассматриваемого канала в единичное состояние, устанавливая тем самым нулевой сигнал на шине 2, закрывая таким образом элементы И 8, 9 и открывая через элементы НЕ 13 элементы И 10 (по второму входу) всех каналов. При этом к. моменту выдачи сигнала с выхода блока 19 канала 3, на регистре 20 которого установлен код 001, элемент И 9 этого канала 3 будет закрыт, .а с выхода элемента И 10 (который открыт в данном канале 3 по первому входу сигналом с единичного выхода

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1986 |

|

SU1397914A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-15—Публикация

1987-06-10—Подача