Оо

со со

ел

05

t13

Изобретение относится к вычислительной технике и может быть исполь - зёвано для определения вероятностных характеристик систем массового обслуживания .

Целью изобретения является расширение функциональных возможностей устройства за счет моделирования систем массового обслуживания с изме- няющейся интенсивностью поступления запросов на обслуживание и повышение быстродействия.

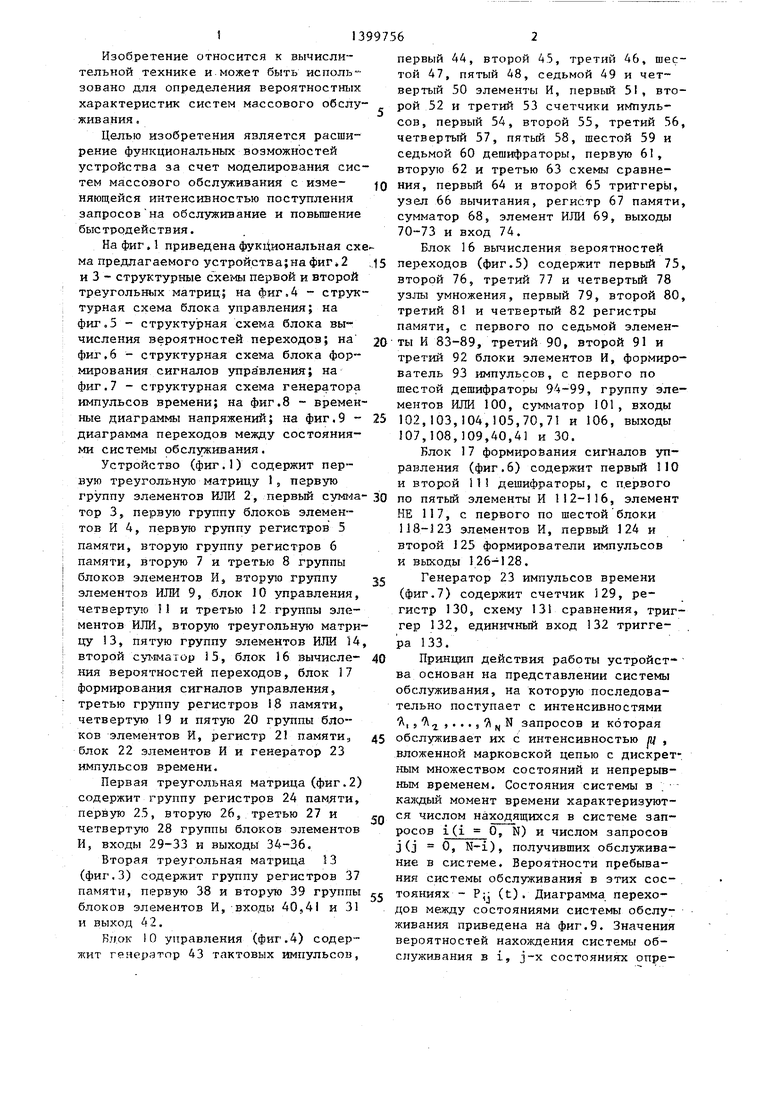

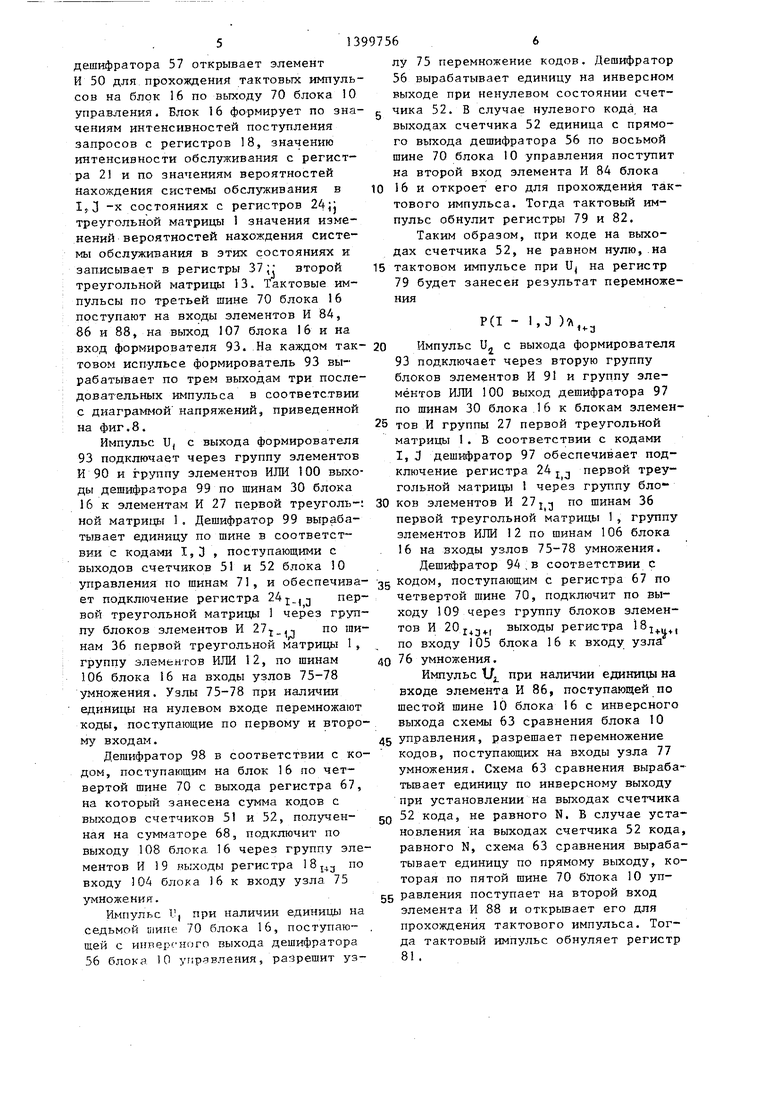

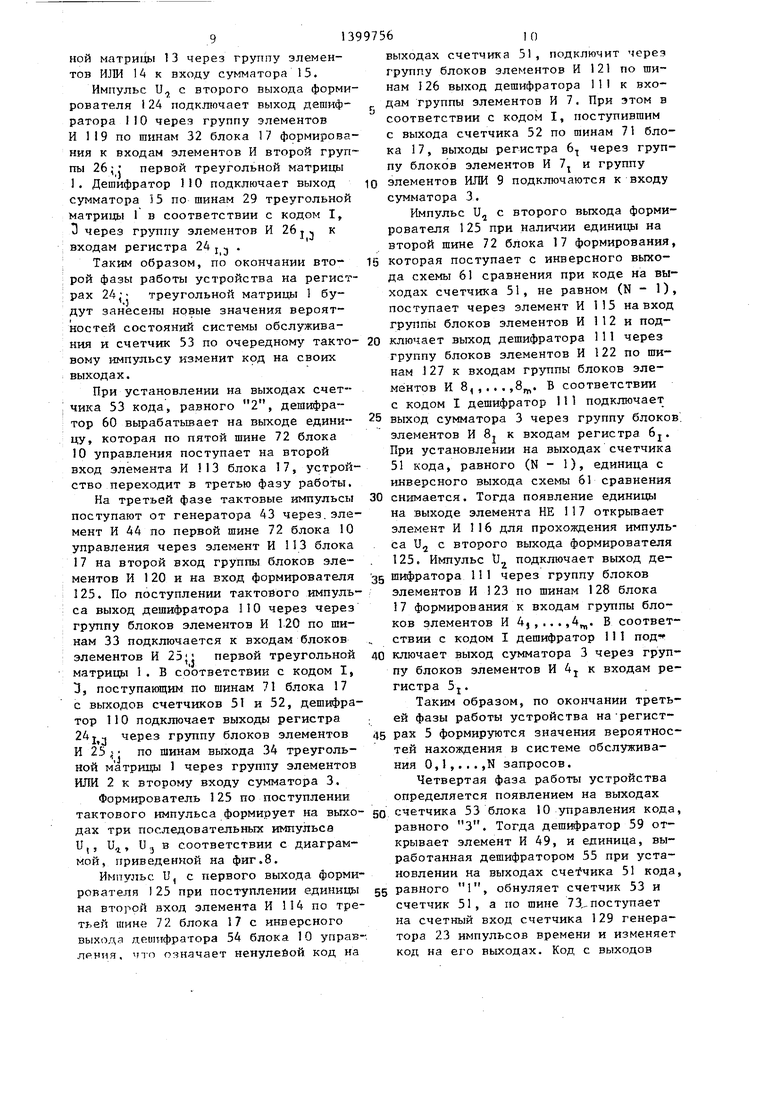

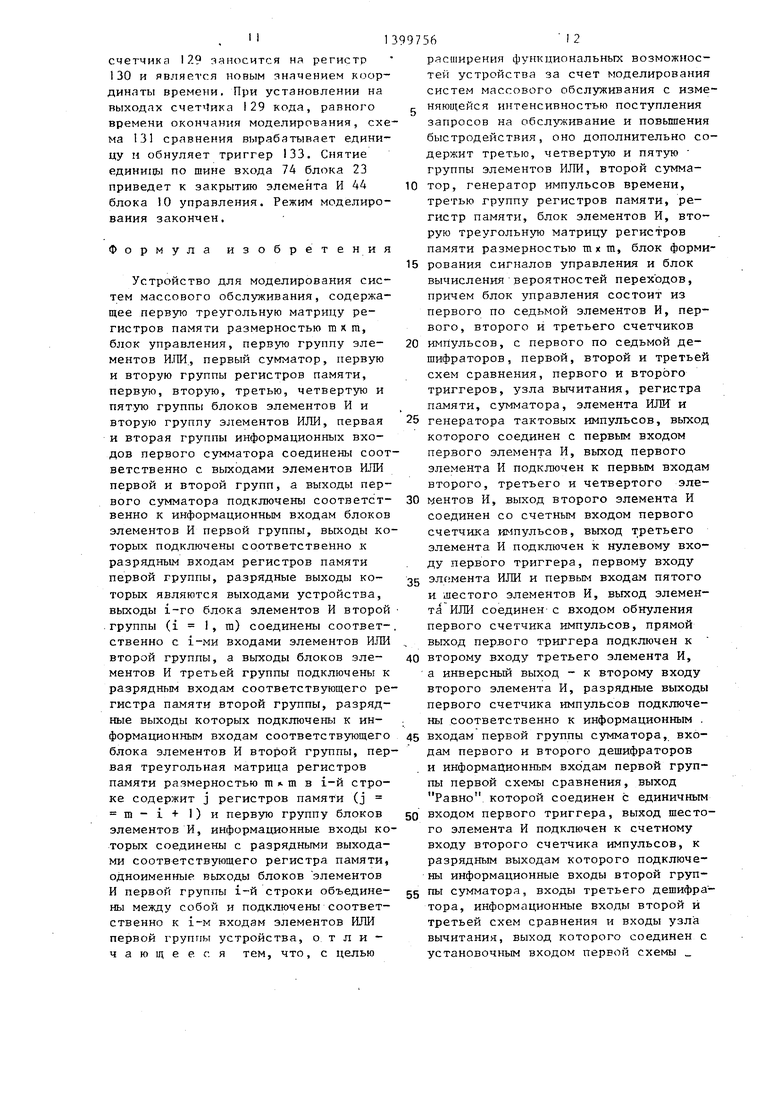

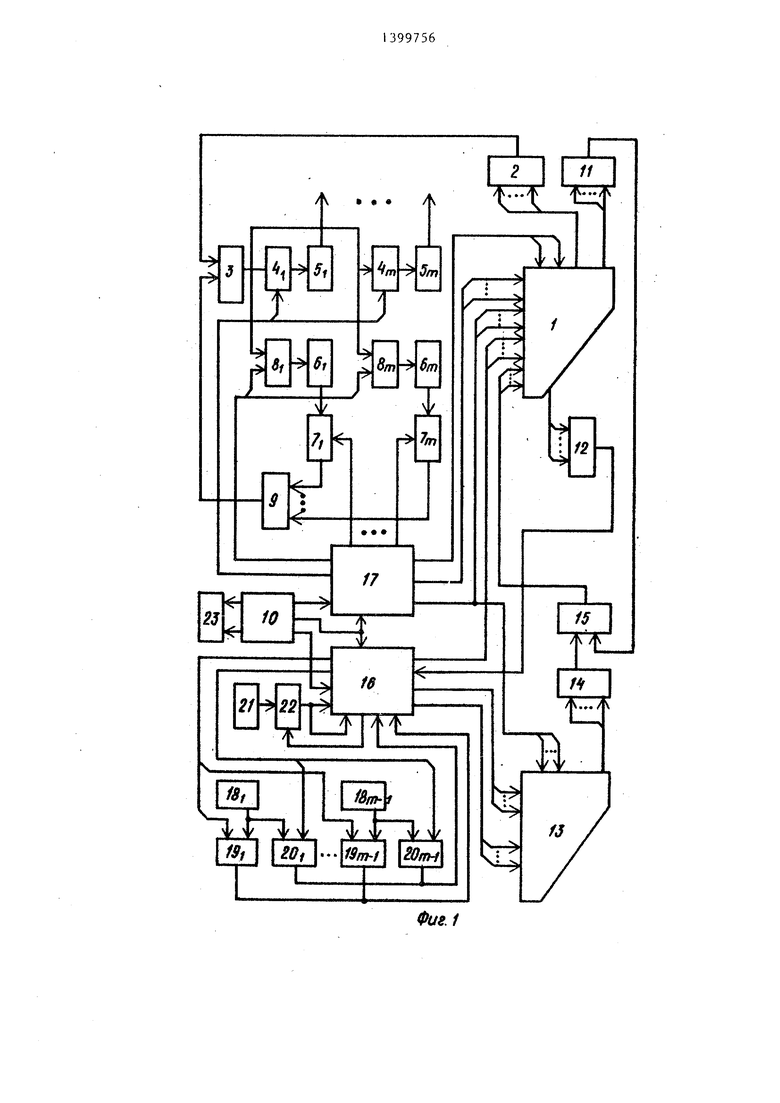

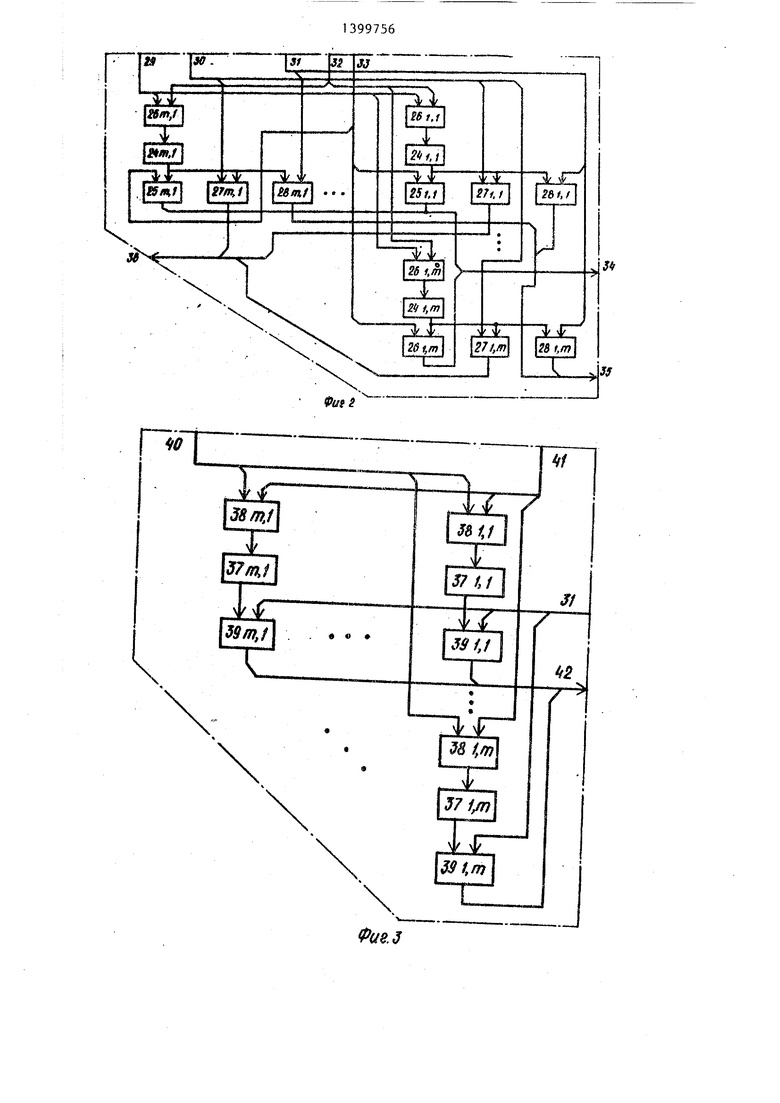

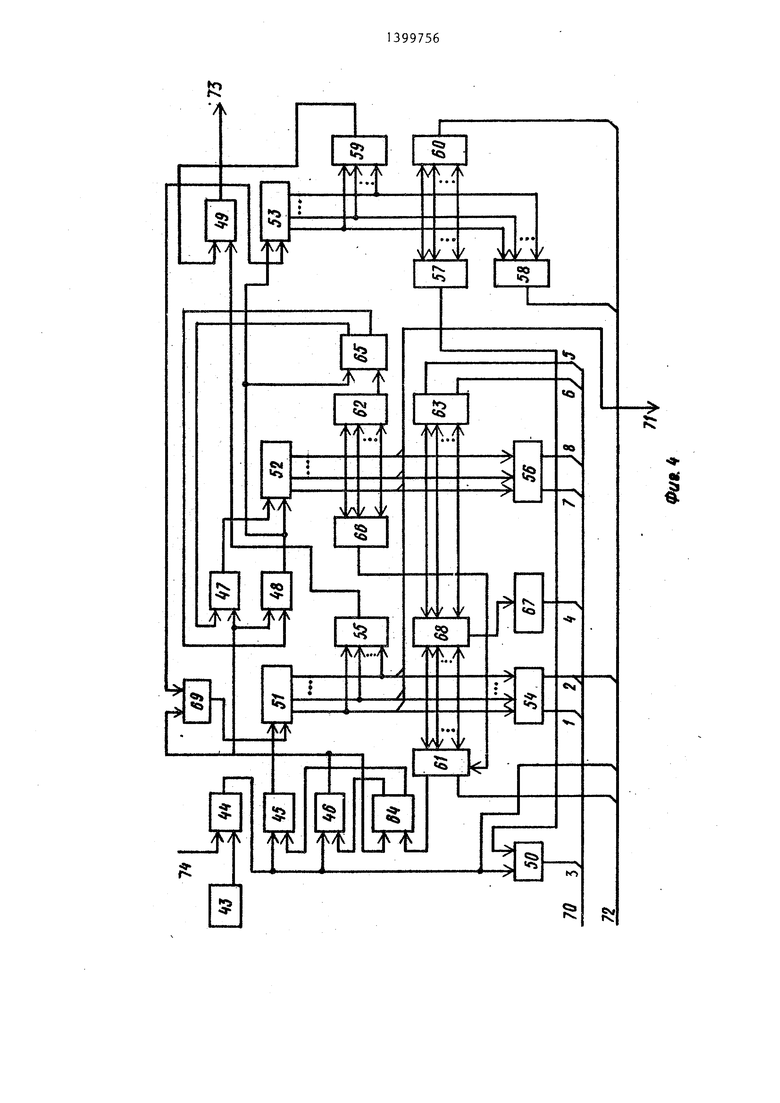

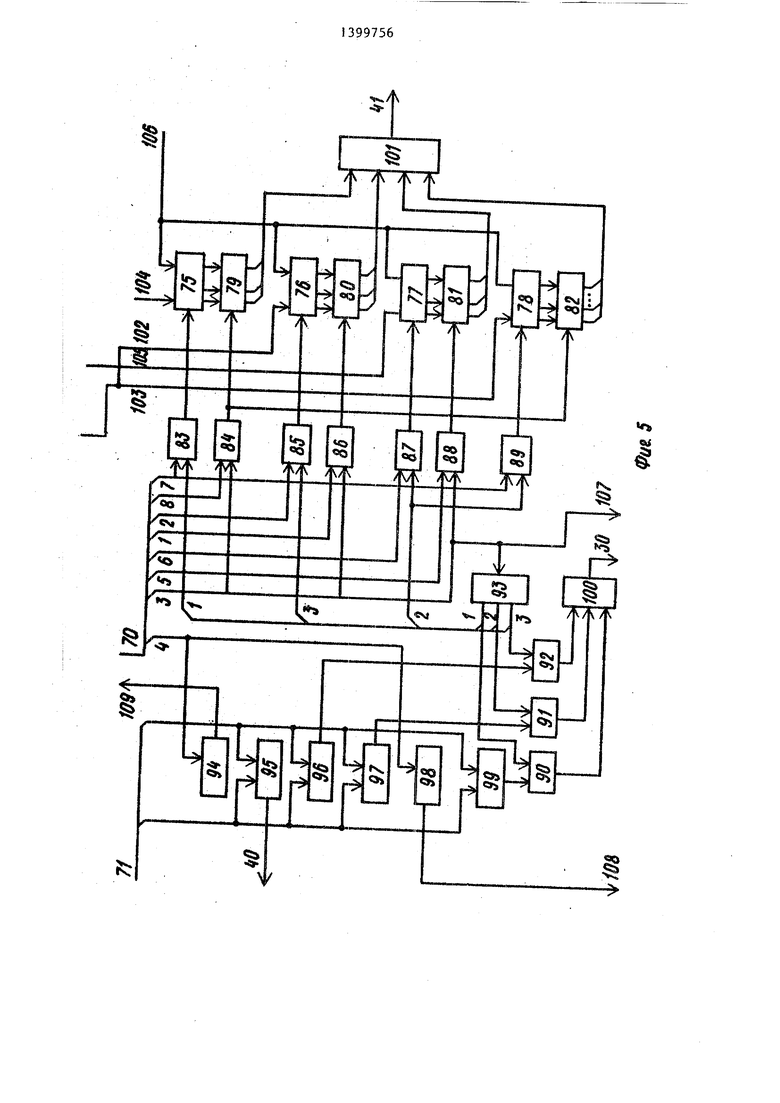

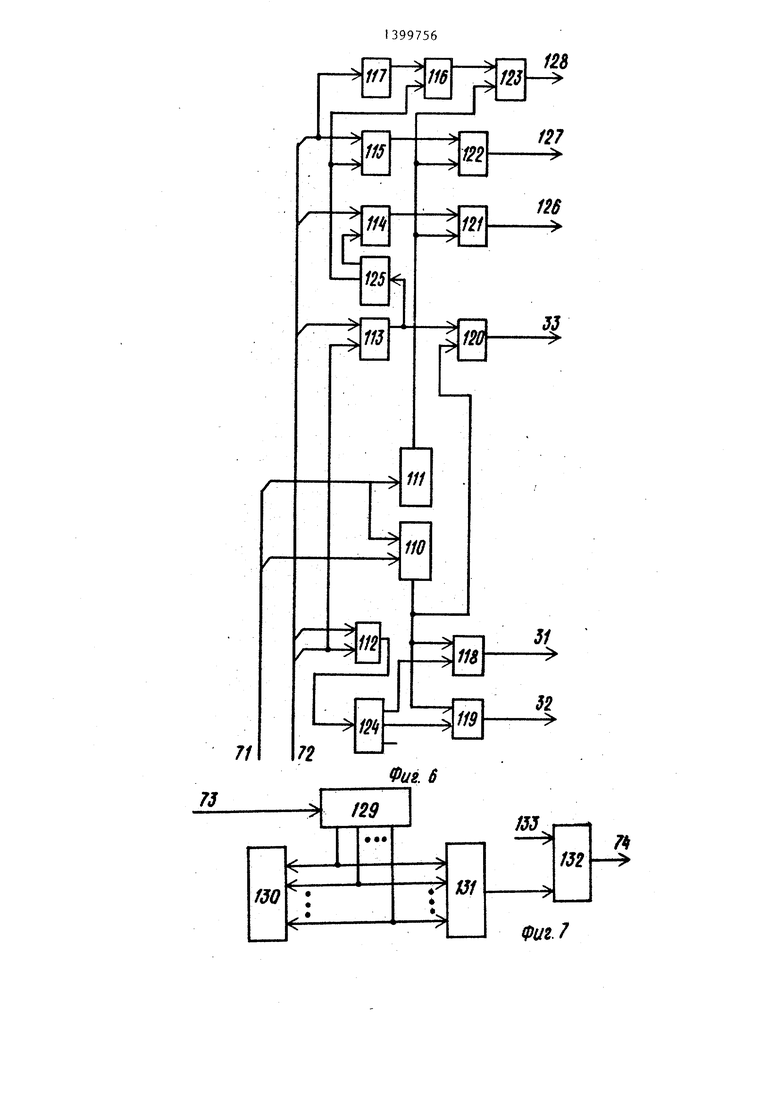

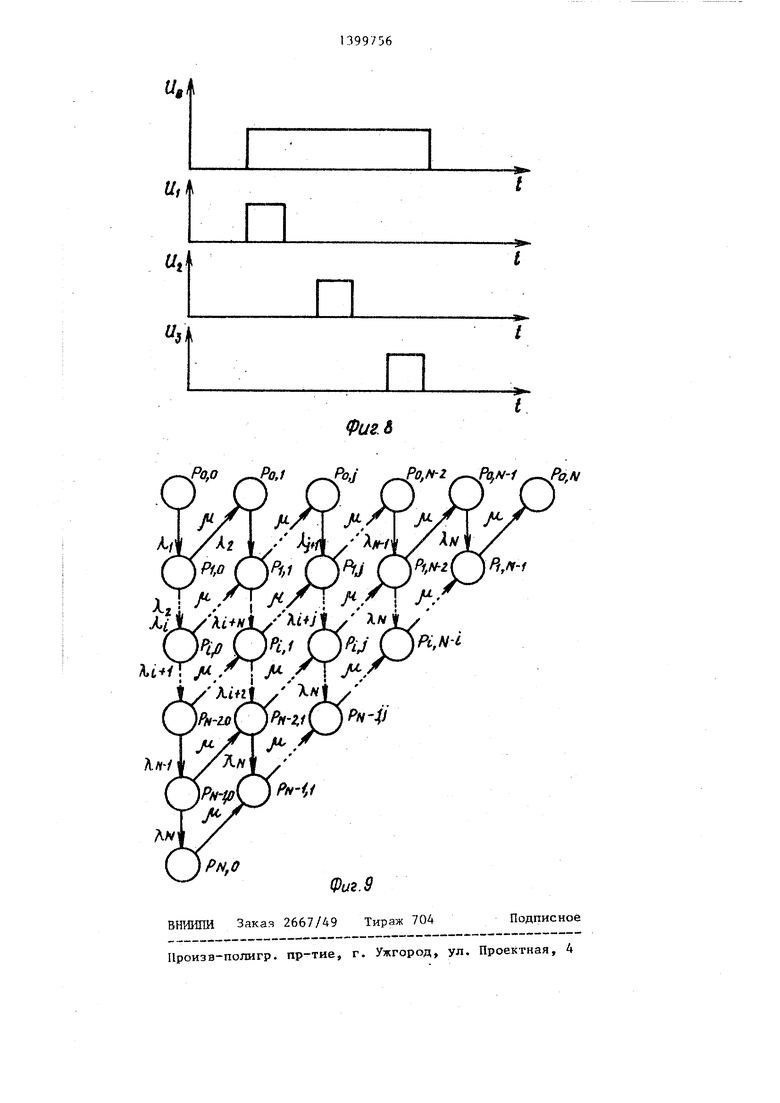

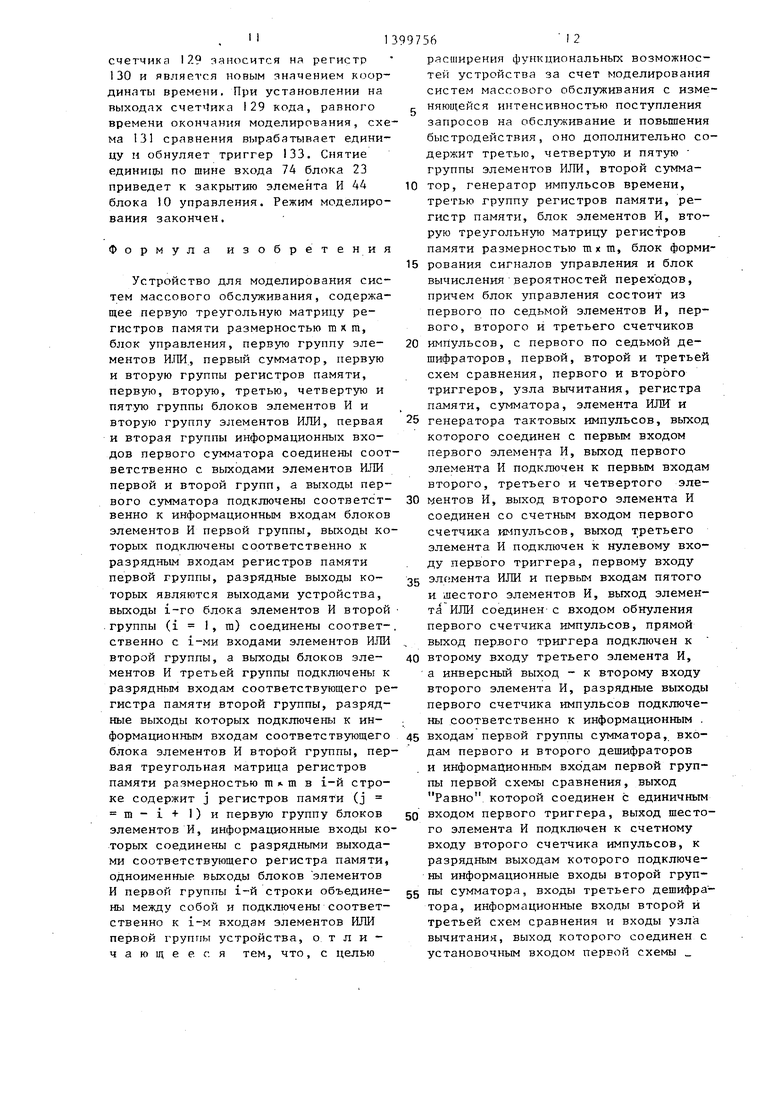

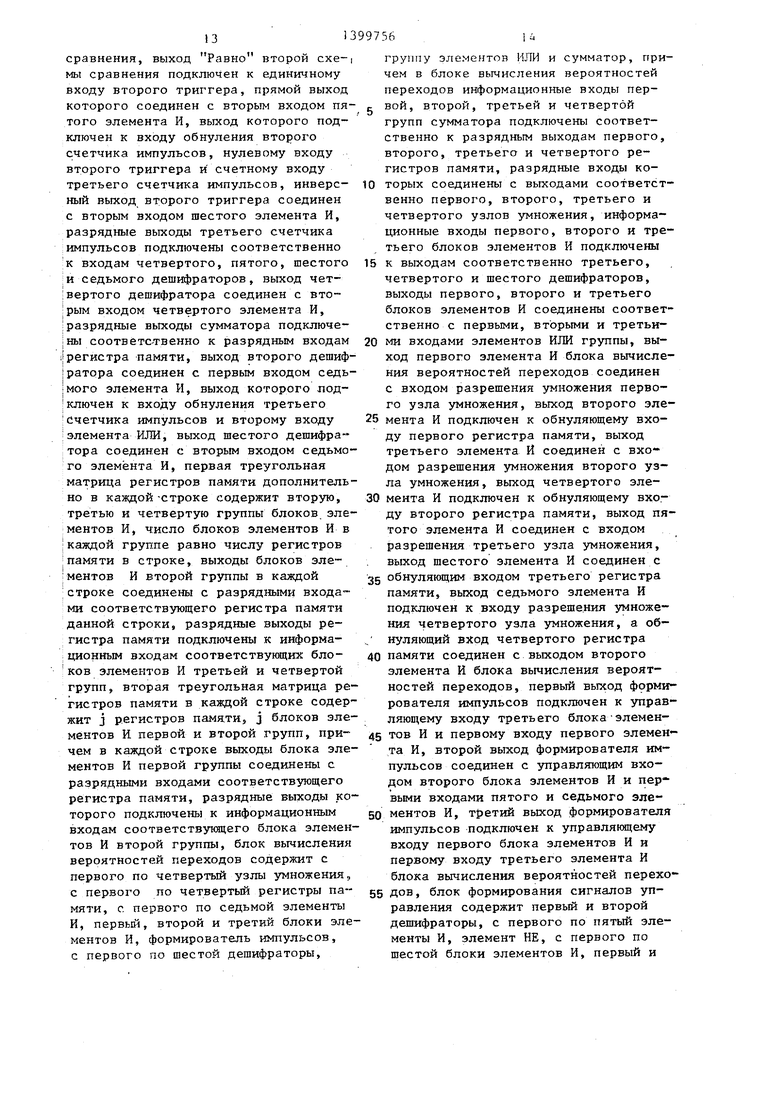

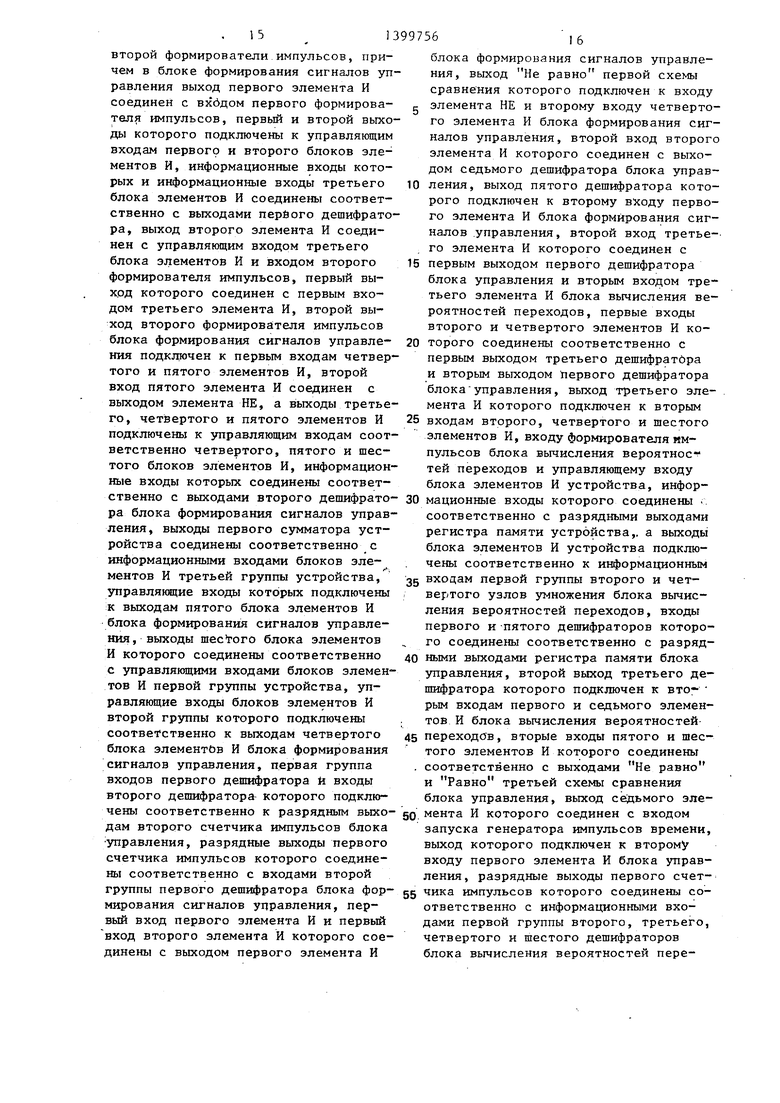

На фиг. 1 приведена фуктДиональная схма предлагаемого устройств а; на фиг 2 и 3 - структурные схемы первой и второй треугольш 1х матриц; на фиг.4 - структурная схема блока управления; на фиг,5 - структу рная схема блока вычисления вероятностей переходов; на фи1,6 - структурная схема блока фор мирования сигналов управления; на фиг.7 - структурная схема генератора импульсов времени; на фиг.8 - времен

ные диагр,аммы напряжений; на фиг.9 - 25 102,103,104,105,70,71 и 106, выходы

первый 44, второй 45, третий 46, шестой 47, пятый 48, седьмой 49 и четвертый 50 элементы И, первый 51, второй 52 и третий 53 счетчики импульсов, первый 54, второй 55, третий 56, четвертый 57, пятый 58, шестой 59 и седьмой 60 дешифраторы, первую 61, вторую 62 и третью 63 схемы сравнения, первый 64 и второй 65 триггеры, узел 66 вычитания, регистр 67 памяти, сумматор 68, элемент ИЛИ 69, выходы 70-73 и вход 74.

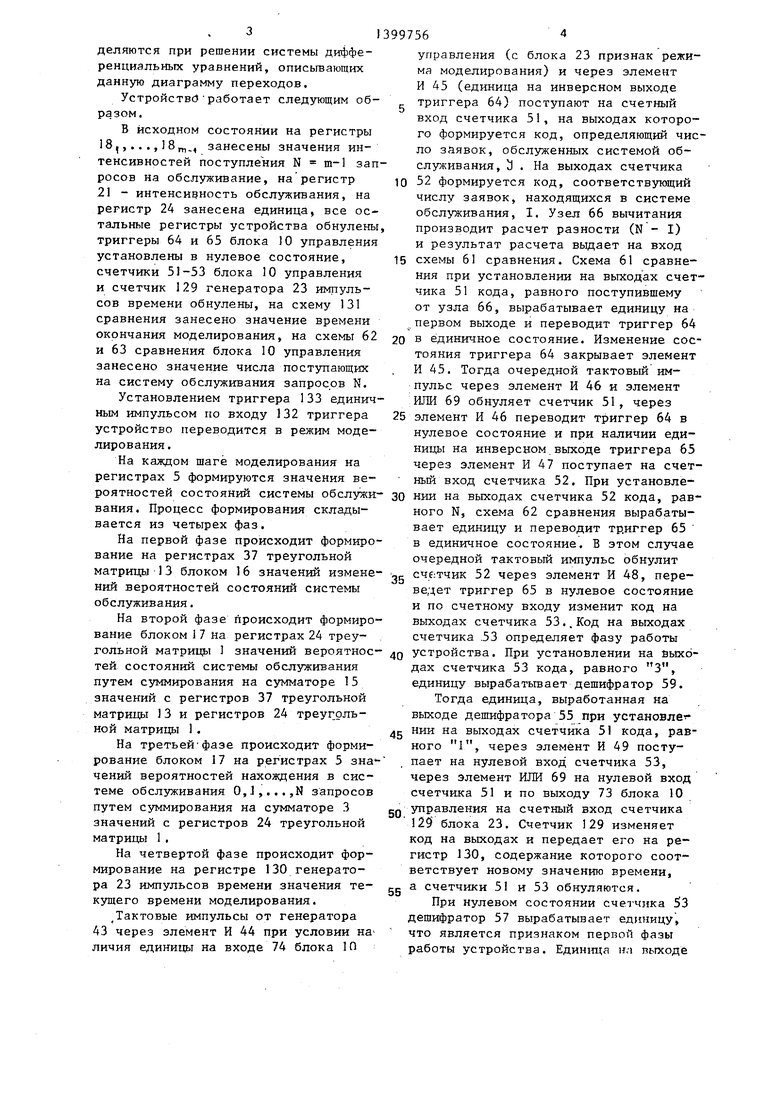

Блок 16 вычисления вероятностей переходов (фиг.5) содержит первьй 75, второй 76, третий 77 и четвертый 78 узлы умножения, первый 79, второй 80, третий 81 и четвертый 82 регистры памяти, с первого по седьмой элементы И 83-89, третий 90, второй 91 и третий 92 блоки элементов И, формирователь 93 импульсов, с первого по шестой дешифраторы 94-99, группу элементов ИЛИ 100, сумматор 101, входы

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования систем массового обслуживания | 1989 |

|

SU1652979A1 |

| Устройство для моделирования сетевых графов | 1982 |

|

SU1065858A1 |

| Устройство для определения времени проведения технического обслуживания системы | 1987 |

|

SU1571633A1 |

| Устройство для моделирования сетевых графов | 1981 |

|

SU1013965A1 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Устройство для моделирования сетевых графов | 1983 |

|

SU1151979A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

| Устройство отображения информации на экране телевизионного индикатора | 1986 |

|

SU1425768A1 |

| Устройство для формирования гистограммы случайных чисел | 1988 |

|

SU1702391A1 |

| Устройство для моделирования биматричных игр | 1986 |

|

SU1388847A1 |

Изобретение относится к вычислительной технике и может быть использовано для определения вероятностных характеристик систем массового обслуживания. Цель изобретения - расширение функциональных возможностей устройства за счет моделирования систем массового обслуживания с изменяющейся интенсивностью поступления запросов на обслуживание и повьппение быстродействия. Цель достигается тем, что в устройство дополнительно введены группы элементов ИЛИ, сумматор, генератор импульсов времени, группа регистров памяти, регистр памяти, блок элементов И, треугольная матрица регистров памяти, блок формирователей сигналов управления и блок вычисления вероятностей переходов. 9 ил.

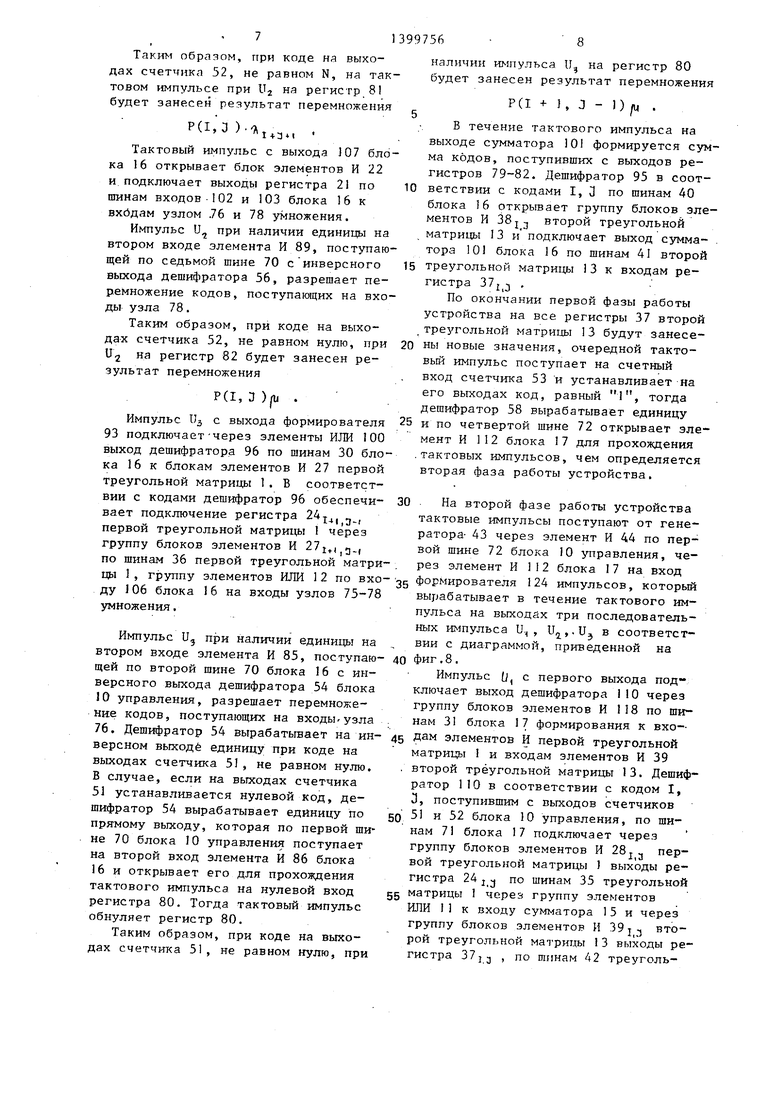

диаграмма переходов между состояниями системы обслуживания.

Устройство (фиг.1) содержит первую треугольную матрицу 1, первую

группу элементов ИЛИ 2, первый сумма-ЗО по пятый элементы И П2-П6, элемент

тор 3, первую группу блоков элементов И 4, первую группу регистров 5 памяти, вторую группу регистров 6 памяти, вторую 7 и третью 8 группы блоков элементов И, вторую группу элементов ИЛИ 9, блок 10 управления, четвертую П и третью 12 группы элементов ИЛИ, BTopjm треугольную матрицу 13, пятую группу элементов ИЛИ 14,

35

НЕ 117, с первого по Е естой блоки 118-123 элементов И, первый 124 и второй 125 формирователи импульсов и вькоды 126-128.

Генератор 23 импульсов времени (фиг.7) содержит счетчик 129, регистр 130, схему 1ЗГ сравнения, триггер 132, единичный вход 132 триггера 133.

второй сзгмматор 15, блок 16 вычисления вероятностей перекодов, блок 17 формирования сигналов управления, третью группу регистров 18 памяти, четвертую 19 и пятую 20 группы блоков элементов И, регистр 21 памяти, блок 22 элементов И и генератор 23 импульсов времени.

Первая треугольная матрица (фиг.2) содержит группу регистров 24 памяти, первую 25, вторую 26, третью 27 и четвертую 28 группы блоков элементов И, входы 29-33 и выходы 34-36.

Вторая треугольная матрица 13 (фиг.З) содержит группу регистров 37 памяти, первую 38 и вторую 39 группы блоков элементов И,-входы 40,41 и 31 и выход 4 2.

Блок 10 управления (фиг.4) содержит генератор 43 тактовых импульсов,

107,108,109,40,41 и 30.

Блок 17 формиройания сигналов управления (фиг.6) содержит первый ПО и второй 1 1 дешифраторы, с п.ервого

5

0

5

с

0

НЕ 117, с первого по Е естой блоки 118-123 элементов И, первый 124 и второй 125 формирователи импульсов и вькоды 126-128.

Генератор 23 импульсов времени (фиг.7) содержит счетчик 129, регистр 130, схему 1ЗГ сравнения, триггер 132, единичный вход 132 триггера 133.

Принцип действия работы устройства основан на представлении системы обслуживания, на которую последовательно поступает с интенсивностями Д, } 7i,..., запросов и которая обслуживает их с интенсивностью гц , вложенной марковской цепью с дискретным множеством состояний и непрерьш- ным временем. Состояния системы в , - каждый момент времени характеризуются числом находящихся в системе запросов i(i О, N) и числом запросов j(j 0, N-i), получивших обслуживание в системе. Вероятности пребывания системы обслуживания в этих состояниях - P;j (t) . Диаграмма переходов между состояниями системы обслуживания приведена ни фиг.9. Значения вероятностей нахождения системы обслуживания в i, j-x состояниях опре3

деляются при решении системы дифференциальных уравнений, описьгеающих данную диаграмму переходов.

Устройства работает следующим образом.

В исходном состоянии на регистры 18,,.. ., 1 8„, занесены значения ин- тенсивностей поступления N т-1 зап росов на обслуживание, на регистр 21 - интенсивность обслуживания, на регистр 24 занесена единица, все остальные регистры устройства обнулены триггеры 64 и 65 блока 10 управления установлены в нулевое состояние, счетчики 51-53 блока 10 управления и счетчик 129 генератора 23 импульсов времени обнулены, на схему 131 сравнения занесено значение времени окончания моделирования, на схемы 62 и 63 сравнения блока 10 управления занесено значение числа поступающих на систему обслуживания запросов N,

Установлением триггера 133 единичным импульсом по входу 132 триггера устройство переводится в режим моделирования.

На каждом шаге моделирования на регистрах 5 формируются значения вероятностей состояний системы обслуживания. Процесс формирования складывается из четырех фаз.

На первой фазе происходит формирование на регистрах 37 треугольной матриць 13 блоком 16 значений изменений вероятностей состояний системы обслуживания.

На второй фазе происходит формирование блоком 1 7 На регистрах 24 треугольной матрш5 1 1 значений вероятностей состояний систамь обслуживания путем суммирования на сумматоре 15 значений с регистров 37 треугольной матрицы 13 и регистров 24 треугольной матрицы 1.

На третьей фазе происходит формирование блоком 17 на регистрах 5 зна чений вероятностей нахождения в системе обслуживания 0,J,,..,N запросов путем суммирования на сумматоре 3 значений с регистров 24 треугольной матрицы 1.

На четвертой фазе происходит формирование на регистре 130 генератора 23 импульсов времени значения текущего времени моделирования.

Дактовые импульсы от генератора 43 через элемент И 44 при условии на личия единицы на входе 74 блока Ш

997564

управления (с блока 23 признак режима моделирования) и через элемент И 45 (единица на инверсном выходе

t- триггера 64) поступают на счетный вход счетчика 51, на выходах которого формируется код, определяющий число заявок, обслуженных системой обслуживания, 3 . На выходах счетчика

10 52 формируется код, соответствующий числу заявок, находящихся в системе обслуживания, I. Узел 66 вычитания производит расчет разности (N - I) и результат расчета выдает на вход

15 схемы 61 сравнения. Схема 61 сравнения при установлении на выходах счетчика 51 кода, равного поступившему от узла 66, вырабатывает единицу на первом выходе и переводит триггер 64

20 в единичное состояние. Изменение состояния триггера 64 закрывает элемент И 45. Тогда очередной тактовый импульс через элемент И 46 и элемент ПЛИ 69 обнуляет счетчик 51, через

25 элемент И 46 переводит триггер 64 в нулевое состояние и при наличии единицы на инверсном выходе триггера 65 через элемент И 47 поступает на счет- ный вход счетчика 52, При установле30 НИИ на выходах счетчика 52 кода, равного N, схема 62 сравнения вырабатывает единицу и переводит триггер 65 в единичное состояние, В этом случае очередной тактовьй импульс обнулит

-g счг:тчик 52 через элемент И 48, переведет триггер 65 в нулевое состояние и по счетному входу изменит код на выходах счетчика 53..Код на выходах счетчика .53 определяет фазу работы

40 устройства. При установлении на выходах счетчика 53 кода, равного 3, единицу вырабатьгеает дешифратор 59,

Тогда единица, выработанная на выходе дешифратора 55 при установлв

Д2 Нин на выходах счетчика 51 кода, равного I, через элемент И 49 поступает на нулевой вход счетчика 53, через элемент ИЛИ 69 на нулевой вход счетчика 51 и по выходу 73 блока 10

50 управления на счетный вход счетчика 129 блока 23. Счетчик 129 изменяет код на выходах и передает его на регистр 130, содержание которого соответствует новому значению времени,

gg а счетчики 51 и 53 обнуляются.

При нулевом состоянии счетчика 53 дешифратор 57 вырабатывает единицу, что является признаком первой фазы работы устройства. Един1ща н,ч выходе

513997566

дешифратора 57 открывает элемент лу 75 перемножение кодов. Дешифратор И 50 для прохождения тактовых импуль- 56 вырабатывает единицу на инверсном сов на блок 16 по выходу 70 блока 10 управления. Блок 16 формирует по зна- g

10

чениям интенсивностей поступления запросов с регистров 18, значению интенсивности обслуживания с регистра 2 и по зна гениям вероятностей Нахождения системы обслуживания в IfJ -X состояниях с регистров 24;j треугольной матрицы 1 значения изменений вероятностей нахождения системы обслуживания в этих состояниях и записывает в регистры 37; второй треугольной матрИ1Цз1 13. Тактовые импульсы по третьей шине 70 блока I6 поступают на вхсзды элементов И 84, 86 н 88, на выход 107 блока 16 и на вход формирователя 93. На каждом так- 20 товом исп-ульсе формирователь 93 вырабатывает по трем выходам три последовательных импульса в соответстврш с диаграммой напряжений, приведенной на фиг.8.25

Импульс U( с выхода формирователя 93 подключает через группу элементов И 90 и группу элементов ИЛИ I00 выходы дешифратора 99 по шинам 30 блока

выходе при ненулевом состоянии счетчика 52. В случае нулевого кода, на выходах счетчика 52 единица с прямого выхода дешифратора 56 по восьмой шине 70 блока 10 управления поступит на второй вход элемента И 84 блока 16 и откроет его для прохождения так тового импульса. Тогда тактовый импульс обнулит регистры 79 и 82.

Таким образом, при коде на выходах счетчика 52, не равном нулю,.на 15 тактовом импульсе при Uj на регистр 79 будет занесен результат перемноже ния

Р(1 - 1,а )

и-з

Импульс Uj с выхода формирователя 93 подключает через вторую группу блоков элементов И 91 и группу элементов ИЛИ 100 выход дешифратора 97 по шинам 30 блока 16 к блокам элемен тов И группы 27 первой треугольной матрицы 1. В соответствии с кодами I, Л дешифратор 97 обеспечивает подключение регистра первой треугольной матрицы 1 через группу бло16 к элементам И 27 первой треуголь-: 30 ков элементов И 27 jj по шинам 36

ной матри1л 1 I , Дешифратор 99 вырабатывает единицу по шине в соответствии с кодами 1,3 , поступающими с выходов счетчиков 51 и 52 блока 10

первой треугольной матрицы 1, rpjm элементов ИЛИ 12 по шинам 106 блок 16 на входы узлов 75-78 умножения. Дешифратор 94,в соответствии с

управления по шинам 71, и обеспечива- д кодом, поступающим с регистра 67 по ет подключение регистра пер- четвертой шине 70, подключит по вы- вой треугольной матрии з 1 через группу блоков элементов И 27 по шинам 36 первой треугольной матрицы 1, группу элементов ИЛИ 12, но шинам 106 блока 16 на входы узлов 75-78 умножения. Узлы 75-78 при наличии единицы на нулевом входе перемножают коды, поступающие по первому и второму входам.

Дешифратор 98 в соответствии с кодом, поступающим на блок 16 по четвертой шине 70 с выхода регистра 67, на который занесена сумма кодов с выходов счетчиков 51 и 52, полученная на сумматоре 68, подключит по выходу 108 блока 16 через группу элементов И 19 выходы регистра 18 j., по входу 104 блока 16 к входу узла 75 умножения:.

И шyльc Г, при наличии единицы на седьмой liiHiU 70 блока 16, поступаю- . щей с инверсного выхода дешифратора 56 блока 10 уг рзвления5 разрешит узходу 109 через группу блоков элемен тов И 20j.j, выходы регистра 18 по входу 105 блока 16 к входу узла

40 76 умножения.

Импульс l/j при наличии единицы на входе элемента И 86, поступающей по шестой шине 10 блока 16 с инверсного выхода схемы 63 сравнения блока 10

45 управления, разрешает перемножение кодов, поступающих на входы узла 77 умножения. Схема 63 сравнения выраб тьшает единицу по инверсному выходу при установлении на выходах счетчика

5Q 52 кода, не равного N. В случае уста новления на выходах счетчика 52 код равного N, схема 63 сравнения выраба тывает единицу по прямому выходу, ко торая по пятой шине 70 бЛока 10 уп5g равления поступает на второй вход элемента И 88 и открьюает его для прохождения тактового импульса. Тогда тактовый импульс обнуляет регистр 81 .

лу 75 перемножение кодов. Дешифратор 56 вырабатывает единицу на инверсном

выходе при ненулевом состоянии счетчика 52. В случае нулевого кода, на выходах счетчика 52 единица с прямого выхода дешифратора 56 по восьмой шине 70 блока 10 управления поступит на второй вход элемента И 84 блока 16 и откроет его для прохождения тактового импульса. Тогда тактовый импульс обнулит регистры 79 и 82.

Таким образом, при коде на выходах счетчика 52, не равном нулю,.на тактовом импульсе при Uj на регистр 79 будет занесен результат перемножения

Р(1 - 1,а )

и-з

Импульс Uj с выхода формирователя 93 подключает через вторую группу блоков элементов И 91 и группу элементов ИЛИ 100 выход дешифратора 97 по шинам 30 блока 16 к блокам элементов И группы 27 первой треугольной матрицы 1. В соответствии с кодами I, Л дешифратор 97 обеспечивает подключение регистра первой треугольной матрицы 1 через группу блоков элементов И 27 jj по шинам 36

первой треугольной матрицы 1, rpjmny элементов ИЛИ 12 по шинам 106 блока 16 на входы узлов 75-78 умножения. Дешифратор 94,в соответствии с

д кодом, поступающим с регистра 67 по четвертой шине 70, подключит по вы-

ходу 109 через группу блоков элементов И 20j.j, выходы регистра 18 по входу 105 блока 16 к входу узла

40 76 умножения.

Импульс l/j при наличии единицы на входе элемента И 86, поступающей по шестой шине 10 блока 16 с инверсного выхода схемы 63 сравнения блока 10

45 управления, разрешает перемножение кодов, поступающих на входы узла 77 умножения. Схема 63 сравнения выраба- тьшает единицу по инверсному выходу при установлении на выходах счетчика

5Q 52 кода, не равного N. В случае установления на выходах счетчика 52 кода, равного N, схема 63 сравнения вырабатывает единицу по прямому выходу, которая по пятой шине 70 бЛока 10 уп5g равления поступает на второй вход элемента И 88 и открьюает его для прохождения тактового импульса. Тогда тактовый импульс обнуляет регистр 81 .

Таким образом, при коде на выходах счетчика 52, не равном N, на тактовом импульсе при U на регистр 81 будет занесен результат перемножения

p(i, a).,,,, .

Тактовый импульс с выхода J07 блока 16 открывает блок элементов И 22 и подключает выходы регистра 2) по шинам входов-102 и 103 блока 16 к вхбдам узлом .76 и 78 умножения.

Импульс и, при наличии единицы на втором входе элемента И 89, поступающей по седьмой шине 70 с инверсного выхода деши4 ратора 56, разрешает перемножение кодов, поступающих на входы узла 78.

Таким образом, при коде на выходах счетчика 52, не равном нулю, при

и.

на регистр 82 будет занесен результат перемножения

Р(1, Л)р .

Импульс Пг, с выхода формирователя 93 подключает Через элементы ИЛИ 100 выход дешифратора 96 по шинам 30 блока 16 к блокам элементов И 27 первой треугольной матрицы 1. В соответствии с кодами дешифратор 96 обеспечивает подключение регистра 241, ,j, первой треугольной матрицы 1 через группу блоков элементов И 27i,|.j-t по шинам 36 первой треугольной матрицы 1, группу элементов ИЛИ 12 по входу 106 блока 16 на входы узлов 75-78 умножения.

Импульс и, при наличии единшЦ) на втором входе элемента И 85, поступающей по второй шине 70 блока 16 с инверсного выхода дешифратора 54 блока 10 управления, разрешает перемножение кодов, поступающих на входы узла 76. Дешифратор 54 вырабатывает на инверсном выходе единицу при коде на выходах счетчика 51, не равном нулю. В случае, если на выходах счетчика 53 устанавливается нулевой код, дешифратор 54 вырабатывает единицу по прямому выходу, которая по первой шине 70 блока 10 управления поступает на второй вход элемента И 86 блока 16 и открывает его для прохождения тактового импульса на нулевой вход регистра 80. Тогда тактовый импульс обнуляет регистр 80.

Таким образом, при коде на выходах счетчика 51, не равном нулю, при

наличии импульса U на регистр 80 будет занесен результат перемножения

PCI + }, J - )) /U . 5

В течение тактового импульса на

выходе сумматора 101 формируется сумма кодов, поступивших с выходов регистров 79-82. Дешифратор 95 в соот0 ветствии с кодами I, 3 по шинам 40 блока 16 открьшает группу блоков элементов И 38j-j второй треугольной матрицы 13 и подключает выход сумма- . тора 10 блока 16 по шинам 41 второй

5 треугольной матрицы 13 к входам регистра 37jj .

По окончании первой фазы работы устройства на все регистры 37 второй трез гольной матрицы 13 будут занесе0 ны новые значения, очередной тактовый импульс поступает на счетный вход счетчика 53 и устанавливает на его выходах код, равный I, тогда дешифратор 58 вырабатывает единицу

5 и по четвертой шине 72 открывает элемент И 112 блока 17 для прохождения .тактовых импульсов, чем определяется вторая фаза работы устройства,

0 На второй фазе работы устройства тактовые импульсы поступают от генератора- 43 через элемент И 44 по первой шине 72 блока 10 управления, через элемент И 112 блока I7 на вход

5 формирователя 124 импульсов, который вырабатывает в течение тактового импульса на выходах три последовательных импульса и. , U2,.Uj в соответствии с диаграммой, приведенной на

0 фиг.8,

Импульс U с первого выхода подключает выход дешифратора 110 через группу блоков элементов И 118 по шинам 31 блока 17 формирования к вхо-5 дам элементов И первой треугольной

матрицы I и входам элементов И 39 . второй треугольной матрицы 13. Дешифратор 110 в соответствии с кодом I, D, поступившим с выходов счетчиков

0 31 и 52 блока 10 управления, по шинам 71 блока 17 подключает через группу блоков элементов И 28 первой треугольной матрицы 1 выходы регистра 24 J ,j по шинам 35 треугольной

5 матрицы 1 через группу элементов ИЛИ I1 к входу сумматора 15 и через группу блоков элементов И 39 j-, второй треугольной матрицы 13 выходы регистра 37}3 , по шинам 42 треугольной матрицы 13 через группу элементов ИЛИ 1А к входу сумматора 15.

Импульс и, с второго выхода формирователя 124 подключает выход дешифратора ПО через группу элементов И 119 по шинам 32 блока 17 формирования к входам элементов И второй группы 26; первой треугольной матрицы 1. Дешифратор 110 подключает выход сумматора 15 по шинам 29 треугольной матрии ы 1 в соответствии с кодом I, J через группу элементов И 26 j ,. к входам регистра 24 , .

Таким образом, по окончании второй фазы работы устройства на регистрах 24.

О

треугольной матрицы 1 будут занесены новые значения вероятностей состояний системы обслужива15 которая поступает с инверсного выхода схемы 61 сравнения при коде на вы ходах счетчика 51, не равном (N - 1) поступает через элемент И 115 на вход группы блоков элементов И 112 и под-

ния и счетчик 53 по очередному такто- 20 ключает выход дешифратора 111 через

вому импульсу изменит код на своих выходах.

При установлении на выходах счетчика 53 кода, равного 2, дешифратор 60 вьфабатьшает на выходе единицу, которая по пятой шине 72 блока 10 управления поступает на второй вход элемента И 113 блока 17, устройство переходит в третью фазу работы.

На третьей фазе тактовые импульсы поступают от генератора 43 через.элемент И 44 по первой шине 72 блока 10 управления через элемент И 113 блока 17 на второй вход группь блоков элементов И 120 и на вход формирователя 125. По поступлении тактового импульса выход дешифратора ПО через через группу блоков элементов И 120 по шинам 33 подключается к входам блоков элементов И 251 первой треугольной

«

матрицы 1. В соответствии с кодом I, 3, поступающим по шинам 71 блока 17 с выходов счетчиков 51 и 52, дешифратор ПО подключает выходы регистра 24j.j через группу блоков элементов И 25 , по шинам выхода 34 треугольной м атрш) 1 через группу элементов ИЛИ 2 к второму входу сумматора 3. Формирователь 125 по поступлении

тактового импульса формирует на выхо- 50 счетчика 53 блока 10 управления кода,

Импульс и, с первого выхода формирователя 125 при поступлении единицы на второй вход элемента И П4 по третьей шине 72 блока 17 с инверсного выхода яйюифратора 54 блока 10 управ-, лр.нчя, что означает ненулейой код на

равного

крывает элемент И 49, и единица, выработанная дешифратором 55 при установлении на выходах 51 кода, 55 равного 1, обнуляет счетчик 53 и счетчик 51, а по шине 73„поступает на счетный вход счетчика 129 генератора 23 импульсов времени и изменяет код на его выходах. Код с выходов

выходах счетчика 51, подключит через группу блоков элементов И 121 по шинам 126 выход дешифратора 111 к входам труппы элементов И 7. При этом в соответствии с кодом I, поступившим с выхода счетчика 52 по шинам 71 блока 17, выходы регистра 6 через группу блоков элементов И 7 и группу

элементов ИЛИ 9 подключаются к входу сумматора 3,

Импульс и с второго выхода формирователя 125 при наличии единицы на второй шине 72 блока 17 формирования,

которая поступает с инверсного выхода схемы 61 сравнения при коде на выходах счетчика 51, не равном (N - 1), поступает через элемент И 115 на вход группы блоков элементов И 112 и под-

группу блоков элементов И 122 по шинам 127 к входам группы блоков элементов И 8,,...,8. В соответствии с кодом I дешифратор 111 подключает

25 выход сумматора 3 через группу блоков элементов И 8j к входам регистра 6j. При установлении на выходах счетчика 51 кода, равного (N - 1), единица с инверсного выхода схемы 61 сравнения

30 снимается. Тогда появление единицы на выходе элемента НЕ 117 открьтает элемент И 116 для прохождения импульса и с второго выхода формирователя 125. Импульс tJ.j подключает выход де35 шифратора 111 через группу блоков элементов И 123 по шинам 128 блока 17 формирования к входам группы блоков элементов И 4j,...,4. В соответствии с кодом I дешифратор 11 1 под-

40 ключает выход сумматора 3 через группу блоков элементов И 4j к входам регистра 5 J.

Таким образом, по окончании третьей фазы работы устройства на регист45 рах 5 формируются значения вероятностей нахождения в системе обслуживания 0,1,...,N запросов.

Четвертая фаза работы устройства определяется появлением на выходах

крывает элемент И 49, и единица, выработанная дешифратором 55 при установлении на выходах 51 кода, 5 равного 1, обнуляет счетчик 53 и счетчик 51, а по шине 73„поступает на счетный вход счетчика 129 генератора 23 импульсов времени и изменяет код на его выходах. Код с выходов

ч13997

счетчика 129 заносится на регистр 130 и ЯВЛЯЕТСЯ новым значением координаты времени. При установлении на выходах счетЧика 129 кода, равного с времени окончания моделирования, схема 131 сравнения вырабатывает единицу и обнуляет триггер 133. Снятие единицы по шине входа 74 блока 23 приведет к закрытию элемента И 44 ю блока 10 управления. Режим моделирования закончен.

Формула изобретения

Устройство для моделирования систем массового обслуживания, содержащее первую треугольную матрицу регистров памяти размерностью m х т, блок управления, первую группу эле- ментов ШИ, первый сумматор, первую и вторую группы регистров памяти, первую, вторую, третью, четвертую и пят.ую группы блоков элементов И и вторую группу элементов ИЛИ, первая и вторая группы информационных входов первого сумматора соединены соответственно с выходами элементов ИЛИ первой и второй групп, а выходы первого сумматора подключены соответст- венно к информационным входам блоков элементов И первой группы, выходы которых подключены соответственно к разрядным входам регистров памяти первой группы, разрядные выходы ко- торых являются выходами устройства, выходы блока элементов И второй .группы (i 1, га) соединены соответственно с 1-ми входами элементов ИЛИ второй группы, а выходы блоков эле- ментов И третьей группы подключены к разрядным входам соответствующего регистра памяти второй группы, разрядные выходы которых подключены к информационным входам соответствующего блока элементов И второй группы, первая треугольная матрица регистров памяти размерностью m . m в i-й строке содержит j регистров памяти (j m - i + 1) и первую группу блоков элементов И, информационные входы которых соединены с разрядными выходами соответствующего регистра памяти, одноименные выходы блоков элементов И первой группы i-й строки объедине- ны между собой и подключены соответственно к i-M входам элементов ИЛИ первой группы устройства, отличающееся тем, что, с целью

с

5

0 5 0 0 5 0 g

56 12

расширения функциональных возможностей устройства за счет моделирования систем массового обслуживания с изменяющейся интенсивностью поступления запросов на обслуживание и повьшения быстродействия, оно дополнительно содержит третью, четвертую и пятую группы элементов ИЛИ, второй сумматор, генератор импульсов времени, третью группу регистров памяти, регистр памяти, блок элементов И, вторую треугольную матрицу регистров памяти размерностью тх т, блок формирования сигналов управления и блок вычисления вероятностей переходов, причем блок управления состоит из первого по седьмой элементов И, первого, второго и третьего счетчиков импульсов, с первого по седьмой дешифраторов, первой, второй и третьей схем сравнения, первого и второго триггеров, узла вычитания, регистра памяти, сумматора, элемента ИЛИ и генератора тактовых импульсов, выход которого соединен с первым входом первого элемента И, выход первого элемента И подключен к первым входам второго, третьего и четвертого элементов И, выход второго элемента И соединен со счетным входом первого счетчика и пyльcoв, выход третьего элемента И подключен к нулевому входу первого триггера, первому входу элггмента ИЛИ и первым входам пятого и шестого элементов И, выход элемента ИЛИ соединен-с входом обнуления первого счетчика импульсов, прямой выход первого триггера подключен к второму входу третьего элемента И, а инверсный выход - к второму входу второго элемента И, разрядные выходы первого счетчика импульсов подключены соответственно к информационным . входам первой группы сумматора, входам первого и второго дешифраторов и информационным вхбдам первой группы первой схемы сравнения, выход Равно которой соединен с единичным входом первого триггера, выход шестого элемента И подключен к счетному входу второго счетчика импульсов, к разрядным выходам которого подключены информационные входы второй группы сумматора, входы третьего дешифратора, информационные входы второй и третьей схем сравнения и входы узла вычитания, выход которого соединен с установочным входом первой схемы

13

сравнения, выход Равно второй cxeмы сравнения подключен к единичному входу второго триггера, прямой выход которого соединен с вторым входом пятого элемента И, выход которого подключен к входу обнуления второго счетчика импульсов, нулевому входу второго триггера и счетному входу третьего счетчика импульсов, инверсный выход второго триггера соединен с вторым входом шестого элемента И, разрядные выходы третьего счетчика импульсов подключены соответственно к входам четвертого, пятого, шестого ;И седьмого дешифраторов, выход чет- ;Вертого дешифратора соединен с вто™ рым входом четвертого элемента И, iразрядные выходы сумматора подключе- |ны соответственно к разрядным входам if регистра памяти, выход второго дешиф- ратора соединен с первым входом седь- |Мого элемента И, выход которого лод- :ключей к входу обнуления третьего :счетчика импульсов и второму входу I элемента ИЛИ, выход шестого дешифра-- тора соединен с вторым входом седьмого элемента И, первая треугольная матрица регистров памяти дополнительно в каждой-строке содержит вторую, третью и четвертую группы блоков элементов И, число блоков элементов Ив I каждой группе равно числу регистров ;памяти в строке, выходы блоков эле- iментов И второй группы в каждой ;строке соединены с разрядными входами соответствующего регистра памяти данной строки, разрядные выходы регистра памяти подключены к информа- ; ционным входам соответствунидих бло- ков элементов И третьей и четвертой групп, вторая треугольная матрица регистров памяти в каждой строке содержит j регистров памяти, j блоков элементов И первой и второй групп, причем в каждой строке выходы блока элементов И первой группы соединены с разрядными входами соответствующего регистра памяти, разрядные выходы которого подключены к информационным входам соответствующего блока элементов И второй группы, блок вычисления вероятностей переходов содержит с первого по четвертьй узлы утмножения, с первого по четвертый регистры памяти, с первого по седьмой элементы И, первый, второй и третий блоки элементов И, формирователь импульсов, с первого по шестой дешифраторы.

99756ii.

группу элементов ИЛИ и сумматор, причем в блоке вычисления вероятностей переходов информационные входы перg вой, второй, третьей и четвертой групп сумматора подключены соответственно к разрядным выходам первого, второго, третьего и четвертого регистров памяти, разрядные входы ко- 10 торых соединены с выходами соответственно первого, второго, третьего и четвертого узлов умножения, информационные входы первого, второго и третьего блоков элементов И подключены

15 к выходам соответственно третьего, четвертого и шестого дешифраторов, выходы первого, второго и третьего блоков элементов И соединены соответственно с первыми, вторыми и третьи20 ми входами элементов ИЛИ группы, выход первого элемента И блока вычисления вероятностей переходов соединен с входом разрешения умножения первого узла умножения, выход второго эле25 мента И подключен к обнуляющему входу первого регистра памяти, выход третьего элемента И соединен с входом разрешения умножения второго узла умножения, выход четвертого эле30 мента И подключен к обнуляющему входу второго регистра памяти, выход пятого элемента И соединен с входом разрешения третьего узла умножения, выход шестого элемента И соединен с

35 обнуляющим входом третьего регистра памяти, выход седьмого элемента И подключен к входу разрешения умноже кия четвертого узла умножения, а об- „ нуляющий вход четвертого регистра

40 памяти соединен с выходом второго элемента И блока вычисления вероятностей переходов, первый выход формирователя импульсов подключен к управляющему входу третьего блока-элемен45 тов И и первому входу первого элемента И, второй выход формирователя импульсов соединен с управляющим входом второго блока элементов И и выми входами пятого и седьмого эле50 ментов И, третий выход формирователя импульсов подключен к управлян цему входу первого блока элементов И и первому входу третьего элемента И блока вычисления вероятностей перехо55 дов, блок формирования сигналов управления содержит первый и второй дешифраторы, с первого по пятый элементы И, элемент НЕ, с первого по шестой блоки элементов И, первый и

15 1

второй формирователи импульсов, причем в блоке формирования сигналов управления выход первого элемента И соединен с вхбдом первого формирователя импульсов, первый и второй выходы которого подключены к управляющим входам первого и второго блоков элементов И, информационные входы которых и информационные входы третьего блока элементов И соединены соответственно с выходами перйого дешифратора, выход второго элемента И соединен с управляющим входом третьего блока элементов И и входом второго формирователя импульсов, первый выход которого соединен с первым входом третьего элемента И, второй выход второго формирова:теля импульсов блока формирования сигналов управления подключен к первым входам четвертого и пятого элементов И, второй вход пятого элемента И соединен с выходом элемента НЕ, а выходы третьего, четвертого и пятого элементов И подключены к управляющим входам соответственно четвертого, пятого и шестого блоков элементов И, информационные входы которых соединены соответ

ственно с выходами второго дешифрато- ЗО мационные входы которого соединены

ра блока формирования сигналов управления, выходы первого сумматора устройства соединены соответственно с информационными входами блоков элементов И третьей группы устройства, управляющие входы которых подключены к выходам пятого блока элементов И блока формирования сигналов управления, выходы щес гого блока элементов И которого соединены соответственно с управляющими входами блоков элементов И первой группы устройства, управляющие входы блоков элементов И второй группы которого подключены соответственно к выходам четвертого блока элементов И блока формирования сигналов управления, первая группа входов первого дешифратора и входы второго дешифратора которого подключены соответственно к разрядным вьосо- 50, мента И которого соединен с входом

дам второго счетчика импульсов блока управления, разрядные выходы первого счетчика импульсов которого соединены соответственно с входами второй

группы первого дешифратора блока фор- gg чика импульсов которого соединены со- мирования сигналов управления, пер- ответственно с информационными вхо- вый вход первого элемента И и первый дами первой группы второго, третьего, вход второго элемента И которого сое- четвертого и шестого дешифраторов динены с выходом первого элемента И блока вычисления вероятностей переI 6

блока формирования сигналов управления, выход Не равно первой схемы сравнения которого подключен к входу элемента НЕ и второму входу четвертого элемента И блока формирования сигналов управления, второй вход второго элемента И которого соединен с выходом седьмого дешифратора блока управления, выход пятого дешифратора которого подключен к второму входу первого элемента И блока формирования сигналов .управления , второй вход третье-го элемента И которого соединен с 5 первым выходом первого дешифратора блока управления и вторым входом третьего элемента И блока вычисления вероятностей переходов, первые входы второго и четвертого элементов И которого соединены соответственно с первым выходом третьего дешифратора и вторым выходом первого дешифратора блока управления, выход третьего элемента И которого подключен к вторым входам второго, четвертого и шестого элементов И, входу формирователя импульсов блока вычисления вероятное- тей переходов и управляющему входу блока элементов И устройства, инфор0

5

соответственно с разрядными выходами регистра памяти устройства,, а выходы блока элементов И устройства подключены соответственно к информационным

35 входам первой группы второго и четвертого узлов умножения блока вычисления вероятностей переходов, входы первого и -пятого дешифраторов которого соединены соответственно с разряд40 ными выходами регистра памяти блока управления, второй выход третьего дешифратора которого подключен к вто- рым входам первого и седьмого элементов И блока вычисления вероятностей45 переходов, вторые входы пятого и шестого элементов И которого соединены . соответственно с выходами Не равно и Равно третьей схемы сравнения блока управления, выход седьмого элезапуска генератора импульсов времени, выход которого подключен к второму входу первого элемента И блока управления, разрядные выходы первого счет17

ходов, информационные входы второй группы второго, третьего, четвертого и шестого дешифраторов которого соединены соответственно с разрядными выходами второго счетчика импульсов блока управления, разрядные выходы регистров памяти третьей группы устройства соединены с информационными входами соответствующих блоков элементов И четвертой и пятой групп устройства, управляющие входы блоков элементов И .четвертой группы устройства соединены соответственно с выходами пятого дешифратора блока вычисления вероятностей переходов, выходы первого дешифратора которого подключены соответственно к управляющим входам блоков элементов И пятой :группы устройства, выходы которых j подключен1.1 соответственно к информа- Iционным входам первой группы третье- I го узла умножения блока вычисления I вероятностей- переходов, информацион- :иые входы первой группы первого узла умножения которого соединены соответственно с выходами блоков элементов И четвертой группы устройства, i-й выход второго дешифратора блока вычисления вероятностей пере;содов соединен с управлянйцими входами всех блоков элементов И первой группы i-й : строки второй треугольной матрицы ре- ; гистров памяти, информационные входы всех блоков элементов И первой группы которой подключены соответственно к выходам сумматора блока вычисления вероятностей переходов, i-й выход элемента ИЛИ группы которого подклю- I чей к управляющим входам блоков зле- : ментов И третьей группы 1-й строки первой треугольной матрицы регистров памяти, выходы блоков элементов И третьей группы i-й строки которой подключены соответственно к i-м входам . элементов ИЛИ третьей группы уст18

выходы которых соединены соответственно с информяиионными входами второй группы nepBf)i o, второт о,

третьего и четвертого узлов умножения блока вычисления вероятностей переходов, i-й выход третьего блока элементов И блока формирования сигналов управления соединен соответственно с управляющими входами блоков элементов И первой группы i-й строки первой треугольной матрицы регистров памяти, i-й выход второго блока элементов И блока формирования сигналов

;5шравления подключён к управляющим входам блоков элементов И второй группы i-й строки первой треугольной матрицы регистров памяти, выходы блоков элементов И четвертой группы i-й

строки которой подключены соответственно к входам i-й группы элементов ИЛИ четвертой группы устройства, выходы которых соединены соответственно с информационными входами первой

группы второго су1чматора устройства,

выходы которого подключены соответст- , венно к информационным .входам всех блоков элементов И второй группы первой треугольной матрицы регистров

памяти, управляющие входы блоков элементов И четвертой группы i-й строки первой треугольной матрицы регистров памяти подключены к выходу пер- вого блока элементов И блока формиро

вания сигналов управления и управляющим входам блоков элементов И второй группы i-й строки второй треугольной матрицы регистров памяти, одно имен- ные выходы блоков элементов И второй

группы i-й строки которой объединены и подключены соответственно к входам i-й группы элементов ИЛИ пятой группы устройства, выходы которых соединены соответственно с информационными входами второй группы второго сумматора устройства.

//

/, ..

0ui.1

Фцв.З

fe

Л

9

«S

JT

v

w

ev.

/ / / v / v

:::

/ /V

I

oo

(

/

ем «О

o

«o

00

«Г

/Vv

J

x v

I

r±

РигВ

Ро,о

Л.1

. (

у« л/ 1 Лс УТ М X

Т л ,

Фб/г.5

ВНИИПИ заказ 2667/49 Тираж 70А

йройзв-подагр. пр-тие, г. Ужгород, ул. Проектная. 4

PO.H-Z ,N-1 0,Ы

P1,ff-1

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования сетевых графов | 1981 |

|

SU1013965A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-05-30—Публикация

1986-12-02—Подача