Изобретение относится к вычислительной технике и может быть использовано для определения вероятностных характеристик систем обслужирпния

Целью изобретения является расширение функдаопальных возможностей устройства за счет моделирования систем массового обслуживания с подключением резерва с изменяющейся интенсивностью поступления запросов на обслуживание.

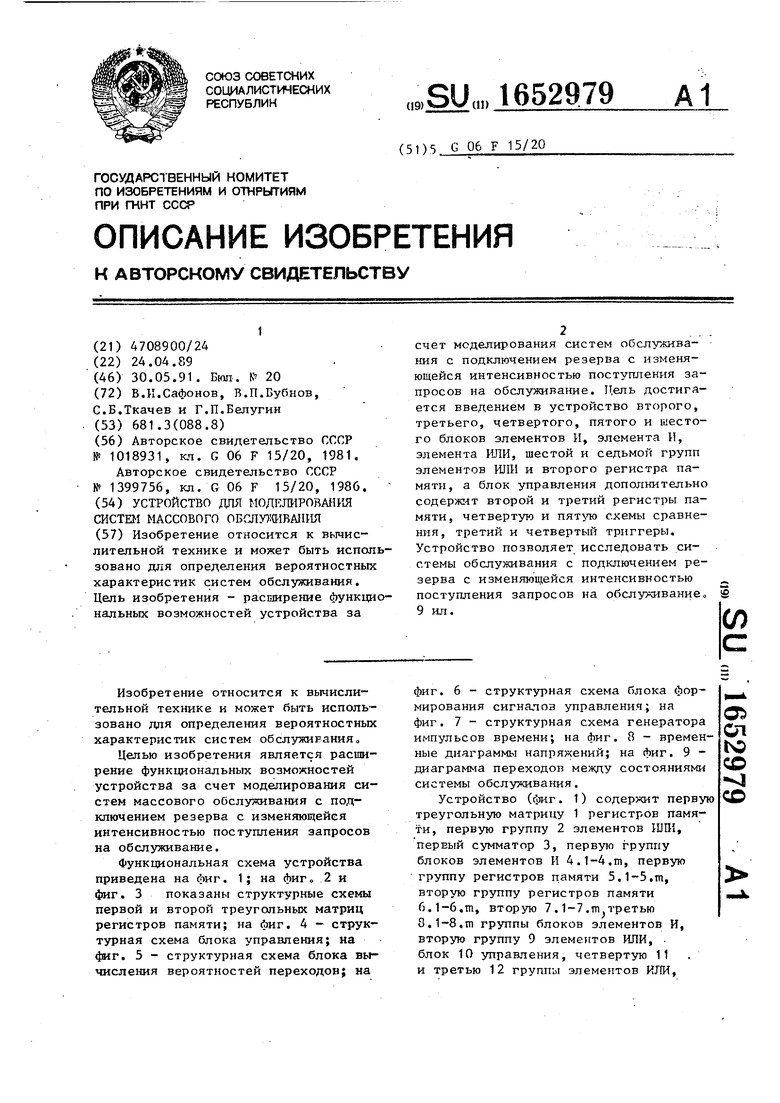

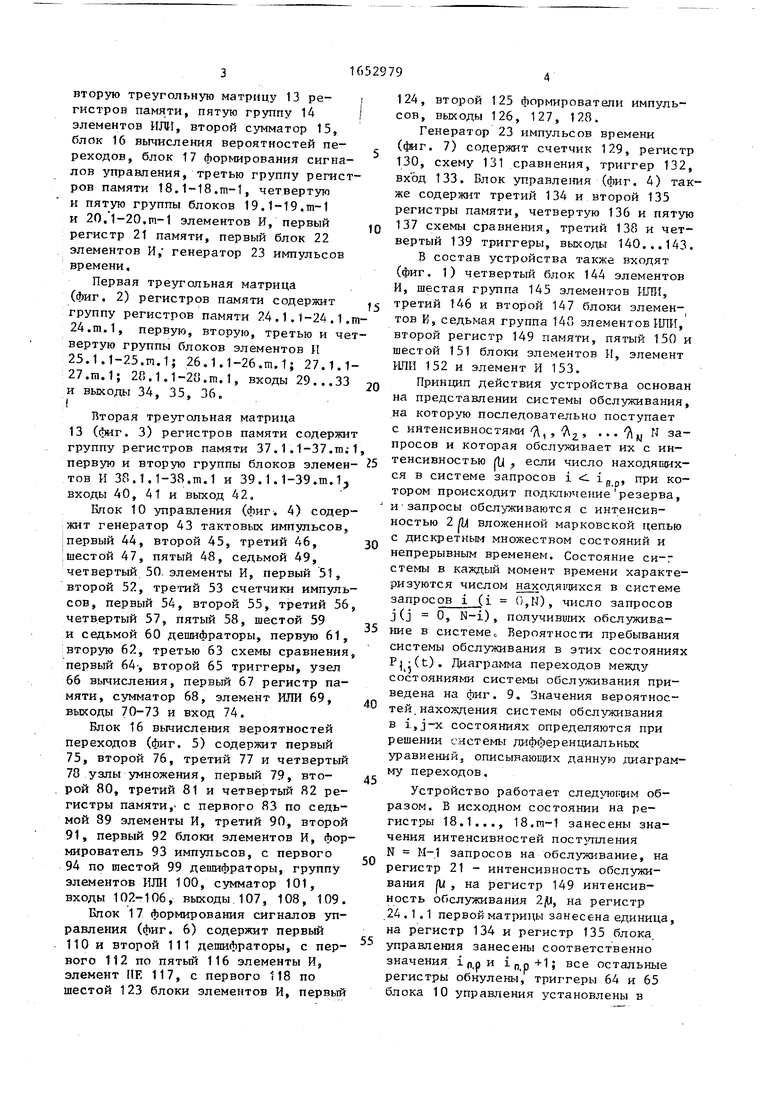

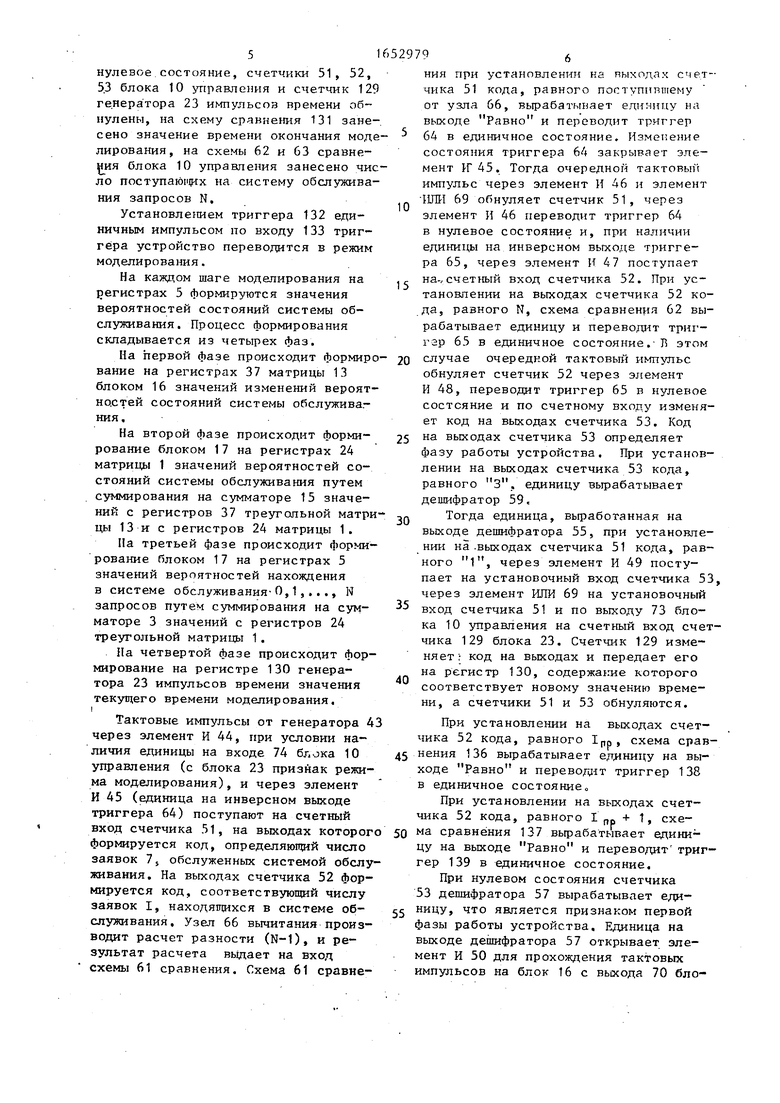

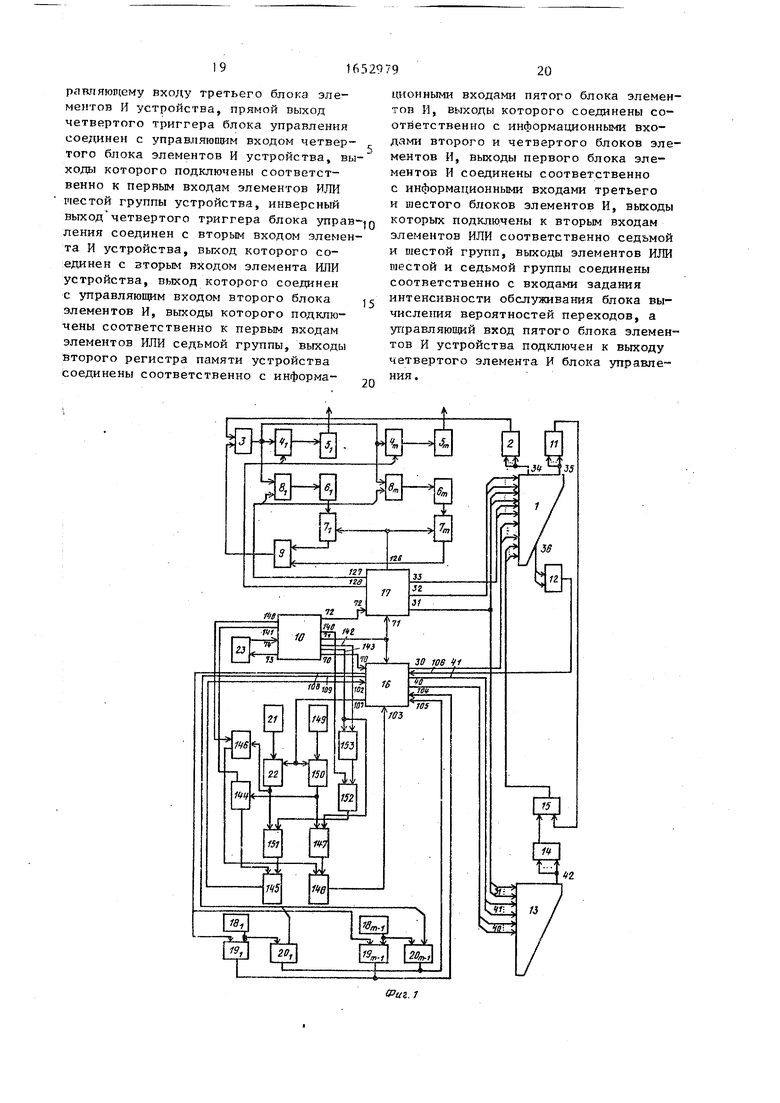

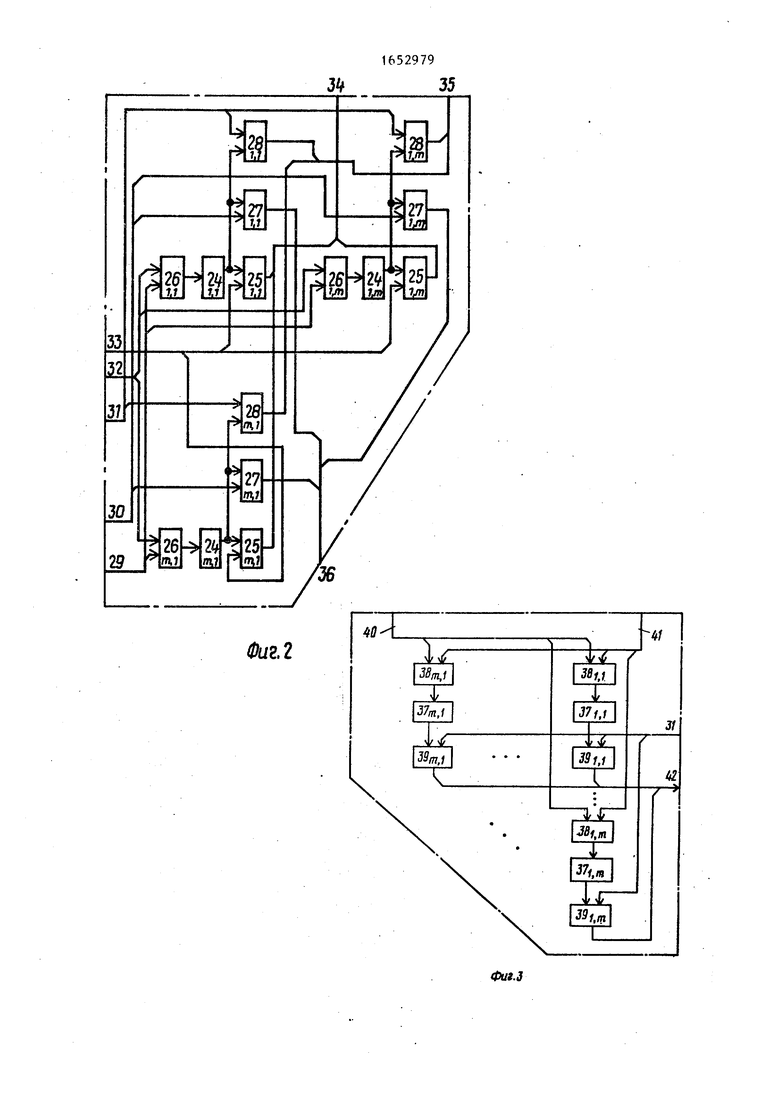

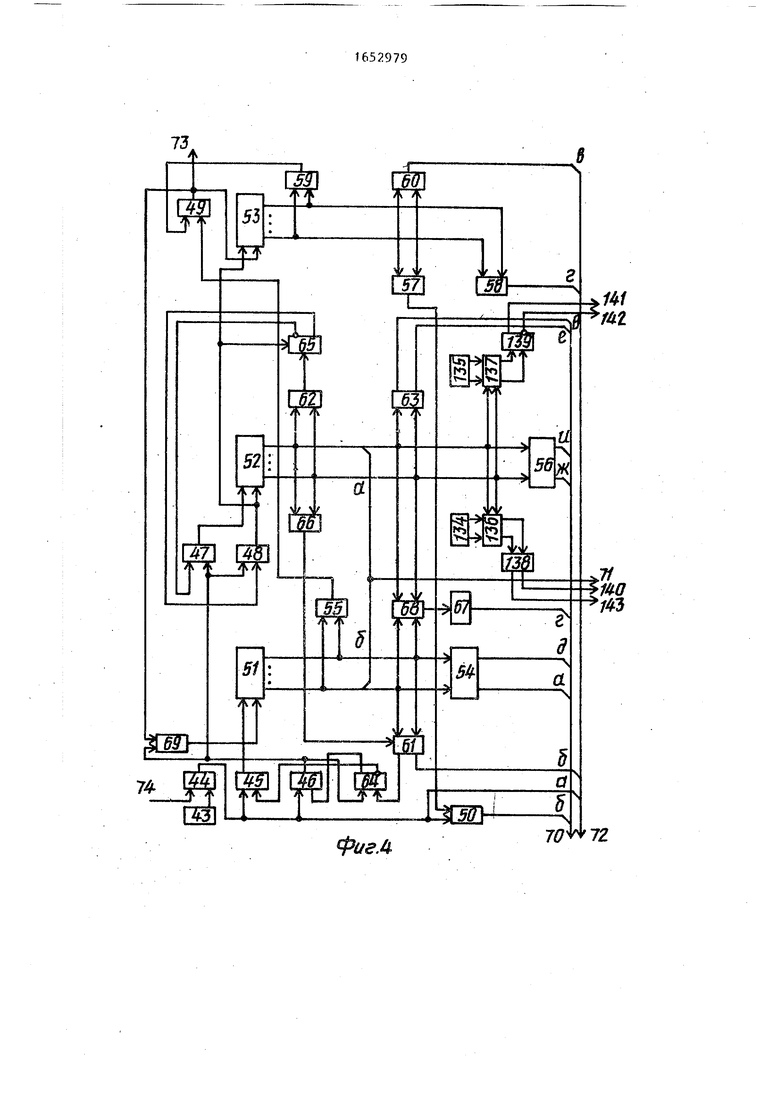

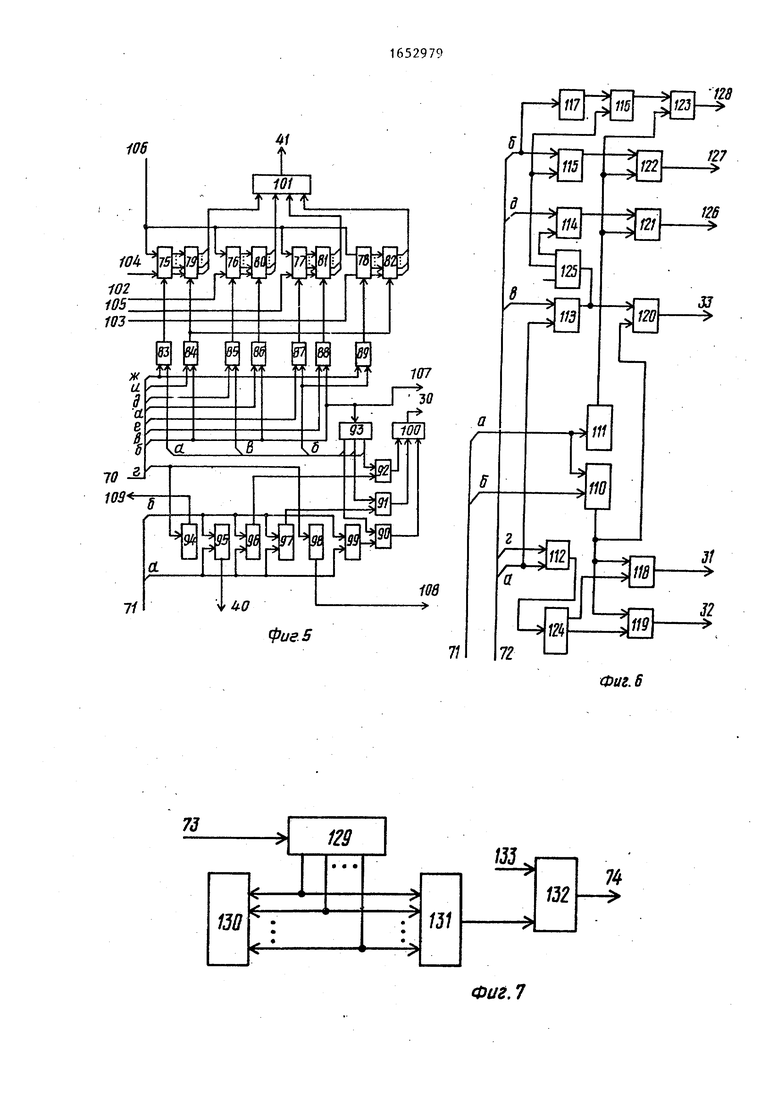

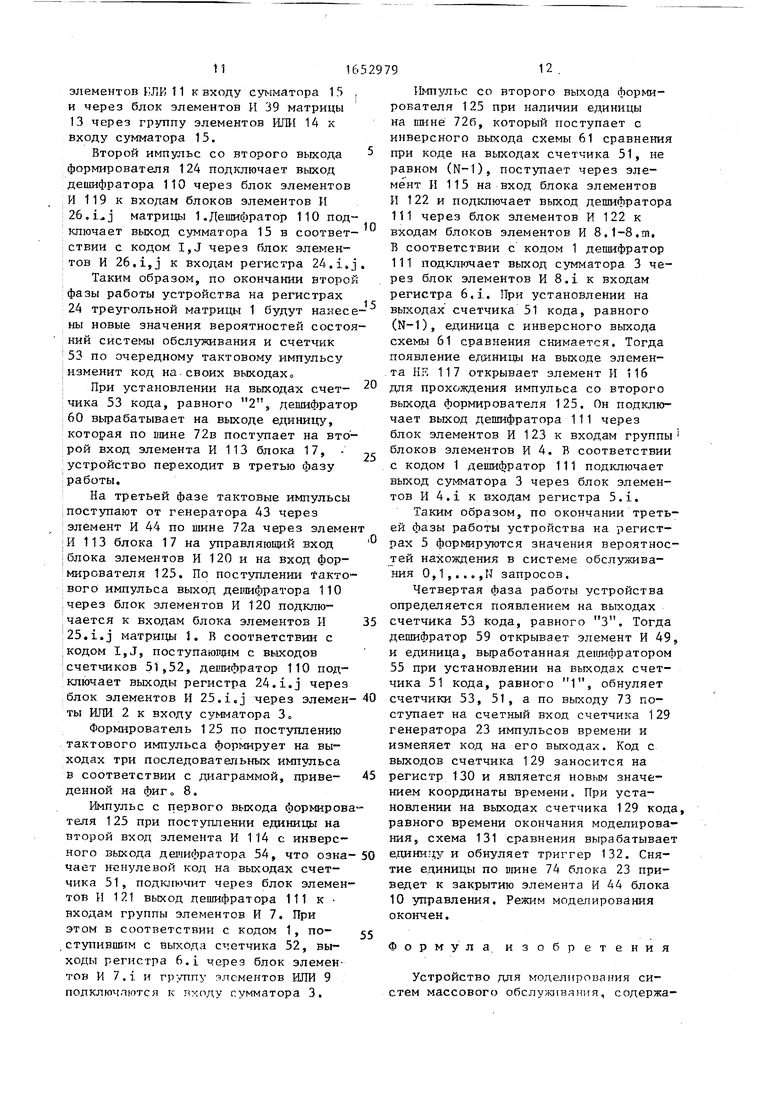

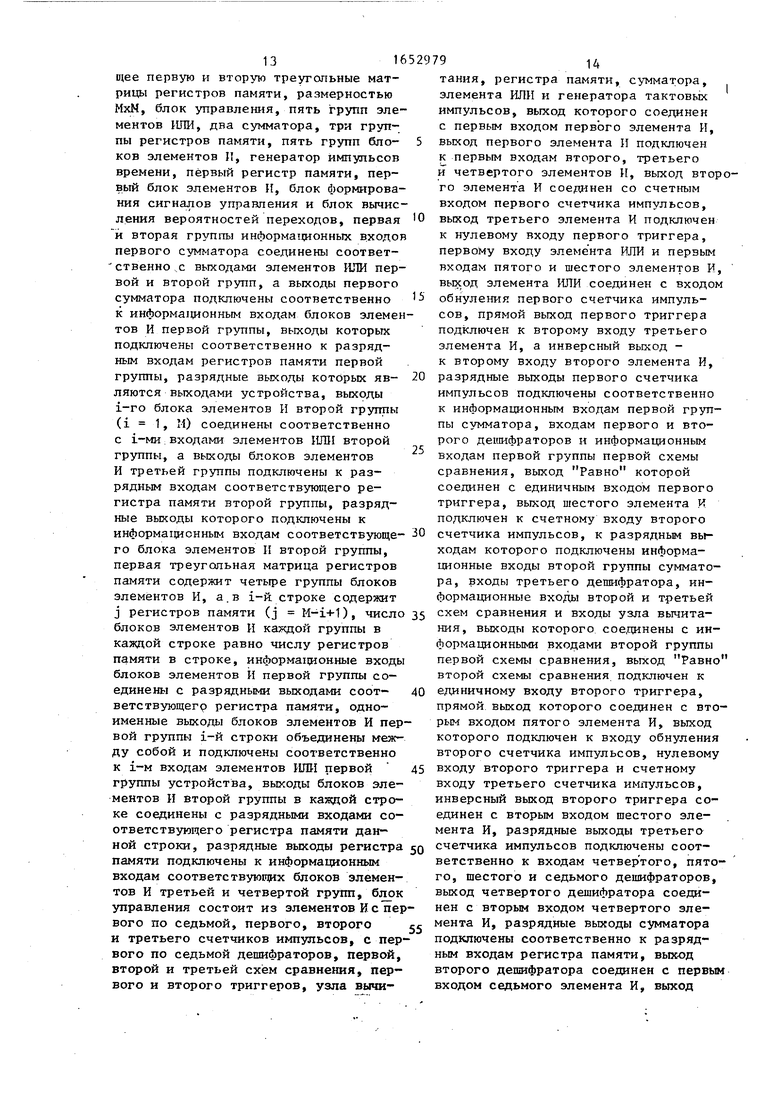

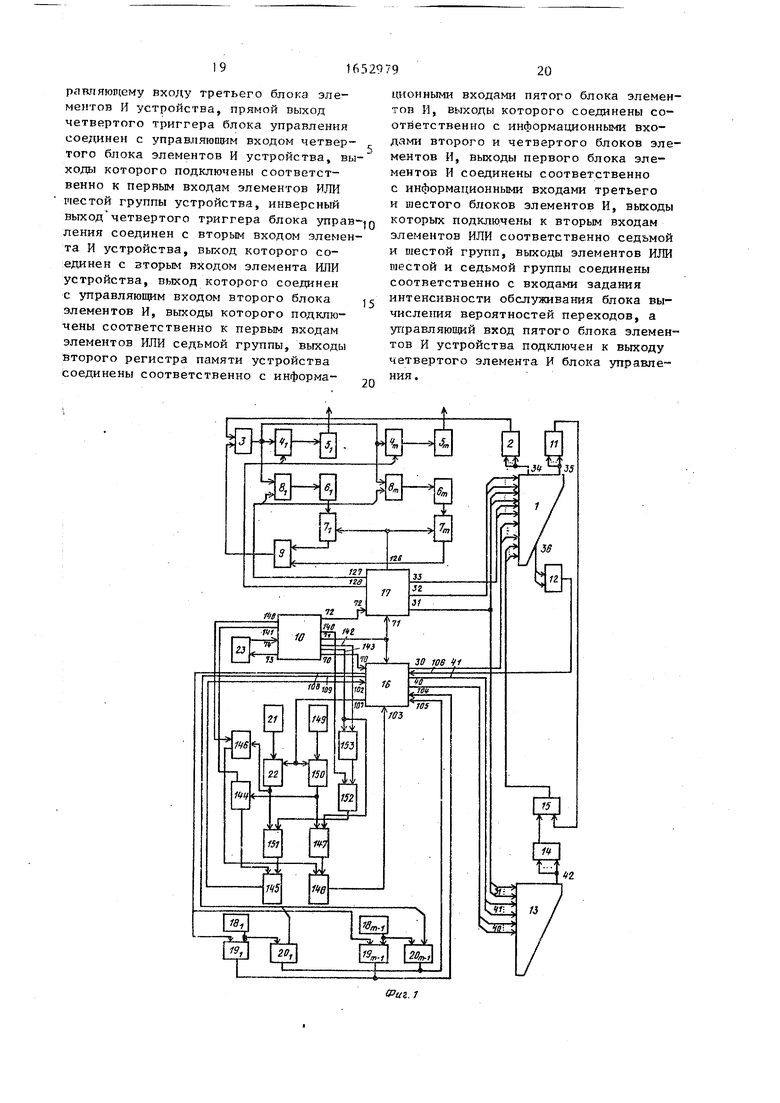

Функциональная схема устройства приведена на фиг. 1; на фиг 2 и фиг. 3 показаны структурные схемы первой и второй треугольных матриц регистров памяти; на фиг. 4 - структурная схема блока управления; на фиг. 5 - структурная схема блока вычисления вероятностей переходов; на

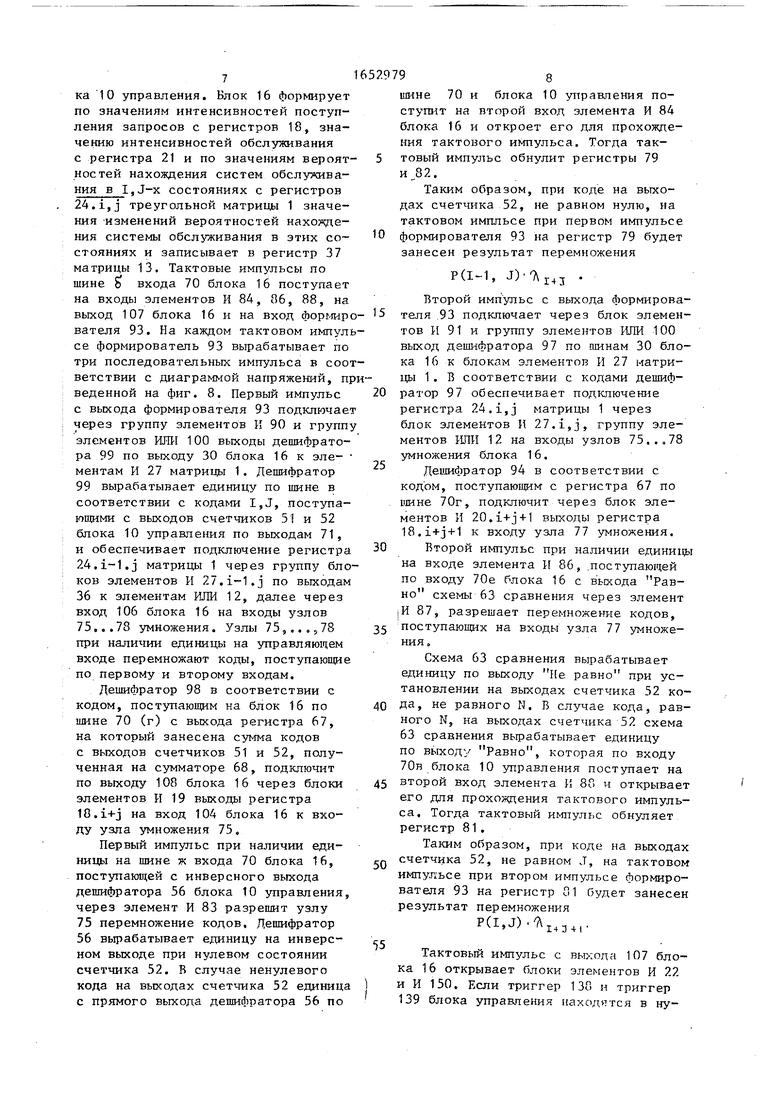

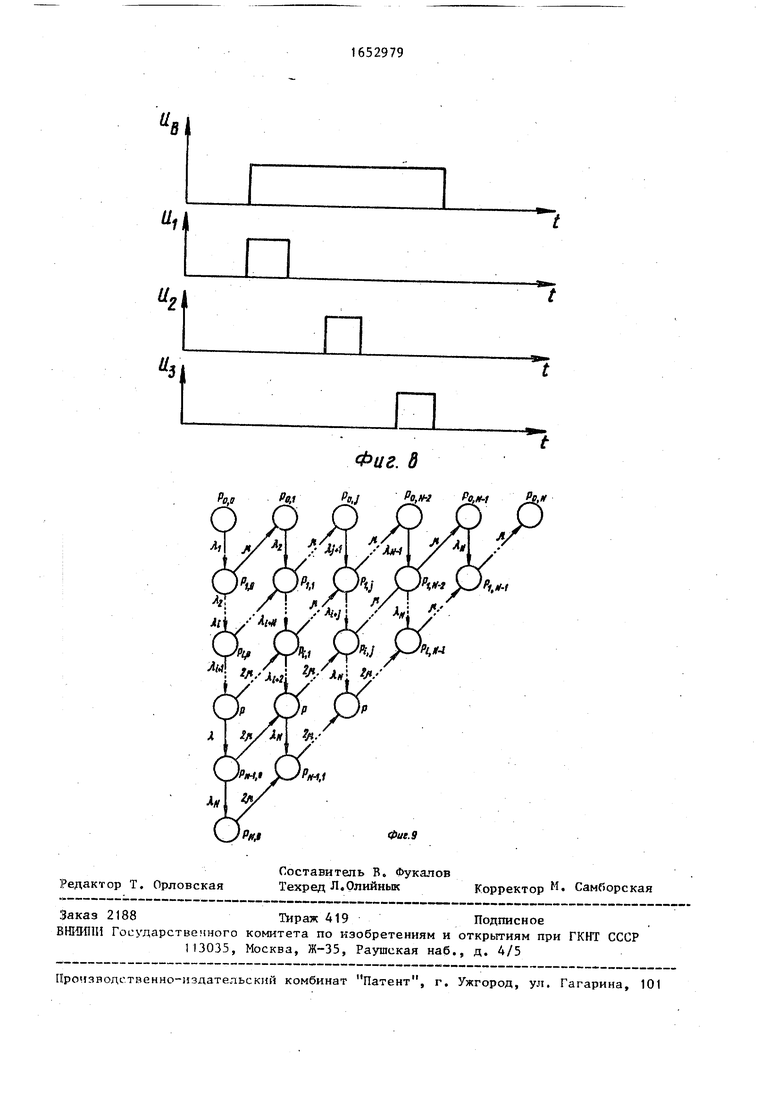

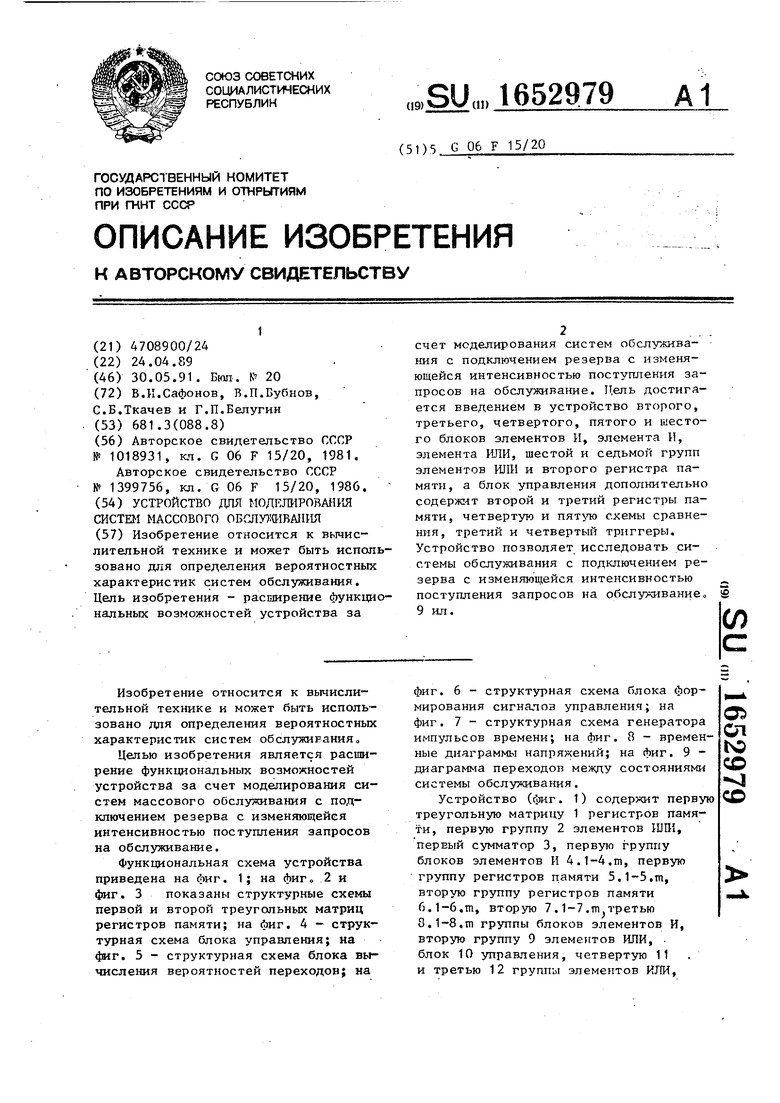

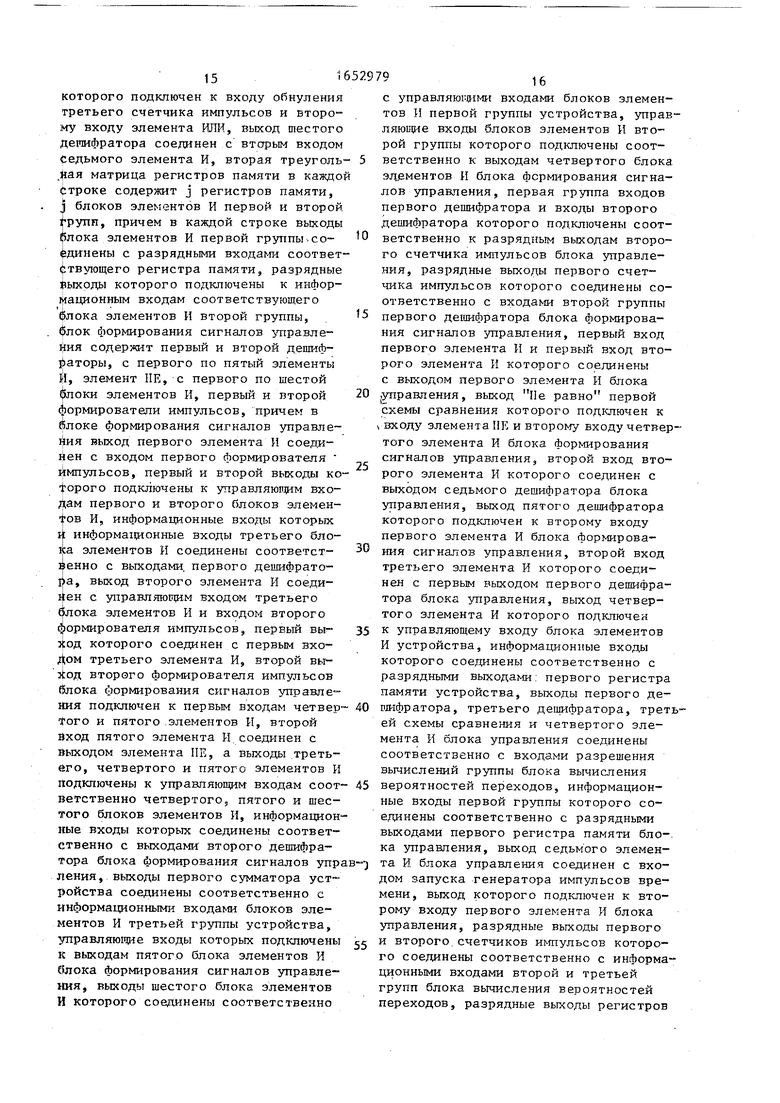

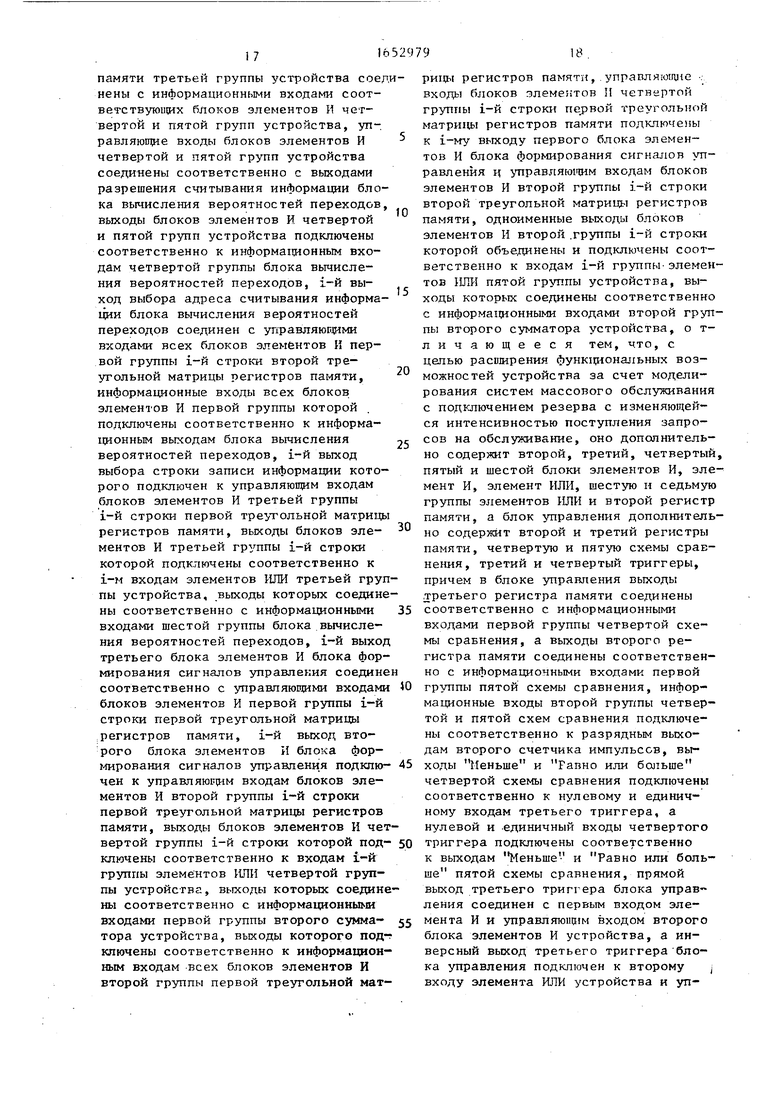

фиг. 6 - структурная схема блока формирования сигналов управления; на фиг. 7 - структурная схема генератора импульсов времени; на фиг. 8 - временные диаграммы напряжений; на фиг. 9 - диаграмма переходов между состояниями системы обслуживания.

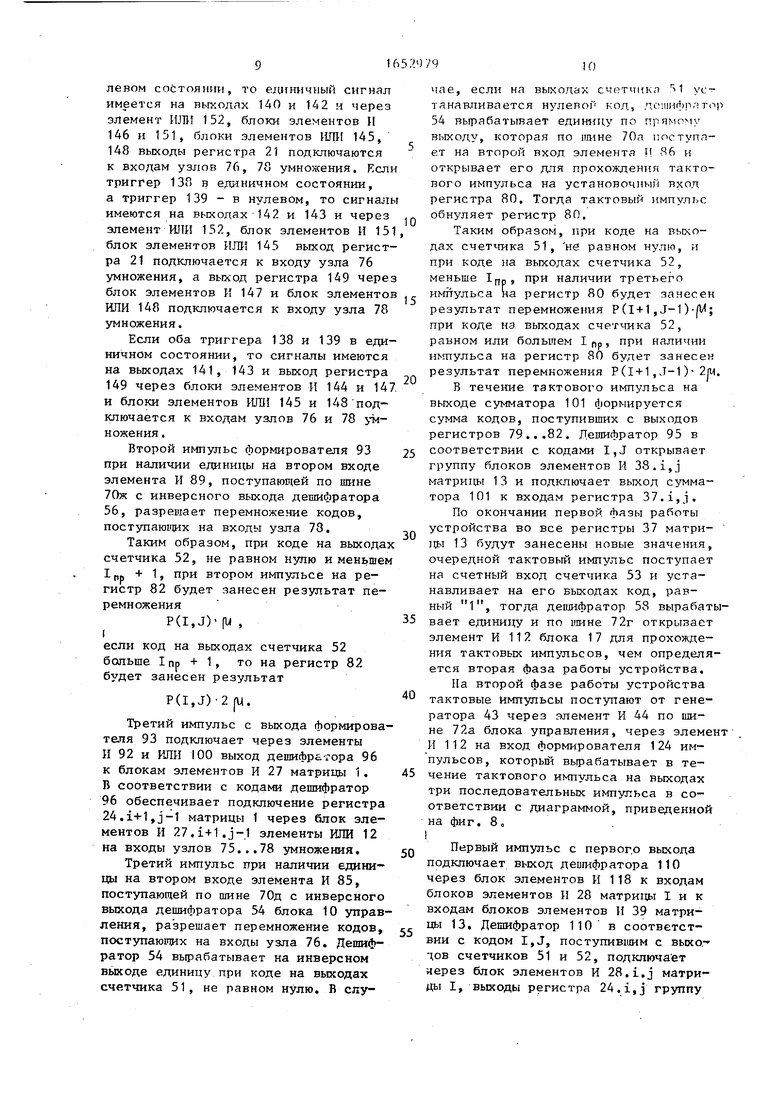

Устройство (фиг. 1) содержит первую треугольную матрицу 1 регистров памяти, первую группу 2 элементов ИЛИ, первый сумматор 3, первую группу блоков элементов И 4.1-4.т, первую группу регистров памяти 5.1-5.т, вторую группу регистров памяти 6.1-6.т, вторую 7 .1-7.тп третью S.1-8.m группы блоков элементов И, вторую группу 9 элементов ИЛИ, блок 10 управления, четвертую 11 и третью 12 группы элементов ИЛИ,

0 СП N3

СО

vl

СО

вторую треугольную матрицу 13 регистров памяти, пятую группу 14 i элементов ИЛИ, второй сумматор 15, блок 16 вычисления вероятностей переходов, блок 17 формирования сигналов управления, третью группу регистров памяти 18.1-18.m-1, четвертую и пятую группы блоков 19.1-19.m-1 и 20.1-20.m-1 элементов И, первый регистр 21 памяти, первый блок 22 элементов И, генератор 23 импульсов времени.

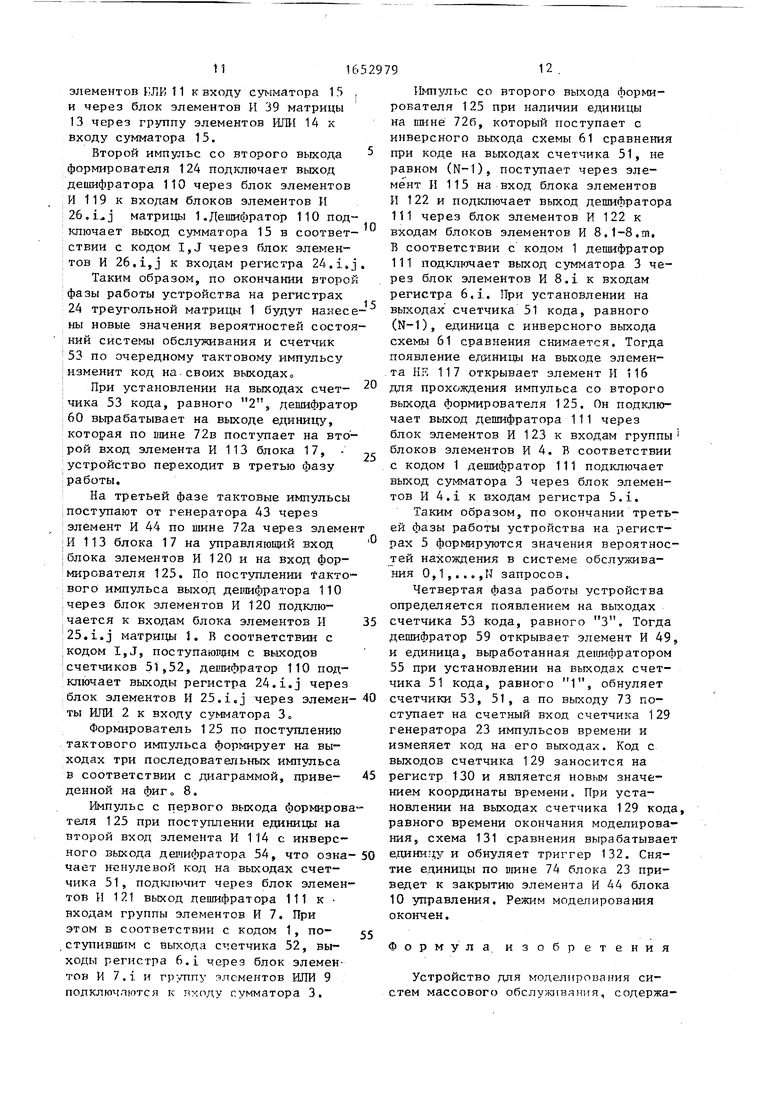

Первая треугольная матрица (фиг. 2) регистров памяти содержит группу регистров памяти 24 .1.1-2Ј.1.т 24.т.1, первую, вторую, третью и четвертую группы блоков элементов И 25.1.1-25.п.1; 26.1.1-26.т.1; 27.1.1- 27.т.1; 20.1.1-2«.т.1, входы 29...33 и выходы 34, 35, 36. I

Вторая треугольная матрица 13 (фиг. 3) регистров памяти содержит группу регистров памяти 37.1.1-37.т;1 первую и вторую группы блоков элемен- тов И ЗГ. 1.1-38.т. 1 и 39 . 1.1-39.т. 1., входы 40, 41 и выход 42.

Блок 10 управления (фиг. 4) содержит генератор 43 тактовых импульсов, первый 44, второй 45, третий 46, шестой 47, пятый 48, седьмой 49, четвертый 50 элементы И, первый 51, второй 52, третий 53 счетчики импульсов, первый 54, второй 55, третий 56, четвертый 57, пятый 58, шестой 59 и седьмой 60 дешифраторы, первую 61, вторую 62, третью 63 схемы сравнения, первый 64, второй 65 триггеры, узел 66 вычисления, первый 67 регистр памяти, сумматор 68, элемент ИЛИ 69, выходы 70-73 и вход 74.

Блок 16 вычисления вероятностей переходов (фиг. 5) содержит первый 75, второй 76, третий 77 и четвертый 70 узлы умножения, первый 79, вто- рой 80, третий 81 и четвертый 82 регистры памяти, с первого 83 по седьмой 89 элементы И, третий 90, второй 91, первый 92 блоки элементов И, формирователь 93 импульсов, с первого 94 по тестой 99 дешифраторы, группу элементов ИЛИ 100, сумматор 101, входы 102-106, выходы 107, 108, 109. Блок 17 формирования сигналов управления (фиг. 6) содержит первый 110 и второй 111 дешифраторы, с первого 112 по пятый 116 элементы И, элемент НЕ 117, с первого 118 по шестой 123 блоки элементов И, первый

0 $ Q

5

0

124, второй 125 формирователи импуль- соп, пыходы 126, 127, 128,

Генератор 23 импульсов времени (фиг. 7) содержит счетчик 129, регистр 130, схему 131 сравнения, триггер 132, вход 133. Блок управления (фиг. 4) также содержит третий 134 и второй 135 регистры памяти, четвертую 136 и пятую 137 схемы сравнения, третий 138 и четвертый 139 триггеры, выходы 140...143.

В состав устройства также нходят (фиг. 1) четвертый блок 144 элементов И, шестая группа 145 элементов ИЛИ, третий 146 и второй 147 блоки элементов К, седьмая группа 14 элементов ИЛИ, второй регистр 149 памяти, пятый 150 и шестой 151 блоки элементов И, элемент ИЛИ 152 и элемент И 153.

Принцип действия устройства основан на представлении системы обслуживания, на которую последовательно поступает с интенсивноетями Я ( , ft , .. . w N запросов и которая обслуживает их с интенсивностью Яд , если число находящихся в системе запросов i i ino, при котором происходит подключение резерва, и запросы обслуживаются с интенсивностью 2 (А вложенной марковской цепью с дискретным множеством состояний и непрерывным временем. Состояние си- стемы в каждый момент времени характеризуются числом находящихся в системе запросов i(i ,Ю число запросов j(j 0, N-i), получивших обслуживание в системе,. Вероятности пребывания системы обслуживания в этих состояниях Pj (t). Диаграмма переходов между состояниями системы обслуживания приведена на фиг, 9. Значения вероятностей нахождения системы обслуживания в i,j-x состояниях определяются при решении .истемы дифференциальных уравнений, описывающих данную диаграмму переходов.

Устройство работает следуюжм образом. В исходном состоянии на регистры 18.1..., 18.Ш-1 занесены значения интенсивностей поступления N М-1 запросов на обслуживание, на регистр 21 - интенсивность обслуживания (Ц , на регистр 149 интенсивность обслуживания 2|U, на регистр 24 . 1 .1 первой матрицы занесена единица, на регистр 134 и регистр 135 блока управления занесены соответственно значения i „n и inn+1; все остальные регистры обнулены, триггеры 64 и 65 блока 10 управления установлены в

нулевое СОСТОЛИЦР,

S1 Ч2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1399756A1 |

| Устройство для сжатия и восстановления информации | 1983 |

|

SU1149295A1 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Устройство для редактирования информации | 1981 |

|

SU980099A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| Устройство для решения системы линейных алгебраических уравнений | 1986 |

|

SU1405073A1 |

| Многоканальный многомерный цифровой коррелометр | 1984 |

|

SU1187177A1 |

| Устройство для моделирования биматричных игр | 1986 |

|

SU1388847A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Устройство для контроля и управления технологическими процессами испытаний и тренировки фотоэлектронных умножителей | 1988 |

|

SU1517041A1 |

Изобретение относится к вычислительной технике и может быть использовано для определения вероятностных характеристик систем обслуживания. Цель изобретения - расширение функциональных возможностей устройства за счет моделирования систем обслуживания с подключением резерва с изменяющейся интенсивностью поступления запросов на обслуживание. Цель достигается введением в устройство второго, третьего, четвертого, пятого и шестого блоков элементов И, элемента И, элемента ИЛИ, шестой и седьмой групп элементов ИЛИ и второго регистра памяти, а блок управления дополнительно содержит второй и третий регистры памяти, четвертую и пятую схемы сравнения, третий и четвертый триггеры. Устройство позволяет исследовать системы обслуживания с подключением резерва с изменяющейся интенсивностью поступления запросов на обслуживание 9 ил. (С С/)

ка 10 управления. Клок 16 формирует по значениям интенсивностей поступления запросов с регистров 18, значению интенсивностей обслуживания с регистра 21 и по значениям вероятностей нахождения систем обслужива- ния в I,J-x состояниях с регистров 24.i,j треугольной матрицы 1 значения изменений вероятностей нахождения системы обслуживания в этих состояниях и записывает в регистр 37 матрицы 13. Тактовые импульсы по шине о входа 70 блока 16 поступает на входы элементов И 84, 86, 88, на выход 107 блока 16 и на вход форпиро вателя 93. На каждом тактовом импульсе формирователь 93 вырабатывает по три последовательных импульса в соответствии с диаграммой напряжений, прведенной на фиг. 8. Первый импульс с выхода формирователя 93 подключает через группу элементов И 90 и группу элементов ИЛИ 100 выходы дешифратора 99 по выходу 30 блока 16 к эле- ментам И 27 матрицы 1. Дешифратор 99 вырабатывает единицу по шине в соответствии с кодами I,J, поступающими с выходов счетчиков 5 и 52 блока 10 управления по выходам 71, и обеспечивает подключение регистра 24.i-1.j матрицы 1 через группу блоков элементов И 27.1-1.J по выходам 36 к элементам ИЛИ 12, далее через вход 106 блока 16 на входы узлов 75... 78 умножения. Узлы 75,..., 78 при наличии единицы на управляющем входе перемножают коды, поступающие по первому и второму входам.

Дешифратор 98 в соответствии с кодом, поступающим на блок 16 по шине 70 (г) с выхода регистра 67, на который занесена сумма кодов с выходов счетчиков 51 и 52, полученная на сумматоре 68, подключит по выходу 108 блока 16 через блоки элементов И 19 выходы регистра 1B.i+j на вход 104 блока 16 к входу узла умножения 75.

Первый импульс при наличии единицы на шине ж входа 70 блока 16, поступающей с инверсного выхода дешифратора 56 блока 10 управления, через элемент И 83 разрешит узлу 75 перемножение кодов. Дешифратор 56 вырабатывает единицу на инверсном выходе при нулевом состоянии счетчика 52. В случае ненулевого кода на выходах счетчика 52 единица с прямого выхода дешифратора 56 по

10

202979в

шине 70 и блока 10 управления поступит на второй вход элемента И 84 блока 16 и откроет его для прохождения тактового импульса. Тогда тактовый импульс обнулит регистры 79 и. 82.

Таким образом, при коде на выходах счетчика 52, не равном нулю, на тактовом импльсе при первом импульсе формирователя 93 на регистр 79 будет занесен результат перемножения

5

0

0

5

0

5

0

5

PU-1, J)l(Ar + 3

Второй импульс с выхода формирователя 93 подключает через блок элементов И 91 и группу элементов 11ГГИ 100 выход дешифратора 97 по шинам 30 блока 16 к блоклм элементов И 27 матрицы 1 , В соответствии с кодами дешифратор 97 обеспечивает подключение регистра 24.i,j матрицы 1 через блок элементов И 27.i,j, группу элементов ИЛИ 12 на входы узлов 75... 78 умножения блока 16.

Дешифратор 94 в соответствии с кодом, поступающим с регистра 67 по шине 70г, подключит через блок элементов И 20.1+J+1 выходы регистра 18.1+J+1 к входу узла 77 умножения.

Второй импульс при наличии единицы на входе элемента И 86, поступающей по входу 70е блока 16 с выхода Равно схемы 63 сравнения чсфез элемент И 87, разрешает перемножение кодов, поступающих на входы узла 77 умножения .

Схема 63 сравнения вырабатывает единицу по выходу Не равно при установлении на выходах счетчика 52 кода, не равного N. В случае кода, равного N, на выходах счетчика 52 схема 63 сравнения вырабатывает единицу по выходу Равно, которая по входу 70в блока 10 управления поступает на второй вход элемента И 80 и открывает его для прохождения тактового импульса. Тогда тактовый импульс обнуляет регистр 81.

Таким образом, при коде на выходах счетчика 52, не равном Л, на тактовом импульсе при втором импульсе формирователя 93 на регистр 1 будет занесен результат перемножения

P(l,J)IO+r

Тактовый импульс с выхода 107 блока 16 открывает блоки элементов И 22 и И 150. Если триггер 130 и триггер 139 блока управления находятся в нуленом сnc 1 оянни, то единичны сигнал имеется на пыходлх 140 и 142 н черем элемент ИЛИ 152, блоки элементов И 146 и 151, блоки элементов ИЛИ 145,

148выходы регистра 21 подключаются

к входам узлов 76, 70 умножения. Renч триггер 13 в единичном состоянии, а триггер 139 - в нулевом, то сигналы имеются на выхолах 142 и 143 и через элемент ИЛИ 152, блок элементов И 151 блок элементов ИЛИ 145 выход регистра 21 подключается к входу узла 76 умножения, а выход регистра 149 через блок элементов I 147 и блок элементов ИЛИ 148 подключается к входу узла 78 умножения.

Если оба триггера 138 и 139 в единичном состоянии, то сигналы имеются на выходах 141, 143 и выход регистра

149через блоки элементов И 144 и 147 и блоки элементов ИЛИ 145 и 143 подключается к входам узлов 76 и 78 умножения .

Второй импульс формирователя 93 при наличии единицы на втором входе элемента И 89, поступающей по шине 70ж с инверсного выхода дешифратора 56, разрешает перемножение кодов, поступающих на входы узла 73.

Таким образом, при коде на выходах счетчика 52, не равном нулю и меньшем I„р + 1, при втором импульсе на регистр 82 будет занесен результат перемножения

P(I.J)1 (И ,

I

если код на выходах счетчика 52 больше Iпр + 1, то на регистр 82 будет занесен результат

P(I,J)-2 |U.

Третий импульс с выхода формирователя 93 подключает через элементы И 92 и ИЛИ IOO выход дешифрг- /ора 96 к блокам элементов И 27 матрицы , В соответствии с кодами дешифратор 96 обеспечивает подключение регистра 24.i+1,j-1 матрицы 1 через блок элементов И 27.i-i-1.j-1 элементы ИЛИ 12 на входы узлов 75... 78 умножения.

Третий импульс при наличии единицы на втором входе элемента И 85, поступающей по шине 70д с инверсного выхода дешифратора 54 блока 10 управления, разрешает перемножение кодов, поступающих на входы узла 76. Дешифратор 54 вырабатывает на инверсном выходе единицу при коде на выходах счетчика 51, не равном нулю. В слу

чае, если на выходах СЧРТЧИКЛ i 1 ч- т я на вливаетея нулевой гол, I ITH IP,TOI 54 вырабатывает единицу по гт выходу, которая по шине 70л поступает на второй вход элемента I 46 и открывает его для прохождении тактового импульса на установочный вхоп регистра 80. Тогда тактовый импульс обнуляет регистр 80.

Таким образом, при коде на выходах счетчика 51, не равном нулю, и при коде на выходах счетчика 52,

5

0

5

0

меньше I

пр

при наличии третьего

импульса на регистр 80 будет занесен результат перемножения P(I + 1 ,J-1 )-|М; при коде НУ выходах счетчика 52, равном или большем Inf, при наличии импульса на регистр 80 будет занесен результат перемножения Р(1 + 1,Л-1 ) 2|М.

В течение тактового импульса на выходе сумматора 101 формируется сумма кодов, поступивших с выходов регистров 79...82. /Тетифратор 95 в соответствии с кодами I,J открывает группу блоков элементов И 38.i,j матрицы 13 и подключает выход сумматора 101 к входам регистра 37.i,j.

По окончании первой фазы работы устройства во все регистры 37 матрицы 13 будут занесены новые значения, очередной тактовый импульс поступает на счетный вход счетчика 53 и устанавливает на его выходах код, рав5

0

5

0

5

ный 1, тогда дешифратор 58 вырабатывает единицу и по шине 72г открывает элемент И 112 блока 17 для прохождения тактовых импульсов, чем определяется вторая фаза работы устройства. На второй фазе работы устройства тактовые импульсы поступают от генератора 43 через элемент И 44 по шине 72а блока управления, через элемент И 112 на вход формирователя 124 импульсов, который вырабатывает в течение тактового импульса на выходах три последовательных импульса в соответствии с диаграммой, приведенной на фиг. 8 „

Первый импульс с первог.о выхода подключает выход дешифратора 110 через блок элементов И 118 к входам блоков элементов И 28 матрицы I и к входам блоков элементов И 39 матрицы 13, Дешифратор 110 в соответствии с кодом I,J, поступившим с выходов счетчиков 51 и 52, подключает лерез блок элементов И 28.i.j матрицы I, выходы регистра 24,i,j группу

I

элементов ГЛИ 11 к входу сумматора 1 5 и через блок элементов И 39 матрицы 13 через группу элементов ИЛИ 14 к входу сумматора 15.

Второй импульс со второго выхода формирователя 124 подключает выход дешифратора 110 через блок элементов И 119 к входам блоков элементов И 26.1..J матрицы 1 .Дешифратор 110 подключает выход сумматора 15 в соответствии с кодом I,J через блок элементов И 26,i,j к входам регистра 24.i.j

Таким образом, по окончании второй

Импульс со второго выхода форми- роьателя 125 при наличии единицы на шине 72б, который поступает с инверсного выхода схемы 61 сравнения при коде на выходах счетчика 51, не равном (N-1), поступает через элемент И 115 на вход блока элементов И 122 и подключает выход дешифратора 111 через блок элементов И 122 к входам блоков элементов И 8.1-8.т. В соответствии с колом 1 дешифратор 111 подключает выход сумматора 3 через бпок элементов И 8.1 к входам регистра 6.л. При установлении на

фазы работы устройства на регистрах

24 треугольной матрицы 1 будут напесе-5 выходах счетчика 51 кода, равного

ны новые значения вероятностей состоя- (N-1), единица с инверсного выхода

ний системы обслуживания и счетчик

53 по очередному тактовому импульсу

изменит код на своих выходах

25

При установлении на выходах счет- чика 53 кода, равного 2, дешифратор 60 вырабатывает на выходе единицу, которая по шине 72в поступает на второй вход элемента И 113 блока 17, устройство переходит в третью (Ьазу работы.

На третьей фазе тактовые импульсы поступают от генератора 43 через элемент И 44 по шине 72а через элемент И 113 блока 17 на управляющий вход блока элементов И 120 и на вход формирователя 125. По поступлении тактового импульса выход дешифратора 110 через блок элементов И 120 подключается к входам блока элементов И 25.1.J матрицы 1. В соответствии с кодом I,J, поступающим с выходов счетчиков 51,52, дешифратор 110 подключает выходы регистра 24.1.J через

схемы 61 сравнения снимается. Тогда появление единицы на выходе элемента Г. 117 открывает элемент И 116 для прохождения импульса со второго выхода формирователя 125. Он подключает выход дешифратора 111 через блок элементов И 123 к входам группы блоков элементов И 4. В соответствии с кодом 1 дешифратор 111 подключает выход сумматора 3 через блок элементов И 4.1 к входам регистра 5.1.

Таким образом, по окончании треть ей фазы работы устройства на регистрах 5 формируются значения вероятнос тей нахождения в системе обслуживания 0,1,...,N запросов.

Четвертая фаза работы устройства определяется появлением на выходах 35 счетчика 53 кода, равного 3. Тогда дешифратор 59 открывает элемент И 49 и единица, выработанная дешифратором 55 при установлении на выходах счетчика 51 кода, равного 1, обнуляет

блок элементов И 25.i.j через элемен- 40 счетчики 53, 51, а по выходу 73 поступает на счетный вход счетчика 129 генератора 23 ИМПУЛЬСОВ времени и изменяет код на его выходах. Код с выходов счетчика 129 заносится на 45 регистр 130 и является новым значением координаты времени. При установлении на выходах счетчика 129 код равного времени окончания моделирова ния, схема 131 сравнения вырабатывае

ты ИЛИ 2 к входу сумматора 3„

Формирователь 125 по поступлению тактового импульса формирует на выходах три последовательных импульса в соответствии с диаграммой, приведенной на фиг о 8.

Импульс с первого выхода формирователя 125 при поступлении единицы на второй вход элемента И 114 с инверсного выхода дешифратора 54, что озна- 50 единицу и обнуляет триггер 132. Сня- чает ненулевой код на выходах счетчика 51, подключит через блок элементов И 121 выход дешифратора 111 к входам группы элементов И 7. При этом Б соответствии с кодом 1, по- 55 ступившим с выхода счетчика 52, выходы регистра 6.i через блок элемен тон И 7.1 и rp/nnv -элементов ИЛИ 9 подключимте я к Т ХОДУ гумматора 3.

тие единицы по шине 74 блоьа 23 приведет к закрытию элемента И 44 блока 10 управления. Режим моделирования окончен.

Формула изобретения

Устройство для моделиронания систем массового обслч /кнв , содержа

Импульс со второго выхода форми- роьателя 125 при наличии единицы на шине 72б, который поступает с инверсного выхода схемы 61 сравнения при коде на выходах счетчика 51, не равном (N-1), поступает через элемент И 115 на вход блока элементов И 122 и подключает выход дешифратора 111 через блок элементов И 122 к входам блоков элементов И 8.1-8.т. В соответствии с колом 1 дешифратор 111 подключает выход сумматора 3 через бпок элементов И 8.1 к входам регистра 6.л. При установлении на

5 выходах счетчика 51 кода, равного

5

схемы 61 сравнения снимается. Тогда появление единицы на выходе элемента Г. 117 открывает элемент И 116 для прохождения импульса со второго выхода формирователя 125. Он подключает выход дешифратора 111 через блок элементов И 123 к входам группы блоков элементов И 4. В соответствии с кодом 1 дешифратор 111 подключает выход сумматора 3 через блок элементов И 4.1 к входам регистра 5.1.

Таким образом, по окончании третьей фазы работы устройства на регистрах 5 формируются значения вероятностей нахождения в системе обслуживания 0,1,...,N запросов.

Четвертая фаза работы устройства определяется появлением на выходах 5 счетчика 53 кода, равного 3. Тогда дешифратор 59 открывает элемент И 49, и единица, выработанная дешифратором 55 при установлении на выходах счетчика 51 кода, равного 1, обнуляет

счетчики 53, 51, а по выходу 73 поступает на счетный вход счетчика 129 генератора 23 ИМПУЛЬСОВ времени и изменяет код на его выходах. Код с выходов счетчика 129 заносится на регистр 130 и является новым значением координаты времени. При установлении на выходах счетчика 129 кода, равного времени окончания моделирования, схема 131 сравнения вырабатывает

единицу и обнуляет триггер 132. Сня-

тие единицы по шине 74 блоьа 23 приведет к закрытию элемента И 44 блока 10 управления. Режим моделирования окончен.

Формула изобретения

Устройство для моделиронания систем массового обслч /кнв , содержа

131

щее первую и вторую треугольные матрицы регистров памяти, размерностью MxN, блок управления, пять групп элементов ИЛИ, два сумматора, три группы регистров памяти, пять групп блоков элементов II, генератор импульсов времени, первый регистр памяти, первый блок элементов И, блок формирования сигналов управления и блок вычисления вероятностей переходов, первая и вторая группы информационных входо первого сумматора соединены соответственно с выходами элементов ИЛИ первой и второй групп, а выходы первого сумматора подключены соответственно к информационным входам блоков элеметов И первой группы, выходы которых подключены соответственно к разрядным входам регистров памяти первой группы, разрядные аыходы которых являются выходами устройства, выходы 1-го блока элементов И второй группы (, II) соединены соответственно с i-ми входами элементов ИЛИ второй группы, а выходы блоков элементов И третьей группы подключены к разрядным входам соответствующего регистра памяти второй группы, разрядные выходы которого подключены к

информационным входам соответствующе- 30 счетчика импульсов, к разрядным выго блока элементов И второй группы, первая треугольная матрица регистров памяти содержит четыре группы блоков элементов И, а в i-й строке содержит j регистров памяти (j M-i-Н), число блоков элементов И каждой группы в каждой строке равно числу регистров памяти в строке, информационные входы блоков элементов И первой группы соединены с разрядными выходами соот- ветствующего регистра памяти, одноименные выходы блоков элементов И первой группы i-й строки объединены между собой и подключены соответственно к i-м входам элементов ИЛИ первой группы устройства, выходы блоков элементов И второй группы в каждой строке соединены с разрядными входами соответствующего регистра памяти данной строки, разрядные выходы регистра 50 счетчика импульсов подключены соотпамяти подключены к информационным входам соответствующих блоков элементов И третьей и четвертой групп, блок управления состоит из элементов И с первого ПО СедЬМОЙ, ПерВОГО, ВТОРОГО се

и третьего счетчиков импульсов, с первого по седьмой дешифраторов, первой, второй и третьей схем сравнения, первого и второго триггеров, узла вычиветственно к входам четвертого, пято го, шестого и седьмого дешифраторов, выход четвертого дешифратора соединен с вторым входом четвертого элемента И, разрядные выходы сумматора подключены соответственно к разрядным входам регистра памяти, выход второго дешифратора соединен с первы входом седьмого элемента И, выход

2979

0

5

14

тания, регистра памяти, сумматора, элемента ИЛИ и генератора тактовых импульсов, выход которого соединен с первым входом первого элемента И, выход первого элемента И подключен к первым входам второго, третьего и четвертого элементов И, выход второго элемента И соединен со счетным входом первого счетчика импульсов, выход третьего элемента И подключен к нулевому входу первого триггера, первому входу элемента ИЛИ и первым входам пятого и шестого элементов И, выход элемента ИЛИ соединен с входом обнуления первого счетчика импульсов, прямой выход первого триггера подключен к второму входу третьего элемента И, а инверсный выход - к второму входу второго элемента И, разрядные выходы первого счетчика импульсов подключены соответственно к информационным входам первой группы сумматора, входам первого и второго дешифраторов и информационным входам первой группы первой схемы сравнения, выход Равно которой соединен с единичным входом первого триггера, выход шестого элемента И подключен к счетному входу второго

ходам которого подключены информационные входы второй группы сумматора, входы третьего дешифратора, информационные входы второй и третьей схем сравнения и входы узла вычитания, выходы которого соединены с информационными входами второй группы первой схемы сравнения, выход Равно второй схемы сравнения подключен к единичному входу второго триггера, прямой выход которого соединен с вторым входом пятого элемента И, выход которого подключен к входу обнуления второго счетчика импульсов, нулевому входу второго триггера и счетному входу третьего счетчика импульсов, инверсный выход второго триггера соединен с вторым входом шестого элемента И, разрядные выходы третьего

ветственно к входам четвертого, пятого, шестого и седьмого дешифраторов, выход четвертого дешифратора соединен с вторым входом четвертого элемента И, разрядные выходы сумматора подключены соответственно к разрядным входам регистра памяти, выход второго дешифратора соединен с первым входом седьмого элемента И, выход

15

15

которого подключен к входу обнуления третьего счетчика импульсов и второму входу элемента ИЛИ, выход шестого дешифратора соединен с вторым входом седьмого элемента И, вторая треуголь- 5 нал матрица регистров памяти в каждой строке содержит j регистров памяти, j блоков элементов И первой и второй групп, причем в каждой строке выходы блока элементов И первой группы со- Ю единены с разрядными входами соответствующего регистра памяти, разрядные выходы которого подключены к информационным входам соответствующего блока элементов И второй группы, блок формирования сигналов управления содержит первый и второй дешифраторы, с первого по пятый элементы И, элемент НЕ, с первого по шестой блоки элементов И, первый и второй формирователи импульсов, причем в блоке формирования сигналов управления выход первого элемента И соединен с входом первого формирователя импульсов, первый и второй выходы которого подключены к управляющим входам первого и второго блоков элементов И, информационные входы которых и информационные входы третьего блока элементов И соединены соответственно с выходами первого дешифратора, выход второго элемента И соединен с управляющим входом третьего блока элементов И и входом второго формирователя импульсов, первый выход которого соединен с первым входом третьего элемента И, второй выход второго формирователя импульсов блока формирования сигналов управле165297916

с управляю щми входами блоков элементов И первой группы устройства, управляющие входы блоков элементов И второй группы которого подключены соответственно к выходам четвертого блока элементов И блока формирования сигналов упраатения, первая группа входов первого дешифратора и входы второго дешифратора которого подключены соответственно к разрядным выходам второго счетчика импульсов блока управления, разрядные выходы первого счетчика импульсов которого соединены соответственно с входами второй группы первого дешифратора блока формирования сигналов управления, первый вход первого элемента И и первый вход второго элемента И которого соединены с выходом первого элемента И блока .управления, выход Не равно первой схемы сравнения которого подключен к , входу элемента ПК и второму входу четвертого элемента И блока формирования сигналов управления, второй вход второго элемента И которого соединен с выходом седьмого дешифратора блока управления, выход пятото дешифратора которого подключен к второму входу первого элемента И блока Нормирования сигналов управления, второй вход третьего элемента И которого соединен с первым выходом первого дешифратора блока управления, выход четвертого элемента И которого подключен к управляющему входу блока элементов И устройства, информационные входы которого соединены соответственно с разрядными выходами первого регистра памяти устройства, выходы первого де20

25

30

35

ния подключен к первым входам четвеи- 40 шифратора, третьего дешифратора, третьтого и пятого элементов Н, второй вход пятого элемента И соединен с выходом элемента НЕ, а выходы третьего, четвертого и пятого элементов И подключены к управляющим входам соот- ветственно четвертого, пятого и шестого блоков элементов И, информационные входы которых соединены соответственно с выходами второго дешифратора блока формирования сигналов управ- j та И блока управления соединен с вхоления, выходы первого сумматора устройства соединены соответственно с информационными входами блоков элементов И третьей группы устройства, управляющие входы которых подключены к выходам пятого блока элементов И блока формирования сигналов управления, выходы шестого блока элементов И которого соединены соответственно

ей схемы сравнения и четвертого элемента И -.лока управления соединены соответггйенно с входами разрешения вычислений группы блока вычисления вероятностей переходов, информационные входы первой группы которого соединены соответственно с разрядными выходами первого регистра памяти блока управления, выход седьмого элемендом напуска генератора импульсов времени, выход которого подключен к второму входу первого олекента И блока управления, разрядные выходы первого и второго счетчиков импульсов которого соединены соответственно с информационными входами второй и третьей групп блока вычисаения вероятностей переходов, разрядные выходы регистров

памяти третьей группы устройства сое; нены с информационными входами соответствующих блоков элементов И четвертой и пятой групп устройства, управляющие входы блоков элементов И четвертой и пятой групп устройства соединены соответственно с выходами разрешения считывания информации блока вычисления вероятностей переходов, выходы блоков элементов И четвертой и пятой групп устройства подключены соответственно к информационным входам четвертой группы блока вычисления вероятностей переходов, i-й выход выбора адреса считывания информации блока вычисления вероятностей переходов соединен с управляюгдоми входами всех блоков элементов И первой группы i-й строки нторой треугольной матрицы регистров памяти, информационные входы всех блоков элементов И первой группы которой подключены соответственно к информационным выходам блока вычисления вероятностей переходов, i-й выход выбора строки записи информации которого подключен к управляющим входам блоков элементов И третьей группы i-й строки первой треугольной матрицы регистров памяти, выходы блоков эле- ментов И третьей группы i-й строки которой подключены соответственно к 1-м входам элементов ИЛИ третьей группы устройства, выходы которых соединены соответственно с информационными входами шестой группы блока вычисления вероятностей переходов, i-й выход третьего блока элементов И блока формирования сигналов управления соедине соответственно с управлякшяими входами блоков элементов И первой группы 1-й строки первой треугольной матрицы

регистров памяти.

1-й выход второго блока элементов И блоча формирования сигналов управления подкпю- чен к управляющем входам блоков элементов И второй группы i-й строки первой треугольной матрицы регистров памяти, выходы блоков элементов И четвертой группы i-й строки которой под- ключены соответственно к входам 1-й группы элементов ИЛИ четвертой группы устройств., выходы которых соединены соответственно с информационными входами первой группы второго сумма- тора устройства, выходы которого подключены соответственно к информационным входам всех бпоков элементов И второй группы первой треугольной мат0

5

- 0 5 О

0

5

5 0 5

рицы регистров памяти, управлявшие входы блоков -щементов И четвертой группы i-й строки первой треугольной матрицы регистров памяти подключены к i-му выходу первого блока элементов И блока формирования сигналов управления ц управляющим входам блоков элементов И второй группы i-й строки второй треугольной матрицы регистров памяти, одноименные выходы блоков элементов И второй группы i-й строки которой объединены и подключены соответственно к входам i-й группы элементов ИЛИ пяток группы устройства, выходы которых соединены соответственно с информационными входами второй группы второго сумматора устройства, о т- личающееся тем, что, с целью расширения функциональных возможностей устройства за счет моделирования систем массового обслуживания с подключением резерва с изменяющейся интенсивностью поступления запросов на обслуживание, оно дополнительно содержит второй, третий, четвертый, пятый и шестой блоки элементов И, элемент И, элемент ИЛИ, шестую и седьмую группы элементов ИЛИ и второй регистр памяти, а блок управления дополнительно содержит второй и третий регистры памяти, четвертую и пятую схемы сравнения, третий и четвертый триггеры, причем в блоке управления выходы третьего регистра памяти соединены соответственно с информационными входами первой группы четвертой схемы сравнения, а выходы второго регистра памяти соединены соответственно с информационными входами первой группы пятой схемы сравнения, информационные входы второй группы четвертой и пятой схем сравнения подключены соответственно к разрядным выходам второго счетчика импульсов, выходы Меньше и Равно или больше четвертой схемы сравнения подключены соответственно к нулевому и единичному входам третьего триггера, а нулевой и единичный входы четвертого триггера подключены соответственно к выходам Меньше и Равно или больше пятой схемы сравнения, прямой выход третьего трип ера блока управления соединен с первым входом элемента И и управляющим входом второго блока элементов И устройства, а инверсный выход третьего триггера блока управления подключен к второму , входу элемента ИЛИ устройства и упрлвляндаему входу третьего блока элементов И устройства, прямой выход четвертого триггера блока управлении соединен с управляющим входом четвертого блока элементов И устройства, вы ходы которого подключены соответственно к первым входам элементов ИЛИ шестой группы устройства, инверсный выход четвертого триггера блока управ ления соединен с вторым входом элемента И устройства, выход которого соединен с вторым входом элемента ИЛИ устройства, выход которого соединен с управляющим входом второго блока элементов И, выходы которого подключены соответственно к первым входам элементов ИЛИ седьмой группы, выходы второго регистра памяти устройства соединены соответственно с информа

цноиными входами пятого блока элемен- -ов И, выходы которого соединены соответственно с информационными входами второго и четвертого блоков элементов И, выходы первого блока элементов И соединены соответственно с информационными входами третьего и шестого блоков элементов И, выходы которых подключены к вторым входам элементов ИЛИ соответственно седьмой и шестой групп, выходы элементов ИЛИ шестой и седьмой группы соединены соответственно с входами задания интенсивности обслуживания блока вычисления вероятностей переходов, а утфавляющнй вход пятого блока элементов И устройства подключен к выходу четвертого элемента И блока управления .

о гм ю

Ј.

I

52

f

ran

51

74

$

W

т

- л,

56 ж

г д

±m

5k

ФигЛ

70

7Z

Фиг 5

73

129

130

71

Фиг. 6

133

132

П

131

Фиг Л

jtS //. //

: у 4./ / Hi /

Фиг.9

| Устройство для моделирования систем массового обслуживания | 1982 |

|

SU1018931A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1399756A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-05-30—Публикация

1989-04-24—Подача