О

00 00

Изобретение относится к вычислительной технике и может быть использовано при цифровой обработке значений параметров объекта, пред ста вимь.1Х как случайные величины, искаженные помехами.

Цель изобретения - повышение быстродействия устройства.

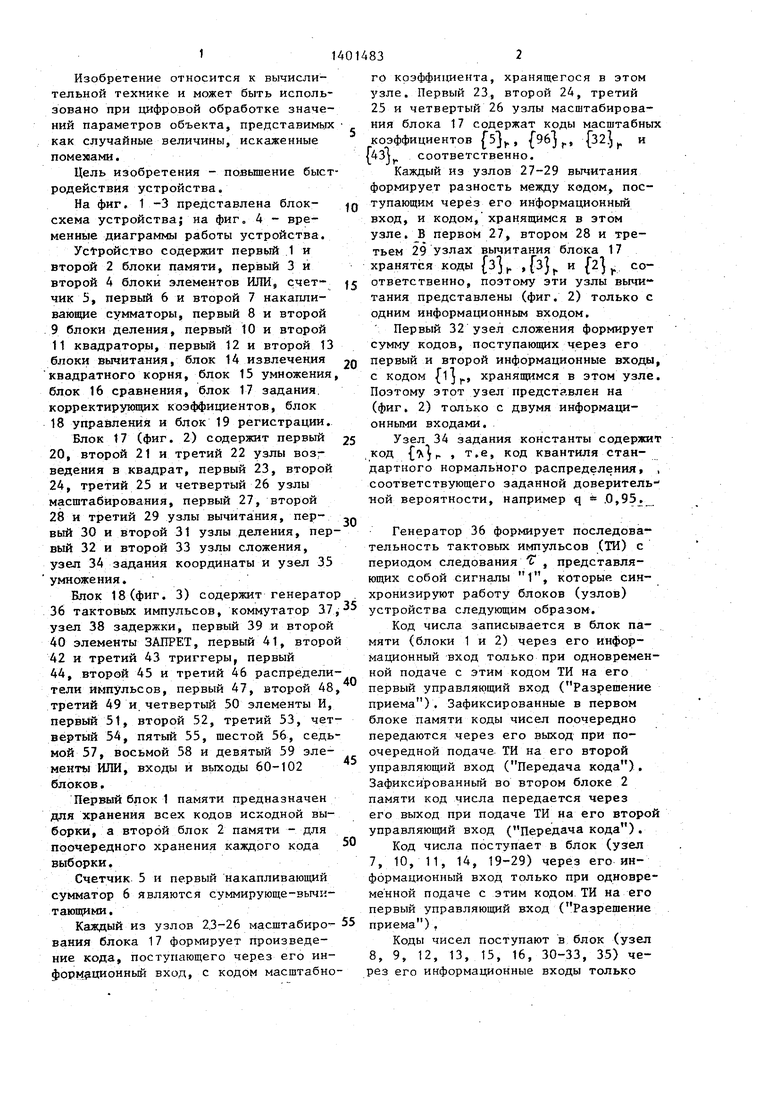

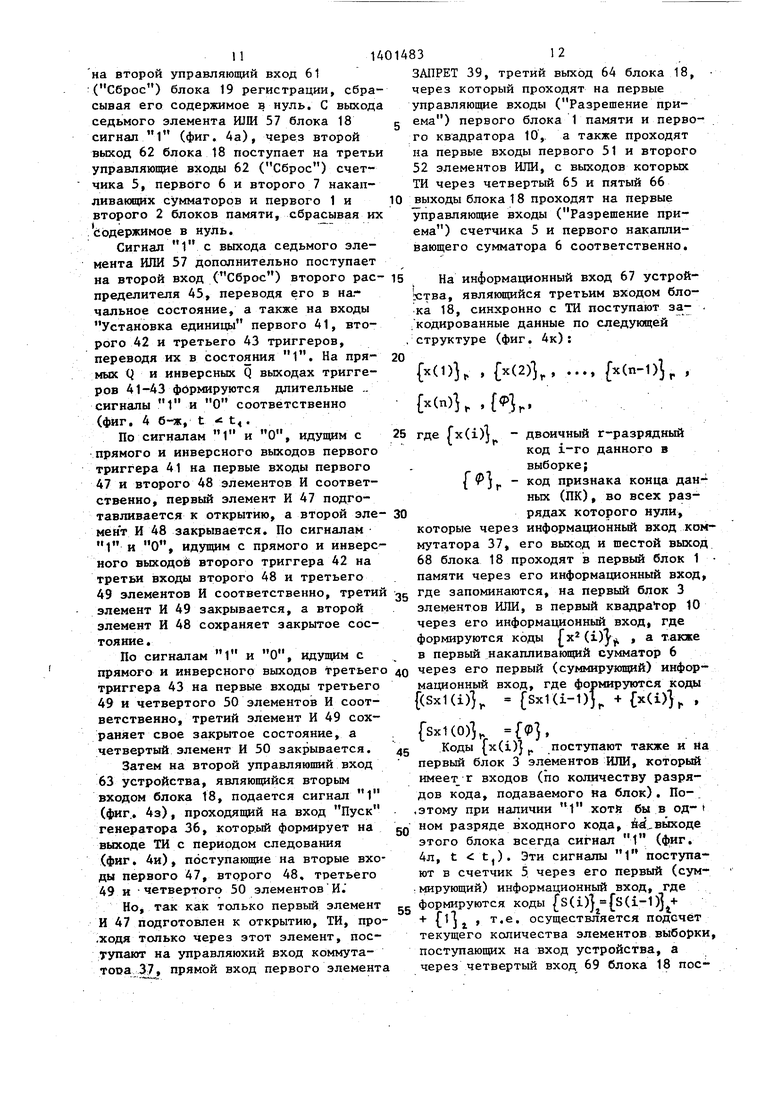

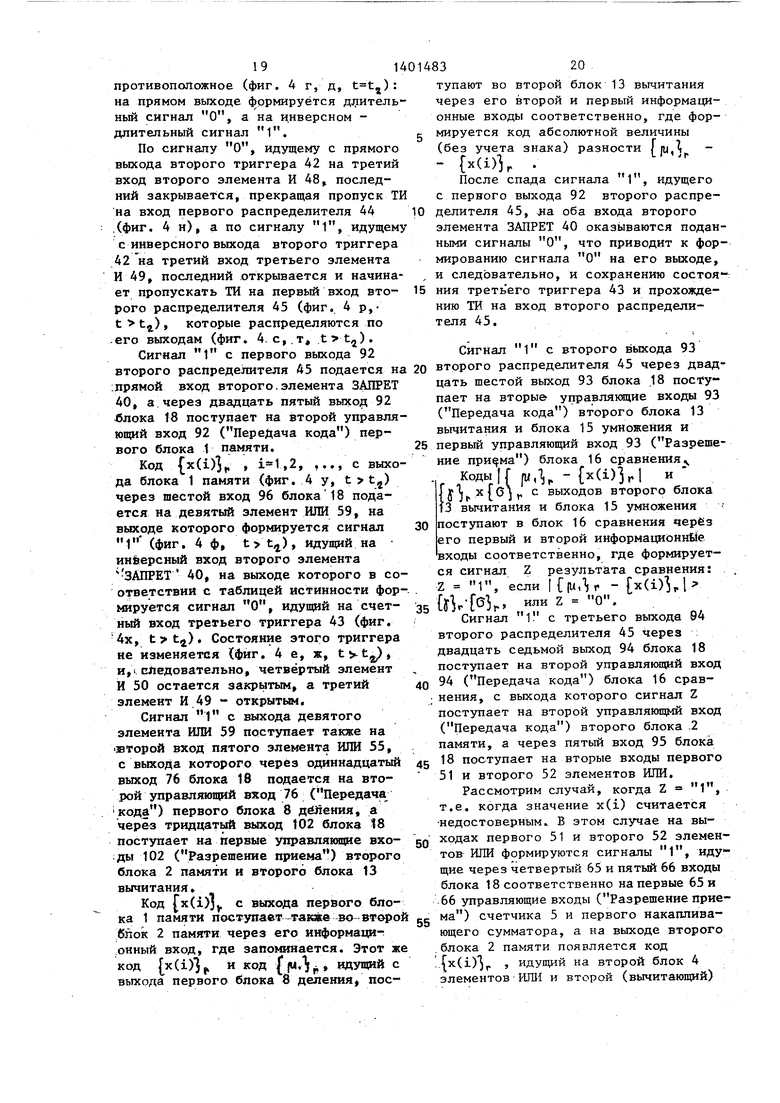

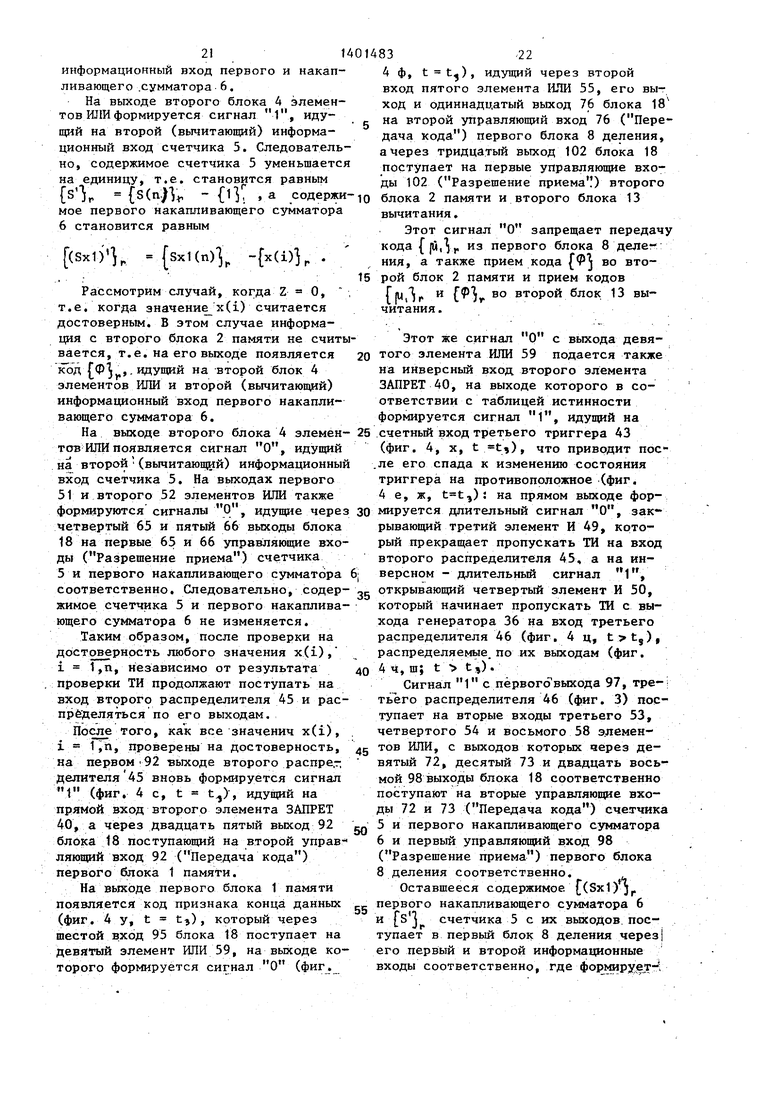

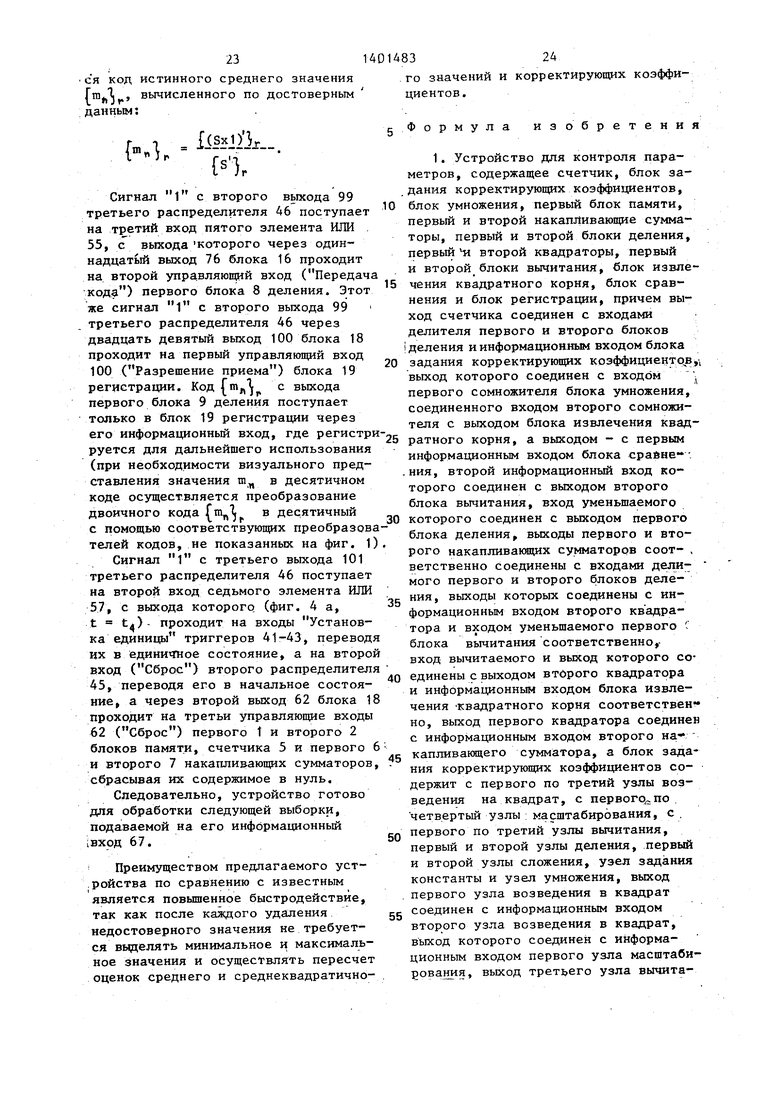

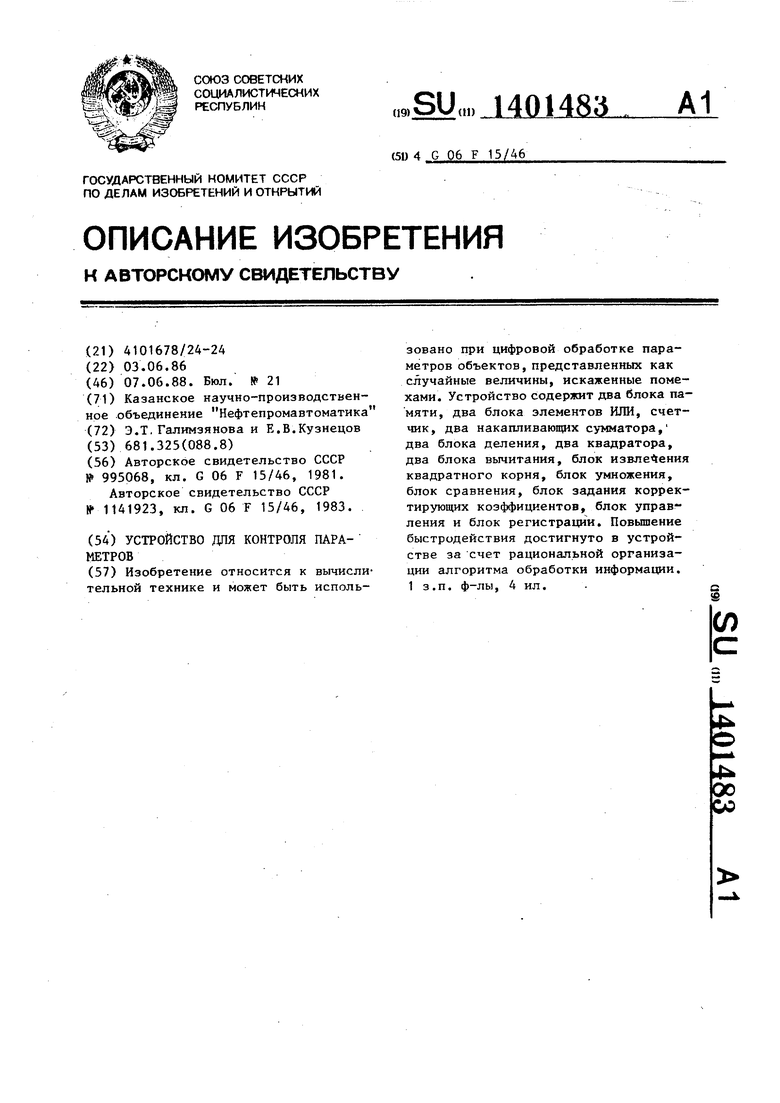

На фиг. 1-3 представлена блок- схема устройства; на фиг, 4 - временные диаграммы работы устройства.

Уctpoйcтвo содержит первый 1 и второй 2 блоки памяти, первый 3 и второй А блоки элементов ИЛИ, счет- чик 5, первый 6 и второй 7 накапли- ваюпще сумматоры, первый 8 и второй 9 блоки деления, первый 10 и второй 11 квадраторы, первый 12 и второй 13 блоки вычитания, блок 14 извлечения квадратного корня, блок 15 умножения, блок 16 сравнения, блок 17 задания, корректирующих коэффициентов, блок 18 управления и блок 19 регистрации.

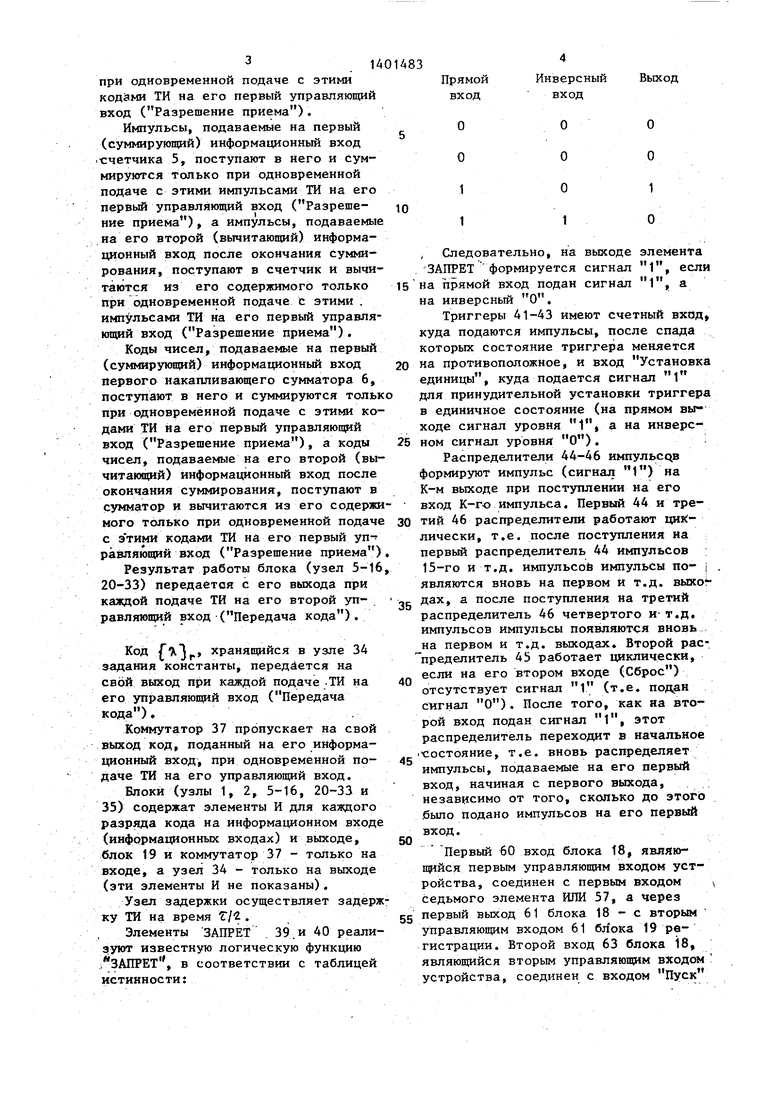

Блок 17 (фиг, 2) содержит первый 20, второй 21 и третий 22 узлы ъоз- ведения в квадрат, первый 23, второй 24, третий 25 и четвертый 26 узлы масштабирования, первый 27, второй 28 и третий 29 узлы вычитания, пер- вый 30 и второй 31 узлы деления, первый 32 и второй 33 узлы сложения, узел 34 задания координаты и узел 35 умножения.

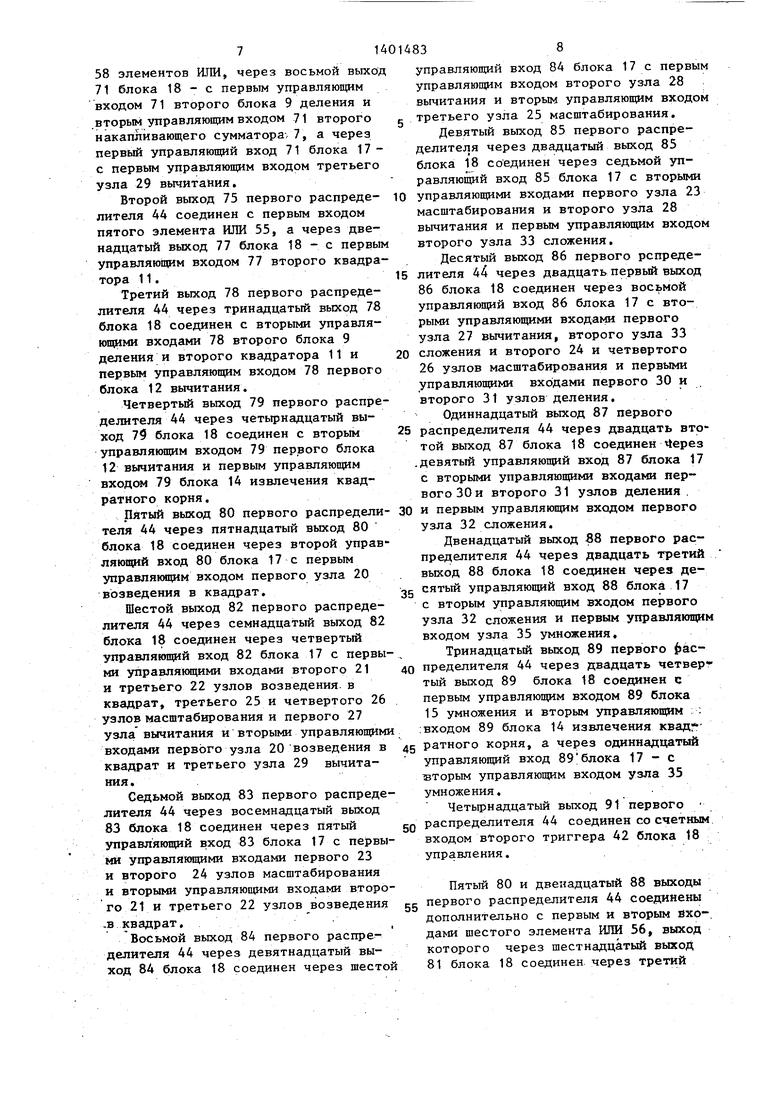

Блок 18(фиг. 3) содержит генератор 36 тактовых импульсов, коммутатор 37, узел 38 задержки, первый 39 и второй 40 элементы ЗАПРЕТ, первый 41, второй 42 и третий 43 триггеры, первый 44, второй 45 и третий 46 распределители импульсов, первый 47, второй 48, третий 49 и. четвертый 50 элементы И, первый 51, второй 52, третий 53, четвертый 54, пятый 55, шестой 56, седьмой 57, восьмой 58 и девятый 59 элементы ШШ, входы и выходы 60-102 блоков.

Первый блок 1 памяти предназначен для хранения всех кодов исходной выборки, а второй блок 2 памяти - для поочередного хранения каждого кода выборки.

Счетчик 5 и первый накапливающий сумматор 6 являются суммирующе-вычитающими.

Каждый из узлов 2.3-26 масштабиро- вания блока 17 формирует произведение кода, поступающего через его ин- формэциоиньш вход, с кодом масштабно

го коэффициента, хранящегося в этом узле. Первый 23, второй 24, третий 25 и четвертый 26 узлы масштабирования блока 17 содержат коды масштабны коэффициентов f З} , {96., (32 и

соответственно.

Каждый из узлов 27-29 вычитания формирует разность между кодом, поступающим через его информационный вход, и кодом, хранящимся в этом узле. В первом 27, втором 28 и третьем 29 узлах вычитания блока 17 хранятся коды {З ответственно, поэтому эти узлы вычи тания представлены (фиг. 2) только с одним информационным входом.

Первый 32 узел сложения формирует сумму кодов, поступающих через его первый и второй информационные входы с кодом ., хранящимся в этом узле Поэтому этот узел представлен на (фиг, 2) только с двумя информационными входами.

Узел 34 задания константы содержи

.код { Л г- т.е, код квантиля стандартного нормального распределения, соответствующего заданной доверительной вероятности, например q .0,95

Генератор 36 формирует последова тельность тактовых импульсов (ТИ) с периодом следования , представляющих собой сигналы 1, которые синхронизируют работу блоков (узлов) устройства следующим образом.

Код числа записывается в блок памяти (блоки 1 и 2) через его информационный вход только при одновременной подаче с этим кодом ТИ на его первый управляющий вход (Разрешение приема). Зафиксированные в первом блоке памяти коды чисел поочередно передаются через его выход при поочередной подаче ТИ на его второй управляющий вход (Передача кода). Зафиксированный во втором блоке 2 памяти код числа передается через его выход при подаче ТИ на его второй управляющий вход (Передача кода) ,

Код числа поступает в блок (уэгел

7,10, 11, 14, 19-29) через его информационный вход только при одновременной подаче с этим кодом. ТИ на его первый управляющий вход (Разрешение приема),

Коды чисел поступают в блок (узел

8,9, 12, 13, 15, 16, 30-33, 35) через его информационные входы только

1А

при одновременной подаче с этими кодами ТИ на его первый управляющий вход (Разрешение приема).

Импульсы, подаваемые на первый (суммирующий) информационный вход .счетчика 5, поступают в него и суммируются только при одновременной подаче с этими импульсами ТИ на его первый управляющий вход (Разрешение приема), а импульсы, подаваемые на его второй (вычитающий) информационный вход после окончания суммирования, поступают в счетчик и вычитаются из его содержимого только при одновременной подаче с этими, импульсами ТИ на его первый управля- юпр1й вход (Разрешение приема) ,

Коды чисел, подаваемые на первый (суммирующий) информационный вход первого накапливающего сумматора 6, поступают в него и суммируются тольк при одновременной подаче с этими кодами ТИ на его первый управляющий вход (Разрешение приема), а коды чисел, подаваемые на его второй (вы- читаю ций) информационный вход после окончания суммирования, поступают в сумматор и вычитаются из его содержимого только при одновременной подаче с э тими кодами ТИ на его первый уп- равляюший вход (Разрешение приема)

Результат работы блока (узел 5-16 20-33) передается с его выхода при каждой подаче ТИ на его второй уп- равляюпщй вход (Передача кода).

Код f Зг з Ранящийся в узле 34 задания константы, передается на свой выход при калдчой подаче .ТИ на его управляющей вход (Передача кода),.

Коммутатор 37 пропускает на свой выход код, поданный на его информационный вход, при одновременной подаче ТИ на его управляющий вход.

Блоки (узлы 1, 2, 5-16, 20-33 и 35) содержат элементы И для каждого разряда кода на информационном входе (информаи онных входах) и выходе, блок 19 и коммутатор 37 - только на входе, а узел 34 - только на выходе (эти элементы И не показаны).

Узел задержки осуществляет задержку ТИ на время Г/2 .

Элементы ЗАПРЕТ 39.и 40 реализуют известную логическую функцию , ЗАПРЕТ, в соответствии с таблицей истинности:

Инверсный вход

О О

Выход

10

1

, Следовательно, на выходе элемента ЗАПРЕТ формируется сигнал 1, если 15 на прямой вход подан сигнал 1, а

5

0

5

на инверсный О.

Триггеры 41-43 имеют счетный вход, куда подаются импульсы, после спада которых состояние триггера меняется 0 на противоположное, и вход Установка единицы, куда подается сигнал 1 для принудительной установки триггера в единичное состояние (на прямом выходе сигнал уровня 1, а на инверсном сигнал уровня О).;

Распределители 44-46 импульсцв формируют импульс (сигнал 1) на К-м выходе при поступлении на его вход К-го импульса. Первый 44 и третий 46 распределители работают лически, т.е. после поступления на первый распределитель 44 импульсов : 15-го и т.д. импульсой импульсы по- I являются вновь на первом и т.д. дах, а после поступления на третий распределитель 46 четвертого и- т.д. импульсов импульсы появляются вновь на первом и т.д. выходах. Второй рас- пределитель 45 работает циклически, если на его втором входе (Сброс) отсутствует сигнал 1 (т.е. поддан О) . После того, как на второй вход подан сигнал 1, этот распределитель переходит в начальное хюстояние, т.е. вновь распределяет импульсы, подаваемые на его первый вход, начиная с первого выхода, ; независимо от того, сколько до этого .было подано импульсов на его первый вход.

Первый 60 вход блока 18, являющийся первым управляющим входом устройства, соединен с первым входом седьмого элемента ИЛИ 57, а через первый выход 61 блока 18 - с вторым управляющим входом 61 бЛока 19 регистрации. Второй вход 63 блока 18, являющийся вторым управляющим входом устройства, соединен с входом Пуск

0

5

0

5

генератора 36, третий вход 67 блока 18, являющийся информационным входом устройства, соединен с информацион ным входом коммутатора 37, выход которого через шестой выход 68 блока 18 соединен с первым информационным входом 68 первого накапливающего сумматора бис информационными входами 68 первого, квадратора 10, первого блока 3 элементов ИЛИ и первого блока t памяти.

Выход первого блока 3 элементов ИЖ соединен с первым информационным входом счетчика 5, а через четвертый вход 69 блока 18 - с инверсным ахо- дом первого элемента ЗАПРЕТ 39, Выход счетчика 5 соединен с вторыми информационными входами первого 8 и второго 9 блоков деления, а через информационный вход 74 блока 17 - с информационным входом третьего узла 29 вычитания.

Выходы первого 6 и второго 7 на- каш1иваю1цих сумматоров соединены с первыми информационными входами первого 8 и второго 9 блоков деления соответственно. Выход первого квадратора 10 соединен с информационным входом второго накапливающего сумматора 7, Выход первого блока 8 деления соединен с информационным входом второго квадратора 11, первым информационным входом второго блока 13 вычитания и информационным входом блока 19 регистрации. Выход второго блока 9 деления соединен с первьш информационным входом первого блока 12 вычитания, соединенного вторым информационным входом с выходом второго квадратора 11, la вЫходом - с информационным входом блока 14 извлечения квадратного корня, выход которого соединен с вторым информационным входом блока 15 умножения, соеди ненного первым информационным входом через вьвсод 90 блока 17с выходом узла 35 умножения, а выходом - с вторым информационным входом блока 16 сравнения,Выход первого блока 1 памяти соединен с вторым информационным входом второго блока 13 вычитания, информа- 1Ц1онным входом второго блока 2 памяти, а через шестой,вход 96 блока 18 - с, выходами девятого элемента ИЛИ 59,

Выход второго блока 13 вычитания соединен с первым информационным

входом блока 16 сравнения, выход которого соединен с вторым управляющим входом второго блока 2 памяти, с а через пятый вход 95 блока 18 - с вторыми входами первого 51 и второго 52 элементов ИЛИ,

Выход второго блока 2 памяти соединен с вторым информационным входом

0 первого накапливающего сумматора 6 и входами второго блока 4 элементов ИЛИ, выход которого соединен с вторым информационным входом счетчика 5, Выход седьмого элемента ИЛИ 57

15 соединен с входами Установка единицы, первого 41, второго 42 и третьего 43 триггеров и входом Сброс второго распределителя 45, а через второй выход 62 блока 18 - с третьими

0 управляющими входами 62 (Сброс) счетчика 5, первого 6 и второго 7 накапливаюдах сумматоров .и первого 1 и второго 2 блоков памяти.

Выход генератора 36 соединен с

5 вторьгми входами первого 47, второго 48, третьего 49 и четвертого 50 эле- .ментов И, Первые входы первого 47 и второго 48 элементов И соединены с прямым и инверсным выходами первого

0 триггера 41 соответственно, а его счетный вход соединен с выходом первого элемента ЗАПРЕТ 39 блока управления,.

Выход первого элемента И 47 соеди35 нен с входом узла 38 задержки, управляющим входом коммутатора 37, первыми входами первого 51 и второго 52 элементов ИЛИ и прямым входом первого элемента ЗАПРЕТ 39, а через третий

0 выход 64 блока 18 - с первыми управляющими входами 64 первого блока 1 памяти и первого квадратора 10,

Прямой и инверсный выходы второго

42 триггера соединены с третьими

5 входами второго 48 и третьего 49 элементов И соответственно, выходы КОТОРЫХ соАдинены с входом первого распределителя 44 и первым входом второго распределителя 45 соответ0 ственно.

Прямой и инверсный выходы третье-, го триггера 43 соединены с первыми входами третьего 49 и четвертого 50 элементов И соответственно, выход

g последнего соединен с входом третьего распределителя 46,

Первый распределитель 44 соединен первым выходом 71 с первыми входами третьего 53, четвертого 54 и восьмог.о.

58 элементов ИЛИ, через восьмой выход 71 блока 18 - с первым управляющим входом 71 второго блока 9 деления и вторым управляющим входом 71 второго накапливающего сумматора/7, а через первый управляющий вход 71 блока 17- с первым управляющим входом третьего узла 29 вычитания.

Второй выход 75 первого распределителя А4 соединен с первым входом пятого элемента ИЛИ 55, а через двенадцатый выход 77 блока 18 - с первым управляющим входом 77 второго квадратора 11.

Третий выход 78 первого распределителя 44 через тринадцатый выход 73 блока 18 соединен с вторыми управля- кяцими входами 78 второго блока 9 деления и второго квадратора 11 и первым управляющим входом 78 первого блока 12 вычитания.

Четвертый выход 79 первого распределителя 44 через четьфнадцатый выход 79 блока 18 соединен с вторым управляющим входом 79 первого блока 12 вычитания и первым управляющим входом 79 блока 14 извлечения квадратного корня.

управляющий вход 84 блока 17 с первым управляющим входом второго узла 28 вычитания и вторым управляющим входом

третьего узла 25 масштабирования.

Девятый выход 85 первого распределителя через двадцатый выход 85 блока 18 соединен через седьмой управляющий вход 85 блока 17 с вторыми

управляющими вxoдa ffl первого узла 23 масштабирования и второго узла 28 вычитания и первым управляющим входом второго узла 33 сложения.

Десятый выход 86 первого рспределителя 44 через двадцать первый выход 86 блока 18 соединен через восьмой управляюш;ий вход 86 блока 17 с вторыми управляющими входами первого узла 27 вычитания, второго узла 33

сложения и второго 24 и четвертого 26 узлов масштабирования и первыми управляющими входами первого 30 и второго 31 узлов деления.

Одиннадцатый выход 87 первого

распределителя 44 через двадцать вто той выход 87 блока 18 соединен tiepes .девятый управляющий вход 87 блока 17 с вторыми управляющими входами первого 30 и второго 31 узлов деления ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для прогнозирования надежности по результатам ускоренных испытаний | 1987 |

|

SU1508238A1 |

| УСТРОЙСТВО ОБРАБОТКИ ЦВЕТНЫХ ИЗОБРАЖЕНИЙ | 1999 |

|

RU2159958C1 |

| Адаптивный временной дискретизатор | 1990 |

|

SU1791822A1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧ НЕЛИНЕЙНОГО СТОХАСТИЧЕСКОГО ПРОГРАММИРОВАНИЯ | 1991 |

|

RU2006933C1 |

| Устройство для вычисления структурной и интервальной функций | 1984 |

|

SU1166135A1 |

| Генератор случайных чисел | 1986 |

|

SU1417006A1 |

| УСТРОЙСТВО ДЛЯ НЕРАЗРУШАЮЩЕГО КОНТРОЛЯ МАТЕРИАЛОВ И ИЗДЕЛИЙ | 1990 |

|

RU2028606C1 |

| Цифровой измеритель показателей качества электрической энергии трехфазной сети | 1988 |

|

SU1633368A1 |

| Рентгенотелевизионный дефектоскоп | 1989 |

|

SU1658049A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОЙ ОЦЕНКИ ФАЗОВОЙ НАПРЯЖЕННОСТИ РЕСПОНДЕНТА | 2012 |

|

RU2492520C1 |

Изобретение относится к вычислительной технике и может быть использовано при цифровой обработке параметров объектов, представленных как случайные величины, искаженные помехами. Устройство содержит два блока памяти, два блока элементов ИЛИ, счетчик , два накапливающих сумматора, два блока деления, два квадратора, два блока вычитания, блок извле 1ения квадратного корня, блок умножения, блок сравнения, блок задания корректирующих коэффициентов, блок управления и блок регистрации. Повышение быстродействия достигнуто в устройстве за счет рациональной организации алгоритма обработки информации. 1 3.п. ф-лы, 4 ил.

Пятый выход 80 первого распредели- 30 и первым управляющим входом первого

теля 44 через пятнадцатый выход 80 блока 1В соединен через второй управляющий вход 80 блока 17 с первым управляющим входом первого узла 20 возведения в квадрат.

Шестой выход 82 первого распределителя 44 через семнадцатый выход 82 блока 18 соединен через четвертый управляю1ций вход 82 блока 17 с первыми управлякицими входами второго 21 и третьего 22 узлов возведения, в квадрат, третьего 25 и четвертого 26 узлов масщтабирования и первого 27 узла вычитания и вторыми управляющими входами первого узла 20 возведения в квадрат и третьего узла 29 вычитания.

Седьмой выход 83 первого распределителя 44 через восемнадцатый выход 83 блока 18 соединен через пятый управляющий вход 83 блока 17 с первыми управляющими входами первого 23 и второго 24 узлов масштабирования и вторыми управляющими входами второго 21 и третьего 22 узлов возведения ,в квадрат.

Восьмой выход 84 первого распределителя 44 через девятнадцатый выход 84 блока 18 соединен через шестой

узла 32 сложения.

Двенадцатый выход S8 первого распределителя 44 через двадцать третий выход 88 блока 18 соединен через деog сятый управляющий вход 88 блока 17 с вторым управляющим входом первого узла 32 сложения и первым управляющи входом узла 35 умножения.

Тринадцатый выход 89 первого f uc40 пределителя 44 через двадцать четвер тый выход 89 блока 18 соединен с первым управляющим входом 89 блока 15 умножения и вторым управляющим : . : входом 89 блока 14 извлечения ратного корня, а через одиннадцатый управляющий вход 89 блока 17 - с вторым управляющим входом узла 35 умножения..

Четырнадцатый выход 91 первого распределителя 44 соединен со счетным входом второго триггера 42 блока 18 управления.

50

55

Пятый 80 и двенадцатый 88 выходы первого распределителя 44 соединены дополнительно с первым и вторым входами шестого элемента ИЛИ 56, выход которого через шестнадцатый выход 81 блока 18 соединен через третий

узла 32 сложения.

Двенадцатый выход S8 первого распределителя 44 через двадцать третий выход 88 блока 18 соединен через десятый управляющий вход 88 блока 17 с вторым управляющим входом первого узла 32 сложения и первым управляющим входом узла 35 умножения.

Тринадцатый выход 89 первого f ucпределителя 44 через двадцать четверг тый выход 89 блока 18 соединен с первым управляющим входом 89 блока 15 умножения и вторым управляющим : . входом 89 блока 14 извлечения квад ратного корня, а через одиннадцатый управляющий вход 89 блока 17 - с торым управляющим входом узла 35 умножения..

Четырнадцатый выход 91 первого распределителя 44 соединен со счетным входом второго триггера 42 блока 18 управления.

55

Пятый 80 и двенадцатый 88 выходы первого распределителя 44 соединены дополнительно с первым и вторым входами шестого элемента ИЛИ 56, выход которого через шестнадцатый выход 81 блока 18 соединен через третий

91

управляющий вход 81 блока 17 с управляющим входом узла 34 задания конс- танты, выход которого соединен с информационным входом первого узла 20 возведения в квадрат и первым . информационным входом узла 35 умножения .

Выход первого узла 20 возведения в квадрат соединен с информационными входами третьего узла 25 масштабирования, второго узла 21 возведения в квадрат и первого узла 27 вычитания.

Второй узел 28 вычитания соединен информационным входом с выходом третьего узла 25 масштабирования, а выходом - с первым информационным входом второго узла 33 сложения, соединенного вторым информационным входом с 1выходом первого узла 23 масштабиро

вания, а выходом - с первым информационным входом первого узла 30 деления.

Выход третьего узла 29 вычитания соединен с информационными входами третьего у:зла 22 возведения в квадрат и четвертого узла 26 масштабирования, выходы которых соединены с информационным входом второго узла 24 масштабирования и вторым информационным входом второго узла 31 деления соответственно, первый информационный вход последнего соедине с выходом первого узла 27 вычитания.

Выход второго узла 24 масштабирования соединен с вторым информационным входом первого узла 30 деления, выход которого соединен с первым информационным входом первого узла 32 сложения, соединенного вторым информационным входом с выходом второго узла 31 Деления, а выходом - с вторым информационным входом узла 35 умножения. Выход второго узла 21 возведения в квадрат соединен с информационным входом первого узла 23 масштабирования.

Выход узла 38 задержки через седьмой выход 70 блока 18 соединен с вторым управляющим входом первого квадратора 10 и первым управляющим входом второго накапливающего сумматора 7.

Выходы первого 51, второго 52, третьего 53, четвертого 54 и пятого 55 элементов ИЛИ соединены через четвертый 65, пятый 66, девятый 72, десятый 73 и одиннадцатый 76 выходы блока 18 с первыми управляющими вхо1

1483

0

15

0

0

дами 65 и 66 счетчика 5 и первого накапливающего сумматора 6,и вторыми 72, 73 и 76 управляющими входами i счетчика 5, первого накапливающего сумматора 6 и первого блока 8 деления соответственно.

Выходы восьмого 58 и девятого 59 элементов ИЛИ через двадцать восьмой 98 и тридцатый выходы 102 блока 18 соединены с первым управляющим входом 98 первого блока 8 деления и первыми управляющими входами 102 второго блока 2 памяти и второго блока 13 вычитания соответственно, а выход девятого элемента ИЛИ 59 дополнительно соединен с вторьм входом пятого элемента ИЛИ 55 и с инверсным входом второго элемента ЗАПРЕТ 40, выход которого соединен со счетным входом третьего триггера 43.

Первый выход 92 второго распределителя 45 соединен с прямым входом второго злемента ЗАПРЕТ 40, а через 5 двадцать пятый выход 92 блока 18 - с вторым управляющим входом 92 первого блока 1 памяти.

Второй выход 93 второго распределителя 45 через двадцать шестой выход 0 93 блока 18 соединен с первым управляющим входом 93 блока 16 сравнения и вторыми управляющими входами 93 блока 15 умножения и второго блока 13 вычитания, а третий выход 94 вто- рого распределителя 45 через двадцать седьмой выход 94 блока 18 соединен с вторым управляющим входом 94 блока 16 сравнения.

Первый выход 97 третьего распределителя 46 соединен с вторыми входами третьего 53, четвертого 54 и восьмого 58 элементов ШШ.

Второй выход 99 третьего распределителя 46 соединен с третьим входом пятого элемента ИЛИ 55, а через двадцать девятый выход 100 блока 18 - с первым управляющим входом 100 блока 19 регистрации.

Третий выход 101 третьего распределителя 46 соединен с вторым входом седьмого элемента ШШ 57.

Устройство работает следующим образом.

На первый управляющий вход 60 уст - ройства (фиг. 3), являющийся первым входом блока 18, подается сигнал 1. который поступает на первый вход седьмого элемента ИЛИ 57 а через первый выход 61 блока 18 - (фиг, 1)

5

0

5

0

5

сигнал 1 (фиг. Аа), через второй выход 62 блока 18 поступает на третьи управляющие входы 62 (Сброс) счетчика 5, первого 6 и второго 7 накапливающих сумматоров и первого 1 и второго 2 блоков памяти, сбрасывая их

управляющие входы (Разрешение при- g ема) первого блока 1 памяти и перво

11140148312

на второй управляющий вход 61ЗАПРЕТ 39, третий выход 64 блока 18,

(Cбpoc) блока 19 регистрации, сбра- через который проходят на первые сывая его содержимое в нуль. С выхода седьмого элемента ИЛИ 57 блока 18

го квадратора 10,. а также проходят на первые входы первого 51 и второго 52 элементов ИЛИ, с выходов которых ТИ через четвертый 65 и пятый 66 10 выходы блока 18 проходят на первые управляющие входы (Разрешение прийодержимое в нуль.

Сигнал 1 с выхода седьмого элемента ИЛИ 57 дополнительно поступает на второй вход (Сброс) второго рас- 15 предепителя 45, переводя его в начальное состояние, а также на входы Установка единицы первого 41, второго 42 и третьего 43 триггеров, переводя их в состояния 1. На пря- 20 MEJK Q и инверсных Q выходах триггеров 41-43 фбрмируются длительные .. сигналы 1 и О соответственно (фиг. 4 б-ж, t -е t.

По сигналам 1 и О, идущим с прямого и инверсного выходов первого триггера 41 на первые входы первого 47 и второго 48 элементов И соответственно, первый элемент И 47 подготавливается к открытию, а второй эле- 30 мент И 48 закрывается. По сигналам 1 и О, идущим с прямого и инверсного выходов второго триггера 42 на

ема) счетчика 5 и первого накапливающего сумматора 6 соответственно.

На информахщонный вход 67 устрой- Ктва, являкнцийся третьим входом блока 18, синхронно с ТИ поступают за- ;кодированные данные по следующей структуре (фиг. 4к):

(х(1), , {х(2) 5, ..., {х(п-1)5 ,

И .Mr.

25 где fx(i)j - двоичный г-разрядный код i-ro данного в выборке;

{ j. - код признака конца данных (ПК), во всех разрядах которого нули,

которые через информационный вход коммутатора 37, его выход и шестой выход 68 блока 18 проходят в первый блок 1 третьи входы второго 48 и третьего памяти через его информационный вход, 49 элементов И соответственно, третий .jg где запоминаются, на первый блок 3 элемент И 49 закрывается, а второй элементов ШШ, в первый квадра гор 10 элемент И 48 сохраняет закрытое сое- через его информационный вход, где тояние.формируются коды {зс (1)у , а также

По сигналам 1 и О, идущим с в первый накапливающий сумматор 6 прямого и инверсного выходов третьего 40 через его первый (суммирующий) инфор- триггера 43 на первые входы третьего 49 и четвертого 50 элементов И соответственно, третий элемент И 49 сохраняет свое закрытое состояние, а четвертый элемент И 50 закрывается. Затем на второй управляющий вход 63 устройства, являющийся вторым входом блока 18, подается сигнал 1 (фиг.. 4з), проходящий на вход Пуск генератора 36, который формирует на выходе ТИ с периодом следования (фиг. 4и), поступающие на вторые входы первого 47, второго 48. третьего 49 и -четвертого 50 элементов И.

Но, так как только первый элемент И 47 подготовлен к открытию, ТИ, про- .ходя только через этот элемент, поступают на управляюхий вход коммута- тотэа 37. прямой вход первого элемента

мационный вход, где формируются коды f(Sx1(i) Sx1(i-1)5 + {x(i)} ,

fsxUO) {ф,

45 Коды x(i) поступают также и На первый блок 3 элементов ИЛИ, который имеет г входов (по количеству разрядов кода, подаваемого на блок). По.этому при наличии 1 хоти бы в од- t ном разряде входного кода, й „выходе этого блока всегда сигнал 1 (фиг. 4л, t t,). Эти сигналы 1 поступают в счетчик 5 через его первый (сум:мирующий) информационный вход, где формируются коды (i)j (i-1)j + + {П , ) т.е. осуществляется подсчёт текущего количества элементов выборки, поступающих на вход устройства, а через четвертый вход 69 блока 18 пос50

55

управляющие входы (Разрешение при- ема) первого блока 1 памяти и первочерез который проходят на первые

го квадратора 10,. а также проходят на первые входы первого 51 и второго 52 элементов ИЛИ, с выходов которых ТИ через четвертый 65 и пятый 66 выходы блока 18 проходят на первые управляющие входы (Разрешение приема) счетчика 5 и первого накапливающего сумматора 6 соответственно.

На информахщонный вход 67 устрой- Ктва, являкнцийся третьим входом блока 18, синхронно с ТИ поступают за- ;кодированные данные по следующей структуре (фиг. 4к):

в первый накапливающий сумматор 6 через его первый (суммирующий) инфор-

мационный вход, где формируются коды (Sx1(i) Sx1(i-1)5 + {x(i)} ,

fsxUO) {ф,

Коды x(i) поступают также и На первый блок 3 элементов ИЛИ, который имеет г входов (по количеству разрядов кода, подаваемого на блок). Поэтому при наличии 1 хоти бы в од- t ном разряде входного кода, й „выходе этого блока всегда сигнал 1 (фиг. 4л, t t,). Эти сигналы 1 поступают в счетчик 5 через его первый (суммирующий) информационный вход, где формируются коды (i)j (i-1)j + + {П , ) т.е. осуществляется подсчёт текущего количества элементов выборки, поступающих на вход устройства, а через четвертый вход 69 блока 18 пос

на первые входы третьего 53, четвер- g того 54 и восьмого 58 элементов ИЛИ,

131401Д8314

тупают на инверсный вход первого эле- Сигнал 1 с первого 71 выхода мента ЗАПРЕТ 39, Так как на оба входа первого распределителя 44 поступает первого элемента ЗАПРЕТ 39 поданы 1. то на его выходе в соответствии с

приведенной таблицей истинности фор- через восьмой выход 71 блока 1.8 мируются сигналы О идущие на на первый управляющий вход 71 (Раз- счетный вход первого триггера 41 решение приема) второго блока 9 (см, фиг. 4м, ,), состояние кото- деления и второй управляющий вход рого не изменяется.10 71 (Передача кода) второго 7 накапТактовые импульсы с выхода первого элемента И 47 поступают также на узел 38 задержки, с выхода которого, задерживаясь на время ь/2, через седьмой выход 70 блока 18 проходят на 15 29 вычитывания, первый управляющий вход 70 (Разре- г...... in шение приема) второго накапливающего сумматора 7 и второй управляющий вход 70 (Передача кода) первого квадратора 10, на выходе которого

ливающего сумматора, а через первый управляющий вход 71 блока 17 поступает на первый управляющий вход (Разрешение приема) третьего узла

Сигналы 1 с выходов третьего 53, четвертого 54 и восьмого 5В элементов ИЛИ через девятый 72, десятый 73 и двадцать восьмой 98 выходы блока 18

- ,. 20 поступают на вторые 72 и 73 управляформируются коды (i))). поступа- ющие входы Передача кода) счетчика ющие во второй накапливающий сумматор 5 и первого накапливающего сумматора 7 через его информационный вход, где 6 и первый управляющий вход 98 (Раз- ормируются коды {Sx2(i) } ,i {Sk2(i-1),4+ решение приема) первого блока 8 де- + (i)| , где | Sx2(0) ления соответственно.

После того, как все коды Гх(х) Код {S(n)j с выхода счетчика 5 поступили в устройство, в первом -поступает в первый 8 и второй 9 бло- блоке 1 памяти сказываются записанны- ки деления через их вторые информа- ми все коды fx(i)j , i T7n, а ционные входы, а через их первые содержимое счетчика 5, первого 6 и 30 информационные входы поступают коды второго 7 накапливающих сумматоров (п) (п), с выходов пер- становится равным {s (п)31. вого 6 и второго 7 накапливающих сум- Sx1(n)}p и rSx2(n) соответствен- маторов соответственно. Первый 8 и но, на первый блок 3 элементов ИЛИ . второй 9 блоки деления формируют коды подаются г нулей кода ПК, на выходе 35 первого ,}г и второго fjUj J началь ных моментов соответственно. Код

которого формируется сигнал О (фиг, 4л, t t,), поступающий через четвертый вход 69 блока 18 на инверсный вход первого элемента ЗАПРЕТ

fs(n)V с выхода счетчика 5 поступает также через информационный вход 74 блока 17 /в третий гузел 29 вычита39, на выходе которого в соответствии 40 «ия через его информационный вход, с таблицей истинности, формиру- где формируется код S(n)j - f2j . «ется сигнал 1, поступающий на счет- Сигнал 1 с второго выхода 75 ный вход первого триггера 41 (фиг. 4м, первого распределителя 44 поступает t t,). После спада этого сигнала на первый вход пятого элемента ИЛИ 55, состояние первого триггера 41 меняет- 45 выхода через одиннадцатый ся на противоположное: на прямом вы- выход 76 блока 18 поступает на вто- ходе формируется длительный сигнал РОЙ управляющий вход 7.6 (Передача О, а на инверсном - длительный сиг- жода) первого блока 8, деления. Этот нал t (фиг. 46, в; t t,). По этим же сигнал 1 с второго выхода 75 сигналам первый элемент И 47 закрыва- 50 первого распределителя 44 через две- ется, прекращая пропуск тактовых импульсов, что приводит к блокированию коммутатора 37, а следовательно, и информационного входа устройства, а второй элемент И 48 открывается и ..начинает пропускать тактовые импульсы на вход первого распределителя 44 (фиг. 4н, t t,), которые распределяются по его выходам (фиг. 40п).

надцатый выход 77 блока 18 поступает ,на первый управляющий вход 77 (Раз- решение приема) второго квадратор

ра 11.

55

Код fw,, с выхода первого блока 8 деления поступает на второй квадратор 11 через его информационный вход, где формируется код «

на первые входы третьего 53, четвер- того 54 и восьмого 58 элементов ИЛИ,

Сигнал 1 с первого 71 выхода первого распределителя 44 поступает

через восьмой выход 71 блока 1.8 на первый управляющий вход 71 (Раз- решение приема) второго блока 9 деления и второй управляющий вход 71 (Передача кода) второго 7 накап29 вычитывания, г...... in

ливающего сумматора, а через первый управляющий вход 71 блока 17 поступает на первый управляющий вход (Разрешение приема) третьего узла

ных моментов соответственно. Код

fs(n)V с выхода счетчика 5 поступает также через информационный вход 74 блока 17 /в третий гузел 29 вычита«ия через его информационный вход, где формируется код S(n)j - f2j Сигнал 1 с второго выхода 75 первого распределителя 44 поступает на первый вход пятого элемента ИЛИ 5 выхода через одиннадцатый выход 76 блока 18 поступает на вто- РОЙ управляющий вход 7.6 (Передача жода) первого блока 8, деления. Этот же сигнал 1 с второго выхода 75 первого распределителя 44 через две-

надцатый выход 77 блока 18 поступает ,на первый управляющий вход 77 (Раз- решение приема) второго квадратор

ра 11.

«ия через его информационный вход, где формируется код S(n)j - f2j . Сигнал 1 с второго выхода 75 первого распределителя 44 поступает на первый вход пятого элемента ИЛИ 55 выхода через одиннадцатый выход 76 блока 18 поступает на вто- РОЙ управляющий вход 7.6 (Передача жода) первого блока 8, деления. Этот же сигнал 1 с второго выхода 75 первого распределителя 44 через две-

Код fw,, с выхода первого блока 8 деления поступает на второй квадратор 11 через его информационный вход, где формируется код «

Причем код ((кЛр с выхода первого блока 8 деления, поступая также на информационный вход блока 19 регистрации и первый информационный вход второго блока 13 вычитания, в эти . блоки не проходит, так как на первые управляющие входы (Разрешение приема) этих блоков поданы сигналы О (в дальнейшем такие ситуации не рассматриваются) .

Сигнал 1 с третьего выхода 78 первого распределителя А4 через тринадцатый выход 78 блока 18 поступает на вторые управляющие входы 78 (Передача кода) второго блока 9. деления и второго квадратора 11 и первый управляющий вход 78 (Разрешение приема) первого блока 12 вычитания.

Коды f |U-i 5ip и fjii f с выходов второг блока 9 деления и второго квадратора 11 поступают в первый блок 12 вычитания через его первый и второй информационные входы соответственно, где формируется код (С5. flUtV- - f U «.iJr

Сигнал 1 с четвертого выхода 79 первого распределителя 44 через че тырнадцатый выход 79 блока 18 поступает на второй управляющий вход 79 (Передача кода) первого блока 12 вычитания и первый управляющий вход 79 (Разрешение приема) блока 14 из влечения квадратного корня. Код fcfV с выхода первого блока 12 вычитания поступает в блок 14 извлечения ; квадратного корня через его информационный вход, где формируется код f0)p .

Сигнал 1 с пятого выхода 80 пер вого распределителя 44 через пятнадцатый выход 80 блока 18 и второй управляющий вход 80 блока 17 поступает на первый управляющий вход (Разрешение приема) первого узла 20 воз- ведения в квадрат блока 17. Этот же сигнал 1 с пятого выхода 80 первого распределителя 44 через первый вход шестого элемента ИЛИ 56, его выход, шестнадцатый выход 81 бло ка 18 и третий управлякиций вход 81 блока 17 поступает на управляющий вход (Передача кода) узла 34 задания константы блока 17, с выхода

которого код поступает в первый узел 20 возведения в квадрат блока 17, где формируется код f (}.

Сигнал 1 с шестого выхода 82 первого распределителя 44 через сем.

соответственно,

надцатый выход 82 блока 18 и четвертый управляющий вход 82 блока 17 проходит на вторые управляющие входы (Передача кода) первого узла 20 возведения в квадрат блока 17 и третьего узла 29 вычитания, первые управляющие входы (Разрешение приема) второго 21 и третьего 22 узлов возведения в квадрат, первого узла 27 вычитания и третьего 25 и четвертого 26 узлов масштабирования.

Код } с выхода первого узла 20, возведения в квадрат поступает во .: второй уЗел 21 возведения в квадрат, третий узел 25 масштабирования и пер- вый узел 27 вычитания через их информационные входы, где формируются коды

32, X , и (31 г -{ ХПг тветственно.

Код .{s (п) р 2 ; с выхода третьего узла 29 вычитания поступает в третий

.узел 22 возведения в квадрат и четвертый узел 26 масштабирования через их ипформа1щонныё входы, где формируются коды ({s(n) 5y,- Г2 р2 Ич

., X (Cs(n)j -{2} .соответственно.

Сигнал 1 с седьмого выхода 83 первого распределителя 44 через восемнадцатый выход 83 блока 18 и пятый управляющий вход 83 блока 17 проходит на вторые управляющие входы (Передача кода) второго 21 и третьего 22 узлов возведения в квадрат и первые управляющие входы (Разрешение приема) первого 23 и второго 24 узлов масштабирования.

Код f 5 h выхода второго узла 2 i возведения в квадрат поступает в первый узел 23 масштабирования через его информационный вход, где формируются код Г5 5 X {-Х . Код (ftS) -.

- 21 , Гс выхода третьего узла 22

40 45 Q

возведения в квадрат поступает во второй узел 24 масштабирования через его информационный вход, где форми- руется код 96 х ( fs(h) J { -.-Jfl X- J 2j ). Сигнал 1 с восьмого выхода 84 первого распределителя 44 через девятнадцатый выход 84 блока t8 и шестой управляющий вход 84 блока 17 поступает на второй управляю- gg вход (Передача кода) третьего ,узла 25 масштабирования ц первый управляющий вход (Разрешение приема) второго узла 28 вычитания. Код t32jp х

X 3

с вькода третьего узла 25

масштабирования поступает во второй узел 28 вьтитания через его информационный вход, где формируется код (31/- {32|,к,,.

го 31 узлов деления и первый управляющий вход (Разрешение приема) первого узла 32 сложения.

Коды f А J, и {в с выходов первого 30 и второго 31 узлов деления поступают в первый узел 32 сложения через его первый и второй информацион-. ные входы, где формируется код 1 + А ,(Bj. .

Сигнал 1 с двенадцатого выхода 88 первого распределителя 44 через двадцать третий выход 88 блока 18 и десятый управляющий вход 88 блока 17

Сигнал 1 с девятого выхода 85 первого распределителя 44 через двадцатый выход 85 блока 18 и седьмой управляющий вход 85 блока 17 поступает на вторые управляющие вХодЫ (Пе- ю редача кода) первого узла 23 масштабирования и второго узла 28 вычитания и,первый управляющий вход (Разрешение приема) второго узла 33 сложения. Коды fs(, xl-f A j, X 15 поступает на второй управляющий вход X выходов первого узла 23 (Передача кода) первого узла 32 ; . масштабирования и второго узла 28 сложения и первый управляющий вход вычитания соответственно проходят во (Разрешение приема) узла 35 умиоже- :второй узел 33 сложения через его второй и первый информационные вхо- 20 ды, где формируется код Гз.,- f32V х

-Шг -W.

Сигнал 1 с десятого выхода 86 первого распределителя 44 через двадцать первый выход 86 блока 18 и вось-25 вход 81 блока 17 поступает на управ- мой управляющий вход 86 блока 17 пос- ляющий вход (Передача кода) узла тупает на вторые управляющие входы (Передача кода) второго 24 и четвертого 26 узлов масштабирования, первого узла 27 вычитания и второго узла 33 сложения и первые управляющие входы (Разрешение приема) первого 30 и второго 31 узлов деления. Коды 3, - 32) X , + {Sl, X - i; и (96, X (х(п)}, ) с выхода второго узла 33

ния.

Этот же сигнал 1 с двенадцатого выхода 88 первого распределителя 44 через второй вход шестого элемента ИЛИ 56, его выход, шестнадцатый выход 81 блока 18 и третий управляющий

30

i- jf хИ 1

- 2),

35

сложения и второго узла 24 масштаби

рования соответственно поступают в

первый узел 30 деления через его

первый и второй информационные входы, . умножения и второй управляннций вход

, ,..,....

.34 задания константы. Коды f Л и {l + ГA + . выходов узла 34 задания константы и первого узла 32 сложения соответственно поступают в узел 35 умножения через его первый и второй информационные входы, где формируется код , - ({Or + л + Ъ) x( J.

Сигнал 1 с тринадцатого выхода 89 первого распределителя 44 через двадцать четвертый вьгход 89 блока 18 поступает на первый управляющий вход 89 (Разрешение приема) блока 15

где формируется код {A ({З} -Г32У, , , xf),)/

, ..Cs(«)}

-{2 )2.

I Koды|3jr -lyilr и f ({.S(ri)ja - {2)р ) с выходов первого узла 27 вычитания и четвертого узла 26 масштабирования соответственно поступают во второй узел 31 деления через его первый и второй инфор- мационные входы, где формируется код №, f3l, .f,n)/({4, X X lS(n)|j. - 2 ) .

Сигнал 1 с одиннадцатого выхода 87 первого распределителя 44 через двадцать второй выход 87 блока 18 и девятый управляющий вход 87 блока 17 поступает на вторые управляюп е входы (Передача кода) первого 30 и второ89 (Передача кода) блока 14 извлечения квадратного корня, а через одиннадцатый управляющий вход 89 блока 17 поступает на второй управ- с ляющий вход (Передача кода) узла 35 умножения.

Код (orj с выхода блока 14 извлечения квадратного корня непосредственно, а код с выхода узла 35 умножения через выход 90 блока 17 поступают в блок 15 умножения через его второй и первый 90 информационные

входы, где формируется код х

с jr

X С .

Сигнал 1 с четьфнадцатого выхода 91 первого распределителя 44 поступает на счетный вход второго триггера 42, состояние которого (посла спада зтого импульса) меняется на

50

56

го 31 узлов деления и первый управляющий вход (Разрешение приема) первого узла 32 сложения.

Коды f А J, и {в с выходов первого 30 и второго 31 узлов деления поступают в первый узел 32 сложения через его первый и второй информацион-. ные входы, где формируется код 1 + А ,(Bj. .

Сигнал 1 с двенадцатого выхода 88 первого распределителя 44 через двадцать третий выход 88 блока 18 и десятый управляющий вход 88 блока 17

поступает на второй управляющий вход (Передача кода) первого узла 32 ; . сложения и первый управляющий вход (Разрешение приема) узла 35 умиоже-

поступает на второй управляющий вход (Передача кода) первого узла 32 ; . сложения и первый управляющий вход (Разрешение приема) узла 35 умиоже-

вход 81 блока 17 поступает на управ- ляющий вход (Передача кода) узла

ния.

Этот же сигнал 1 с двенадцатого выхода 88 первого распределителя 44 через второй вход шестого элемента ИЛИ 56, его выход, шестнадцатый выход 81 блока 18 и третий управляющий

25 вход 81 блока 17 поступает на управ- ляющий вход (Передача кода) узла

30

35

.34 задания константы. Коды f Л и {l + ГA + . выходов узла 34 задания константы и первого узла 32 сложения соответственно поступают в узел 35 умножения через его первый и второй информационные входы, где формируется код , - ({Or + л + Ъ) x( J.

Сигнал 1 с тринадцатого выхода 89 первого распределителя 44 через двадцать четвертый вьгход 89 блока 18 поступает на первый управляющий вход 89 (Разрешение приема) блока 15

,..,....

89 (Передача кода) блока 14 извлечения квадратного корня, а через одиннадцатый управляющий вход 89 блока 17 поступает на второй управ- ляющий вход (Передача кода) узла 35 умножения.

Код (orj с выхода блока 14 извлечения квадратного корня непосредственно, а код с выхода узла 35 умножения через выход 90 блока 17 поступают в блок 15 умножения через его i второй и первый 90 информационные

входы, где формируется код х

с jr

X С .

Сигнал 1 с четьфнадцатого выхода 91 первого распределителя 44 поступает на счетный вход второго триггера 42, состояние которого (посла спада зтого импульса) меняется на

19

Ч):

противоположное (фиг, 4 г, д, t на прямом выходе Формируется длительный сигнал О, а на инверсном - длительный сигнал 1.е

По сигналу О, идущему с прямого выхода второго триггера 42 на третий вход второго элемента И 48 последний закрывается, прекращая пропуск ТИ на вход первого распределителя 44 10 (фиг. 4 н), а по сигналу 1, идущему с инверсного выхода второго триггера 42 на третий вход третьего элемента И 49, последний открывается и начинает пропускать ТИ на первый вход второго распределителя 45 (фиг, 4 р,- t t), которые распределяются по .его выходам (фиг. 4, с,.т, ). Сигнал 1 с первого выхода 92

тупают во второй блок 13 вычитания через его второй и первый информационные входы соответственно, где формируется код абсолютной величины

(без учета знака) разности шД С/- 1L I г

x(i)j .

После спада сигнала 1, идущего с перного выхода 92 второго распределителя 45, чНа оба входа второго элемента ЗАПРЕТ 40 оказываются поданными сигналы О, что приводит к формированию сигнала О на его выходе, , и следовательно, и сохранению состоя : 15 ния треть его триггера 43 и прохождению ТИ на вход второго распределителя 45.

Сигнал 1 с второго выхода 93

второго распределителя Д5 подается на 20 второго распределителя 45 через двад- ;лрямой вход второго.элемента ЗАПРЕТ Цать шестой выход 93 блока ,18 посту- 40, а через двадцать пятый выхо 92 пает на вторые управляющие входы 93 блока t8 поступает на второй управля- (Передача кода) второго блока 13 ющий вход 92 (Передача кода) пер- вычитания и блока 15 умножения и

25 первый управляющий вход 93 (Разреше35

вого блока 1 памяти.

Код x(i)p , i-1,2, ,.., с выхода блока 1 памяти (фиг, 4 у, t t) через шестой вход 96 блока 18 подается на девятый элемент ИЛИ 59, на выходе которого формируется сигнал 30 1 (фиг. 4 ф, t t). Идущий на инёерсный вход второго элемента ЗАПРЕТ 40, на выходе которого в соответствия с таблицей истинности фор- . мируется сигнал О, идущий на счетный вход третьего триггера 43 (фиг,

4х, ). Состояние этого триггера не изменяется фиг. 4 е, ж, , и,V следовательно, четвёртый элемент И 50 остается закрытым, а третий 40 элемент И 49 открытым.:

Сигнал 1 с выхода девятого элемента ИЛИ 59 поступает также на

второй вход пятого элемента ИЛИ 55, с выхода которого через одиннадцатый 45 выход 76 блока 18 подается на второй управляющий вход 76 (Передача

кода) первого блока 8 дё тения, а через тридцатьЕЙ выход t02 блока tS поступает на первые управляняцие вхо- 50

:ды 102 (Разрещение приема) второго блока 2 памяти и второго блока 13 вычитания,

Код {x(i)jj. с выхода первого блоние приема) блока 16 сравнения, Коды I Г /и,, - {х(г)р1 и ГгЛ xfOj с выходов второго блока 13 вычитания и блока 15 умножения поступают в блок 16 сравнения через его первый и второй информационнее входы соответственно, где формируется сигнал Z результата сравнения: Z 1, если - х(1)И

CirVi r 2 О Сигнал 1 с третьего выхода 94 второго распределителя 45 через двадцать седьмой выход 94 блока 18 поступает на второй управляющий вход 94 (Передача кода) блока 16 сравнения, с выхода которого сигнал Z поступает на второй управляющмй вход (ПбРЗДзча кода) второго блока -2 памяти, а через пятый вход 95 блока 18 поступает на вторые входы первого 51 и второго 52 элементов ИЛИ.

Рассмотрим случай, когда Z 1, т.е. когда значение x(i) считается недостоверным В этом случае на выходах первого 51 и второго 52 элементов ИЛИ формируются сигналы 1, идущие через четвертый 65 и пятый 66 входы блока 18 соответственно на первые 65 и 66 управляющие входы (Разрешение приека 1 памяти поступает-таюке во-вт ч ой ,-,- ма) счетчика 5 и первого накаплива -«5О

бпок 2 памяти через его информаци-г ,онный вход, где запошшается. Этот же

код x(i)3p и код {(U. lfp, идупий с xd) выхода первого блока 8 деления посющего сумматора, а на выходе второго блока 2 памяти появляется код

, идущий на второй блок 4 элементов ИЛИ и второй (вычитающий)

е

10

0148320

тупают во второй блок 13 вычитания через его второй и первый информационные входы соответственно, где формируется код абсолютной величины

(без учета знака) разности шД С/- 1L I г

x(i)j .

После спада сигнала 1, идущего с перного выхода 92 второго распределителя 45, чНа оба входа второго элемента ЗАПРЕТ 40 оказываются поданными сигналы О, что приводит к формированию сигнала О на его выходе, , и следовательно, и сохранению состоя : 15 ния треть его триггера 43 и прохождению ТИ на вход второго распределителя 45.

Сигнал 1 с второго выхода 93

5

0

0 :

5

0

ние приема) блока 16 сравнения, Коды I Г /и,, - {х(г)р1 и ГгЛ xfOj с выходов второго блока 13 вычитания и блока 15 умножения поступают в блок 16 сравнения через его первый и второй информационнее входы соответственно, где формируется сигнал Z результата сравнения: Z 1, если - х(1)И

CirVi r 2 О Сигнал 1 с третьего выхода 94 второго распределителя 45 через двадцать седьмой выход 94 блока 18 поступает на второй управляющий вход 94 (Передача кода) блока 16 сравнения, с выхода которого сигнал Z поступает на второй управляющмй вход (ПбРЗДзча кода) второго блока -2 памяти, а через пятый вход 95 блока 18 поступает на вторые входы первого 51 и второго 52 элементов ИЛИ.

Рассмотрим случай, когда Z 1, т.е. когда значение x(i) считается недостоверным В этом случае на выходах первого 51 и второго 52 элементов ИЛИ формируются сигналы 1, идущие через четвертый 65 и пятый 66 входы блока 18 соответственно на первые 65 и 66 управляющие входы (Разрешение прие xd)

ющего сумматора, а на выходе второго блока 2 памяти появляется код

xd)

, идущий на второй блок 4 элементов ИЛИ и второй (вычитающий)

информационный вход первого и накапливающего .сумматора 6,

На выходе второго блока 4 элементов ИЛИ формируется сигнал 1, идущий на второй (вычитающий) информационный вход счетчика 5. Следовательно, содержимое счетчика 5 уменьшается на единицу, т.е. становится равным

{S lr {S(n)l - {1 5 , а содержи-10 блока мое первого накапливающего сумматора 6 становится равным

15

4 ф, t t), идущий через второй вход пятого элемента ИЛИ 55, его выход и одиннадцатый выход 76 блока 18 на второй управляющий вход 76 (Передача кода) первого блока 8 деления, а через тридцатый выход 102 блока 18 поступает на первые управляющие входы 102 (Разрешение приема) второго

2 памяти и второго блока 13 вычитания,

Этот сигнал О запрещает передачу кода ((u,V из первого блока 8 деления, а также прием кода {Ф во второй блок 2 памяти и прием кодов f|4ili f ° второй блок 13 вычитания.

Этот же сигнал О с выхода девятого элемента ИЛИ 59 подается также на инверсный вход второго элемента ЗАПРЕТ 40, на выходе которого в соответствии с таблицей истинности формируется сигнал 1, идущий на На выходе второго блока 4 элемен- 25 счетный вход третьего триггера 43 тсгв ИЛИ появляется сигнал О, идущий (фиг. 4, х, t t3), что приводит поена второй (вычитающий) информационный .ле его спада к изменению состояния вход счетчика 5. На выходах первого триггера на противоположное (фиг. 51 и второго 52 элементов ИЛИ также 4 е, ж, ,): на прямом выходе фор- формируются сигналы О, идущие через ЗО мируется длительный сигнал О, зак

(8x1), sxKn) (i)}, .

Рассмотрим случай, когда Z 0, т.е. когда значение x(i) считается достоверным. В этом случае информация с второго блока 2 памяти не считывается, т.е. на его выходе появляется 20 код ,. идущий на второй блок 4 элементов ИЛИ и второй (вычитающий) информационный вход первого накапливающего сумматора 6.

рывающий третий элемент И 49, который прекращает пропускать ТИ на вход второго распределителя 45, а на инП1 |Г

четвертый 65 и пятый 66 выходы блока 18 на первые 65 и 66 управляющие входы (Разрешение приема) счетчика 5 и первого накапливающего сумматора 6 соответственно. Следовательно, содер- - открывающий четвертый элемент И 50, жимое счетчика 5 и первого накаплива- который начинает пропускать ТИ с вы- ющего сумматора 6 не изменяется. хода генератора 36 на вход третьего Таким образом, после проверки на распределителя 46 (фиг. 4 ц, ), достоверность любого значения x(i), i 1,n, независимо от результата проверки ТИ продолжают поступать на вход второго распределителя 45 и расверсном - длительный сигнал 1

распределяемые, по их выходам (фиг. 40 4ч, ш; t t,)

Сигнал 1 с первого выхода 97, третьЪго распределителя 46 (фиг. 3) поступает на вторые входы третьего 53, четвертого 54 и восьмого 58 элемен- g тов НИИ, с выходов которых через де- вятьй 72, десятый 73 и двадцать восьмой 98 выходы блока 18 соответственно поступают на вторые управляющие входы 72 и 73 (Передача кода) счетчика

прёделяться по его выходам.

После того, как все значенич x(i), i 1,n, проверены на достоверность, на первом 92 выходе второго распре,- делителя 45 вновь формируется сигнал t (фиг, 4 с, t t), идущий на прямой вход второго элемента ЗАПРЕТ 40, а через двадцать пятый выход 92 блока t8 поступающий на второй управляющий вход 92 (Передача кода) первого блока 1 памяти.

На выходе первого блока 1 памяти появляется код признака конца данных (фиг. 4 у, t t), который через шестой вход 95 блока 18 поступает на девятый элемент ИЛИ 59, на выходе которого формируется сигнал О (фиг.

рывающий третий элемент И 49, который прекращает пропускать ТИ на вход второго распределителя 45, а на иноткрывающий четвертый элемент И 50, который начинает пропускать ТИ с вы- хода генератора 36 на вход третьего распределителя 46 (фиг. 4 ц, ),

П1 |Г

открывающий четвертый элемент И 50 который начинает пропускать ТИ с в хода генератора 36 на вход третьег распределителя 46 (фиг. 4 ц,

версном - длительный сигнал 1

открывающий четвертый элемент И 50, который начинает пропускать ТИ с вы- хода генератора 36 на вход третьего распределителя 46 (фиг. 4 ц, ),

распределяемые, по их выходам (фиг. 4ч, ш; t t,)

Сигнал 1 с первого выхода 97, тре; тьЪго распределителя 46 (фиг. 3) поступает на вторые входы третьего 53, четвертого 54 и восьмого 58 элемен- тов НИИ, с выходов которых через де- вятьй 72, десятый 73 и двадцать восьмой 98 выходы блока 18 соответственно поступают на вторые управляющие входы 72 и 73 (Передача кода) счетчика

5и первого накапливающего сумматора

6и первый управляющий В1ход 98 (Разрешение приема) первого блока 8 деления соответственно.

Оставшееся содержимое {(8x1) первого накапливающего сумматора 6 и Sj счетчика 5 с их выходов, поступает в первый блок 8 деления через| его первый и второй информационные входы соответственно, где формирует-

23

ся код истинного среднего значения ГтД , вычисленного по достоверным данньм:

Ы.

I(Sj1) ir

i

Сигнал 1 с второго вьпсода 99

третьего распределителя 46 поступает на третий вход пятого элемента ИЛИ 55, с выхода которого через один- надцатьй выход 76 блока 16 проходит на второй управляющий вход (Передача

третьего распределителя 46 через

двадцать девятый выход 100 блока 18

проходит на первый управляющий вход

100 (Разрешение приема) блока 19

регистрации. Код с выхода

первого блока 9 деления поступает

только в блок 19 регистрации через

нения и блок регистрации, причем выход счетчика соединен с входами делителя первого и второго блоков i деления и информационньвя входом блока

20 задания корректирующих коэФфидиентрв,-, выход которого соединен с входом первого сомножителя блока умножения, соединенного входом второго сомножителя с выходом блока извлечения квад- его информационный вход, где регистри-..

25 ратного корня, а выходом - с первым

«%тга mf еу IT т гн13-гч

информационным входом блока срайне . .ния, второй информационный вход которого соединен с выходом второго блока вычитания, вход уменьшаемого

руется для дальнейшего использования (при необходимости визуального представления значения m

.,„ в десятичном коде осуществляется преобразование

двоичного кода Гт. в десятичный

It 30 которого соединен с выходом первого с помощью соответствующих преобразова- „

телей кодов, не показанных на фиг. 1).

Сигнал 1 с третьего выхода 101 третьего распределителя 46 поступает на второй вход седьмого элемента ИЛИ

35

блока деления, выходы первого и второго накапливакядих сумматоров соот- , ветственно Соединены с входами делимого первого и второго блоков деления, выходы которых соединены с информационным входом второго кв адра- тора и входом уменьшаемого первого блока вычитания соответственно,- вход вычитаемого и выход которого со57, с выхода которого (фиг. 4 а, t t)- проходит на входы Установка единицы триггеров 41-43, переводя их в едини тое состояние, а на второй

вход (Сброс) второго распределителя- диненыс выходом второго квадратора 45, переводя его в начальное состоя- „ информационным входом блока извле- кие, а через второй выход 62 блока 18 проходит на третьи Управляюш;ие входы 62 (Сброс) первого 1 и второго 2 блоков памяти, счетчика 5 и первого 6 капливающего сумматора, а блок задачения Квадратного корня соответствен но, выход первого квадратора соединен с информационным входом второго на.

и второго 7 накапливающих сумматоров, сбрасывая их содержимое в нуль.

Следовательно, устройство готово для обработки следующей выборки, подаваемой на его информационный ;вхрд 67.

Преимуществом предлагаемого устройства по сравнению с известньм является повышенное быстродействие, так как после каждого удаления недостоверного значения не требуется выделять минимальное и максимальное значения и осуществлять пересчет оценок среднего и среднеквадратично50

55

ния корректирующих коэффициентов содержит с первого по третий узлы возведения на квадрат, с первого по . четвертый узлы : масштабирования, с . первого по третий узлы вычитания, первый и второй узлы деления, первый и второй УЗЛЫ сложения, узел задания константы и узел умножения, выход первого узла возведения в квадрат соединен с информационным входом второго узла возведения в квадрат, выход которого соединен с информационным входом первого узла масштабирования, выход третьего узла вычита140148324

го значений и корректирующих коэффициентов.

(-Формула изобретения

блока деления, выходы первого и второго накапливакядих сумматоров соот- , ветственно Соединены с входами делимого первого и второго блоков деления, выходы которых соединены с информационным входом второго кв адра- тора и входом уменьшаемого первого блока вычитания соответственно,- вход вычитаемого и выход которого со диненыс выходом второго квадратора „ информационным входом блока извле- капливающего сумматора, а блок зада диненыс выходом второго квадратора „ информационным входом блока извле- капливающего сумматора, а блок задачения Квадратного корня соответствен но, выход первого квадратора соединен с информационным входом второго на.

диненыс выходом второго квадратора „ информационным входом блока извле- капливающего сумматора, а блок зада

ния корректирующих коэффициентов содержит с первого по третий узлы возведения на квадрат, с первого по . четвертый узлы : масштабирования, с . первого по третий узлы вычитания, первый и второй узлы деления, первый и второй УЗЛЫ сложения, узел задания константы и узел умножения, выход первого узла возведения в квадрат соединен с информационным входом второго узла возведения в квадрат, выход которого соединен с информационным входом первого узла масштабирования, выход третьего узла вычита251401483 .26

ния соединен с информационным входомвходом второго квадратора, с вторым третьего узла возведения в квадрат,управляющим входом второго блока выход которого соединен с информаци-деления, четырнадцатым выходом - с онным входом второго узла масштабиро-первым управляющим входом блока изв.- вания, информационный вход третьеголечения квадратного корня и вторым узла вычитания является информаци-управляющим входом первого блока вы- онным входом блока задания корректи-читания, пятнадцатым, шестнадцатым, рующих коэффициентов, выход третьегосемнадцатым,восемнадцатым,девятнад- узла масштабиро.вания соединен с ин- двадцатью, двадцать первым, формационньм входом второго узладвадцать вторым, двадцать третьим и вычитания, выход которого соединен сдвадцать четвертым выходами - с вторым, входов первого слагаемого второго .третям, четвертым, пятым, шестым, узла сложения, выход первого узла деле-седьмым, восьмым, девятьш, десятым , ния соединен с входом первого слагаемо- gи одиннадцатым управляющими входами : го пер во го узла сложения, а выход узла-блока задания корректируюпр1х коэффи- умножения является выходом блока за-циентов соответственно, двадцать Дания корректирукицихI коэффигщентов,пятым выходом - с вторым управляющим отличающееся тем, что,входом первого блока памяти, двад- с целью повьшения быстродействия шестым выходом - с первыми уп- устройства, в него введены второйравляющими входами блока сравнения, блок памяти, первый и второй элемен-блока умножения и второго блока вы- ты ИЛИ и блок управления, причемчитания, двадцать седьмым выходом - блок управления соединен первым выхо-с вторым управляющим входом блока срав- дом с первым управляющим входом 25нения, двадцать восьмым выходом - с блока регистрации, вторым выходом -вторым управляющим входом первого . с входами сброса счетчика, первого иблока деления, двадцать девятым второго блоков памяти и первого и вто-.выходом - с вторым управляющим вхо- рого накапливающих сумматоров, тре-дом блока регистрации, тридцатым тьим выходом - с первь1ми управляющими 30выходом -с первым управлякм19 м входом входами первого блока памяти и пер- второго блока памяти и вторым управ- вого квадратора, четвертым и пятым ляющим входом второго блока вычита- выходами - с первым управляющим вхо-ния, двадцать четвертым выходом блок дом счетчика и входом суммированияуправления соединен с вторым управ- первого накапливающего сумматора соот-ляющим входом блока умножения и вто- ветственно, шестым выходом - с входомрым управляющим входом блока извлече- суммирования первого накапливающего .ния квадратного корня, первый, второй сумматора с информационными входамии третий входы блока управления явля- первого квадратора, первого блокаются первым и вторым управляющими : памяти и с входами первого блока эле- ,.входами и информационным входом уст- ментов ИШ, седьмым выходом - с первымройства соответственно, четвертый : управлякщим входом второго накапли-вз од блока управления соединен с вы- вающего сумйатора и вторым управля-ходом первого блока элементов ИЛИ, ющим входом первого квадратора, вось-пятый вход - с выходом блока сравне- мым выходом - с первыми управляющиминия, а шестой вход - с выходом перво- входами блока задания корректирующих го блока памяти, выход блока сравне- коэффициентов и второго блока деле-ния соединен с вторым управляющим НИИ, с вторым управляющим входомвходом второго блока памяти,соеди-. второго накапливающего сумматора,ненного выходом с входом вычитания девятым, десятым и одиннадцатым выхо- первого накапливающего сумматора- и дами - с вторыми управляющими входамивходом блока элементов ИЛИ, выход счётчика, первого накапливающегокоторого соединен с вычитающим входом сумматора и с первым управляющим вхо-счетчика, суммирующий вход которого дом первого блока деления соответ-соединен с выходом первого элемента ственно;, двенадцатым выходом - с пер-ИЛИ, выход первого блока памяти соевым управляющим входом второго квад-динен с информационным входом второго ратора, тринадцатым вькодом - с пер-блока памяти и входом вычитаемого вым управляющим входом первого блокавторого блока вычитания, выход перво- вычитываиия и с первым управляющимго блока деления соединен с информа-v

ционным входом блока регистрации, узел задания константы блока задания корректирующих коэффициентов соединён выходом с информационным входом пер- вого узла возведения в квадрат, вхо- дом первого сомноямтеля узла умножения, а управляющим входом - с третьим управляющим входом блока задания корректирующих коэффициентов, первый узел возведения в квадрат выходом дополнительно соединен с информационными входами первого узла вычитания и третьего узла Масштабирования, а первым управляющим входом - с вто- :рым управляющим входом .блока задания корректирующих коэффициентов, второй узел сложения соединен входом второго слагаемого с выходом первого узла масштабирования, а вьпсодом с входом делимого первого узла деления, соединенного входом делителя с выходом второго узла масштабирования, второй узел деления соединен входом Делимого с выходом первого узла вычитания, входом делителя - с выходом четвертого узла масштабирования, а выходом - с входом второго слагаемого первого уз ла сложения, соединенного выходом с входом второго Сомножителя узла Умй ожения, четвертый узел ласштаби-т рования соединен информационным входом с выходом третьего узла вычитания, первый управляющий вход которого соединен с первым управляюш;им входом блока задания корректирующих коэффициентов, первые управляющие входы пер iBoro узла вычитания, второго и третьего узлов возведения в квадрат, третьего и четвертого узлов масютаби- рования, вторые управляющие входы первого узла возведения в квадрат и третьего узла вычитания являются четвертым управляющим входом блока зада- :ния корректирующих коэффициентов, первый управляющий вход второго узла вычитания и второй управлянмций вход третьего у5ла масштабирования являются шестым управляющим входом блока задания корректируюш 1х коэффициентов, первые управляющие входы второго узла сложения и первого узла масштабирова ния И второй управляющий вход второго узла вычитания являются седьмым управляющим входом блока задания корректирующих коэффициентов,вторые управлякицие входы первого узла вычитания,второго узла сложения и четвертого узла масштабирования, первые управлякяцие входы вто-

Q о 25 зо о д -

35

5

рого узла масштабирования и второго узла деления являются восьмым управляющим входом блока задания корректирующих коэффициентов, первые управляющие входы узла умножения и первого узла сложения являются десятым управляющим входом блока задания кор- 1ректирующих коэффициентов, вторые управляющие входы первого узла сложения, первого и второго узлов деления являются девятым управляющим входом блока задания корректирующих коэффициентов, вторые управляющие входы второго и третьего узлов возведения в квадрат, первого и второго узлов масштабирования являются пятым управляющим входом блока задания корректирующих коэффициентов,а второй управляющий вход узла умножения является . одиннадцатым управляюш;нм входом блока задания корректирующих коэффициентов.

pa соединен с первым выходом первого Тзаспределителя импульсов, тактовый вход которого и тактовые входы второго и третьего распределителей импуль сов соединены с выходами второго, тр тьего и четвертого элементов И соответственно, первый вход и первый выход блока управления соединены с первым входом седьмого элемента И, второй вход которого соединен с первым выходом третьего распределителя импульсов, второй вход блока управления соединен с входом Пуск генератора тактовых импульсов, третий вход блока управления соединен с информационным входом коммутатора, выход которого соединен с шестым выходом блока управления, первый распределитель импульсов соединен вторым выходом с первыми входами третьего, четвертого и восьмого элементов ИЛИ и восьмым выходом блока управления, третьим выходом - с первым входом пятого элемента ШШ и с двенадцатым выходом блока управления, четвертым ;выходом - с первым входом шестого элемента ИЛИ и с двадцать третьим выходом блока управления, пятым выходом - с вторым входом шестого элемента ШШ и с пятнадцатым выходом блока управления, шестым, седьмым, восьмым, девятым, десятым, одиннадцатым, двенадцатым, тринадцатым и .четырнадцатым вьЬсодами - с тринадцатым, четырнадцатым, семнадцатым, восемнадцатым, девятнадцатым, двад- цатым, двадцать первым, двадцать вто

5

0

5

0

5

рым и двадцать четвертым выходами блока управления соответственно, второй распределитель импульсов соединен первым выходом с двадцать пятым выходом блока управления и прямым входом второго элемента ЗАПРЕТ, инверсный вход которого и второй вход пятого элемента ИЛИ подключены к выходу девятого элемента ШШ и являются тридцатым выходом блока управления, вход девятого элемента ИЛИ является шестым входом блока управления, второй и третий выходы второго распределителя импульсов являются двадцать шестым и двадцать седьмым выходами блока управления соответственно, третий распределитель импульсов -соединен вторым выходом с вторыми.входами третьего, четвертого и восьмого элементов ШШ, а третьим выходом - с двадцать девятым выходом блока управления и третьим входом пятого элемента ШШ, выход которого и выходы первого, второго, третьрего, четвертого шестого и восьмого элементов ИЛИ .являются одиннадцатым, четвертин, пятым, девятым, десятым, шестнадцать и двадцать восьмым выходами блока управления соответственно, инверсный вход первого элемента ЗАПРЕТ соединен с четвертым входом блока управления, а выход элемента задержки является седьмым выходом блока управления , вторые входы первого и второго элементов ИЛИ являются пятым входом блока управления.

I I

-

9mtf 3f

tM.fy.1f

ftffJF-a

fa. If amf-t9

ff9M.fy.n

9m tut. 99

Л f7

fnt24-tef9 tMAlt

99

9ux.Sitn OmlJ 79 9wi.iji.i9

Omit urf 9Mc.fy.1t

OtnB-г 77 7fl«p fn IB

7f

- $29ш,аЛ

«7

9ml-99l9 9Mt,ditt9

Sftuxf H 699)1./л19 „, Omia-to litUjr.Sklt

15

.Utf

Onie-totUta Omis-te 9nn-M8tt a OmtS-toHtttr enM. .И ..St.Hta.lt

tt

азвш.

втв-а

.18

юг ff келг,13

| Устройство для контроля параметров | 1981 |

|

SU995068A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР И 1141923, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-07—Публикация

1986-06-03—Подача