1

Изобретение относится к области. автоматики и вычислительной техники и может быть использовано в система программного управления станками.

Известны интерполяторы, работающие по принципу цифровых дифференциальных анализаторов (ОДА), построенные на сдвиговых регистрах, работающие в двоичной системе и содержащие специальные блоки определения старшего разряда регистра подынтегральной функции .

Недостатком этих устройств является то, что реализация их требует значительного оборудования, они не учитывают возможного изменения значению подынтегральных функций (их разрядности) на участке интерполяций, что снижает быстродействие интерполятора из-за необходимости работать с масштабом, рассчитанньм для максимально возможной разрядности.

Наиболее близким техническим решением к данному изобретению является интерполятор для систем программного управления, содержащий блок ввода программы, первый выход которого связан с первым вхо дом блока задания скорости ,второй

вход которого- соединен с выходом первого элемента И, коммутатор и по каждой координате счетчик перемещений, первый регистр, сумматор и последовательно соединенные второй регистр и блок коррекции, выходы первого регистра и блока коррекции соединены с первым и вторым входами сумматора данной координаты соответственно, первый выход сумматора связан со входом первого регистра одноименной координаты, второй выход блока ввода программы подключен к первы- входам счетчиков перемещений и коммутатора, выходы которюго подсоединены к одним из входов блоков коррекции, третий выход блока ввода программы связан со входами вторых регистров, первый выход блока задания скорости связан с третьими входами сумматоров, а входы первого элемента И соединены с выходами счетчиков перемещений 3.

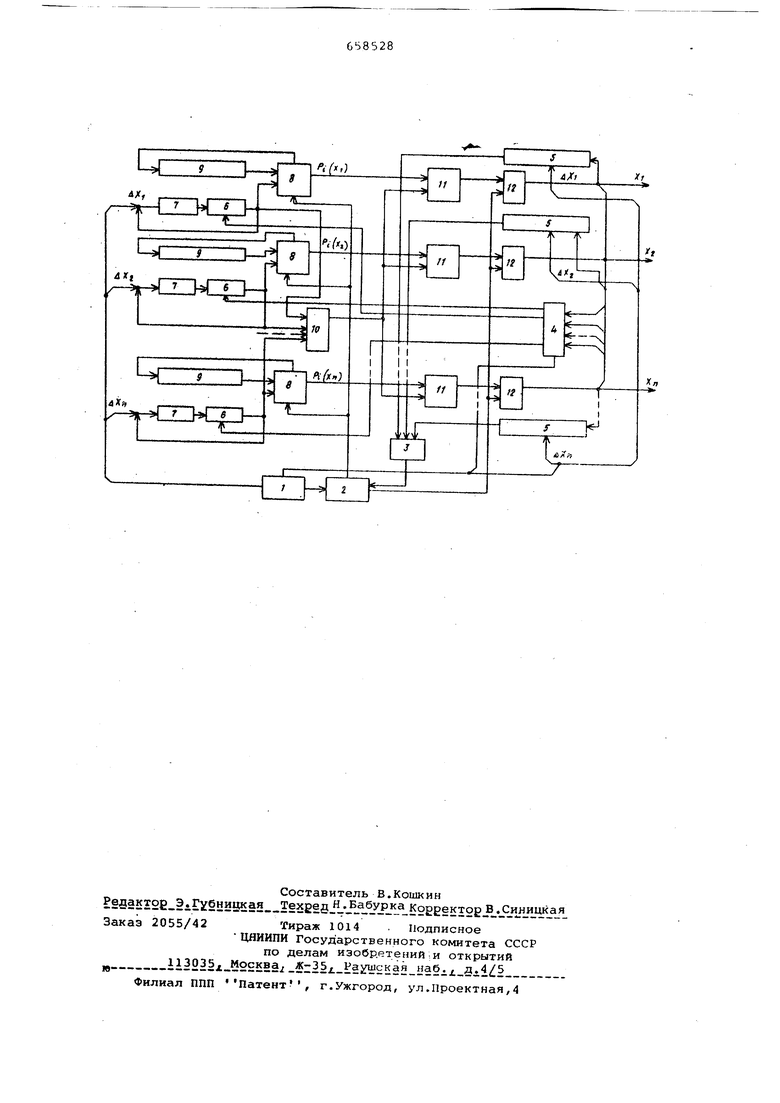

Недостатком этого интерполятора является то, что использование предварительно рассчитанного масштабного коэффициента М усложняет подготовку программ, увеличивает о.бъем вводимой информации, требует значительного дополнительного оборудования и снижает быстродействие, так как в процессе работы интерполятора вводимая в него информация корректируется в широких пределах и, следовательно, величина М должна определяться, исходя из наихудшего случая. Целью предлагаемого изобретения является упрощение интерпблятрра и повышение его быстродействия. Поставленная цель достигается тем что в интерполятор введены элемент ИЛИ и по каждой координате второй элемент И и триггер, единичный вход которого подключен ко второму выходу сумматора данной координаты, нулевые входы триггеров подключены к выходу элемента ИЛИ, входы которого подсоединены ко входам вторых регистров и к выходам блоков коррекции и ко вторым входам сумматоров, единичные выходы триггеров подсоединены к одним из входов вторых элементов И соответствующей координаты, другие входы вторых элементов И подключены ко второму, выходу блока задания ско рости, а выходы - ко вторым входам коммутатора, ко вторым входам счетчиков перемещений и к выходам интер полятора. На чертеже представлена блок-схе интерполятора. Интерполятор содерх и блок ввода программы 1, блок задани скорости .2, первый элемент И 3, ком мутатор 4, счетчики перемещений 5, блоки коррекции б, вторые регистры 7, сумматоры 8, первые регистры 9, элемент ИЛИ 10, триггеры 11 и вторы элементы И 12, Рассмотрим работу интерполятора например, в двух следующих режимах: в режиме линейной интерполяции и в режиме круговой интерполяции В режиме линейной интерполяции вводимая информация перед началом работы распределяется следующим образом. Код скорости с выхода блок 1 записывается в блок 2, а величины перемещений йХ, дХ ... ДХ заносятся в регистры 7 соответствующих 1 оординат и одновременно, з виде дополнительного кода, в счетчики перемещений 5. В коммутатор 4 посту пает, признак линейной интерполяции. По этому признаку коммутатор 4 выраьатывает сигналы, настраивающие блоки б на передачу без коррекции к дов с выходов блоков б коррекции на входы регистров 7, При работе в режиме линейной интерполяции импульса с выхода блока задания скорости 2 поступают на су мматоры 8, осуществляют поразрядное сложение содержимого регистров 7 и 9, при этом полученная сумма -записывается в р гистры 9. Сигналы переноса, возника ющие при суммировании двух любых разрядов слагаемых, устанавливают в 1 триггеры 11, а сигналы 1 следую шнх (старших) разрядов приращений через элемент ИЛИ 10 сбрасывают все триггеры .11 в 0. Таким образом, в одном цикле сум1лирова1шя в состоянии 1 будет находиться только тот из триггеров 11, который установлен в 1 переполнением из старшего разряда, причем этот старший разряд определяется большим из приращений X., ДХд ...ДХ„.Такт блока задания корости 2, следующий за тактом уммирования старшего разряда, потупает на входы всех элементов И 12, открытые единичными выходами триггеров 11, и затем на счетные входы счетчиков 5 и выходы соответствующей координаты интерполятора. При этом, независимо от величины заданных приращений, переполнение, возникающее в старшем разряде любой из координат, будет выделяться и поступать на выход. Так будет продолжаться до тех пор, пока все счетчики 5 не окажутся в нулевом состоянии. Тогда элемент И 3 формирует сигнал окончания отработки кадра, который поступает в блок задания скорости 2 и прерывает выработку тактовых импульсов. В режиме круговой интерполяции вводимая информация распределяется по блокс1М следующим образом, Инфор7 мация о координатах начальной точки дуги окружности X заносится в регистры 7 тех координат, которые определяются нужной плоскостью интерполяции. Так, при интерполяции в плоскости Xj ОХ Хц, заносится в регистр 7 координаты Х , а в регистр 7 координаты Х , Величины приращений, определяер.1ые как разность координат конечной и начальной точки дуги, т.е. как дх х - х, и X , заносятся в виде дополнительного кода в соответствующие счетчики перемещений 5 , что йХ заносится в счетчик 5, соответствую-: щий Координате Хг , адХл - в счетчик 5, соответствующий координате Х, Например, при интерполяции в плоскости заносится в счетчик 5координатьа Х, адХ - в счетчик 5 координаты Х . В коммутатор 4 поступапает с выхода блока 1 признак плоскости и направления интерполяции. При этом коммутатор 4 формирует сигналы, настраивающие один из блоков 6сложения-вычитания на добавление, а другой - на вычитание 1 к содержимому соответствующего регистра 7 в процессе его рециркуляции, что обеспечивает коррекцию подынтегральной функции. Далее работа осуществляется так же, как при линейной интерполяции, и так же происходит выделение переноса из старшего разряда, как и в режиме линейной интерполяции. При этом схема обеспечивает точное выделение переполнения, несмотря на то, что содержимое регистров 7 и их разрядность в процессе отработки дуги окружности непрерывно меняется Оканчивается круговая интерполяция, когда счетчики 5 окажутся в состоянии О. Таким образом, преимуществом данного интерполятора являются его упрощение, возможность произвольного увеличения числа интегратора в интерполяторе без усложнения схемы, расширение класса обрабатываемых траекторий за счет возможности отработки траекторий, теку щие координаты которых во время работы могут изменять разрядность своих знач-ений (например, дуги окру ностей, парабол и т.д.), повышение быстродействия за счет автоматическ го определения старшего значащего разряда всех интеграторов и возможности работать на скорости, соответствующей наибольшей скорости выработки приращений интеграторами. Формула изобретения Интерполятор для систем программ ного управления, содержащий блок ввода программы, первый выход которого связан с первым входом блока задания скорости, второй вход которого соединен с выходом первого элемента И, коммутатор и по каждой координате счетчик перемещений, первый регистр, сумматор и последовательно соединенные второй регистр ;И блок коррекции, выходы первого регистра и блока коррекции соединен с первым и вторым входс1Ми сумматора данной координаты соответственно, первый выход сумматора связан со вх дом первого регистра одноименной координаты, второй выход блока ввода программы подключен ч первым входам счетчиков перемещений и коммутатора, выходы которого подсоединены к одним из входов блоков коррекции, третий ВЫХОД блока ввода программы связан со входами вторых регистров, первый выход блока задания скорости связан с третьими входами сумматоров, а входы первого элемента И соединены,с выходами счетчиков перемещений, отличающий с я тем, что, с целью упрощения и повьлиения быстродействия интерполятора, в него введены элемент ИЛИ и по каждой координате второй элемент И и триггер, единичный вход которого подключен ко второму выходу сумматора данной координаты, нулевые входы триггеров подключены к выходу элемента ИЛИ, входы которого подсоединены ко входам вторых регистров и к выходам блоков коррекции и ко вторым входам сумматоров, единичные выходы триггеров подсоединены к одним из входов вторых элементов И соответствующей координаты, другие входы вторых элементов И подключены ко второму выходу блока задания скорости, а выходы - ко вторым входам коммутатора, ко вторым входам счет|чиков перемещений и т вьйходам интерполятора. Источники информации, принятые ,во внимание при экспертизе 1.Авторское свидетельство СССР 555381, кл. G 05 В ;9/18, 1975. 2.Воронов А.А и др. Цифровые :аналоги, для систем автоматического управления, М., АН СССР, ,1960, ст. 132-139. 3.Дригваль Г.П. Цифровые дифференциальные анализаторы, М., Совет1970, ст.183-215. ское радио

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейно-круговой интерполятор | 1977 |

|

SU741234A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Линейно-круговой интерполятор | 1979 |

|

SU847279A1 |

| Линейно-круговой интерполятор | 1986 |

|

SU1312530A1 |

| Устройство для задания программы | 1979 |

|

SU849148A1 |

| Цифровой интерполятор | 1984 |

|

SU1238033A1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

| Линейно-круговой интерполятор | 1978 |

|

SU807236A1 |

| Линейно-круговой интерполятор | 1987 |

|

SU1462250A2 |

| Линейно-круговой интерполятор | 1978 |

|

SU746431A1 |

Авторы

Даты

1979-04-25—Публикация

1977-03-01—Подача