4

О 00

11

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых рычислительных машинах.

Целью изобретения является повышение точности работы.

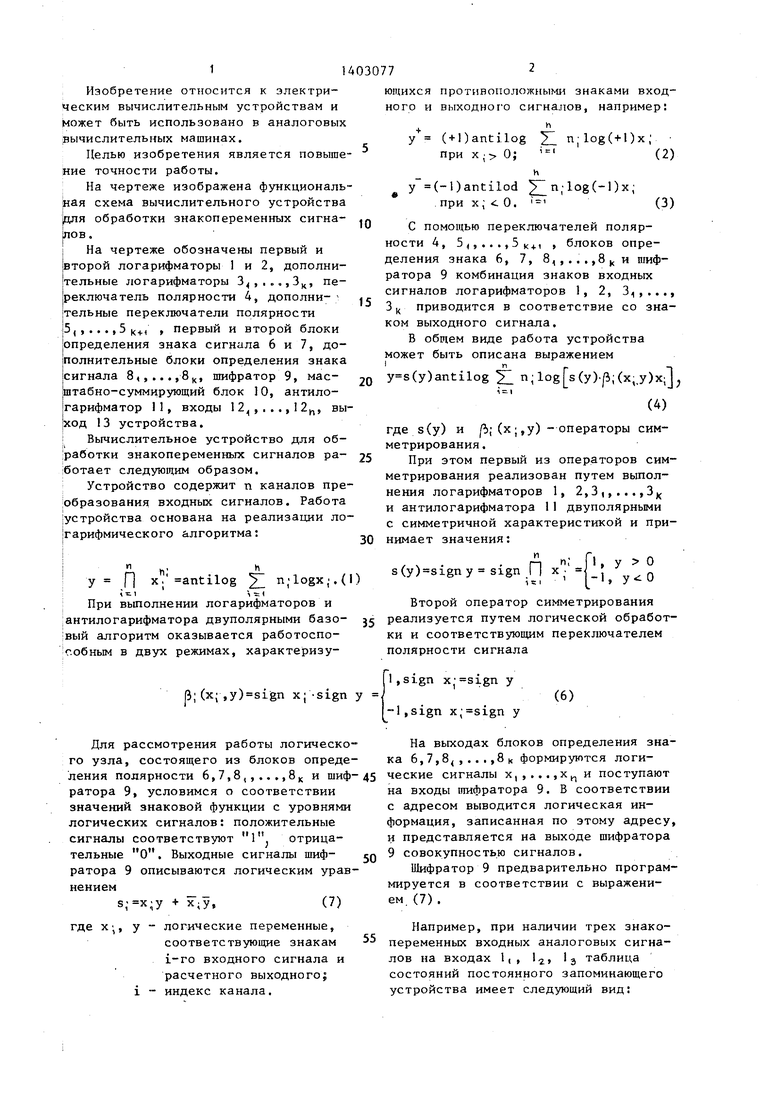

На чертеже изображена функциональ йая схема вычислительного устройства |для обработки знакопеременных сигна- |лов.

i На чертеже обозначены первый и |второй логарифма торы 1 и 2, дополнительные логарифматоры 3,,„.,3, пе- Ьеключатель полярности 4, дополни-; тельные переключатели полярности 5,,...,5к+, , первый и второй блоки Ьпределения знака сигнала 6 и 7, дополнительные блоки определения знака сигнала 8,,...,8, шифратор 9, мае- Штабно-суммирующий блок 10, антило- |гарифматор 11, входы 12,...,12, вы |ход 13 устройства.

; Вычислительное устройство для об- |работки знакопеременных сигналов ра- |ботает следующим образом.

Устройство содержит п каналов пре |образования входных сигналов. Работа |устройства основана на реализации ло |гарифмического алгоритма:

ющихся противоположными знаками входного и выходног о сигналов, например:

+и

у (+I)antilog 21 п;log(+l)x;

при х; 0; (2)

h

у (-l)antilod n;log(-l)x;

при х; :: 0. (3)

С помощью переключателей полярности 4, 5,,..., 5 4.1 блоков определения знака 6, 7, 8,,...,8ц и шифратора 9 комбинация знаков входных сигналов логарифматоров 1, 2, 3,, ..., 3 приводится в соответствие со знаком ВЫХОДГ1ОГО сигнала.

В общем виде работа устройства может быть описана выражением

(y)antilog

l

(4)

где s(y) и Ь; (х;,у) -операторы симметрирования.

При этом первый из операторов симметрирования реализован путем выполнения логарифматоров 1, 2,3,,...,3, и антилогарифматора 11 двуполярными с симметричной характеристикой и принимает значения:

n;log s(y).p;(x,,y)x;

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1985 |

|

SU1282163A1 |

| Логарифмирующий фотометр | 1986 |

|

SU1362947A1 |

| Устройство для возведения в степень | 1977 |

|

SU653619A1 |

| Вычислитель статистических момен-TOB | 1978 |

|

SU807342A1 |

| Широтно-импульсный развертывающий функциональный преобразователь | 1987 |

|

SU1474693A1 |

| Следящий функциональный преобразователь | 1976 |

|

SU634308A1 |

| Вычислительное устройство и запоминающий масштабно-суммирующий блок | 1980 |

|

SU1043670A1 |

| Способ получения цветоделенных изображений и устройство для его осуществления | 1985 |

|

SU1264129A1 |

| Логарифматор | 1986 |

|

SU1427363A1 |

| Логарифмическое вычислительное устройство | 1978 |

|

SU828197A1 |

Изобретение относится к электрическим вычислительным устройствам, вьтолняющим операции умножения, деления и возведения в степень, и может быть использовано в аналоговых вычислительных машинах. Целью изобретения является повьшение точности. Вычислительное устройство для обработки знакопеременных сигналов содержит первый, второй логарифматоры 1 и 2 и дополнительные логарифматоры 3,,..., 3, переключатель полярности сигнала 4и дополнительные переключатели полярности сигнала 5 , . . .5, , первый, второй блоки определения знака сигнала 6, 7 и дополнительные блоки определения знака сигнала 8(,..,,8ц шифратор 9, масштабно-суммирующий блок 10, антилогарифматор 11, входы 12,,...,12 и выход 13. Работа устройства основана на реализации логарифмического алгоритма вычислений, 1 ил. (Л

П

.|,h

antilog 2 n;logx;.(l)

чл : (

При выполнении логарифматоров и ;антилогарифматора двуполярными базо- |вый алгоритм оказывается работоспо- :собным в двух режимах, характеризуП ,si.gn у

3; (х; ,y)sign xj-sign у |(6)

-1,sign у

Для рассмотрения работы логического узла, состоящего из блоков определения полярности 6,7,8,,...,8ц и шифратора 9, условимся о соответствии значений знаковой функции с уровнями

логических сигналов: положительные

I1111

сигналы соответствуют 1 отрицательные О. Выходные сигналы шифратора 9 описываются логическим уравнением

+ х;у,(7)

где х, у - логические переменные, соответствующие знакам i-ro входного сигнала и расчетного выходного| i - индекс канала.

s(y)sign у sign П X

П|

1, у О -1,

Второй оператор симметрирования реализуется путем логической обработки и соответствующим переключателем полярности сигнала

На выходах блоков определения знака 6,7,8,...,8к формируются логические сигналы x,,...,Xj и поступают на входы шифратора 9. В соответствии с адресом выводится логическая информация, записанная по этому адресу, и представляется на выходе шифратора 9 совокупностью сигналов.

1иифратор 9 предварительно программируется в соответствии с выражением. (7).

Например, при наличии трех знакопеременных входных аналоговых сигналов на входах 1,, Ц 1э таблица состояний постоянного запоминающего устройства имеет следующий вид:

с помощью переключателей полярности 4, 5, ,..., 5 , , управляемых шифратором 9, разнополярные комбинации входных сигналов приводятся к однополярным комбинациям: положительным или отрицательным, как это требуется для правильного установления знака выходного сигнала устройства.

Устройство, реализующее логарифмический алгоритм по выражению (1), осуществляет операции умножения, деления, возведения в степень. Тип операции определяется в основном масштабно-суммирующим блоком 10. I Формула изобретения

сигнала, входы которых являются соответственно первым и вторым информационными входами вычислительного устройства, переключатель полярности сиг нала, отличающееся тем, что, с целью повышения точности, в него введены k дополнительных логариф маторов, k дополнительных блоков опре деления знака сигнала, (k+1) дополнительных переключателей полярности и шифратор, причем вход первого блока определения знака сигнала соединен с информационным входом переключателя полярности, вход второго блока опреде ления знака сигнала соединен с информационным входом первого дополнительного переключателя полярности сигнала, входы дополнительных блоков определения знака сигнала являются дополнительными информационными входами вычислительного устройства и соединены с информационными входами дополни- тельных переключателей полярности сиг нала, с второго по (k+l)-й выход переключателя полярности сигнала подклю чены к входу первого логарифматора, выход первого дополнительного переключателя полярности сигнала подключен к входу второго логарифматора, выходы дополнительных переключателей полярности сигнала с второго по (k+l)-й подключены к входам соответствующих дополнительных логарифмато- ров, выходы дополнительных логариф- маторов соединены с соответствующими входами масштабно-суммирующего блока, выходы первого, второго и дополнительных переключателей полярности сигнала подключены к соответствующим входам шифратора, выходы которого соединены с управляющими входами соответственно первого и второго переключателей полярности и соответст40

Вычислительное устройство для обработки знакопеременных сигналов, содержащее первый и второй логарифмато- ры, выходы которых подключены к соответствующим входам масштабно-сумми- 45 вующих дополнительных переключателей рующего блока, выход которого соеди- полярности, причем логарифматоры и иен с входом антилогарифматора, пер- антилргарифматор выполнены двухполяр- вый и второй блоки определения знака ными.

5

10

15

20

03077

сигнала, входы которых являются соответственно первым и вторым информационными входами вычислительного устройства, переключатель полярности сигнала, отличающееся тем, что, с целью повышения точности, в него введены k дополнительных логариф- маторов, k дополнительных блоков определения знака сигнала, (k+1) дополнительных переключателей полярности и шифратор, причем вход первого блока определения знака сигнала соединен с информационным входом переключателя полярности, вход второго блока определения знака сигнала соединен с информационным входом первого дополнительного переключателя полярности сигнала, входы дополнительных блоков определения знака сигнала являются дополнительными информационными входами вычислительного устройства и соединены с информационными входами дополни- тельных переключателей полярности сигнала, с второго по (k+l)-й выход переключателя полярности сигнала подключены к входу первого логарифматора, выход первого дополнительного переключателя полярности сигнала подключен к входу второго логарифматора, выходы дополнительных переключателей полярности сигнала с второго по (k+l)-й подключены к входам соответствующих дополнительных логарифмато- ров, выходы дополнительных логариф- маторов соединены с соответствующими входами масштабно-суммирующего блока, выходы первого, второго и дополнительных переключателей полярности сигнала подключены к соответствующим входам шифратора, выходы которого соединены с управляющими входами соответственно первого и второго переключателей полярности и соответст25

30

35

40

-45 вующих дополнительных переключателей полярности, причем логарифматоры и антилргарифматор выполнены двухполяр- ными.

| Патент США № 3940603, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Бонч-Бруевич A.M | |||

| и др | |||

| Бесконтактные элементы самонастраивающихся систем | |||

| М.: Машиностроение, 1968, CJ36-137, рис.75 | |||

| . | |||

Авторы

Даты

1988-06-15—Публикация

1986-06-17—Подача