Изобретение относится к вычисли-- тельной технике и может использоваться в цифровых вьиислительнык машинах для преобразования вещественных пятиразрядных чисел в технические целочисленные логарифмы.

Цель изобретения - сокращение аппаратных затрат при обработке пятиразрядных чисел.

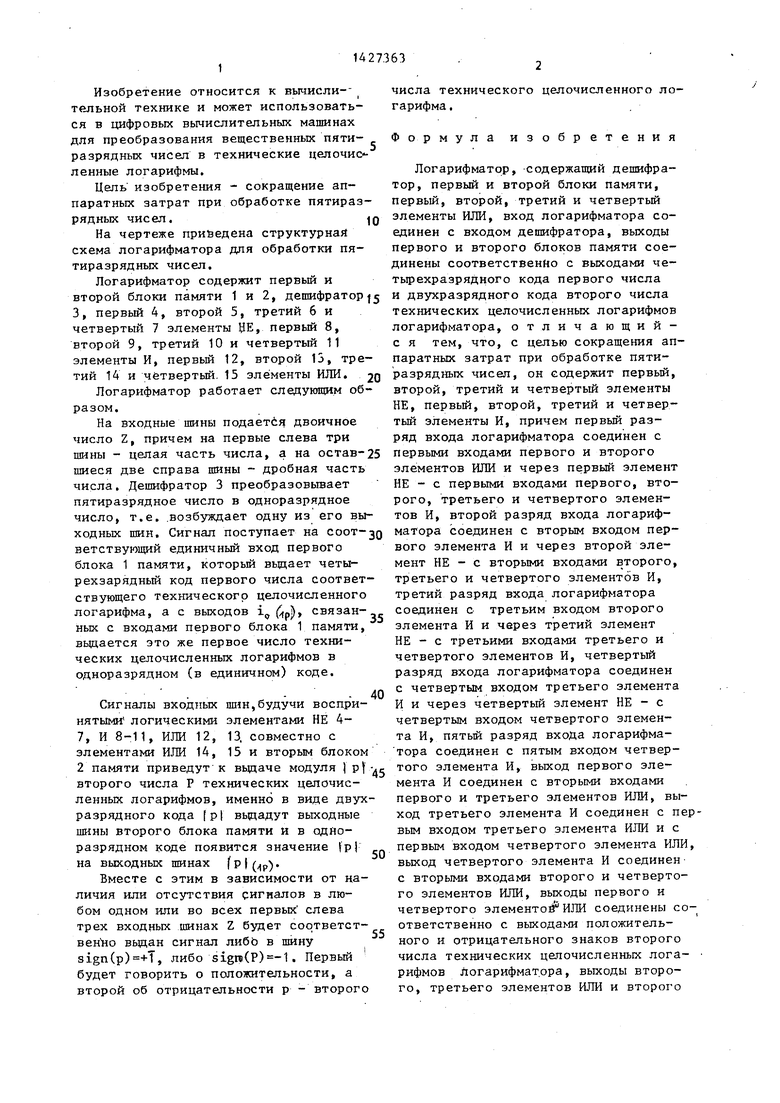

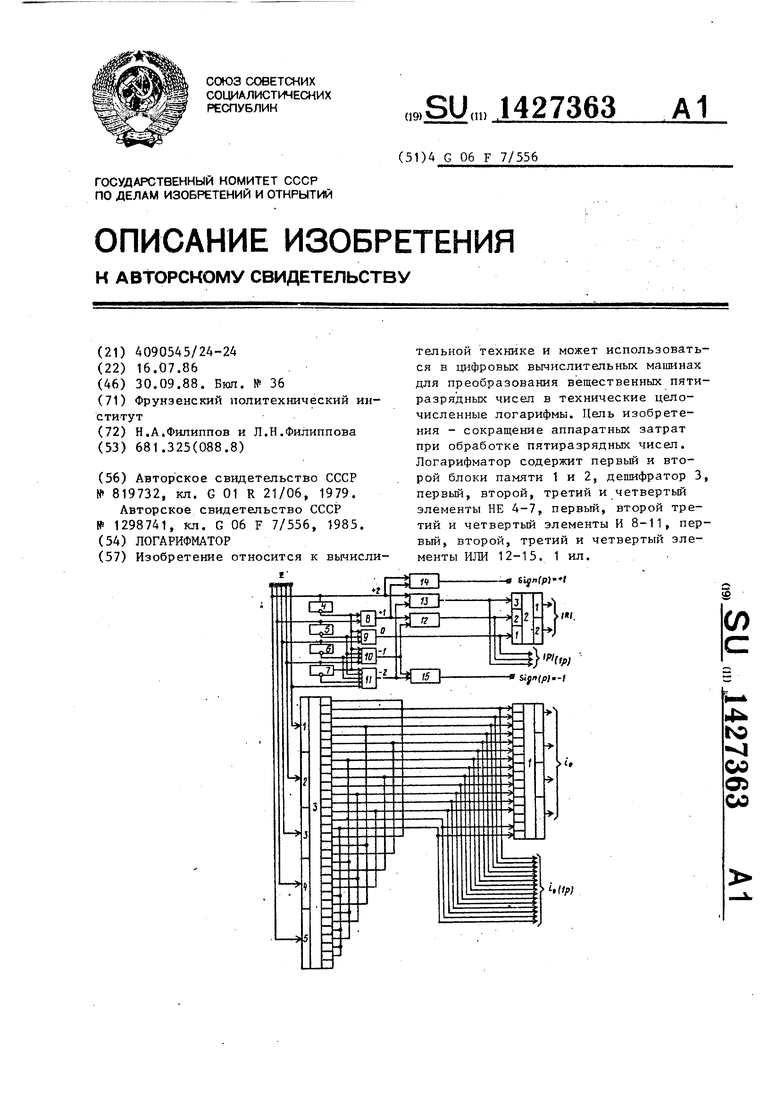

На чертеже приведена структурная схема логарифматора для обработки пятиразрядных чисел.

Логарифматор содержит первый и второй блоки памяти 1 и 2, дешифратор 3, первый 4, второй 5, третий 6 и четвертый 7 элементы ЦЕ, первый 8, второй 9, третий 10 и четвертый 11 элементы И, первьм 12, второй 13, третий 14 и четвертый. 15 элементы ИЛИ.

Логарифматор работает следующим образом.

На входные шины подается двоичное число Z, причем на первые слева три шины - делая часть числа, а на оставшиеся две справа шины - дробная часть числа. Дешифратор 3 преобразовывает пятиразрядное число в одноразрядное число, т.е. .возбуждает одну из его выходных шин. Сигнал поступает на COOTветствующий единичный вход первого блока 1 памяти, который вьщает четы- рехзарядньй код первого числа соответствующего технического целочисленного логарифма, а с выходов i, (ipi), связанных с входами первого блока 1 памяти, вьдается это же первое число технических целочисленных логарифмов в одноразрядном (в единичном) коде.

.--

Сигналы входных Ш1Н,будучи воспринятыми логическими элементами НЕ 4- 7, И 8-11, ИЛИ 12, 13. совместно с элементами ИЛИ 14, 15 и вторым блоком 2 памяти приведут к вьщаче модуля 1 Р второго числа Р технических целочисленных логарифмов, именно в виде двухразрядного кода р| вьщадут выходные шины второго блока памяти и в одноразрядном коде появится значение р на выходных щинах (Р|(/|р)

Вместе с этим в зависимости от наличия или отсутствия сигналов в любом одном или во всех первых слева трех входных шинах Z будет соответст- вен но вьздан сигнал либЬ в шину sign(p)+T, либо signi(P)-1. Первый будет говорить о положительности, а второй об отрицательности р - второго

0

Q

0

5

0

числа технического целочисленного логарифма .

Формула изобретения

Логарифматор, содержащий дешифратор, первый и второй блоки памяти, первьй, второй, третий и четвертый элементы ИЛИ, вход логарифматора соединен с входом дешифратора, выходы первого и второго блоков памяти соединены соответственно с выходами че- тьфехразрядного кода первого числа и двухразрядного кода второго числа технических целочисленных логарифмов логарифматора, отличающий- с я тем, что, с целью сокращения аппаратных затрат при обработке пятиразрядных чисел, он содержит первьй, второй, третий и четвертый элементы НЕ, первый, второй, третий и четвертый элементы И, причем первый разряд входа логарифматора соединен с первыми входами первого и второго элементов ИЛИ и через первый элемент НЕ - с первыми входами первого, второго, третьего и четвертого элементов И, второй разряд входа логарифматора соединен с вторым входом первого элемента И и через второй элемент НЕ - с вторыми входами второго, третьего и четвертого элементов И, третий разряд входа логарифматора соединен с третьим входом второго элемента И и через третий элемент НЕ - с третьими входами третьего и четвертого элементов И, четвертый разряд входа логарифматора соединен с четвертым входом третьего элемента И и через четвертый элемент НЕ - с четвертым входом четвертого элемента И, пятьй разряд входа логарифма- тора соединен с пятым входом четвертого элемента И, выход первого элемента И соединен с вторыми входами первого и третьего элементов ИЛИ, выход третьего элемента И соединен с первым входом третьего элемента ИЛИ и с первым входом четвертого элемента ИЛИ, выход четвертого элемента И соединен с вторыми входами второго и четвертого элементов ИЛИ, выходы первого и четвертого элементойР ИЛИ соединены со- ответственно с выходами положительного и отрицательного знаков второго числа технических целочисленных лога- рифмов логарифматора, выходы второго, третьего элементов ИЛИ и второго

О

элемента И соединены соответственно с первым, вторым и третьим входами второго блока памяти и первым, вторым и третьим разрядными, выходами одноразрядного кода второго числа техничес- ких целочисленных логарифмов логариф- матора, первый, второй, четвертый, - BocbMo/i и шестнадцатый выходы дешифратора соединены с первым входом пер- вого блока, памяти, второй вход которого соединен с семнадцатым выходом дешифратора, третий, шестой, двенадцаты и двадцать четвертый, выходы которого соединены с девятым входом первого блока памяти, третий вход которого соединен с девятым и восемнадцатым выходами дешифратора, пятый, десятый и двадцатый выходы которого соединены с пятым входом первого, блока памя- ти, четвертый вход которого соединен с девятнадцатым выходом дешифратора, седьмой, четырнадцатый и двадцать восьмой выходы которого соединены с тринадцатым входом первого блока па-

мяти, шестой вход которого соединен с двадцать первым выходом дешифратора, одиннадцатый и двадцать второй выходы которого соединены с седьмым входом первого блока, памяти, восьмой вход которого соединен с двадцать третьим выходом дешифратора, тринадцатый и двадцать шестой выходы которого соединены с одиннадцатым входом первого блока памяти, десятый вход которого соединен с двадцать пятым выходом дешифратора, пятнадцатый, тридцатый и тридцать первый выходы которого соединены ,р пятнадцатым входом первого блока памяти, двенадцатый вход которого соединен с двадцать седьмым выходом дешифратора, двадцать девятый выход которого соединен с четырнадцатым входом первого блока памяти, с шестнадцатого по тридцатый вькоды дешифратора соединены соответственно с первого по пятнадцатый выходами первого числа одноразрядного кода технических целочисленных логарифмов логарифматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ СОВМЕСТНО ХРАНИМЫХ ГРАНИЦ ПРИ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЯХ | 2012 |

|

RU2497179C1 |

| Устройство для логарифмирования | 1980 |

|

SU959072A1 |

| Логарифматор | 1985 |

|

SU1298741A1 |

| Устройство автоматизированного контроля электронных систем | 1982 |

|

SU1061075A2 |

| Устройство для вычисления функций | 1985 |

|

SU1287150A1 |

| УСТРОЙСТВО СОВМЕСТНОГО КОДИРОВАНИЯ ГРАНИЦ ПРИ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЯХ | 2012 |

|

RU2497180C1 |

| Устройство для логарифмирования и потенцирования | 1978 |

|

SU711561A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Устройство для логарифмирования | 1982 |

|

SU1030800A1 |

| ШИФРАТОР | 1988 |

|

SU1605892A1 |

Изобретение относится к вычислиЁ тельной технике и может использоваться в цифровых вычислительных машинах для преобразования в ещественных пятиразрядных чисел в технические целочисленные логарифмы. Цель изобретения - сокращение аппаратных затрат при обработке пятиразрядных чисел. Логарифматор содержит первый и второй блоки памяти 1 и 2, дешифратор 3, первый, второй, третий и четвертый элементы НЕ 4-7, первьм, второй третий и четвертый элементы И 8-11, первый, второй, третий и четвертый элементы ИЛИ 12-15. 1 ил. в Sijnfp}- / s (Л i)fW 4s to САЭ О) CO

| Цифровой ваттметр | 1978 |

|

SU819732A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Логарифматор | 1985 |

|

SU1298741A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-30—Публикация

1986-07-16—Подача