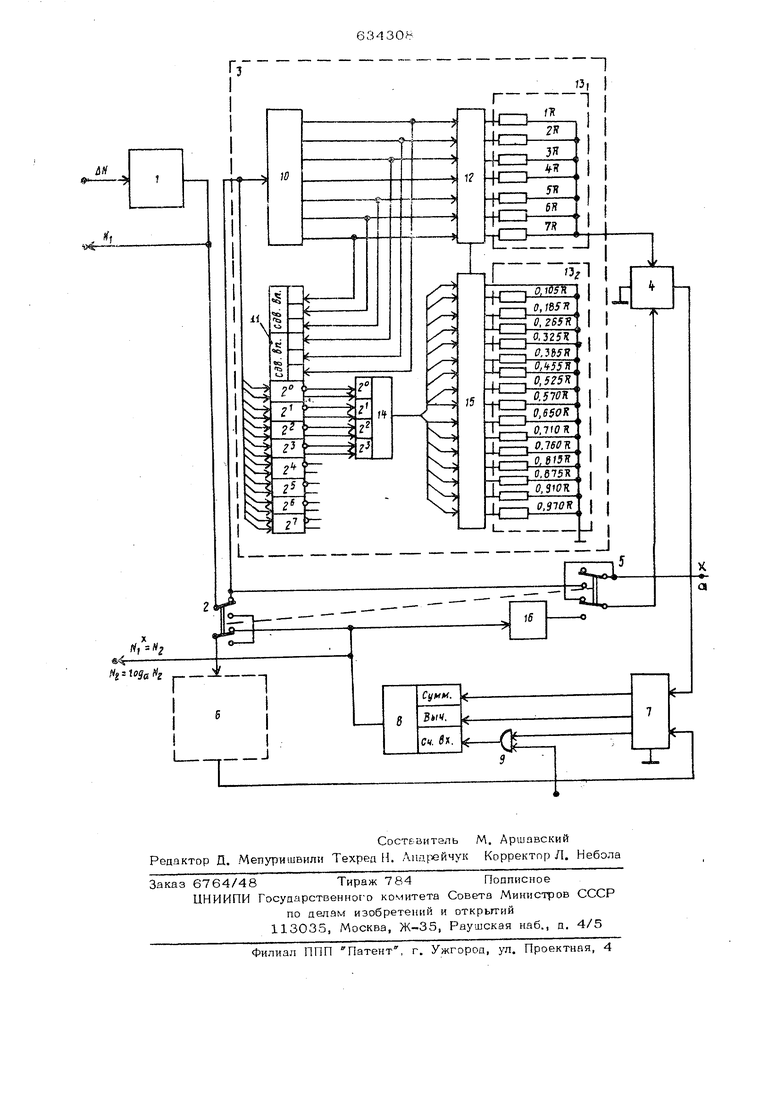

Предлагаемое устройство относится к области вычислительных машин и может быть использовано аля обработки цифровой измерительной информации. Известно устройство для вычисления степенной функции ij , содержащее группу сдвиговых регистров, группу cy маторов, коммутатор, выходной регистр и блок управления. Недостатком устройства является его большая сложность. Наиболее близким по конструкции и вь полняемьтм функциям является устройст во 2 , содержащее первый и второй реверсивные счетчики, первый и второй логарифматоры, шину показателя степени, множительный блок, первый вход которого соединен с выходом первого логарифматора,элемент И и блок сравнения, первы вход которого соединен с выходом множительного блока, второй вход соединен с выходом второго логарифматора, первы и второй выходы блока сравнения соедине ны с входами суммирования и вычитания второго реверсивного счетчика соответственно, а третий выход через элемент И соединен со счетным входом второго реверсивного счетчика. Недостатком известного устройства является относительная узость функцио шль- ных возможностей, заключающаяся в невозможности вычислений логарифмической функции. Целью изобретения является расширение функциональных возможностей за счет вычисления логарифмических функций. Указанная цель достигается тем, что устройство содержит цифроаналоговый преобразователь и первый и второй переключатели, причем выход второго реверсивного счетчика соединен со входом цифроаналогового преобразователя и через первый переключатель - со входом второго логарифматора, выход первого реверсивного счетчика через первый переключатель соединен со входом первого логарифматора и через второй переключа- 3634 тель к шине показателя степени, выход цифроаналогового преобразователя через второй переключатель соединен со вторым входом множительного блока, который через второй переключатель соединен с шиной показателя степени. На чертеже приведена блок-схема преобразователя. Вход первого реверсивного счетчика 1, осуществляющего суммирова- ние или вычитание импульсов в зависимое ти от знака вводимой переменной величины, Соединен с входом преобразователя, через который вводится переменная величина t Д К , представляющая собой последовательность счетных импульсов. Выход первого реверсивного счетчика 1 соединен с выходом преобразователя контролирующим суммарное показание сче ;Чика в течение всего времени преобразования, и через переключатель 2 с входом первого логарифматора 3. Вьтсод первого логарифматора 3 соединен с входом множительного блока 4, второй вход которого соединен через второй переключатель 5 с шиной показателя степени x(oi)| через которую вводится значение переменных X - показателя функпии Ч N, или а - основание логарифма при вььчислении функции у N , , или у -шб Н1 соответственно. В первом Случае множительным блоком выполняется операция X1о i ° втором EodgOiNn,. Выходы множительного блока 4 и второго логарифматора 6 соединены с входами блока сравнения 7, три выхода . которого соединень с входами второго реверсивного счетчика 8 суммирование, вычитание и через элемент И 9 со счетным входом. Блок сравнения 7 предназначен для включений второго реверсивного счетчика 8 в режимы:

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий преобразователь функций вида у= | 1972 |

|

SU481918A1 |

| Цифровой логарифматор | 1975 |

|

SU603996A1 |

| Логарифмирующее устройство | 1972 |

|

SU482768A1 |

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

| Цифровой коррелятор | 1980 |

|

SU894719A1 |

| Логарифмирующее устройство | 1979 |

|

SU858011A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для вычисления параметров экспоненциальных функций | 1980 |

|

SU911524A1 |

| Преобразователь комплексных сигналов | 1983 |

|

SU1104525A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

Выход второго реверсивного счетчика 8 соединен через переключатель 2 со вхо дом второго логарифматора бис выходом преобразователя, с которого считываются результаты вычислений: у «Ы , Логарифматоры 3, 6 прецназначены для представления в аналоговой форме соот ветственно значений Eotf 2. 1 ЯЁ 2 2 при работе преобразователя в режиме вычисления Ч N. и для представления в аналоговой форме соответственно значений обоО и Eo6,V , при работе преобразова & & 1g теля в р ежиме вычисления у в cog д, N . Логарифматоры 3, 6 имеют одинаковые пЬстроения и выполнены следующим образом, С входом логарифматора соединены входы блока 10 выделения старшего значащего разряда и информационные входы сдвигающего регистра 11, Каждый из выходов блока 1О выделения старшего значащего разряда соединен с одним из управляющих входов коммутатора 12, предназначенного для подключения одного из сопротивлений R , резистор ной матрицы 13 к части резисторнойматри цы 13 дробных значений 0,105 0,185 i 0,265 R; 0,325 0,385 R; 0,455 0,525 R; O,570 R; 0,650 R;O,71O Rj 0,760 R| 0,815 R; 0,875 R; 0,910 R| O,970 R. Выходы блока lO выделения старшего значащего разряда соединены также с управляющими входами сдвигающего регистра 11, таким образом, что при коде числа N, со старшим зна-.. чащим разрядом 2 , 2 или 2 производится сдвиг кодачисла W на 3,2 или 1 разряд вправо (умножение) соорветственно, а для числа I i со старшим значащим разрядом 2 , 2 или 2 - на 1, 2 или 3 разряда влево (деление) со- . ответственно. Выходы 2 , 2 , 2 , 2 Сдвигающего регистра 11 соединены со входами 2° , 2 , 2 , 2 дешифратора 14, а выходы последнего с управляющими входами коммутатора 15, ключи которого стоят в цепях- сопротивлений дробной части матрицы 13 . Один коммутирующий выход каждого ключа соединен с соотвврствующим сопротивлением, а вторые вььходы ключей целой и дробной матрицы соединены, между собой. Общая точка схемы, объединяющая вторые выводы сопротивлений кратных R , является выходом логарифматоров 3 и 6, а обшая точка, объединяющая вторые выводы сопротивлений меньших R , соединена с корпусом. 56 При работе преобразователя в режим вычисления функции у 8о4 g N шина Х(с«) преобразователя через второй пер ключатель 5 соединяется с входом пер вого логарифматора, а вход множительно блока 4 соединяется с выходом цифроаналогового преобразователя 16, вход к торого постоянно соединен с выходом второго реверсивного счетчика . Алгоритм вычисления логарифмов чисел заключается в следующем. Показатель степени старшего значащего разряда численно равен характерис eog.N Располагая значениями мантисс логарифмов всех чисел в интервале (в данном логарифматоре для удобства понимания взят конкретный пример - используются предварительно вычисленные с определенной точностью значения мантисс чисел в интервале , ) с помощью логарифматора можно с той же точностью вычислить все числа, мень ше 2 , Таким образом, для вычисления мантисс логарифмов чисел меньших 2 необходимо умножать эти числа на 24-т (где m - старший зн чащий разряд числа N ), после чего значение мантиссы вновь полученного числа беретс из известного массива логарифмов чисел в интервале 2 +2 , что аналогично сдвигу кода числа Н вправо на}т-к разрядов. Аналогично для вычисления мантисс логарифмов чисел ( N 2) необходимо умножить эти числа на2 ( )после чего значение мантиссы вно полученного числа берется из известного массива логарифмов чисел в интервале 2 (24 -2 5 ), что аналогично сдвигу кода числа N влево на |гП-к| разрядов. Исходная информация в логарифматоре представлена в виде номиналов сопротивлений R , 2R , ,,. , 71 (для вьн числения характеристики) и номиналов сопротивлений R «i 1, численные значени которых соответствуют мантиссам логарифмов чисел в интервале 2 . Выбор необходимого значения характерис тик логарифма двоичного числа К производится через коммутатор 12, управляемый блоком 10 выделения старшего значащего разряда, а выбор значения мантиссы осуществляется через коммутатор 15, управляемый с выходов дешиф тора 14, количество выходов которого равно количеству номиналов дробных значений 1 Преобразователь в режиме вычисления У W работает следующим образом. Предположим на входах преобразователя (входы первого реверсивного счет чика 1 и множительного блока 4) присутствуют переменные величины AWj.X и в первом реверсивном счетчике 1 сформировано число NJ , например, Nj .0.,,2S40,,,22.1,24i,20rlOS, введенное в первый логарифматор 3 в блок 10 выделения старшего значащего разряда и сдвигающий регистр 11, Блок выделения старшего значащего разряда выделит из кода числа N г разряд 2 , в результате чего на соответствующем его выходе появится управляющий сигнал, с помощью Которого через коммутатор 12 к коммутатору 15 будет подключено сопротивление 6 R . Одновременно этим же сигналом будет произведен сдвиг кода числа W , в регистре li на |гт1-и| (то есть на ) разряда влево и с выхода дешифратора 14 через коммутатор 15 последовательно к сопротивлению 61 будет подключено сопротивление 0,65О R, Суммарное сопротивление 6,650R или эквивалентные ему величины тока или напряжения в множительном блоке 4 умножаются на аналоговую величину X и результат, подается на один вход блока сравнения 7, на второй вход которого с выхода второго логарифмато- ра 6 поступает сигнал, пропорциональный оЙ2.2 где значение выходного кода второго реверсивного счетчика 6. При К og 2 выхода блока сравнения 7 на второй реверсивный счетчик 8 поступает сигнал, переключающий в режим суммирования. В этом случае происходит заполнение второго реверсивного счетчика 8 импульсами через элемент К 9 и преобразование получаемого числа во втором логарифматоре 6 в его логарифм до тех пор, пока не наступит равенство X to 2 i а 2 г что означает N| В результате чего элемент И 9 закрывается, препятствуя поступлению счетных импульсов, Анало- Г гчная операция производится прихЕоб Н о6 2, 2 лишь разницей, что второй реверсивный счетчик 6 работает в режиме вычитания, Для работы в режиме вычисления y-EogcjN переключатели 2, 5 переводятся в положения, соединяющие выход пер63BoTD реверсивного счетчика 1 с входом второго логарифматора 6, шина х(а) преобразователя, через которую подается значение величины d соединяется с вхо дом первого логарифматора 3, вьтход циф роаналогового преобразователя 16 соединяется со вторым входом множительного блока 4. В этом случае в первом погарифматоре 3 вычисляется значение величины Коб 2 01 . которое подается на один вход множительного блока 4, во втором реверсивном счетчике 8 формируется число М 2 , аналоговый эквивален которого подается с выхода цифроанало- гового преобразователя 16 на второй вход множительного блоко 4, вычисленно подается значение величины на один вход блока сравнения 7, на втор вход которого с выхода второго логарифматора 6 подается значение величины &otf 2. 1 достижении равенства - N t элемент И 9 закрывае ся и число Х , накопленное к этому времени во котором реверсивном счетчике 8, является результатом вычислений и считывается с выхода преобразователя, так как прообразуя равенствоН, Ni можно получить Работа логарифматоров в обоих режимах аналогична. Таким образом, дополнительное введение в преобразователь цифроаналогового преобразователя и двух переключателей, коммутирующих соответствующим образом связи между блоками, позволяет вычислят как показательную, так и логарифмическую функции. 8 Формула изобретения Следящий функциональный преобразователь, содержащий первый и второй реверсивные счетчики, первый и второй логарифматоры, шину показателя степени, множительный блок, первый вход которого соединен с выходом первого логарифматора, элемент И и блок сравнения, первый вход которого соединен с выходом множительного блока, второй вход соединен с выходом второго логарифматора, первый и второй выходы блока сравнения соединены с входами суммирования и вьгчита- ния второго реверсивного счетчика соответственно, а третий выход через элемент И соединен со счетным входом второго реверсивного счетчика, отличающийся тем, что, с целью расширения функциональных возможностей за счет вычисления логарифмических функций, он содержит цифроаналоговый преобразователь и первый и второй переключатели, причем выход второго реверсивного счетчика соединен со входом цифроаналогового преобразователя и через первый переключатель - со входом второго логарифматора, выход первого реверсивного счетчика через первый переключатель соединен со входом первого логарифматора и через второй переключатель к шине показателя степени, выход цифроаналогового преобразователя через второй переключатель соединен со вторым входом множительного блока, который через второй переключатель соединен с шиной показателя степени. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР № 491946, кл. q 06 F 7/38, 1973. 2.Авторское свидетельство СССР № 481918, кл. Q Об J З/ОО, 25J08.74.

Авторы

Даты

1978-11-25—Публикация

1976-11-01—Подача