о

00

о UD

Од

Изобретение относится к полупро- . водниковой технике и технике накопления информации и может быть использовано в Устройствах вычислительной техники, автоматики и электроники.

Целью изобретения является повышение информационной емкости накопителя.

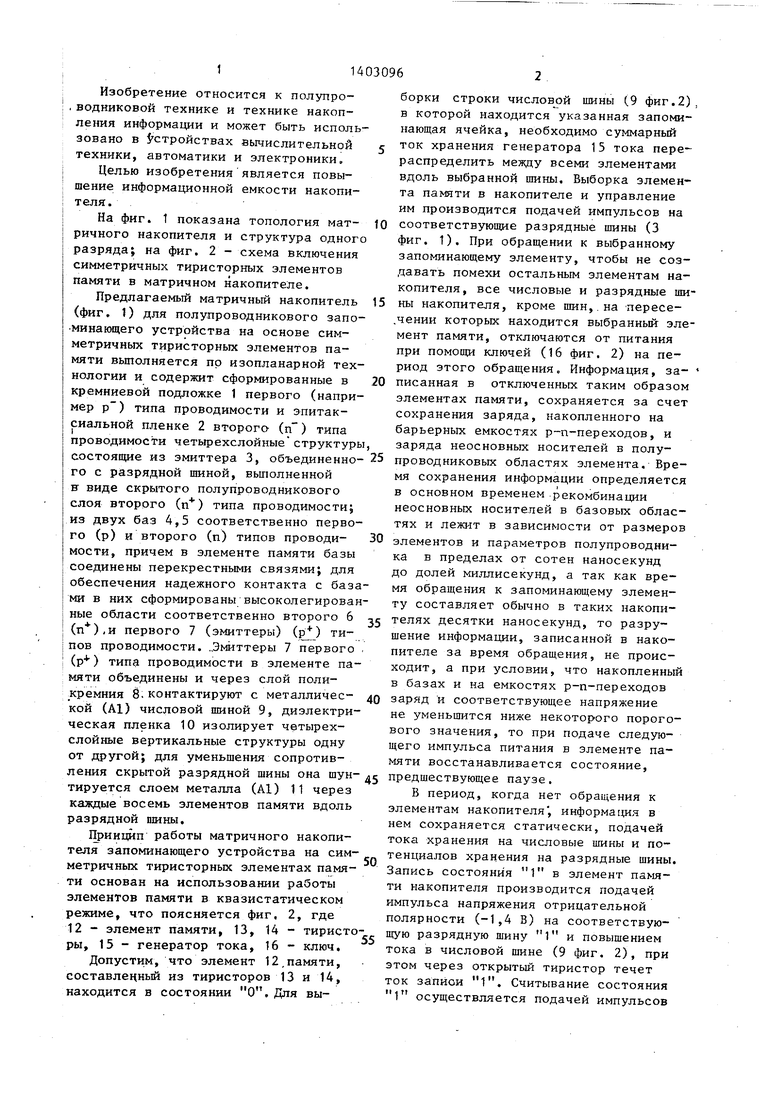

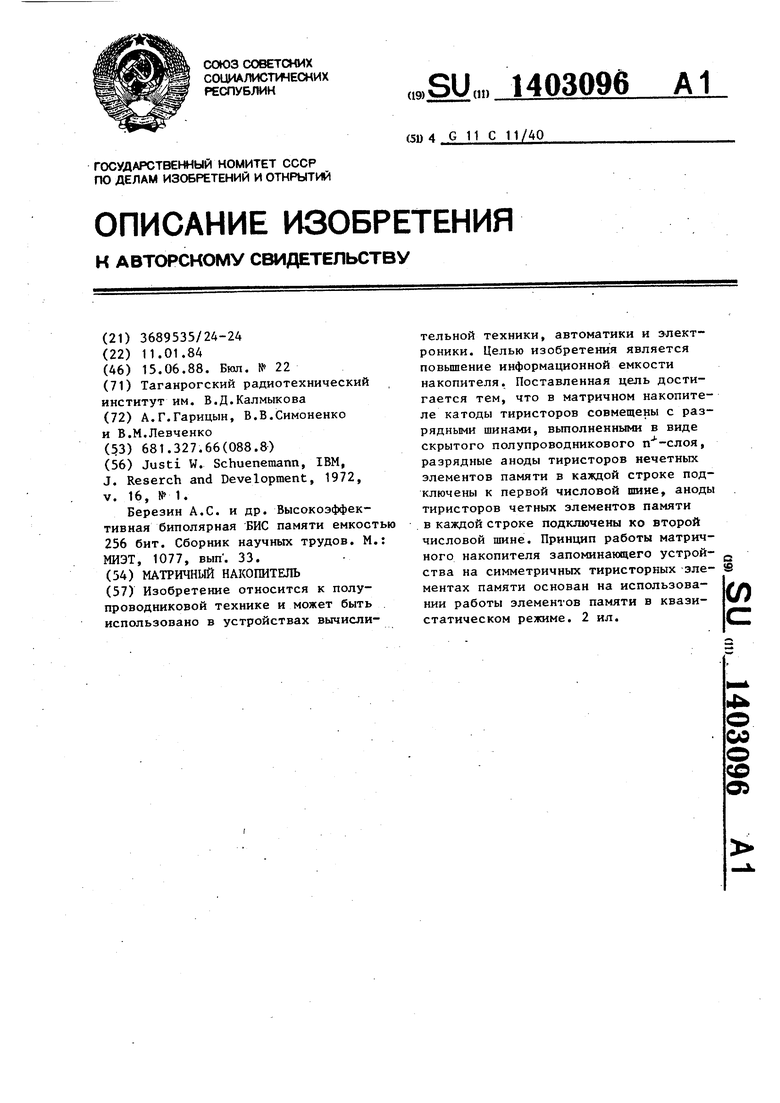

На фиг. 1 показана топология матричного накопителя и структура одного разряда; на фиг. 2 - схема включения симметричных тиристорных элементов памяти в матричном накопителе.

Предлагаемый матричный накопитель (фиг, 1) для полупроводникового запо- минающего устройства на основе симметричных тиристорных элементов памяти вьшолняется по изопланарной технологии и содержит сформированные в кремниевой подложке 1 первого (например р) типа проводимости и эпитак- сиальной пленке 2 второго (п) типа проводимости четырехслойные структуры,

борки строки числовой шины (9 фиг.2), в которой находится указанная запоминающая ячейка, необходимо суммарный

е ТОК хранения генератора 15 тока перераспределить между всеми элементами вдоль выбранной шины. Выборка элемента памяти в накопителе и управление им производится подачей импульсов на

to соответствующие разрядные шины (3 фиг. 1), При обращении к выбранному запоминающему элементу, чтобы не создавать помехи остальным элементам накопителя, все числовые и разрядные ши15 ны накопителя, кроме шин,, на переселении которых находится выбранный элемент памяти, отключаются от питания при помощи ключей (16 фиг, 2) на период этого обращения. Информация, за-

20 писанная в отключенных таким образом элементах памяти, сохраняется за счет сохранения заряда, накопленного на барьерных емкостях р-п-переходов, и заряда неосновных носителей в полусостоящие из эмиттера 3, объединенно- 25 проводниковых областях элемента. Вреборки строки числовой шины (9 фиг.2), в которой находится указанная запоминающая ячейка, необходимо суммарный

ТОК хранения генератора 15 тока перераспределить между всеми элементами вдоль выбранной шины. Выборка элемента памяти в накопителе и управление им производится подачей импульсов на

соответствующие разрядные шины (3 фиг. 1), При обращении к выбранному запоминающему элементу, чтобы не создавать помехи остальным элементам накопителя, все числовые и разрядные шины накопителя, кроме шин,, на переселении которых находится выбранный элемент памяти, отключаются от питания при помощи ключей (16 фиг, 2) на период этого обращения. Информация, за-

писанная в отключенных таким образом элементах памяти, сохраняется за счет сохранения заряда, накопленного на барьерных емкостях р-п-переходов, и заряда неосновных носителей в полу

| название | год | авторы | номер документа |

|---|---|---|---|

| МАТРИЧНЫЙ НАКОПИТЕЛЬ | 1986 |

|

RU1398666C |

| Запоминающее устройство | 1974 |

|

SU658600A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

| ЭЛЕМЕНТ ПАМЯТИ | 1992 |

|

RU2032944C1 |

| ЯЧЕЙКА ПАМЯТИ | 1976 |

|

SU611581A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ | 1972 |

|

SU434481A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО И СПОСОБ УПРАВЛЕНИЯ ИМ | 1979 |

|

RU1110315C |

| Оперативное запоминающее устройство | 1982 |

|

SU1111204A1 |

| Матричный накопитель | 1979 |

|

SU799007A1 |

| Матричный накопитель | 1986 |

|

SU1343443A1 |

Изобретение относится к полупроводниковой технике и может быть использовано в устройствах вычислительной техники, автоматики и электроники. Целью изобретения является повышение информационной емкости накопителя. Поставленная цель достигается тем, что в матричном накопителе катоды тиристоров совмещены с разрядными шинами, вьтолненными в виде скрытого полупроводникового n -слоя, разрядные аноды тиристоров нечетньт элементов памяти в каждой строке подключены к первой числовой шине, аноды тиристоров четных элементов памяти в каждой строке подключены ко второй числовой шине. Принцип работы матричного накопителя запоминающего устрой- ства на симметричных тиристорных эле- S ментах памяти основан на использовании работы элементов памяти в квазистатическом режиме. 2 ил. W

го с разрядной шиной, выполненной ВТ виде скрытого полупроводникового слоя второго (п) типа проводимости; из двух баз 4,5 соответственно первого (р) и второго (п) типов проводи- мости, причем в элементе памяти базы соединены перекрестными связями; для обеспечения надежного контакта с базами в них сформированы высоколегированные области соответственно второго 6 (п),и первого 7 (эмиттеры) (Р) типов проводимости. „Эмиттеры 7 первого () типа проводимости в элементе памяти объединены и через слой поликремния 8. контактируют с металличес- кой (А1) числовой шиной 9, диэлектрическая пленка 10 изолирует четырехслойные вертикальные структуры одну от другой; для уменьшения сопротив

ления скрьпгой разрядной шины она шун-д предшествующее паузе.

тируется слоем металла (А1) 11 через каждые восемь элементов памяти вдоль разрядной пшны.

Принцип работы матричного накопителя запоминающего устройства на симметричных тиристорных элементах памяти основан на использовании работы элементов памяти в квазистатическом режиме, что поясняется фиг, 2, где 12 - элемент памяти, 13, 14 - тиристо50

55

В период, когда нет элементам накопителя , нем сохраняется статич тока хранения на число тенциалов хранения на Запись состояния 1 в ти накопителя производ импульса напряжения от полярности (-1,4 В) на щую разрядную шину 1 тока в числовой шине ( этом через открытый ти ток записи 1. Считыв 1 осуществляется под

ры, 15 - генератор тока, 16 - ключ, Допустим, что элемент 12,памяти, составленный из тиристоров 13 и 14, находится в состоянии О. Для вы00

5

мя сохранения информации определяется в основном временем рекомбинации неосновных носителей в базовых областях и лежит в зависимости от размеров элементов и параметров полупроводника в пределах от сотен наносекунд до долей миллисекунд, а так как время обращения к запоминающему элементу составляет обычно в таких накопителях десятки наносекунд, то разрушение информации, записанной в накопителе за время обращения, не происходит, а при условии, что накопленный в базах и на емкостях р-п-переходов заряд и соответствующее напряжение не уменьшится ниже некоторого порогового значения, то при подаче следующего импульса питания в элементе памяти восстанавливается состояние.

0

5

В период, когда нет обращения к элементам накопителя , информа1щя в нем сохраняется статически, подачей тока хранения на числовые шины и потенциалов хранения на разрядные шины. Запись состояния 1 в элемент памяти накопителя производится подачей импульса напряжения отрицательной полярности (-1,4 В) на соответствующую разрядную шину 1 и повышением тока в числовой шине (9 фиг. 2), при этом через открытый тиристор течет ток записи 1. Считывание состояния 1 осуществляется подачей импульсов

УЖ /////////////////Л

X

/ 2

5

7Г

1 89 10 И 12

(pas.i

fffuaZ

| Justi W | |||

| Schuenemann, IBM, J | |||

| Reserch and Development, 1972, V | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Березин A.С | |||

| и др | |||

| Ножевой прибор к валичной кардочесальной машине | 1923 |

|

SU256A1 |

| Сборник научных трудов | |||

| М.: МИЭТ, 1077, вып | |||

| Способ сопряжения брусьев в срубах | 1921 |

|

SU33A1 |

Авторы

Даты

1988-06-15—Публикация

1984-01-11—Подача