другой вывод которого подключен к базе четвертого п-р-п-транзистора, коллектор которого соединен с кол-, лектором пятого п-р-п-транзистора, являющимся первым выходом блока внут ренней регенерации, эмиттеры четвертого, пятого и шестого п-р-п-транзисторов соединены с третьим генератором тока, база шестого п-р-п-транзистора соединена с вторым источником опорного напряжения, а коллектор подключен к одному выводу четвертого резистора, другой вьшод

которого подключен к источнику положительного напряжения, а коллектор пятого п-р-п-транзистора соединен с одним выводом пятого резистора, другой вывод которого соединен с источником положительного напряжения, четвертый диод, анод которого подключен к базе третьего п-р-п-транзистора, а катод является третьим входом блока внутренней регенерации, база пятого п-р-п-транзистора является четвертым входом блока внутренней регенерации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с произвольной выборкой | 1977 |

|

SU769626A1 |

| Устройство для считывания информа-ции из диНАМичЕСКОгО МАТРичНОгОНАКОпиТЕля | 1978 |

|

SU798996A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1569901A1 |

| Усилитель записи-считывания | 1986 |

|

SU1437913A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1575234A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

| Оперативное запоминающее устройство | 1978 |

|

SU868831A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Запоминающее устройство | 1977 |

|

SU769627A1 |

1. ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее матричньш накопитель, дешифратор строк, выходы которого соединены с соответствующими словарными шинами накопителя, дешифратор столбцов, вькоды которого соединены с первыми входами соответствующих разрядных усилителей считывания, вторые и третьи входы которых соединены с соответствующими разрядными шинами накопителя, а первые и вторые выходы разрядных усилителей считывания соединены соответственно с первым и вторьм входами выходного усилителя и блок выбора кристалла, отличающееся тем, что, с целью повьш1ения надежности путем увеличения достоверности хранимой информации и уменьшения потребляемой мощности, устройство содержит блок внутренней регенерации, первый и второй входы которого соединены соответственно с первыми и вторыми выходами разрядных усилителей счи тывания, а третий и четвертый входы с соответствующими выходами блока выбора кристалла, первый выход блока внутренней регенерации соединен с управляющими входами дешифраторов столбцов и строк, а второй выход с третьим входом выходного усилителя. 2. Устройство по п. 1, отличающееся тем, что блок внутренней регенерации содержит первый и второй п-р-п-транзисторы, базы которых соответственно являются первым и вторым входами блока внутренней регенерации, коллекторы соединены с источниками положительного напряжения, а эмиттеры - соответственно с первым и вторым генераторами тока и первым и вторым эмиттерами двух-, § эмиттерного п-р-п-транзистора, база которого подключена к первому источнику опорного напряжения, а коллектор - к базе р-п-р-транзистора эмиттер которого соединен с анодом первого и катодом второго диодов, первый резистор, один вывод которого соединен с катодом второго лциода, первый резистор, один вывод которого соединен с катодом второго диода, другой вывод - с коллектором двухэмиттерного п-р-п-транзистора и катою о дом первого диода, а анод второго диода соединен с источником положи4 тельного напряжения, коллектор р-п-ртранзистора соединен с базой третьего п-р-п-транзистора, коллектор которого соединен с базой р-п-р-транг зистора, а эмиттер - с одним выводом второго резистора, другой вьгоод которого соединен с базой четвертого п-р-п-транзистора, являющейся вторым выходом блока внутренней регенерации, третий диод, катод которого соединен с шиной нулевого потенциала, а анод .с одним выводом третьего резистора.

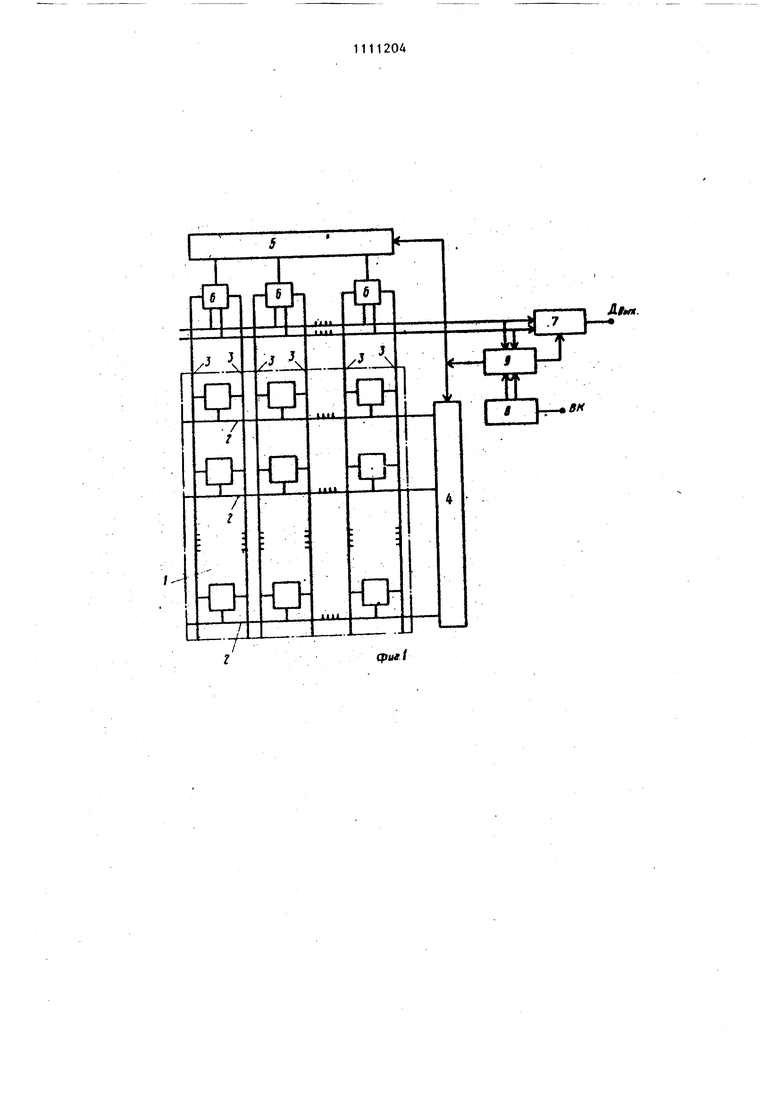

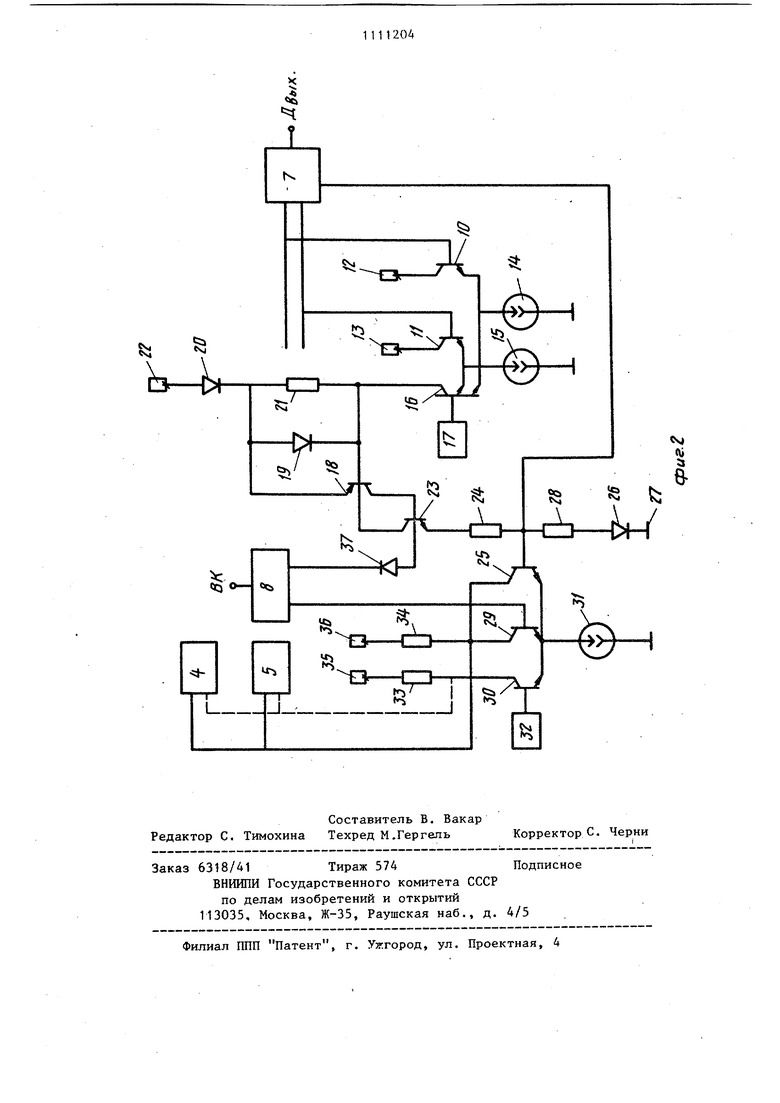

Изобретение относится к цифровой вычислительной технике, в частности к полупроводниковым оперативным запоминающим устройствам (ОЗУ). Известно ОЗУ, содержащее матричный накопитель, дешифратор строк, выходы которого соединены с соответствуюш 1ми словарными шинами нако пителя, дешифратор столбцов, выходы которого соединены с разрядными уси лителями, считывания, входы которых по/1ключены к разрядным шинам, а выходы соединены со входами выходного усилителя, и схему выбора кристалла 1. Недостатком данного ОЗУ является низкая надежность хранения информации. Наиболее близким к данному изобретению является ОЗУ, содержащее матричный накопитель, дешифратор строк, выходы которого соединены :с соответствующими словарными шинами накопителя, дешифратор столбцов, выходы которого соединены с первыми входами соответствующих разрядных усилителей считывания, вторые и третьи входы которых соединены с соответствующими разрядными шинами накопителя, а первые и вторые выходы разрядных усилителей считывания соединены соответственно с первыми вторыми входами выходного усилителя, и блок выбора кристалла Zj . Недостатком этого ОЗУ является низкая достоверность функционирования и большое потребление мощности. Целью изобретения является повышение надежности устройства путем увеличения достоверности хранимой информации и уменьшение потребляемой мощности. Поставленная цель достигается тем, что в оперативное запоминающее устройство, содержащее матричный накопитель, дешифратор строк, выходы которого соединены с соответствующими словарными шинами накопителя, дешифратор столбцов, выходы которого соединены с первыми входами соответствующих разрядных усилителей считывания, вторые и третьи входы которых соединены с соответствующими разрядными шинами накопителя, а первые и вторые выходы разрядных усилителей считывания соединены соответственно с первым и вторым входами выходного усилителя и блока выбора кристалла, введены блок внутренней регенерации, первьш и второй входы которого соединены соответственно с первыми и вторыми выходами разрядных усилителей считьшания, а третий и четвертый входы - с соответствующими выходами блока выбора кристалла, первый выход блока внутренней регенерации соединен с управляющими входами дешифраторов столбцов и строк а второй выход - с третьим входом выходного усилителя. Блок внутренней регенерации содержит первый и второй п-р-п-транзисторы, базы которых соответственно являются первым и вторым входами блока внутренней регенерации, коллекторы соединены с источниками положительного напряжения, а эмиттеры соответственно с первым и вторым генераторами тока и первым и вторым эмиттерами двухэмиттерното п-р-п-тра зистора, база которого подключена к первому источнику опорного напряжения, а коллектор - к базе р-п-р-транзистора эмиттер которого соединен с анодом первого и катодом второго диодов, первый резистор, один вывод которого соединен с катодом второго диода, другой вывод - с коллектором двухэмиттерного п-р-п-транзистора и катодом первого диода а анод второго диода соединен с источником положительного напряжения, коллектор р-п-р-транзистора соединен с базой третьего п-р-п-транзистора, коллектор которого соединен с базой р-п-р-транзистора, а эмиттер с одним вьшодом второго резистора, другой вывод которого соединен с базой четвертого п-р-п-транзистора, являющейся вторым выходом блока внутренней регенерации, третий диод катод которого соединен с шиной нулевого потенциала, а анод - с одним выводом третьего резистора, дру гой вывод которого подключен к базе четвертого п-р-п-транзистора, коллектор которого соединен с колле тором пятого п-р-п-транзистора, являющимся первым выходом блока внутренней регенерации, эмиттеры че вертого, пятого и шестого п-р-п-тра зисторов соединены с третьим генератором тока, база шестого п-р-п-транзистора соединена со вторым источником опорного напряжения, а коллектор подключен к одному выводу четвертого резистора, другой вывод которого подключен к источник положительного напряжения, а коллек тор пятого п-р-п-транзистора соединен с одним выводом пятого резистора, другой вьшод которого соединен с источником положительного напряжения, четвертый диод, анод которого подключен к базе третьего п-р-п-транзистора, а катод является третьим входом блока внутренней регенерации, база пятого п-р-п-тран зистора является четвертым входом блока внутренней регенерации. На фиг. 1 представлена структурная схема ОЗУ; на фиг. 2 - принципиаль ная электрическая схема блока внутренней регенерации. ОЗУ содержит матричный накопитель 1, словарные шины 2, разрядные шины 3, дешифратор 4 строк, дешифратор 5 столбцов, разрядные усилители считывания 6, выходной усилитель 7, блок 8 выбора кристалла, блок внутренней регенерации 9. Блок внутренней регенерации 9 содержит первый и второй п-р-п-транзисторы соответственно 10 и 11, источники положительного напряжения 12 и 13 для п-р-п-транзисторов 10 и 11, первый и второй генераторы тока соответственно 14 и 15, двухэмиттерный п-р-п-транзистор 16, пер- вый источник опорного напряжения 17, р-п-р-транзистор 18, первый и второй диоды соответственно 19 и 20, первый резистор 21, источник положительного напряжения 22, третий п-р-п-транзистор 23, второй резистор 24, четвертый п-р-п-транзистор 25, третий диод 26, шину нулевого потенциала 27, третий резистор 28, пятый п-р-п-транзистор 29, шестой п-р-п-транзистор 30, третий генератор тока 31, второй источник опорного напряжения 32, четвертый и пятый резисторы соответственно 33 и 34, источники положительного напряжения 35 и 36, четвертьй диод 37. ОЗУ работает следующим образом. При обращении к матричному накопителю 1 выбор запоминающих элементов осуществляется понижением потенциала словарной шины 2 в выбранной строке и заданием тока записи-считьгоания в разрядных шинах 3 выбранного столбца в соответствии с кодом адреса, поступающим с дешифраторов строк 4 и столбцов 5.Информационный сигнал в виде разности потенциалов разрядных шин 3 усиливается разрядным усилителем считывания 6 и поступает одновременно на выходной усилитель 7 и блок внутренней регенерации 9. Для экономии потребляемой мощности сигналом с дешифратора столбцов 5 включается разрядньм усилитель считывания 6 только в выбранном столбце. В режиме считывания информации под действием информационного сигнала выходной усилитель 7 переключается в одно из состояний (логического нуля или единицы) и выдает считанную информацию на выход ОЗУ. В режиме записи информации, в от511

личии от режима считывания, выходной усилитель 7 выключен, и записываемая информация на выход ОЗУ не поступает При поступлении информационного сигнала блок внутренней регенерации формирует два управляющий сигнала, один из них фиксирует состояние выходного усилителя 7 (в режиме считывания информации), обеспечивая постоянную выдачу считанной информации на выход ОЗУ независимо от протекающих в дальнейшем процессов в матричном накопителе 1 до окончания обращения к кристаллу. Другой управляющий сигнал отключает дешифраторы строк 4 и столбцов 5 от матричного накопителя 1 и переводит тем самым последний в режим регенерации (хранения) информации. Таким образом, когда процесс считывания или записи уже закончен, но кристалл остается выбранным, блок внутренней регенерации 9 переводит ОЗУ в целом в режим пониженной потребляемой мощности, обеспечивая высокую экономичность. По окончании обращения к кристаллу блок 8 выбора кристалла формирует два управляющих сигнала, один из которых переводит блок внутренней регенерации в исходное состояние, а другой запрещает вклю-, чение дешифраторов строк 4 и столбцов 5.

Введение в ОЗУ блока внутренней регенерации 9 позволяет создать статическое ОЗУ на основе квазистатических элементов памяти.

Блок внутренней регенерации 9 работает следующим образом.

В режиме хранения информации на базы первого и второго п-р-п-тран зисторов соответственно 10 и 11 поступают сигналы высокого логического уровня с первого и второго выходного усилителя 7. Блок 8 выбора кристалла формирует на выходах сигналы соответственно низкого и высокого логического уровня. Таким образом, в режиме хранения информации р-п-р-транзистор 18 и третий п-р-п-транзистор 23 выключены и с резистивного делителя, образованного вторым 24 и третьим 28 резисторами, на базу четвертого п-р-п-транзистора 25 посту,пает сигнал низкого логического уровня. Ток третьего генератора тока 31 протекает через пятый транзистор 29 и формирует на пятом резисторе 34

1204

сигнал низкого логического уровня, отключающий дешифраторы строк 4 и столбцов 5 от матричного накопителя 1.

При обращении к кристаллу блок 8 выбора кристалла формирует на первом выходе сигнал высокого логического уровня (но р-п-р-транзистор 18 и третий п-р-п-транзистор 23 остаются в выключенном состоянии бла0годаря использованию четвертого развязывающего диода 37), а на втором выходе - низкого логического уровня.

Ток третьего генератора тока 31

5 переключается в шестой п-р-п-транзистор 30. На пятом резисторе 34 формируется сигнал высокого логического уровня, разрешающий прохождение кода адреса с дешифраторов

0 строк 4 и столбцов 5 на накопитель 1. В зависимости от используемых конструкций дешифраторов для их включения и выключения может быть использован сигнал противоположной поляр5ности, формируемый на четвертом резисторе 33 (фиг. 2, показано пунктиром) . После завершения в накопителе 1 процесса считывания или записи дифференциальный информационный

0 сигнал поступает с разрядных усилителей считывания 6 на выходной усилитель 7. В зависимости от полярности дифференциального сигнала ток одного из генераторов тока 14 или

5 15 переключается в двухэмиттерный транзистор 16 и включает р-п-р-транзистор 18 и третий п-р-п-транзистор 23. Второй диод 20 и третий диод 26 служат для согласования логичес0ких уровней, а первый диод 19,- для стабилизации тока, протекающего через р-п-р-транзистор 18 и третий п-р-п-транзистор 23. На резистив.ном делителе, образованном вторым

5 и третьим резисторами 24 и 28 формируется сигнал высокого лoгичecкdго уровня, фиксируннций состояние выходного усилителя 7 и переключающий ток третьего генератора тока 31 в

0 четвертый транзистор 25. На пятом резисторе 34 формируется сигнал низкого логического уровня, отключающий дешифраторы строк 4 и столбцов 5 от накопителя 1 и переSводящий последний в режим регенера ции (хранения) информации. С переходном накопителя 1 в режим регенерации информации потенциалы на 711 входах выходного усипителя 7 выравниваются и повышаются. Ток первого или второго генераторов тока 14, 15 вновь переключается в первый или второй п-р-п-транзисгоры 10 и 11, но р-п-р-транзистор 18 и третий . п-р-п-транзистор 23 остаются включенными. Состояние вьпсодного усилителя 7 остается фиксированным до окончания обращения к кристаллу. Ток третьего генератора тока 31 по-прежнему протекает через четвертыйп-р-п-транзистор 25 и формирует на пятом резисторе 34- сигнал низкого логического уровня. Дешифратор строки 4 и столбцов 5 отключены от накопителя 1. Пр окончании обращения к кристалл блок 8 выбора кристалла формирует на Своих выходах сигналы соответственн низкого и высокого логических уровней, р-п-р-транзистор и третий п-р-п -транзистор 23 выключаются, резисти ным делителем, образованным вторым и третьим резисторами 24 и 28, на втором выходе блока внутренней реге нерации 9 формируется сигнал низкого логического уровня, выключающи выходной усилитель 7. Ток третьего генератора тока 31 переключается из четвертого п-р-п-транзистора 25 в пятый п-р-п-транзистор 29. На пятом резисторе 34 по-прежнему формиуется сигнал низкого логического ровня и дешифраторы строк 4 и столбцов 5 отключены от накопителя. Использование блока внутренней регенерации 9 не ухудшает быстродействие ОЗУ, так как включение блока внутренней регенерации 9 и перевод накопителя 1 в режим регенерации информации происходит одновременно с включением выходного усилителя 7. В то же время блок внутренней регенерации 9 позволяет значительно снизить потребляемую ОЗУ мощность за счет выключения ряда блоков или работы их при пониженной потребляемой мощности в режиме регенерации-информации. Кроме того, использование блока внутренней регенерации 9 позволяет повысить достоверность функционирования ОЗУ за счет того., что сигналом, переводящим накопитель 1 в режиме регенерации информации, является внутренний (информационный) сигнал. Введение в ОЗУ блока внутренней регенерации выгодно отличает предложенное оперативное запоминающее устройство от прототипа, так как позволяет повысить достоверность функционирования ОЗУ и снизить потребляемую мощность.

Л/м.

CiJя

}«s

(V

:s

8

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Electronik, № 13, 1981, S | |||

| Способ приготовления пищевого продукта сливкообразной консистенции | 1917 |

|

SU69A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| IEEE Gournal of Solid-State Circuits,; № 5, v | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ УСЛОВНОГО РЕФЛЕКСА^.«.-1 | 1972 |

|

SU429434A1 |

Авторы

Даты

1984-08-30—Публикация

1982-11-16—Подача